用于减轻编程干扰的设备和方法与流程

用于减轻编程干扰的设备和方法

[0001]

相关申请

[0002]

本申请要求于2019年8月29日提交的美国临时申请第62/893,331号的权益,所述美国临时申请特此通过引用整体并入本文。

技术领域

[0003]

本公开总体上涉及存储器,并且具体地,在一或多个实施例中,本公开涉及用于减轻编程干扰的设备和方法。

背景技术:

[0004]

存储器(例如,存储器装置)通常以内部半导体集成电路装置的形式设置于计算机或其它电子装置中。存在许多不同类型的存储器,包含随机存取存储器(ram)、只读存储器(rom)、动态随机存取存储器(dram)、同步动态随机存取存储器(sdram)和闪存。

[0005]

闪存已经发展成为广泛的电子应用的非易失性存储器的流行来源。闪存通常使用单晶体管存储器单元,所述单晶体管存储器单元可以实现高存储器密度、高可靠性和低功耗。通过对电荷储存结构(例如,浮栅或电荷陷阱(charge trap))进行编程(通常被称为写入)或其它物理现象(例如,相变或极化)实现的存储器单元的阈值电压(vt)的变化决定了每个存储器单元的数据状态(例如,数据值)。闪存和其它非易失性存储器的常见用途包含个人计算机、个人数字助理(pda)、数码相机、数字媒体播放器、数字记录器、游戏、电器、车辆、无线装置、移动电话和可移除存储器模块,并且非易失性存储器的用途继续扩展。

[0006]

与非(nand)闪存是一种常见的闪存装置,其由于基本存储器单元配置被布置的逻辑形式而如此命名。通常,与非闪存的存储器单元阵列被布置成使得阵列的行的每个存储器单元的控制栅极连接在一起以形成如字线等存取线。阵列的列包含在一对选择门(例如,源极选择晶体管和漏极选择晶体管)之间串联连接在一起的存储器单元串(通常被称为与非串)。每个源极选择晶体管可以连接到源极,而每个漏极选择晶体管可以连接到数据线,如列位线。已知的是,在存储器单元串与源极之间和/或存储器单元串与数据线之间使用一个以上选择门来实现改变。

[0007]

存储器中的编程通常通过以下来完成:施加由编程验证脉冲分离的多个编程脉冲以将所选组存储器单元中的每个存储器单元编程为相应的预期数据状态(其可以是临时或最终数据状态)。利用此类方案,将编程脉冲施加到用于所选存储器单元的存取线,如通常被称为字线的那些存取线。在每个编程脉冲之后,使用一或多个编程验证脉冲来验证所选存储器单元的编程。目前的编程通常在增量步骤脉冲编程方案中使用许多编程脉冲,其中每个编程脉冲是使存储器单元阈值电压移动某一量的单个脉冲。

技术实现要素:

[0008]

本申请的一方面涉及一种操作存储器的方法,所述方法包括:对串联连接存储器单元串的特定存储器单元执行读出操作,其中所述串联连接存储器单元串的每个存储器单

元连接到多条存取线中的相应存取线;使所述多条存取线中用于所述串联连接存储器单元串的第二存储器单元的所述相应存取线放电到第一电压电平;使所述多条存取线中用于所述特定存储器单元的所述相应存取线放电到高于所述第一电压电平的第二电压电平;以及使所述多条存取线中用于所述串联连接存储器单元串的第三存储器单元的所述相应存取线放电到低于所述第二电压电平并且高于所述第一电压电平的第三电压电平。

[0009]

本申请的另一方面涉及一种操作存储器的方法,所述方法包括:对串联连接存储器单元串的特定存储器单元执行读出操作,其中所述串联连接存储器单元串的每个存储器单元连接到多条存取线中的相应存取线;使所述多条存取线中用于所述串联连接存储器单元串的第一存储器单元子集的所述相应存取线放电到第一电压电平,其中所述第一存储器单元子集的每个存储器单元位于所述串联连接存储器单元串的所述特定存储器单元与第一端之间;使所述多条存取线中用于所述串联连接存储器单元串的第二存储器单元子集的所述相应存取线放电到所述第一电压电平,其中所述第二存储器单元子集的每个存储器单元位于所述特定存储器单元与所述第一存储器单元子集之间;使所述多条存取线中用于所述特定存储器单元的所述相应存取线放电到高于所述第一电压电平的第二电压电平;使所述多条存取线中用于所述串联连接存储器单元串的第三存储器单元子集的所述相应存取线放电到低于所述第二电压电平并且高于所述第一电压电平的第三电压电平,其中所述第三存储器单元子集的每个存储器单元位于所述串联连接存储器单元串的所述特定存储器单元与第二端之间;使所述多条存取线中用于所述串联连接存储器单元串的第四存储器单元子集的所述相应存取线放电到所述第一电压电平,其中所述第四存储器单元子集的每个存储器单元位于所述串联连接存储器单元串的所述第三存储器单元子集与所述第二端之间;以及使所述多条存取线中用于所述串联连接存储器单元串的第五存储器单元子集的所述相应存取线放电到所述第一电压电平,其中所述第五存储器单元子集的至少一个存储器单元位于选自由以下组成的组的位置中:所述串联连接存储器单元串的所述第一存储器单元子集与所述第一端之间;和所述串联连接存储器单元串的所述第四存储器单元子集与所述第二端之间。

[0010]

本申请的另一方面涉及一种存储器,其包括:存储器单元阵列,所述存储器单元阵列包括多个串联连接存储器单元串;以及控制器,所述控制器用于对所述存储器单元阵列进行存取,其中所述控制器被配置成:对所述多个串联连接存储器单元串中的串联连接存储器单元串的特定存储器单元执行读出操作,其中所述串联连接存储器单元串的每个存储器单元连接到多条存取线中的相应存取线;使所述多条存取线中用于所述串联连接存储器单元串的第二存储器单元的所述相应存取线放电到第一电压电平,其中所述第二存储器单元位于所述串联连接存储器单元串的所述特定存储器单元与第一端之间;使所述多条存取线中用于所述特定存储器单元的所述相应存取线放电到高于所述第一电压电平的第二电压电平;并且使所述多条存取线中用于所述串联连接存储器单元串的第三存储器单元的所述相应存取线放电到低于所述第二电压电平并且高于所述第一电压电平的第三电压电平,其中所述第三存储器单元位于所述串联连接存储器单元串的所述特定存储器单元与第二端之间。

[0011]

本申请的又另一方面涉及一种存储器,其包括:存储器单元阵列,所述存储器单元阵列包括多个串联连接存储器单元串;以及控制器,所述控制器用于对所述存储器单元阵

列进行存取,其中所述控制器被配置成:对所述多个串联连接存储器单元串中的串联连接存储器单元串的特定存储器单元执行读出操作,其中所述串联连接存储器单元串的每个存储器单元连接到多条存取线中的相应存取线;使所述多条存取线中用于所述串联连接存储器单元串的第一存储器单元子集的所述相应存取线放电到第一电压电平,其中所述第一存储器单元子集的每个存储器单元位于所述串联连接存储器单元串的所述特定存储器单元与第一端之间;使所述多条存取线中用于所述串联连接存储器单元串的第二存储器单元子集的所述相应存取线放电到所述第一电压电平,其中所述第二存储器单元子集的每个存储器单元位于所述特定存储器单元与所述第一存储器单元子集之间;使所述多条存取线中用于所述特定存储器单元的所述相应存取线放电到高于所述第一电压电平的第二电压电平;使所述多条存取线中用于所述串联连接存储器单元串的第三存储器单元子集的所述相应存取线放电到低于所述第二电压电平并且高于所述第一电压电平的第三电压电平,其中所述第三存储器单元子集的每个存储器单元位于所述串联连接存储器单元串的所述特定存储器单元与第二端之间;使所述多条存取线中用于所述串联连接存储器单元串的第四存储器单元子集的所述相应存取线放电到所述第一电压电平,其中所述第四存储器单元子集的每个存储器单元位于所述串联连接存储器单元串的所述第三存储器单元子集与所述第二端之间;并且使所述多条存取线中用于所述串联连接存储器单元串的第五存储器单元子集的所述相应存取线放电到所述第一电压电平,其中所述第五存储器单元子集的至少一个存储器单元位于选自由以下组成的组的位置中:所述串联连接存储器单元串的所述第一存储器单元子集与所述第一端之间;和所述串联连接存储器单元串的所述第四存储器单元子集与所述第二端之间。

附图说明

[0012]

图1是根据一个实施例的与作为电子系统的一部分的处理器通信的存储器的简化框图。

[0013]

图2a-2b是可以在参考图1描述的类型的存储器中使用的存储器单元阵列的部分的示意图。

[0014]

图3概念性地描绘了根据各个实施例的在描述操作存储器的方法中以供参考的相邻的串联连接存储器单元串。

[0015]

图4描绘了用于与各个实施例一起使用的操作存储器的方法的定时图。

[0016]

图5描绘了用于与各个实施例一起使用的操作存储器的方法的定时图。

[0017]

图6是根据一个实施例的操作存储器的方法的流程图。

[0018]

图7a-7b是根据另一个实施例的操作存储器的方法的流程图。

[0019]

图8描绘了根据另外的实施例的操作存储器的方法的定时图。

具体实施方式

[0020]

在以下详细描述中,对附图进行了参考,所述附图形成所述详细描述的一部分,并且在附图中通过图解的方式示出了具体实施例。在附图中,贯穿若干视图,相似的附图标记描述基本上类似的组件。可以利用其它实施例,并且在不脱离本公开的范围的情况下,可以进行结构、逻辑和电气改变。下面的详细描述因此不应视为具有限制意义。

[0021]

本文所使用的术语“半导体”可以指例如材料层、晶圆或衬底,并且包含任何基底半导体结构。“半导体”应理解为包含硅蓝宝石(sos)技术、硅绝缘体(soi)技术、薄膜晶体管(tft)技术、掺杂和未掺杂的半导体、由基底半导体结构支撑的外延硅层以及本领域的技术人员众所周知的其它半导体结构。此外,当在以下描述中引用半导体时,可能已经利用先前的工艺步骤在基底半导体结构中形成了区域/结,并且术语半导体可以包含含有此类区域/结的底层。除非从上下文中明显看出,否则本文所使用的术语导电(conductive)及其各种相关形式,例如,导电(conduct、conducting、conduction)、导电地(conductively)、导电性(conductivity)等是指电学上的导电。类似地,除非从上下文中明显看出,否则本文所使用的术语连接及其各种相关形式,例如,连接(connect、connected、connection)等是指电连接。

[0022]

在本文中认识到,即使在值预期相等的情况下,工业加工和操作的可变性和准确性也可能导致与其预期值有差异。这些可变性和准确性通常将取决于集成电路装置的制造和操作中所利用的技术。如此,如果值预期相等,则认为那些值相等,而无论其所产生的值如何。

[0023]

在可能缺少体触点的三维存储器阵列(例如,三维与非存储器阵列)中,沟道区域中的电位因其可以是浮置的而可能不易控制。存取操作(例如,编程验证操作)可以使沟道区域中的电位处于通常不同于参考电位(如接地或0v)的不稳定状态。沟道区域中的这种电位可以影响随后的存取操作,例如,编程操作,从而对未被选择用于编程的存储器单元的数据状态产生不期望的改变,所述改变通常被称为干扰。

[0024]

具体地,在编程操作期间,被选择用于进行编程操作的存取线可以连接到被选择用于进行编程的存储器单元(例如,所选存储器单元)以及未选择用于进行编程的存储器单元(例如,未选择的受害者存储器单元)。如果可以暴露于与所选存储器单元的电压相同的电压的受害者存储器单元的沟道区域的电压电平太低,则所述受害者存储器单元可能在编程验证操作之后经历来自随后的编程脉冲的干扰。为了减少编程验证操作之后对受害者存储器单元的干扰,可以使沟道区域升压。然而,如果升压太低,则受害者存储器单元可能经受足以改变其预期数据状态的寄生编程。另外,如果升压太高且局部化,则其可能在受害者存储器单元与所述受害者存储器单元的最靠近的相邻存储器单元之间产生高电场。此类电场可以生成电子-空穴对,从而产生高能自由载流子(例如,热电子),所述高能自由载流子进而也可以改变受害者存储器单元的预期数据状态。随着存储器存储密度(例如,每个存储器单元存储的数位的数量)增加,这些干扰效应可能变得更加关键。

[0025]

一种使串联连接存储器单元串的受害者存储器单元的沟道区域升压的方法可以包含在编程验证操作之后使用于串联连接存储器单元串的所有存取线和选择线放电到参考电位,然后将脉冲施加到选择线(例如,漏极侧选择线)子集和存取线(例如,漏极侧存取线)子集以在随后的编程脉冲之前对沟道进行预充电(通常被称为“播种操作”)。然而,如果已经对与受害者存储器单元处于同一串联连接存储器单元串内的连接到经过脉冲调制的存取线子集的存储器单元进行编程,则此类播种操作的影响可能会减小或甚至消除。各个实施例可以在没有利用此类播种操作的情况下促进减轻对受害者存储器单元的编程干扰。

[0026]

图1是根据一个实施例的呈存储器(例如,存储器装置)100的形式的第一设备的简化框图,所述第一设备与呈处理器130(作为呈电子系统的形式的第三设备的一部分)的形

式的第二设备通信。电子系统的一些实例包含个人计算机、个人数字助理(pda)、数字相机、数字媒体播放器、数字记录器、游戏、电器、车辆、无线装置、移动电话等。处理器130,例如,存储器装置100外部的控制器,可以是存储器控制器或其它外部主机装置。

[0027]

存储器装置100包含逻辑上布置成行和列的存储器单元阵列104。逻辑行的存储器单元通常连接到同一存取线(通常被称为字线),而逻辑列的存储器单元通常选择性地连接到同一数据线(通常被称为位线)。单条存取线可以与一个以上的存储器单元逻辑行相关联,并且单条数据线可以与一个以上的逻辑列相关联。存储器单元阵列104的至少一部分的存储器单元(图1中未示出)能够被编程为至少两种数据状态之一。

[0028]

提供了行解码电路系统108和列解码电路系统110以解码地址信号。地址信号被接收和解码以对存储器单元阵列104进行存取。存储器装置100还包含输入/输出(i/o)控制电路系统112,以管理命令、地址和数据输入到存储器装置100以及从存储器装置100输出数据和状态信息。地址寄存器114与i/o控制电路系统112和行解码电路108以及列解码电路110通信,以在解码之前锁存地址信号。命令寄存器124与i/o控制电路系统112和控制逻辑116通信以锁存传入命令。

[0029]

控制器(例如,存储器装置100内部的控制逻辑116)响应于命令而控制对存储器单元阵列104的存取并生成外部处理器130的状态信息,即,控制逻辑116被配置成对存储器单元阵列104执行存取操作(例如,读取操作、编程操作和/或擦除操作)。控制逻辑116可以被配置成执行本文所描述的各个实施例的方法。控制逻辑116与行解码电路系统108和列解码电路系统110通信,以响应于地址而控制行解码电路系统108和列解码电路系统110。

[0030]

控制逻辑116还与高速缓存寄存器118通信。高速缓存寄存器118按照控制逻辑116的指示锁存传入或传出的数据,以在存储器单元阵列104分别忙于分别写入或读取其它数据的同时临时存储数据。在编程操作(例如,写入操作)期间,可以将数据从高速缓存寄存器118传递到数据寄存器120,以传送到存储器单元阵列104;然后可以将新数据从i/o控制电路系统112锁存在高速缓存寄存器118中。在读取操作期间,可以将数据从高速缓存寄存器118传递到i/o控制电路系统112,以输出到外部处理器130;然后可以将新数据从数据寄存器120传递到高速缓存寄存器118。高速缓存寄存器118和/或数据寄存器120可以形成存储器装置100的数据缓冲器(例如,页缓冲器)(例如,可以形成其一部分)。数据缓冲器可以进一步包含感测装置(图1中未示出),以例如通过感测连接到存储器单元阵列104中的存储器单元的数据线的状态来感测所述存储器单元的数据状态。状态寄存器122可以与i/o控制电路系统112和控制逻辑116通信以锁存状态信息,以供输出到处理器130。

[0031]

存储器装置100在控制逻辑116处通过控制链路132从处理器130接收控制信号。控制信号可以包含芯片启用ce#、命令锁存启用cle、地址锁存启用ale、写入启用we#、读取启用re#和写入保护wp#。根据存储器装置100的性质,可以通过控制链路132进一步接收另外的或替代性控制信号(未示出)。存储器装置100通过多路复用的输入/输出(i/o)总线134从处理器130接收命令信号(其表示命令)、地址信号(其表示地址)和数据信号(其表示数据),并通过i/o总线134将数据输出到处理器130。

[0032]

例如,可以在i/o控制电路系统112处通过i/o总线134的输入/输出(i/o)引脚[7:0]接收命令,并且然后可以将其写入到命令寄存器124中。可以在i/o控制电路系统112处通过i/o总线134的输入/输出(i/o)引脚[7:0]接收地址,并且然后可以将其写入到地址寄存

器114中。可以在i/o控制电路系统112处通过输入/输出(i/o)引脚[7:0](对于8位装置)或输入/输出(i/o)引脚[15:0](对于16位装置)接收数据,并且然后可以将其写入到高速缓存寄存器118中。随后可以将数据写入到数据寄存器120中以对存储器单元阵列104进行编程。对于另一个实施例,可以省略高速缓存寄存器118,并且可以将数据直接写入到数据寄存器120中。还可以通过输入/输出(i/o)引脚[7:0](对于8位装置)或输入/输出(i/o)引脚[15:0](对于16位装置)输出数据。尽管可以参考i/o引脚,但是所述i/o引脚可以包含通过外部装置(例如,处理器130)提供到存储器装置100的电连接的任何导电节点,如常用的导电衬垫或导电凸点。

[0033]

本领域的技术人员应了解,可以提供另外的电路系统和信号,并且已经简化了图1的存储器装置100。应当认识到,参考图1描述的各个块组件的功能可能不一定被分离到集成电路装置的不同组件或组件部分。例如,可以使集成电路装置的单个组件或组件部分适用于执行图1的一个以上的块组件的功能。可替代地,可以组合集成电路装置的一或多个组件或组件部分以执行图1的单个块组件的功能。

[0034]

另外,尽管根据接收和输出各种信号的流行约定描述了特定的i/o引脚,但应注意,可以在各个实施例中使用的其它组合或其它数量的i/o引脚(或其它i/o节点结构)。

[0035]

图2a是可以在参考图1描述的类型的存储器中例如用作存储器单元阵列104的一部分的如与非存储器阵列等存储器单元阵列200a的一部分的示意图。存储器阵列200a包含如字线2020到202

n

等存取线以及如位线2040到204

m

等数据线。字线202可以以多对一关系连接到图2a中未示出的全局存取线(例如,全局字线)。对于一些实施例,存储器阵列200a可以形成于半导体之上,所述半导体例如可以被导电掺杂成具有如p型导电性等导电性类型,例如以形成p阱,或导电掺杂成具有如n型导电性等导电性类型,例如以形成n阱。

[0036]

存储器阵列200a可以以行(各自对应于字线202)和列(各自对应于位线204)布置。每列可以包含串联连接存储器单元(例如,非易失性存储器单元)串,如与非串2060到206

m

之一。每个与非串206可以连接(例如,选择性地连接)到公共源极(src)216,并且可以包含存储器单元2080到208

n

。存储器单元208可以表示用于存储数据的非易失性存储器单元。存储器单元208可以进一步表示非易失性“虚设”存储器单元。虚设存储器单元可以设置在与非串206的边缘处(如字线2020和202

n

处),并且可以起到减少对与非串206的剩余存储器单元208的干扰效应并支持与位线204和/或源极216连接或隔离的作用。虚设存储器单元通常不用于存储可由存储器的用户存取的数据。边缘字线2020和202

n

与分别最靠近所述边缘字线的选择门210或212之间不存在中间存储器单元208。

[0037]

每个与非串206的存储器单元208可以串联连接于如选择门2100到210

m

之一(例如,其可以是源极选择晶体管,通常被称为选择门源极)等选择门210(例如,场效应晶体管)与如选择门2120到212

m

之一(例如,其可以是漏极选择晶体管,通常被称为选择门漏极)等选择门212(例如,场效应晶体管)之间。选择门2100到210

m

可以共同连接到如源极选择线(sgs)等选择线214,并且选择门2120到212

m

可以共同连接到如漏极选择线(sgd)等选择线215。尽管被描绘为传统的场效应晶体管,但是选择门210和212可以利用与存储器单元208类似的(例如,相同的)结构。选择门210和212可以表示串联连接的多个选择门,其中每个串联的选择门被配置成接收同一个或独立的控制信号。

[0038]

每个选择门210的源极可以连接到公共源极216。每个选择门210的漏极可以连接

到对应与非串206的存储器单元2080。例如,选择门2100的漏极可以连接到对应与非串2060的存储器单元2080。因此,每个选择门210可以被配置成将对应与非串206选择性地连接到公共源极216。每个选择门210的控制栅极可以连接到选择线214。

[0039]

每个选择门212的漏极可以连接到对应与非串206的位线204。例如,选择门2120的漏极可以连接到对应与非串2060的位线2040。每个选择门212的源极可以连接到对应与非串206的存储器单元208

n

。例如,选择门2120的源极可以连接到对应的与非串2060的存储器单元208

n

。因此,每个选择门212可以被配置成将对应与非串206选择性地连接到对应位线204。每个选择门212的控制栅极可以连接到选择线215。

[0040]

图2a中的存储器阵列可以是准二维存储器阵列,并且可以具有总体上平面的结构,例如,其中公共源极216、与非串206和位线204在基本上平行的平面中延伸。可替代地,图2a中的存储器阵列可以是三维存储器阵列,例如,其中与非串206可以基本上垂直于含有公共源极216的平面和基本上平行于含有公共源极216的平面的含有位线204的平面延伸。

[0041]

存储器单元208的典型构造包含可以确定存储器单元的数据状态(例如,通过阈值电压的变化)的数据存储结构234(例如,浮栅、电荷陷阱等)和控制栅极236,如图2a所示。数据存储结构234可以包含导电结构和介电结构两者,而控制栅极236通常由一或多种导电材料形成。在一些情况下,存储器单元208可以进一步具有限定的源极/漏极(例如,源极)230和限定的源极/漏极(例如,漏极)232。存储器单元208的控制栅极236连接到(并且在一些情况下形成)字线202。

[0042]

一列存储器单元208可以是选择性地连接到给定位线204的一个与非串206或多个与非串206。一行存储器单元208可以是共同连接到给定字线202的存储器单元208。一行存储器单元208可以但不必包含共同连接到给定字线202的所有存储器单元208。多行存储器单元208通常可以被分成一或多组存储器单元208物理页,并且存储器单元208的物理页通常包含共同连接到给定字线202的每隔一个存储器单元208。例如,共同连接到字线202

n

并且选择性地连接到偶数位线204(例如,位线2040、2042、2044等)的存储器单元208可以是一个存储器单元208(例如,偶数存储器单元)物理页,而共同连接到字线202

n

并选择性地连接到奇数位线204(例如,位线2041、2043、2045等)的存储器单元208可以是另一个存储器单元208(例如,奇数存储器单元)物理页。尽管在图2a中未明确描绘出位线204

3-2045,但是从图中可以明显看出,存储器单元阵列200a的位线204可以连续编号为位线2040到位线204

m

。共同连接到给定字线202的其它组存储器单元208也可以限定存储器单元208物理页。对于某些存储器装置,共同连接到给定字线的所有存储器单元可以被视为存储器单元物理页。存储器单元物理页的在单个读取操作期间读取或在单个编程操作期间编程的部分(在一些实施例中,其仍可以是整行)(例如,存储器单元上页或下页)可以被视为存储器单元逻辑页。存储器单元块可以包含被配置成一起被擦除的那些存储器单元,如连接到字线202

0-202

n

的所有存储器单元(例如,共享公共字线202的所有与非串206)。除非明确区分,否则本文中对存储器单元页的引用是对存储器单元逻辑页的引用。

[0043]

尽管结合与非闪存讨论了图2a的实例,但是本文所描述的实施例和概念不限于特定的阵列架构或结构,并且可以包含其它结构(例如,sonos、相变、铁电等)和其它架构(例如,与(and)阵列、或非(nor)阵列等)。

[0044]

图2b是可以在参考图1描述的类型的存储器中例如用作存储器单元阵列104的一

部分的存储器单元阵列200b的一部分的另一个示意图。图2b中编号相似的元件对应于关于图2a提供的描述。图2b提供了三维与非存储器阵列结构的一个实例的另外的细节。三维与非存储器阵列200b可以结合竖直结构,所述竖直结构可以包含半导体柱,其中柱的一部分可以充当与非串206的存储器单元的沟道区域。与非串206可以各自通过选择晶体管212(例如,其可以是漏极选择晶体管,通常被称为选择门漏极)选择性地连接到位线204

0-204

m

,并且通过选择晶体管210(例如,其可以是源极选择晶体管,通常被称为选择门源极)选择性地连接到公共源极216。多个与非串206可以选择性地连接到同一位线204。与非串206的子集可以通过以下连接到其相应位线204:偏置选择线215

0-215

k

以选择性地激活各自位于与非串206与位线204之间的特定选择晶体管212。可以通过偏置选择线214来激活选择晶体管210。每条字线202可以连接到存储器阵列200b的多行存储器单元。通过特定字线202彼此共同连接的存储器单元行可以统称为层。

[0045]

三维与非存储器阵列200b可以形成于外围电路系统226之上。外围电路系统226可以表示用于存取存储器阵列200b的各种电路系统。外围电路系统226可以包含用于连接到存储器阵列200b的字线202的串驱动器(图2b中未示出)。外围电路系统226可以包含互补电路元件。例如,外围电路系统226可以包含在同一半导体衬底——通常被称为cmos或互补金属氧化物半导体的工艺——上形成的n沟道晶体管和p沟道晶体管两者。尽管由于集成电路制造和设计的进步,cmos通常不再利用严格的金属氧化物半导体构造,但为方便起见,仍保留cmos名称。

[0046]

图3概念性地描绘了根据各个实施例的在描述操作存储器的方法中以供参考的相邻的串联连接存储器单元串(例如,与非串2060和2061)。图3中编号相似的元件对应于关于图2a和2b提供的描述。

[0047]

参考图3,与非串2060和2061各自被描绘成包含分别连接到存取线202

0-202

y

的用于存储数据的y+1个存储器单元208(例如,存储器单元208

0-208

y

)。与非串2060和2061各自被进一步描绘成包含作为虚设存储器单元的分别连接到存取线202

d0-202

d3

的四个存储器单元208(例如,虚设存储器单元208

d0-208

d3

)。尽管描绘了四个虚设存储器单元(其中两个位于与非串206的每个端处),但是可以在与非串206的每个端处使用其它数量的虚设存储器单元,其中每个端彼此独立。与非串206的端处的虚设存储器单元可以被称为边缘虚设存储器单元,如源极侧边缘虚设存储器单元208

d0-208

d1

和漏极侧边缘虚设存储器单元208

d2-208

d3

。另外,已知在用于存储数据的存储器单元之间进一步包含虚设存储器单元。例如,虚设存储器单元可以包含在与非串206中,在存储器单元208

n+3

与存储器单元208

y-1

之间。插置在用于存储数据的存储器单元之间的此类虚设存储器单元可以被称为中间虚设存储器单元。此外,如关于图2a所述,选择门210(例如,选择门2100和2101)和选择门212(例如,选择门2120和2121)可以各自表示串联连接并且在相应选择线上接收同一个或独立的控制信号的相应多个选择门。

[0048]

图4描绘了用于与各个实施例一起使用的操作存储器的方法的定时图。提供图4以将各个实施例的方法置于先前可以执行哪种类型的操作的上下文中。

[0049]

图4的定时图可以表示例如将参考图5描述的对存储器的读出操作,例如编程操作的编程脉冲之后编程验证操作。为简单起见,图4将假定对各自表示与两个数位的位模式相对应的数据状态的mlc存储器单元(例如,使用四个阈值电压范围表示数据状态l0、l1、l2和

l3的四电平存储器单元)进行读出操作。虽然参考mlc存储器单元进行了讨论,但是对较高存储密度存储器单元(例如,tlc(八个数据状态)或qlc(十六个数据状态)存储器单元)执行的读出操作同样适用。表1提供了mlc存储器单元的数据状态与其对应逻辑数据值之间的一种可能的对应关系。数据状态到逻辑数据值的其它分配是已知的。如本文所使用的,保持处于最低数据状态(例如,擦除状态或l0数据状态)的存储器单元将被视为被编程为最低数据状态。

[0050]

表1

[0051][0052]

在图4中,迹线440可以表示施加到连接到被选择用于进行读出操作的存储器单元(例如,目标存储器单元)的存取线的电压电平。以下讨论将至少参考图3进行并且将假定被选择用于进行读出操作的存储器单元是与非串2060的存储器单元208

n

,使得迹线440可以表示施加到存取线202

n

的电压电平。因为存取线202

n

含有目标存储器单元,所以所述存储线可以被称为所选存取线,而剩余存取线202可以被称为未选择的存取线。因为与非串2060含有目标存储器单元,所以所述与非串可以被称为所选串联连接存储器单元串。因为与非串2061可以不含有已经对其进行了读出操作的存储器单元,所以所述与非串可以被称为未选择的串联连接存储器单元串。

[0053]

迹线442可以表示施加到未选择的存取线202(例如,存取线202

d0-202

d1

、202

0-202

n-1

、202

n+1-202

y

和202

d2-202

d3

)中的一或多条存取线的电压电平。迹线444可以表示施加到选择线214的电压电平和/或施加到选择线215的电压电平。迹线446可以表示读出启用信号的电压电平。应认识到,图4的读出操作可以具有一个以上目标存储器单元,并且可以包含连接到用于每个与非串206或其某个子集的所选存取线202的存储器单元208。

[0054]

在时间t0处,预充电阶段可以开始。读出操作的预充电阶段可以使未选择的存取线202处于无论其数据状态如何都足以激活其相应的连接存储器单元的电压电平(例如,通过电压)。如图4的实例中所示出的,含有目标存储器单元(例如,一或多个目标存储器单元)的存储器单元块的所有存取线202的电压电平初始升高到电压电平452。无论存取线202之一的数据状态如何,电压电平452都可以足以激活连接到的所述存取线的每个存储器单元。作为一个实例,电压电平452可以为大约8v。以此方式使所有存取线202一起升高可以促进将期望电压电平是电压电平452的任何存取线202的速度提高到稳定状态。选择线214和选择线215可以升高到足以激活其相应的选择门的电压电平454。读出启用信号通常可以具有指示读出被禁用的逻辑高电平,并且可以转变为逻辑低电平以启用读出。读出启用信号的逻辑高电平可以对应于电压电平448,所述电压电平可以是供电电压(如vcc)。读出启用信号的逻辑低电平可以对应于电压电平450,所述电压电平可以是参考电位(例如,vss、接地或0v)。

[0055]

在时间t1处或大约在时间t1处,可以使所选存取线202

n

放电到电压电平4320。电压

电平4320可以表示旨在区分(例如,在编程验证操作期间的)目标存储器单元的可能数据状态的读出电压(例如,验证电压)。例如,如果目标存储器单元在电压电平4320被施加到存取线202

n

并且因此被施加到目标存储器单元的控制栅极时被激活,则所述目标存储器单元可以被视为具有与低于或等于电压电平4320的阈值电压的范围相对应的数据状态。如果目标存储器单元在电压电平4320被施加到存取线202

n

时被去激活,则所述目标存储器单元可以被视为具有与高于电压电平4320的阈值电压的范围相对应的数据状态。如本领域中众所周知的,当电压电平4320被施加到存取线202

n

时,可以在时间t3处(例如,响应于转变为逻辑低电平的读出启用信号而)执行对数据线的状态进行读出以确定目标存储器单元是否被激活。作为一个实例,电压电平4320可以对应于读出电压,所述读出电压旨在确定如果存储器单元在预充电阶段之后响应于电压电平4320而首次被激活,则所述存储器单元具有l0数据状态。对于一些实施例,尽管电压电平4320被描绘为高于电压电平450,但是电压电平432

0-4322中的一或多个电压电平可以是负电压电平。

[0056]

当电压电平4320在时间t2处被施加到所选存取线202

n

时,电压电平452可以被施加到未选择的存取线202

d0-202

d1

、202

0-202

n-1

、202

n+1-202

y

和202

d2-202

d3

。无论未选择的存取线的数据状态如何,电压电平452都可以足以激活连接到的这些未选择的存取线的存储器单元。另外,当电压电平4320在时间t2处被施加到所选存取线202

n

时,电压电平454可以被施加到选择线214和选择线215。电压电平454可以足以激活连接到这些选择线的选择门。以此方式,如果目标存储器单元被激活,则可以通过与非串206建立电流流动,从而允许对所述目标存储器单元的数据状态进行读出。作为一个实例,电压电平454可以为大约5v。

[0057]

在时间t4处,可以将施加到所选存取线202

n

的电压电平增加到电压电平4321,同时可以维持其它迹线442和444的电压电平。电压电平4321可以表示旨在区分目标存储器单元的不同的可能数据状态的不同的读出电压。如本领域中众所周知的,当电压电平4321被施加到存取线202

n

时,可以在时间t5处执行对数据线的状态进行读出以确定目标存储器单元是否被激活。作为一个实例,电压电平4321可以对应于读出电压,所述读出电压旨在确定如果存储器单元在预充电阶段之后响应于电压电平4321而首次被激活,则所述存储器单元具有l1数据状态。

[0058]

在时间t6处,可以将施加到所选存取线202

n

的电压电平增加到电压电平4322,同时可以维持其它迹线442和444的电压电平。电压电平4322可以表示旨在区分目标存储器单元的不同的可能数据状态的不同的读出电压。如本领域中众所周知的,当电压电平4322被施加到存取线202

n

时,可以在时间t7处执行对数据线的状态进行读出以确定目标存储器单元是否被激活。作为一个实例,电压电平4322可以对应于读出电压,所述读出电压旨在确定如果存储器单元在预充电阶段之后响应于电压电平4322而首次被激活,则所述存储器单元具有l2数据状态。响应于读出电压432

0-4322中的任一读出电压而未被激活的存储器单元可以被视为具有数据状态l3。

[0059]

虽然图4中仅描绘了四个读出电压,但是可以使用其它数量的读出电压。通常,z读出电压可以用于区分z+1个可能数据状态中的每个数据状态。在时间t8处,可以根据实施例对存取线和选择线进行放电。

[0060]

图5描绘了用于与各个实施例一起使用的操作存储器的方法的定时图。例如,图5可以总体上描绘根据一个实施例的处于编程操作的各个阶段的存储器单元阵列的各个节

点的波形。

[0061]

在图5中,迹线572可以表示施加到连接到被选择用于进行编程操作的存储器单元(例如,被选择用于在编程操作期间进行编程的目标存储器单元)的存取线的电压电平,而迹线574可以表示施加到含有被选择用于在编程操作期间进行编程的存储器单元的串联连接存储器单元串的不同存取线(例如,未选择的存取线)的电压电平。以下讨论将至少参考图3进行并且将假定被选择用于进行编程操作的存储器单元是与非串2060的存储器单元208

n

,使得迹线572可以表示施加到存取线202

n

的电压电平,并且迹线574可以表示施加到未选择的存取线202(例如,存取线202

d0-202

d1

、202

0-202

n-1

、202

n+1-202

y

和202

d2-202

d3

)中的一或多条存取线的电压电平。

[0062]

迹线576可以表示施加到在编程操作期间选择性地连接到被选择用于进行编程的存储器单元的数据线(例如,所选数据线)的电压电平,例如,迹线576可以表示施加到数据线2040的电压电平。迹线578可以表示施加到在编程操作期间选择性地连接到未被选择用于进行编程的与所选存取线连接的存储器单元的数据线(例如,未选择的数据线)的电压电平,例如,迹线578可以表示施加到数据线2041的电压电平。

[0063]

在时间t0之前,迹线574可以具有初始电压电平560,如参考电位、接地或vss。可替代地或另外,迹线574的未选择的存取线可以具有高于电压电平560的初始电压电平562。迹线576和578可以各自具有用作抑制电压(如vcc)的初始电压电平568。电压电平568可以被配置成抑制对连接到所选存取线202并且选择性地连接到接收电压电平568的数据线204的存储器单元进行编程。进一步地,在时间t0处,可以将迹线576减小到电压电平560,所述电压电平可以对应于启用电压,所述启用电压被配置成启用对连接到所选存取线202并且选择性地连接到接收电压电平560的数据线204的存储器单元进行编程。

[0064]

在时间t1处,可以将迹线572和574增加到电压电平566。电压电平566可以对应于通过电压,所述通过电压被配置成无论存取线202的数据状态如何都激活连接到所述存取线的存储器单元。在时间t2处,可以将迹线572增加到电压电平570。电压电平570可以对应于编程电压,所述编程电压被配置成使连接到所选存取线并且选择性地连接到接收启用电压的所选数据线的存储器单元的阈值电压变化(例如,增加)。在时间t3处,可以维持迹线572处于电压电平570持续足以影响阈值电压变化的时间段。迹线572在时间t3与时间t4之间的部分可以被称为编程操作的编程脉冲。在时间t4处,可以使迹线572放电到电压电平560。还可以使迹线574放电到电压电平560。在时间t5处,还可以使迹线578放电到电压电平560。在时间t5之后,可以执行例如参考图4所描述的编程验证操作。

[0065]

各个实施例寻求使存取线放电到各种电压电平以促进例如在编程验证操作之后和在随后的编程脉冲之前将电子保留在受害者存储器单元的沟道区域中。图6是根据一个实施例的操作存储器的方法的流程图。

[0066]

在601处,可以对串联连接存储器单元串的特定存储器单元(例如,所选存储器单元或目标存储器单元)执行读出操作,其中串联连接存储器单元串的每个存储器单元连接到多条存取线中的相应存取线。例如,参考图3,特定存储器单元可以是与非串2060的连接到存取线202

n

的存储器单元208

n

。读出操作可以是例如参考图3所描述的编程验证操作。

[0067]

在603处,例如,在完成读出操作之后,可以使所述多条存取线中用于串联连接存储器单元串的第二存储器单元(例如,未选择的存储器单元)的相应存取线放电到第一电压

电平。例如,第一电压电平可以是参考电位。作为另外一个实例,第二存储器单元可以是存储器单元208中位于与非串2060的特定存储器单元与第一端(例如,源极侧或最靠近源极216的端)之间的任何存储器单元,例如,与非串2060的分别连接到存取线202

0-202

n-1

的存储器单元208

0-208

n-1

中的任何存储器单元。603处的放电可以从用于读出操作的电压电平开始。可替代地,603处的放电可以从中间电压电平(如用于读出操作的电压电平与第一电压电平之间的电压电平)开始。

[0068]

在605处,可以使所述多条存取线中用于特定存储器单元的相应存取线放电到高于第一电压电平的第二电压电平。例如,第二电压电平可以是在编程验证操作之后的电压电平与第一电压电平之间的电压电平。作为一个实例,第二电压电平可以为3v。作为另外一个实例,第二电压电平可以高于在读出操作期间使用的编程验证电压和参考电位的平均值。

[0069]

605处的放电可以在603处的放电开始时的时间处开始。可替代地,605处的放电可以在603处的放电开始时的时间之后的时间处开始。605处的放电可以进一步在603处的放电达到第一电压电平时的时间之前的时间处开始。605处的放电可以从用于读出操作的电压电平开始。可替代地,605处的放电可以从中间电压电平(如用于读出操作的电压电平与第二电压电平之间的电压电平)开始。

[0070]

在607处,可以使所述多条存取线中用于串联连接存储器单元串的第三存储器单元(例如,未选择的存储器单元)的相应存取线放电到低于第二电压电平并且高于第一电压电平的第三电压电平。作为一个实例,第三电压电平可以为2v。作为另外一个实例,第三电压电平可以低于在读出操作期间使用的编程验证电压和参考电位的平均值。第三存储器单元可以是存储器单元208中邻近(例如,紧邻)特定存储器单元并且位于与非串2060的特定存储器单元与第二端(例如,漏极侧或最靠近数据线204的端)之间的一或多个存储器单元(例如,与非串2060的分别连接到存取线202

n+1

或更高的存储器单元208

n+1

或更高中的一或多个)中的任何存储器单元208。

[0071]

607处的放电可以在603处的放电开始时的时间处开始。可替代地,607处的放电可以在605处的放电开始时的时间之后的时间处开始。607处的放电可以进一步在605处的放电达到第二电压电平时的时间之前的时间处开始。607处的放电可以从用于读出操作的电压电平开始。可替代地,607处的放电可以从中间电压电平(如用于读出操作的电压电平与第三电压电平之间的电压电平)开始。

[0072]

在609处,可以任选地向所述多条存取线中用于特定存储器单元的相应存取线施加编程脉冲,而不使所述多条存取线中用于特定存储器单元的相应存取线放电到第一电压电平,并且不使所述多条存取线中用于第三存储器单元的相应存取线放电到第一电压电平。例如,可以将用于特定存储器单元的相应存取线的电压电平直接从第二电压电平增加到通过电压,同时可以将用于第三存储器单元的相应存取线的电压电平直接从第三电压电平增加到通过电压。

[0073]

使特定存储器单元的串联连接存储器单元串的特定存储器单元与一端之间的一或多条存取线放电到第一电压电平、使连接到特定存储器单元的存取线放电到高于第一电压电平的第二电压电平和使特定存储器单元的串联连接存储器单元串的特定存储器单元与另一端之间的一或多条存取线放电到低于第二电压电平并且高于第一电压电平的第三

电压电平可以促进将电子保留在连接到与特定存储器单元的存取线相同的存取线的受害者存储器单元的沟道区域中。这可以通过减轻可以造成热电子生成的升压峰值并且进一步促进对此类局部升压的强度的控制来促进减轻在随后的编程脉冲期间对受害者存储器单元的编程干扰。

[0074]

对于一些实施例,可以使特定存储器单元的串联连接存储器单元串的特定存储器单元与另一端之间的另外存取线放电到除第三电压电平之外但也低于第二电压电平并且高于第一电压电平的电压电平。

[0075]

图7a-7b是根据另一个实施例的操作存储器的方法的流程图。在711处,可以对串联连接存储器单元串的特定存储器单元(例如,所选存储器单元或目标存储器单元)执行读出操作,其中串联连接存储器单元串的每个存储器单元连接到多条存取线中的相应存取线。例如,参考图3,特定存储器单元可以是与非串2060的连接到存取线202

n

的存储器单元208

n

。读出操作可以是例如参考图3所描述的编程验证操作。

[0076]

在713处,例如,在完成读出操作之后,可以使所述多条存取线中用于串联连接存储器单元串的第一存储器单元(例如,未选择的存储器单元)子集的相应存取线放电到第一电压电平。例如,第一电压电平可以是参考电位。第一存储器单元子集的每个存储器单元可以位于串联连接存储器单元串的特定存储器单元与第一端之间。第一存储器单元子集可以是连续多个存储器单元。

[0077]

作为实例,第一存储器单元(例如,未选择的存储器装置)子集可以是与非串2060的特定存储器单元与最靠近第一端(例如,源极侧或最靠近源极216的端)的虚设存储器单元之间的多个存储器单元208,例如,与非串2060的分别连接到存取线202

0-202

n-2

的存储器单元208

0-208

n-2

。713处的放电可以从用于读出操作的电压电平(例如,通过电压)开始。可替代地,713处的放电可以从中间电压电平(如用于读出操作的电压电平与第一电压电平之间的电压电平)开始。

[0078]

在715处,可以使所述多条存取线中用于串联连接存储器单元串的第二存储器单元(例如,未选择的存储器单元)子集的相应存取线放电到第一电压电平。第二存储器单元子集的每个存储器单元可以位于特定存储器单元与第一存储器单元子集之间。例如,第二存储器单元子集可以是存储器单元208中的特定存储器单元与第一存储器单元子集之间的一或多个存储器单元,例如,与非串2060的连接到存取线202

n-1

的存储器单元208

n-1

。第二存储器单元子集可以是连续多个存储器单元。

[0079]

715处的放电可以在713处的放电开始时的时间之后的时间处开始。715处的放电可以进一步在713处的放电达到第一电压电平时的时间之前的时间处开始。715处的放电可以从用于读出操作的电压电平(例如,通过电压)开始。可替代地,713处的放电可以从中间电压电平(如用于读出操作的电压电平与第一电压电平之间的电压电平)开始。

[0080]

在717处,可以使所述多条存取线中用于特定存储器单元的相应存取线放电到高于第一电压电平的第二电压电平。例如,第二电压电平可以是在编程验证操作之后的电压电平(或中间电压)与第一电压电平之间的电压电平。作为一个实例,第二电压电平可以为3v。

[0081]

717处的放电可以在715处的放电开始时的时间之后的时间处开始。717处的放电可以进一步在715处的放电达到第一电压电平时的时间之前的时间处开始。717处的放电可

以从用于读出操作的电压电平(例如,编程验证电压)开始。可替代地,717处的放电可以从中间电压电平(如用于读出操作的电压电平与第二电压电平之间的电压电平)开始。

[0082]

在719处,可以使所述多条存取线中用于串联连接存储器单元串的第三存储器单元(例如,未选择的存储器单元)子集的相应存取线放电到低于第二电压电平并且高于第一电压电平的第三电压电平。第三存储器单元子集的每个存储器单元可以位于与非串2060的特定存储器单元与第二端(例如,漏极侧或最靠近数据线204的端)之间,例如,与非串2060的分别连接到存取线202

n+1

或更高的存取线的存储器单元208

n+1

或更高的存储器单元中的一或多个存储器单元。第三存储器单元子集可以邻近(例如,紧邻)特定存储器单元。例如,第三存储器单元子集可以是存储器单元208中的与非串2060的特定存储器单元与第二端之间的一或多个存储器单元,例如,与非串2060的连接到存取线202

n+1-202

n+2

的存储器单元208

n+1-208

n+2

。第三存储器单元子集可以是连续多个存储器单元。

[0083]

719处的放电可以在717处的放电开始时的时间之后的时间处开始。719处的放电可以进一步在717处的放电达到第二电压电平时的时间之前的时间处开始。719处的放电可以从用于读出操作的电压电平(例如,通过电压)开始。可替代地,719处的放电可以从中间电压电平(如用于读出操作的电压电平与第三电压电平之间的电压电平)开始。

[0084]

在721处,可以使所述多条存取线中用于串联连接存储器单元串的第四存储器单元(例如,未选择的存储器单元)子集的相应存取线放电到第一电压电平。第四存储器单元子集的每个存储器单元可以位于串联连接存储器单元串的第三存储器单元子集与第二端之间。作为实例,第四存储器单元子集可以是存储器单元208中位于与非串2060的第三存储器单元子集与最靠近第二端的虚设存储器单元之间的多个存储器单元,例如,与非串2060的分别连接到存取线202

n+3-202

y

的存储器单元208

n+3-208

y

。第四存储器单元子集可以是连续多个存储器单元。

[0085]

721处的放电可以在719处的放电开始时的时间之后的时间处开始。可替代地,721处的放电可以在与719处的放电同时开始。721处的放电可以进一步在719处的放电达到第三电压电平时的时间之前的时间处开始。721处的放电可以从用于读出操作的电压电平(例如,通过电压)开始。可替代地,721处的放电可以从中间电压电平(如用于读出操作的电压电平与第三电压电平之间的电压电平)开始。

[0086]

在723处,可以使所述多条存取线中用于串联连接存储器单元串的第五存储器单元(例如,未选择的边缘虚设存储器单元)子集的相应存取线放电到第一电压电平。第五存储器单元子集的第一存储器单元可以位于串联连接存储器单元串的第一存储器单元子集与第一端之间,例如,与非串2060的分别连接到存取线202

d0-202

d1

的存储器单元208

d0-208

d1

中的一或多个存储器单元,和/或第五存储器单元子集的第二存储器单元可以位于串联连接存储器单元串的第四存储器单元子集与第二端之间,例如,与非串2060的分别连接到存取线202

d2-202

d3

的存储器单元208

d2-208

d3

中的一或多个存储器单元。例如,第五存储器单元子集可以是与非串2060的分别连接到存取线202

d0-202

d3

的存储器单元208

d0-208

d3

中的每个存储器单元。第五存储器单元子集可以包含一个以上的连续多个存储器单元。

[0087]

723处的放电可以在719和/或721处的放电开始时的时间之后的时间处开始。723处的放电可以进一步在719处的放电达到第三电压电平时的时间之前的时间处和/或在721处的放电达到第一电压电平时的时间之前的时间处开始。723处的放电可以从用于读出操

作的电压电平(例如,通过电压)开始。可替代地,723处的放电可以从中间电压电平(如用于读出操作的电压电平与第一电压电平之间的电压电平)开始。

[0088]

在725处,可以任选地向所述多条存取线中用于特定存储器单元的相应存取线施加编程脉冲,而不使所述多条存取线中用于特定存储器单元的相应存取线放电到第一电压电平,并且不使所述多条存取线中用于第三存储器单元的相应存取线放电到第一电压电平。例如,在随后的编程脉冲之前,可以将用于特定存储器单元的相应存取线的电压电平直接从第二电压电平增加到通过电压,同时可以将用于第三存储器单元子集的相应存取线的电压电平直接从第三电压电平增加到通过电压。

[0089]

对于一些实施例,可以使对应于第三存储器单元子集的存取线与对应于第四存储器单元子集的存取线之间的另外存取线放电到低于第三电压电平并且高于第一电压电平的其它电压电平。对于一些实施例,可以针对每个此类较低电压电平使此类另外存取线按顺序放电。例如,在719处放电之后,可以使所述多条存取线中用于串联连接存储器单元串的第六存储器单元(例如,未选择的存储器单元)子集的相应存取线放电到低于第三电压电平并且高于第一电压电平的第四电压电平。第六存储器单元子集的每个存储器单元可以位于第三存储器单元子集与第四存储器单元子集之间。对另外存取线(例如,最后一个另外存取线子集)进行的此类放电可以与721处的放电同时开始。各个存储器单元子集可以相互排斥,并且可以与特定存储器单元一起共同表示串联连接存储器单元串的每个存储器单元。

[0090]

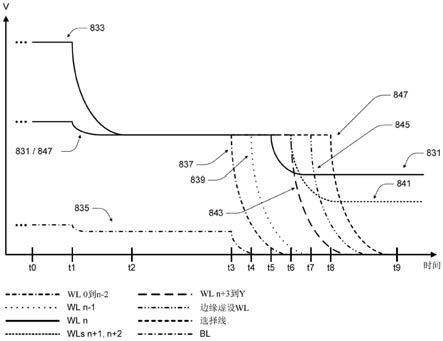

图8描绘了根据另外的实施例的操作存储器的方法的定时图。例如,图8可以描绘如参考图7a-7b所描述的方法的定时图。

[0091]

在图8中,迹线831可以表示施加到连接到被选择用于进行先前的读出操作或随后的编程操作的存储器单元208(例如,目标存储器单元)的存取线202的电压电平。以下讨论将至少参考图3进行并且将假定目标存储器单元是与非串2060的存储器单元208

n

,使得迹线831可以表示施加到存取线202

n

的电压电平。因为存取线202

n

含有目标存储器单元,所以所述存储线可以被称为所选存取线,而剩余存取线202可以被称为未选择的存取线。因为与非串2060含有目标存储器单元,所以所述与非串可以被称为所选串联连接存储器单元串。因为与非串2061可以不含有已经对其进行了读出操作的存储器单元,所以所述与非串可以被称为未选择的串联连接存储器单元串。与非串2061还可以含有受害者存储器单元,例如与非串2061的存储器单元208

n

。

[0092]

迹线833可以表示施加到未选择的存取线202(例如,存取线202

d0-202

d1

、202

0-202

n-1

、202

n+1-202

y

和202

d2-202

d3

)的电压电平。迹线835可以表示施加到数据线204(例如,选择性地连接到与非串2061的受害者存储器单元208

n

的未选择的数据线2041)的电压电平。迹线837可以表示施加到未选择的存取线202

0-202

n-2

的电压电平。迹线839可以表示施加到未选择的存取线202

n-1

的电压电平。迹线841可以表示施加到未选择的存取线202

n+1

和202

n+2

的电压电平。迹线843可以表示施加到未选择的存取线202

n+3-202

y

的电压电平。迹线845可以表示施加到未选择的存取线202

d0-202

d3

的电压电平。迹线847可以表示施加到选择线214和215的电压电平。

[0093]

在时间t0处,迹线831可以具有例如与在编程验证操作期间在所选存取线上使用的(例如,最后使用的)编程验证电压相对应并且与在编程验证操作期间施加到选择线的电压电平相对应的电压电平。作为一个实例,迹线831在时间t0处的电压电平可以为5v。类似

地,迹线833可以具有例如与在编程验证操作期间在未选择的存取线上使用的通过电压相对应的电压电平。作为一个实例,迹线833在时间t0处的电压电平可以为8v。另外,迹线835可以具有例如与在编程验证操作期间在数据线上使用的电压相对应的电压电平。作为一个实例,迹线835在时间t0处的电压电平可以为1v。

[0094]

在时间t1处,可以使迹线831和833放电到低于在编程验证操作期间使用的电压电平的中间电压电平。迹线831的中间电压电平可以是与迹线833的中间电压电平相同的电压电平。另外,在时间t1处,可以使迹线835放电到中间电压电平。

[0095]

在时间t2处,迹线831、833和835可能已经达到其相应的中间电压电平。作为一个实例,在时间t2处,迹线831和833的中间电压电平可以为4.5v,并且迹线835的中间电压电平可以为0.8v。

[0096]

在时间t3处,可以使迹线837放电到可以为0v或接地的第一电压电平,例如,参考电位。注意,对电压电平的放电通常不是瞬时的并且可以如图8所描绘的在某一时间段内衰减到其预期的电压电平。类似地,可以使迹线835放电到第一电压电平。在时间t4处,可以使迹线839放电到参考电位。在时间t5处,可以使迹线831放电到高于第一电压电平的第二电压电平。在时间t6处,可以使迹线和841放电到低于第二电压电平并且高于第一电压电平的第三电压电平。而且,在时间t6处,可以使迹线843放电到第一电压电平。在时间t7处,可以使迹线845放电到第一电压电平。在时间t8处,可以使迹线847放电到第一电压电平。在时间t9处,迹线831可以处于第二电压电平,迹线841可以处于第三电压电平,并且剩余迹线可以处于第一电压电平。然后,可以施加随后的编程脉冲,而不使迹线831和841从其相应的电压电平放电,例如,迹线831从第二电压电平增加到通过电压,迹线841从第三电压电平增加到通过电压,并且剩余的未选择的存取线从第一电压电平增加到通过电压。

[0097]

结论

[0098]

虽然已经在本文中说明和描述了具体实施例,但本领域的普通技术人员应了解,旨在实现相同目的的任何布置可以替代所示出的具体实施例。对本领域的普通技术人员而言,实施例的许多改动将是显而易见的。因此,本申请旨在涵盖实施例的任何改动或者变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1