可程式化电阻式装置存储器及用于该存储器的方法与流程

[0001]

本发明是有关于一种用于将可程式化电阻式装置中的电阻转换为逻辑状态的感测电路;可程式化电阻式装置(programmable resistive device,或prd)存储器为一次性可程式化(one-time programmable,或otp)存储器、多次可程式化(mtp)存储器、相变随机存取存储器(pcram)、铁电随机存取存储器(feram)、电阻式随机存取存储器(rram)及磁性随机存取存储器(mram)等等。

背景技术:

[0002]

可程式化电阻式装置(prd)通常是指其电阻可以通过程式化的手段来改变的装置。电阻状态也可以由电阻值确定;例如,可程式化电阻式装置可以是一次性可程式化(otp)装置,例如电熔丝(或反熔丝),并且程式化的手段可以施加高电压以感应大电流流过otp元件;当大电流流过otp元件时(例如,通过导通选择器),可对otp元件进行程式化,或者烧录成高电阻状态或低电阻状态(取决于熔丝或反熔丝)。

[0003]

图1示出了具有可程式化电阻式元件(programmable resistive element,或pre)11和选择器12的一般的可程式化电阻式装置(prd)10的示意图。pre 11可以是电熔丝、反熔丝、悬浮闸极装置、相变材料、电阻式ram元件或磁性穿隧接面(mtj)等等。选择器12可以是mos、二极管、mos/二极管合并,或甚至是通过施加一信号sel而导通或断开的双极性装置。

[0004]

在读取prd胞(cell)之后,需要将prd装置中的pre的电阻转换为逻辑准位;这可以通过使用一感测电路或感测放大器(sense amplifier,或sa)来实现。感测pre电阻的一般的方法是通过施加流经pre的电流将电阻值转换为电压,然后使用一电压放大器以放大电压信号;这种方式取决于mos装置的放大,而此mos装置通常需要使用消耗大量电流才能获得高增益的高电压以完全地偏压。

[0005]

图2是一般的感测放大器20的示意图。sa 20具有pmos 21,pmos 21的闸极耦合至汲极;pmos 21的闸极也耦合到pmos 22的闸极;pmos 21的源极和pmos 22的源极耦合到电源电压vdd;pmos 21的汲极和pmos 22的汲极分别耦合到nmos 23的汲极和nmos 24的汲极;nmos 23的闸极和nmos 24的闸极分别耦合到差动输入信号vp和差动输入信号vn;nmos 23的源极和nmos 24的源极耦合到nmos 26的汲极,nmos 26的闸极耦合到致能信号ψ,并且nmos 26的源极耦合到地。介于vp和vn之间的输入差动电压可以被放大到输出端vout(在pmos 22的汲极)。当断开nmos 26以禁用sa时,藉由nmos 27将vout保持为高准位。

[0006]

图3是另一种一般的电压感测放大器30的示意图。图3的方式是将在一锁存器中的mos装置偏压到高增益区域中,然后进行锁存。在高增益区域中偏压mos通常需要大量电流,并且需要在高电压下操作。pmos 31的源极耦合到电源电压vdd,pmos 31的汲极耦合到nmos 33的汲极,nmos 33的源极耦合到另一个nmos 35的汲极,nmos 33的闸极耦合到输入电压v+,nmos 35的闸极耦合到pmos 31的闸极。还有另一类似的具有pmos 32的分支,pmos 32的源极耦合到电源电压vdd,pmos 32的闸极耦合到pmos 31的汲极,pmos 32的汲极耦合到nmos 34的汲极,nmos 34的源极耦合到另一个nmos 36的汲极,nmos 34的闸极耦合到另一

个输入电压v-,nmos 36的闸极耦合到pmos 32的闸极。四个装置pmos 31、nmos 35、pmos 32和nmos 36像两个交叉耦合的反向器一样互连,即pmos 31的闸极和nmos 35的闸极耦合到pmos 32的汲极,pmos 32的闸极和nmos 36的闸极耦合到pmos 31的汲极,nmos 35的源极和nmos 36的源极耦合到nmos 39的汲极,nmos 39的闸极耦合到致能信号ψ,nmos 39的源极耦合到地。通过接通该致能信号ψ,可以将v+和v-的输入差动信号分别放大到vn和vp。反向器37和反向器38进一步缓冲内部节点vn和vp以分别输出vout+和vout-。当藉由断开nmos 39以禁用该感测放大器时,装置40将vn和vp保持为vdd。在此实施例中,输入装置33和34被放置在三个mos装置堆叠的中间。在其他实施例中,输入装置33和34可以放置在mos堆叠的顶部或底部。还有在其他实施例中,通过直接用参考及胞电阻分别取代nmos 33和nmos 34以感测。

[0007]

图2或图3中的电压感测的一般方法取决于电源电压vdd和mos门槛值电压vtn和vtp,以在通常需要一些电流的高增益区域中偏压mos装置。如果电源电压为0.8伏特,并且vtn和|vtp|大约为0.3伏特,则仅用0.4伏特来感测prd对于mos处于高增益区域将是非常困难的。即使电压感测放大器能够工作,在高增益区域中的mos偏压电流也将相当高,以使感测放大器(sa)工作;这样做至少需要100ua,而实现1ua的感测电流是几乎是不可能的。在物联网应用中,有一些要求仅使用0.4伏特电压和1ua电流来感测可程式化电阻式装置,而标称电源电压为0.8伏特。

[0008]

通过转换为电压来感测电阻的一般方法需要高电源电压和高电流。但是,半导体行业的趋势是使用低电源电压和低电流消耗,尤其是在pc、平板电脑、智能手机、可携式和iot应用中;因此,将持续需要改进的方法以在低电压和低电流的条件下仍然可以感测可程式化电阻式存储器胞的电阻。

技术实现要素:

[0009]

本文公开了在低电源电压下以低电流感测可程式化电阻式装置胞的实施例。低电压和低电流感测的方法和电路可用于任何种类的可程式化电阻式存储器,例如一次性可程式化(otp)存储器、多次可程式化(mtp)存储器、相变随机存取存储器(pcram)、电阻式随机存取存储器(rram)、铁电随机存取存储器(feram)及磁性随机存取存储器(mram)等等。本文公开的一个或多个实施例可包含或利用将可程式化电阻式装置的感测电阻转换为逻辑状态的技术和电路。

[0010]

在一实施例中,一电容可以在第一时间段期间被充电到接近电源电压准位。然后,该电容可以在第二时间段内通过电阻放电。可以将在放电电容的电压与一参考电压进行比较,以改变一存储器读取输出。一输出逻辑装置(例如比较装置)改变其输出的时间由电阻和电容的乘积所决定。由于电容是已知的或为可知的,因此该输出逻辑装置改变输出的时间与电阻值有关。因此,可以通过自放电开始以来的时间延迟来判断电阻;时间延迟越长,则电阻越大。在一种实施方式中,mos装置仅为用于导通或断开以进行充电或放电的开关,而不是一个放大器。因此,在这种基于时间的感测结构中,mos装置的门槛值电压不是至关重要的。

[0011]

本发明可以以多种方式实现,包含作为方法、系统、装置或设备(包含电脑可读取媒体)。下面讨论本发明的几个实施例。

[0012]

作为一可程式化电阻式存储器,一个实施例可以例如至少包含多个可程式化电阻式装置(prd)胞。该些prd胞中的至少一个可以至少包含一选择器、一可程式化电阻式元件(pre)及一逻辑装置;该选择器由一控制信号所控制,该选择器至少具有一第一端和一第二端,该第二端耦合到一第一导线;该pre的一第一端耦合到一电容,该pre的一第二端耦合到该选择器的该第一端;该逻辑装置可耦合在该pre的该第一端和该电容之间以作为一开关或一多工器。该电容的充电/放电率可用于判断该pre的逻辑状态。

[0013]

作为一电子系统,一个实施例可以例如至少包含一处理器以及可操作地连接到该处理器的一可程式化电阻式存储器。该可程式化电阻式存储器可以至少包含用于提供数据储存的多个可程式化电阻式装置(prd)胞,该些prd胞的每一个可以至少包含一选择器、一可程式化电阻式元件(pre)及一逻辑装置;该选择器由一控制信号所控制,该选择器具有一第一端和一第二端,该第二端耦合到一第一导线;该pre的一第一端耦合到一电容,该pre的一第二端耦合到该选择器的该第一端;该逻辑装置可耦合在该pre的该第一端和该电容之间以作为一开关或一多工器。该电容的充电/放电率可用于判断该pre的逻辑状态。

[0014]

作为一种用于提供包含多个可程式化电阻式装置胞和至少一电容的可程式化电阻式存储器的方法,该些可程式化电阻式装置胞中的至少一个包含至少一可程式化电阻式元件。一实施例可以例如至少包含:对电容充电,停止充电,接着将该可程式化电阻式元件耦合到电容,在该可程式化电阻式元件保持耦合到电容的同时监测电容的放电率,根据放电率的监测判断该可程式化电阻式元件的电阻值,根据所判断的该可程式化电阻式元件的电阻值判断该些可程式化电阻式装置胞中的至少一个的逻辑状态。

[0015]

以下结合附图和具体实施例对本发明进行详细描述,但不作为对本发明的限定。

附图说明

[0016]

通过以下详细描述并结合附图,将容易地理解本发明,其中相同的附图标记表示相似的结构元件,其中:

[0017]

图1示出了一般的可程式化电阻式存储器装置的示意图。

[0018]

图2示出了一般的电压感测放大器的示意图。

[0019]

图3示出了另一种一般的电压感测放大器的示意图。

[0020]

图4(a)示出了根据一实施例的低功率感测电路的示意图。

[0021]

图4(b)示出了根据一实施例的被放电的电压和比较器输出的时序波形。

[0022]

图5(a)示出了根据一实施例的基于时间的感测电路的示意图。

[0023]

图5(b)示出了根据一实施例的在一个胞单元和一个参考单元中的电容放电电压的时序波形。

[0024]

图5(c1)示出了根据一实施例的使用至少一参考行的利用基于时间感测的一pre存储器的一部分的示意图。

[0025]

图5(c2)示出了根据另一实施例的使用至少一参考行的利用基于时间感测的一pre存储器的一部分的示意图。

[0026]

图5(d)示出了根据另一实施例的使用参考列的利用基于时间感测的一pre存储器的一部分的示意图。

[0027]

图5(e)示出了利用自定时电路进行预充电和放电的一pre存储器的一部分的示意

图。

[0028]

图6是根据一实施例的将电阻转换为时间的方法的流程图。

[0029]

图7是根据一实施例的基于时间的电阻感测的方法的流程图。

[0030]

图8示出了根据一实施例的具有至少一使用低电压和低电流感测电路的可程式化电阻式存储器的处理器系统。

具体实施方式

[0031]

下面结合附图和具体实施例对本发明技术方案进行详细的描述,以更进一步了解本发明的目的、方案及功效,但并非作为本发明所附权利要求保护范围的限制。

[0032]

本文公开的实施例使用通过可程式化电阻式元件(pre)放电的电容来评估程式化状态。通过比较达到一预定电压的一放电时间,可以将pre的电阻转换成逻辑状态。可以将放电时间与使用一参考电阻的一独立单元所提供的放电时间进行比较。

[0033]

该可程式化电阻式元件及一感测电路可以被包含在一可程式化电阻式装置(prd)存储器中。可选地,该可程式化电阻式元件及该感测电路可以被包含在一电子系统内。

[0034]

该prd可以是一个一次性可程式化(otp)装置,例如电熔丝(或反熔丝)。流过otp元件的电流(例如,通过导通一选择器)可以对该otp元件进行程式化,或者可以将该otp元件烧录成高电阻状态或低电阻状态(取决于熔丝或反熔丝)。电熔丝可以是一个互连熔丝或触点/通孔熔丝;互连熔丝可以由金属氧化物半导体(mos)闸极、多晶硅、硅化物、硅化的多晶硅、金属、金属合金、局部互连、mos闸极或热隔离主动区制成;触点或通孔熔丝可以由单个或多个触点或通孔制成,以进行程式化。可以通过击穿导体之间的mos氧化物或介电质来制成反熔丝。该prd也可以是其他类型的存储器装置,例如多次可程式化(mtp)存储器、相变随机存取存储器(pcram)、电阻式随机存取存储器(rram)、铁电随机存取存储器(feram)及磁性随机存取存储器(mram)等等,可进行多次的程式化。

[0035]

在这感测电路中的任何mos装置均作为开关。因此,与电源电压相关的mos装置的门槛值电压对于电路的操作来说不是至关重要的。因此,可以在标准的cmos逻辑制程中实现低电压和低电流感测,而无需额外的遮罩或制程步骤以节省成本。

[0036]

图4(a)示出了根据一实施例的低功率的感测电路50的一部分的示意图。感测电路50具有一开关52,该开关52耦合到一电源电压vdd并且通过一电容51接地。该电容51耦合到一开关54,然后耦合到接地的一电阻式装置53。可以通过接通该开关52并断开该开关54来将该电容51充电至vdd。在该电容51充满电之后,可以通过接通该开关54并断开该开关52来使该电容51放电。因此,在该电容51的节点a的电压可以根据一rc时间常数放电至地。该rc时间常数取决于电阻(r)和电容(c)的乘积。由于该电容51的该电容(c)可以固定,所以放电率将取决于该电阻式装置53的电阻(r)。

[0037]

图4(b)示出了根据一实施例的在节点b的电压被放电的时序波形。如果该电阻式装置53的电阻具有比一参考电阻大的电阻,则放电曲线看起来像62。相反地,如果该电阻式装置53的电阻具有比该参考电阻小的电阻,则放电曲线看起来像61。如果一半的vdd(vdd/2)是预定电压,则曲线61和曲线62达到该预定电压的时间延迟ts和tl如图4(b)所示,分别为逻辑波形63和逻辑波形64。电阻越大,则时间延迟越长。换句话说,该感测电路50将电阻转换为时间,如图4(b)所示。如果将一比较器(未示出)耦合到节点b,则在分别经过延迟时

间ts和tl之后,在比较之后的曲线61的放电波形和曲线62的放电波形可以分别升高为vdd以作为逻辑波形63和逻辑波形64。通过将该些延迟时间ts和tl与一参考延迟时间进行比较,可以判断该电阻式装置53的电阻。

[0038]

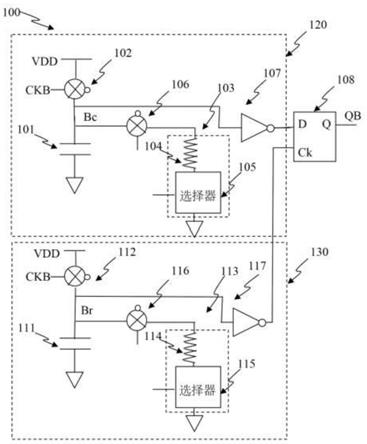

图5(a)示出了根据一实施例的基于时间的感测电路100的示意图的一部分。基于时间的感测电路100具有一个胞单元120和一参考单元130。该胞单元120具有一电容101,该电容101通过一充电通道闸102耦合至一电源电压vdd并耦合至地。该电容101还耦合到一放电通道闸106。该放电通道闸106耦合到一可程式化电阻式装置103。该可程式化电阻式装置103包含与一选择器105串联耦合的一可程式化电阻式元件104,该选择器105偶接至地。放电电容101还耦合到一反向器107,该反向器107可以用为一比较器或逻辑状态转换器。

[0039]

该参考单元130具有一电容111,该电容111通过一充电通道闸112耦合到电源电压vdd并且耦合到地。该电容111还耦合到一放电通道闸116。该放电通道闸116耦合到一参考装置113。该参考装置113包含一参考元件114,该参考元件114与耦合到地的一选择器115串联耦合。该电容111还耦合到一反向器117,该反向器117可以用为一比较器或逻辑状态转换器。该反向器107的输出和该反向器117的输出可以分别耦合到一锁存器(或正反器)108的一输入端和一致能端。该锁存器(或正反器)108的输出端qb可以表示该pre104相对于该参考元件114的逻辑状态。

[0040]

基于时间的感测电路的操作可以进一步详述如下。该胞单元120包含该电容101,并且该参考单元130包含该电容111。该电容101和该电容111通常具有相同的电容值c。该电容101和该电容111可以在施加ckb的情况下被充电至接近vdd,其中所述在施加ckb的情况下指的是导通该充电通道闸102和该充电通道闸112而断开该放电通道闸106和该放电通道闸116。当该电容101和该电容111几乎充满电时,该充电通道闸102和该充电通道闸112可以被断开,而该放电通道闸106和该放电通道闸116以及该选择器105和该选择器115可以被接通。接着,该电容101和该电容111将通过该pre 104的电阻和该参考元件114的电阻分别地放电。该电容101和该电容111还分别耦合到该反向器107和该反向器117,而该反向器107和该反向器117用作逻辑比较器以产生逻辑状态。在放电之前,作为比较器的该反向器107的输出和该反向器117的输出均为0。当该电容电压在该反向器107和该反向器117的跳变点以下放电时,该反向器107的输出和该反向器117的输出将独立地变为1。如果该反向器117的输出变为1,则该锁存器(或正反器)108将被导通以锁存该反向器107的输出。如果在该胞单元120内的该pre 104的电阻小于该参考元件114的电阻,则输出端qb将为高,否则该锁存器(或正反器)108的输出端qb将为低。

[0041]

图5(b)示出了根据一实施例的分别在该胞单元120和该参考单元130中的节点bc和节点br的电容电压的时序波形200。曲线202示出了在该参考单元130中的该电容111的放电。当节点br的电压达到被设置为该反向器117的跳变点的一半的vdd(vdd/2)时,该反向器117的输出将变为高准位。然后,取决于在该胞单元120中的该pre 104的电阻是低于还是高于该参考元件114的电阻,该锁存器(或正反器)108可以分别针对曲线201或曲线203锁存数据1或0。波形211、波形212和波形213分别是曲线201、曲线202和曲线203的比较器输出。

[0042]

图5(c1)示出了根据本发明的一实施例的并入了基于时间的感测电路的一pre宏观的方块图500的一部分的示意图。方块图500具有多个pre胞510和一附加的参考行,该些pre胞510被组织为n列乘m行的阵列。每个pre胞510具有耦合至一选择器512的一pre元件

511。pre 510的一端作为在每一行中的位元线(bl)连接,并且耦合至y写入通道闸(ywpg)540,该y写入通道闸540进一步耦合至vddp以用于程式化。每条位元线还耦合到一个或多个的y读取通道闸(yrpg)530,以作为多工器连接到数据线(dl),然后每条dl耦合到一放电电容535和一比较器540。在另一实施例中,每条dl耦合到多个位元线。

[0043]

另外,在一参考行中有耦合到参考位元线(blr)的一个附加参考电阻551。普通行的比较器输出可以耦合到一锁存器550的输入d,而参考行的比较器输出可以耦合到该锁存器550的致能端e。可以有上拉pmos(未示出)在感测之前将dl0~dlm-1和dlr预充电至vdd。在感测期间,dl预充电被切断,yrpg和wl被导通,在dli(其中i=0、1、

…

、m-1)中的选定dl和dlr将分别通过pre元件511及该参考电阻551放电至地。当dl和dlr电压降到预定门槛值以下时,该比较器输出ci(其中i=0、1、

…

m-1)和cr将改变逻辑状态。cr可用作一锁存致能以锁存一个或多个ci(其中i=0、1、

…

、m-1),以判断该pre元件的电阻是大于还是小于该参考电阻。

[0044]

图5(c2)示出了根据另一实施例的并入了基于时间的感测电路的一pre宏观的方块图500”的一部分的示意图。方块图500”具有多个pre胞510”和一附加的参考行blr,该些pre胞510”被组织为n列乘m行的阵列。每个pre胞510”具有耦合到一选择器512”的一pre元件511”。在每一行中作为位元线(bl)连接的pre 510”的另一端耦合到y写入通道闸(ywpg)540”,该y写入通道闸540”进一步耦合到vddp以用于程式化。每条位元线还耦合到一个或多个y读取通道闸(yrpg)530”,以作为多工器连接到单个数据线(dl0)。在此实施例中,所有的位元线被多路复用到单个数据线(dl0)。另外,如果dl0电容足够大,则可以省略放电电容535”。在参考行blr中有一附加的参考电阻551”耦合到参考位元线。普通行的比较器输出耦合到一锁存器550”的输入d,而参考行的比较器输出耦合到锁存器550”的致能e。可以有上拉pmos(未显示)在感测之前将dl0和dlr预充电至vdd。在感测期间,dl0/dlr预充电被切断,yrpg 530”、参考yrpg 531”和wl被导通,并且选定的bli(其中i=0、1、

…

、m-1)和blr为通过pre元件511”和参考电阻551”分别放电到地。当dl0和dlr电压下降到预定门槛值以下时,比较器输出c0和比较器输出cr将改变逻辑状态。cr可用作锁存致能以锁存c0以判断该pre元件的电阻是大于还是小于该参考电阻。在一些实施例中,可以建立一虚拟参考电容536”以与该数据线电容535匹配。

[0045]

图5(c1)和5(c2)所示的基于时间的感测电路500和500”分别是自定时电路。例如,该参考行放置在最右边,使得在每条字元线(wl)中的该些参考胞将在最后导通。可以将虚拟yrpg 530”或参考yrpg 531”放置为与在普通位元线中的阻抗匹配,或作为多工器。在放电期间,该参考比较器541”可以驱动所有锁存器的致能信号以锁存胞数据。此外,信号cr还可以用于切断wl或yrpg以节省功耗。在这些实施例中,可以精确地追踪该胞及参考单元的时间延迟。该些参考胞可以放置在列中,而不是如图5(c1)或5(c2)所示的在行中。

[0046]

图5(d)示出了根据一实施例的并入了基于时间的感测电路的一pre宏观的方块图500’的一部分的示意图。方块图500’具有多个pre胞510’以及两条附加的参考列wlre、wlro,该些pre胞510’组织为n列乘m行的阵列。每个pre胞510’具有耦合到一选择器512’的pre元件511’。pre 510’的一端可以作为在每一行中的位元线(bl)连接,并且可以耦合到y写入通道闸(ywpg)540’,该y写入通道闸540’进一步耦合到vddp以用于程式化。每条位元线还耦合到一个或多个y读取通道闸(yrpg)530’作为多工器连到数据线(dl),然后每条dl耦

合到一放电电容535’和一比较器540’。每条字元线(wl)仅连接到该些胞的一半。例如,偶数的wl仅连接到偶数的行胞,而奇数的wl仅连接到奇数的行胞。在该胞中具有参考电阻的两个附加参考字元线wlre和wlro也以与普通wl相同的方式连接。如果偶数的wl导通,则奇数的参考wl也导通,反之亦然。通过这种方式,如果一行具有导通的一个胞,则另一行具有导通的一个参考胞,例如wle和wlro,将同时导通。这称为在一对行中的自参考,亦即一个是在偶数行中耦合到一个普通胞,而另一个则是在奇数行中耦合到一个参考胞。因此,该比较器输出可用于比较时序延迟,以便根据哪个单元会更早达到vdd来确定胞电阻。这可以通过将该胞单元的该比较器输出耦合到一锁存器输入d并将该参考单元耦合到该锁存器致能e来完成。例如,如果存取了在c0中的偶数胞,则c0耦合到该锁存器输入d而c1耦合到该锁存器550'的该致能输入e,反之亦然。另一个锁存器552’正好相反;两个锁存器550’和552’在一个输出多工器580’中进一步多路复用,以选择适当的输出以产生q0和q1。有上拉pmos(未显示)可在感测之前将dl0~dlm-1和dlr预充电至vdd。在感测期间,dl预充电被切断,yrpg和wl被导通。至少一对dl将分别通过pre元件511’和该参考电阻551’放电到地。当dl电压降至一预定门槛值以下时,一对行的该比较器输出将改变逻辑状态。该比较器输出c0和c1耦合至一锁存器的输入与致能以判断该pre电阻。在此实施例中,与图5(c1)所示的参考行的实施例相比,甚至可以更好地追踪该胞及参考分支。参考列可以多于一对,以在其他实施例中提供可选择的不同参考电阻准位。在另一实施例中,在一对行中的锁存器的数量可以是一个且具有适当逻辑以判断适当的胞和参考行,以便于分别诠释锁存器输入和致能。

[0047]

图5(e)示出在示意图500

”’

中的电路的一部分,以进一步示出一个自定时电路。电路500

”’

具有多个位元线(bl),570_0

”’

~570_m-1

”’

或bl0~blm-1。每条位元线bl0~blm-1都耦合到至少一y读取通道闸(yrpg)530_0

”’

~530_m-1

”’

,作为一个多工器。该些yrpg的输出耦合到至少一数据线(dl)。在此电路中,k条数据线dl0~dlk-1是从m条位元线bl0~blm-1输入感测的该些多工器yrpg 530_0

”’

~530_m-1

”’

的输出。每条数据线耦合到至少一预充电pmos 520

”’

、电容535

”’

和比较器540_0

”’

~540_k-1

”’

,跟包含以类似的配置彼此耦合的至少一参考位元线blr 571

”’

、参考yrpg531

”’

、参考数据线dlr、参考电容536

”’

及参考比较器541

”’

的参考分支相同。例如,dlr耦合到该参考电容536

”’

和该参考比较器541

”’

,该参考比较器541

”’

具有一输出cr。该cr耦合至nor 590

”’

的输入;nor 590

”’

的输出耦合到上拉pmos 520_0

”’

~520_k-1

”’

的闸极以及参考上拉pmos 521

”’

的闸极。nor 590

”’

的另一输入耦合到ckb,以导通/断开所有的上拉pmos。该参考比较器541

”’

的输出cr还耦合到多个nand闸580_0

”’

~580_n-1

”’

的输入,该些nand闸的输出分别耦合到字元线(wl)wl0~wln-1。如图所示,nand闸的另一输入耦合到x-预解码器或解码器,例如xpdi或xpdj。多个xpdi和xpdj的组合可以为n列产生n个x解码器580_0

”’

~580_n-1

”’

。为了简单起见,未示出胞阵列和输出锁存器。

[0048]

在预充电期间,所有的xpd和yrpg 530_0

”’

~530_m-1

”’

以及531

”’

分别为低准位和断开。dl0~dlk-1和dlr可通过将ckb设置为高准位以将所有上拉pmos 520_0

”’

~520_k-1

”’

和521

”’

相应地导通来预充电至高准位的vdd。在感测期间,使所选择的x-预解码器xpdi有效以导通所选择的字元线wl 580_0

”’

~580_n-1

”’

。而且还导通了该些yrpg 530_0

”’

~530_m-1

”’

和参考yrpg 531

”’

当中的至少一个。然后,将ckb设置为低准位以断开所有的上拉pmos 520_0

”’

~520_k-1

”’

和521

”’

。因此,数据线dl0~dlk-1和参考数据线dlr可以分别

通过该胞pre和参考pre放电。根据该些胞pre和该参考pre的电阻,数据线dl0~dlk-1和dlr可以相应地以不同的速率放电。当dlr电压下降到预定准位,或是例如vdd的一半时,该参考比较器输出cr将从低准位切换为高准位。cr可用于将输出c0~ck-1锁存到锁存器中,其中c0~ck-1分别是该些比较器540_0

”’

~540_k-1

”’

的输出,具有dl0~dlk-1作为输入。还可以提供例如如图5(c1)、图5(c2)和图5(d)所示的锁存器,但为简单起见,于此并未示出。同时,cr将wl驱动器580_0

”’

~580_n-1

”’

设置为无效,以防止进一步放电。cr还可以导通nor 590

”’

以进行预充电并为下一个感测周期作准备。因此,用于下一个感测的预充电不需要从0v开始,从而可以节省能量。在其他实施例中,也可以在cr有效之后断开该些yrpg。

[0049]

图5(c1)、图5(c2)、图5(d)和图5(e)中的电路是出于说明目的。可以有许多不同但又等效的实施例仍落入本发明的范围内。列和行的数量可以变化。数据线和感测单元的数量可以变化。例如,位元线与数据线的比例可以为1:1,或者数据线与位元线的比例可以为1比很多。该参考列/行的数量也可以变化。该参考列/行可以是每列一个、每行一个、每个i/o一个、每区一个,或者可以是宏观的任何列/行的一组。在不同的实施例中,耦合至字元线的该些胞可以完全填充或一半填充。在胞中的选择器可以是nmos、pmos、二极管、合并的mos/二极管或双极性装置等等。该些pre胞可以是如上所述的1r1t胞,该些pre胞可以具有一位元线bl,该bl耦合到nmos选择器的源极,该bl可以耦合到在行中的一个共享的nmos以作为ywpg,然后进一步耦合到vss(地线),而在另一实施例中,该pre的另一端可以直接耦合到vddp。在连到用于程式化的vddp的该些bl之间可以有ywpg的大于一个的准位,但也可以不存在准位。在连到用于读取的该些dl的该些bl之间可以有yrpg的大于一个的准位,但也可以不存在准位。在另一实施例中,可以省略该些附加的dl电容,而是使用内部的bl或dl负载作为取代充电/放电电容。在另一实施例中,可以在充电阶段而不是在放电阶段比较介于胞和参考单元之间的时间延迟。

[0050]

在图5(a)至图5(e)中的基于时间的感测电路仅是示例性实施例,许多改变或变化是可能的。该些通道闸可以实现为nmos、pmos或完整的cmos通道闸。电容可以由mos闸极电容、多晶硅-绝缘体-多晶硅(pip)、金属-绝缘体-金属(mim)电容或其他类型的电容制成。如果使用mos闸极电容,则厚的氧化物i/o装置将比核心逻辑装置更加,可减少漏电流。该些比较装置(例如,反向器或任何逻辑闸)可以体现为任何类型的类比比较器或感测放大器,可为静态或动态比较器。该些比较装置也可以是逻辑闸的配置,例如反向器或施密特触发器,用于在输入达到一定电压准位时切换输出。虽然一半的vdd(vdd/2)是合宜的电压,但是用于比较的参考电压可以是介于vdd及地之间的任何电压。在一些实施例中,可以省略通道闸,例如图5(a)中的通道闸106和116。在一些实施例中,可以使电容充电时间长于放电时间,以减小峰值电流;亦即,充电或放电工作周期不需要为50%。在一些实施例中,可以使用一个锁存器(或正反器)来锁存该输出数据。可以有许多不同的变体和等同的实施例,它们都属于本发明的范围。

[0051]

图6和图7分别示出了根据某些实施例的用于一可程式化电阻式存储器的一基于时间的测量电阻方法300和一基于时间的读取方法400的实施例的流程图。方法300和方法400是在一可程式化电阻式存储器的背景下描述的,例如在图5(c1)、图5(c2)、图5(d)和图5(e)中的可程式化电阻式存储器500、500”、500’和500

’”

。另外,尽管被描述为步骤的流程,但是本领域的普通技术人员应知晓,至少一些步骤可以以不同的顺序执行,包含同时执行

或跳过。

[0052]

图6是根据一实施例的将电阻转换为时间的方法300的流程图。在第一步骤310中,将具有一电容值c的一电容充电至接近例如vdd的一电源电压。在第二步骤320中,该电容通过具有一电阻值r的一电阻式装置放电。在第三步骤325中,获取一固定电压以作为一参考电压准位vr;该固定电压可以预先决定或在需要时决定。在第四步骤330中,将放电电压与参考电压准位进行比较,以判断放电电压是否已经达到参考电压准位。在第五步骤340中,从该电容的该电容值c开始放电直到放电电压被判定为等于或小于参考电压准位的时间由r*c所决定。由于该电容值c是固定的,因此可以据此判断该电阻值r。

[0053]

图7是根据一实施例的基于时间的电阻感测的方法400的流程图。方法400可以使用一prd胞以及一参考单元。在步骤410中,至少两个电容被充电到接近一电源电压vdd。一个电容是该prd胞单元的一部分,而另一个电容是该参考单元的一部分。在步骤420中,该两个电容分别通过可一程式化电阻式元件(pre)和一参考元件放电。该prd胞包含该pre,而该参考单元包含该参考元件。在一种实施方式中,可以通过导通选择器来启动放电。在步骤425中,决定一固定的参考电压以检查放电电压准位。

[0054]

在步骤430中,可以通过比较器将该固定的参考电压与放电电压进行比较;当电压放电至该参考电压准位以下时,比较器的输出可以独立地改变。在步骤440中,当该参考单元中的放电电压准位低于该参考电压准位时,该参考单元的比较器输出可以用于导通一锁存器(或正反器)。在步骤450中,该prd胞的该比较器输出用作锁存器(或正反器)的输入。在步骤460中,锁存器(或正反器)的输出是pre电阻的逻辑状态。在步骤470中,该电容放电被禁止。在步骤480中,再次对该电容和参考电容进行预充电以准备下一次感测。

[0055]

图8示出了根据一实施例的一处理器系统700。根据一实施例,该处理器系统700可以在一可程式化电阻式存储器740中包含一可程式化电阻式装置744和一基于时间的感测电路742。该处理器系统700可以例如有关于一电脑系统。该电脑系统可以包含一中央处理单元(cpu)710,该中央处理单元710通过一公用汇流排715与各种存储器和周围的装置(例如,输入输出单元720、硬盘机730、cdrom 750、可程式化电阻式存储器740和其他存储器760)进行通讯。其他存储器760是一般的存储器,例如静态随机存取存储器(sram)、dram或快闪存储器,通常通过一存储器控制器与cpu 710连接。cpu 710通常是一微处理器、一数位信号处理器或其他可程式化数位逻辑装置。可程式化电阻式存储器740较佳地被构造为一积体电路,该积体电路包含在一存储器阵列中的多个可程式化电阻式装置744及至少一基于时间的感测电路742。该可程式化电阻式存储器740通常通过简单的界面控制或透过一存储器控制器与cpu 710连接。如果需要,该可程式化电阻式存储器740可以在一个单一的积体电路中与该处理器(例如cpu 710)结合。

[0056]

如果该pre是一个一次性可程式化(otp)元件,例如电熔丝,则可靠地对熔丝进行程式化的方法可包含以下步骤:(a)首先从低程式化电压开始对一otp存储器的一部分进行程式化并增加该程式化电压,直到所有计划的otp胞都可以被程式化并通过验证为止,将此电压标记为程式化电压的下限;(b)连续增加该程式化电压以对otp存储器胞的另一部分进行程式化,直到至少一个otp胞(无论是否已程式化)验证失败,将此电压标记为程式化电压的上限。在不同的实施例中,递增的程式化可以发生在相同或另一未程式化的otp存储器上。此外,可以通过相应地重复上述步骤(a)和(b)直到下限、上限或程式化窗口(介于上限

和下限之间的电压范围)达到目标值,来调整程式化时间以特征化该程式化窗口。因此,可以找到可靠地对该电熔丝进行程式化的窗口。在特征化该程式化窗口之后,可以在至少一脉冲的介于下限和上限之间的电压对其他otp胞进行程式化。

[0057]

本发明可以在印刷电路板(pcb)或系统(电子系统、计算系统等等)中的积体电路的一部分或全部中实现。可程式化电阻式存储器可以是熔丝、反熔丝或新兴的非挥发性存储器。熔丝可以是硅化或非硅化的多晶硅熔丝、金属熔丝、mos闸极、局部互连,热隔离主动区域熔丝、触点熔丝、通孔熔丝或鳍式场效电晶体(finfet)本身。反熔丝可以是闸极氧化物崩溃反熔丝、具有介电质在中间的触点反熔丝或通孔反熔丝。新兴的非挥发性存储器可以是电磁ram(mram)、相变存储器(pcm)、导电桥ram(cbram)、铁电ram(feram)或电阻式ram(rram)。虽然程式化机制不同,但是它们的逻辑状态可以通过不同的电阻值来区分。半导体也可以由非晶、多晶硅或有机半导体薄膜基板以所谓的薄膜电晶体(tft)技术代替硅晶技术,例如批量或soi(绝缘层上覆硅)技术来制造。

[0058]

本申请通过引用并入:(1)2017年4月14日提交的标题为“用于可程式化电阻式存储器的超低电压和低电流读取的电路及系统”的美国临时专利申请案第62/485,895号;以及(2)2018年4月14日提交的标题为“用于可程式化电阻式存储器的低功率读取操作”的美国专利申请案第15/953,422号;(3)2019年9月3日提交的美国临时专利申请案第16/559,560号及(4)2020年7月16日提交的美国临时专利申请案第16/931,314号。

[0059]

当然,本发明还可有其它多种实施例,在不背离本发明精神及其实质的情况下,熟悉本领域的技术人员当可根据本发明作出各种相应的改变和变形,但这些相应的改变和变形都应属于本发明所附的权利要求的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1