存储器装置以及其读取方法与流程

1.本发明属于存储技术领域,涉及一种存储器装置以及其读取方法,且特别是有关于一种可提升读取速率的存储器装置以及其读取方法。

背景技术:

2.在现有的技术领域,在非易失性存储器的读取动作中,读取动作的表现度的瓶颈,常限制在所需执行的错误纠正动作所耗去的时间。在理论上,在现有技术中,为降低读取动作所需的时间,可执行连续多个存储页的读取动作,并在前一存储页的页数据被读出后,通过预先获得下一个页地址的方式,可加速连续读取动作的进行。

3.然而,在具有复杂机制的多个位的错误纠正动作被应用在存储器装置中后,每一次的错误纠正动作所需要的时间变得无法预期的长。也因此,针对存储器所进行的多个连续存储页的读取动作,所需要耗去的读取时间往往耗费以执行错误纠正动作,使读取动作的效率无法被提升。

技术实现要素:

4.本发明提供一种存储器的读取方法,可提升读取速率。

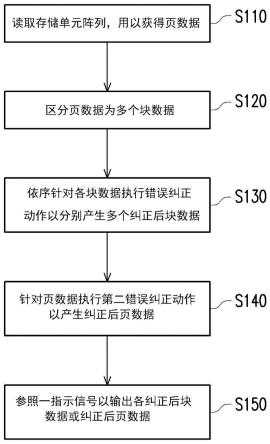

5.本发明的存储器的读取方法包括:读取存储单元阵列,用以获得页数据;区分页数据为多个块数据;依序针对各块数据执行第一错误纠正动作以分别产生多个纠正后块数据;针对页数据执行第二错误纠正动作以产生纠正后页数据;以及,参照一指示信号以输出纠正后块数据。

6.本发明的存储器装置包括存储单元阵列、页缓冲器、数据暂存器、第一错误纠正电路、第二错误纠正电路、控制逻辑以及传输界面。页缓冲器耦接存储单元阵列。页缓冲器储存页数据,其中页数据被区分为多个块数据。数据暂存器用以暂存块数据。第一错误纠正电路耦接数据暂存器,依序针对各块数据执行第一错误纠正动作以分别产生多个纠正后块数据。第二错误纠正电路耦接数据暂存器,针对页数据执行第二错误纠正动作以产生纠正后页数据。控制逻辑耦接第一错误纠正电路以及第二错误纠正电路,用以控制第一错误纠正电路以及第二错误纠正电路以分别执行的一错误纠正动以及第二错误纠正动作。传输界面耦接数据暂存器以通过参考指示信号来输出纠正后块数据。

7.基于上述,本发明通过使页数据分为多个尺寸相对小的块数据。并依序针对块数据执行具有相对快速度的错误纠正动作(第一错误纠正动作),连续的纠正后块数据可以被立刻读出直到出现无法被纠正的块数据。第二错误纠正动作可以干预并取代执行接下来的读出数据的错误纠正动作。如此一来,通过所执行的错误纠正动作具有不多的纠错位数,可降低执行错误纠正动作所需的时间,并用以提升存储器的读取速率。进一步的,若纠正后块数据并非正确,相对慢的错误纠正动作(第二错误纠正动作)所产生的纠正后页数据可以提供以作为读出数据。存储器装置的读出操作的正确度可以被确保。

附图说明

8.图1绘示本发明一实施例的存储器的读取方法的流程图。

9.图2绘示本发明实施例的存储器的读取方法的动作示意图。

10.图3a以及图3b绘示本发明另一实施例的存储器的读取方法的流程图。

11.图4绘示本发明一实施例的存储器装置的示意图。

12.图5a至图7c分别绘示本发明不同实施例的存储器装置的读取动作的波形图。

13.【符号说明】

14.210、410:存储单元阵列

15.220、310、420:页缓冲器

16.230、340、470:传输界面

17.320、441:第一缓存

18.330、442:第二缓存

19.400:存储器装置

20.431:第一ecc电路

21.432:第ecc电路

22.433:第三ecc电路

23.440:数据暂存器

24.450:控制逻辑

25.460:暂存器

26.cch0~cch3:纠正后块数据

27.ch0~ch3:块数据

28.clk、slck:时脉信号

29.cs#:芯片选择信号

30.dqs:数据提取信号

31.i/o、io[7:0]:数据或命令信号

[0032]

pg0~pgn+1:存储页

[0033]

rdy/by#:中断信号

[0034]

t1、t2:延迟时间

[0035]

rd:数据读取命令

[0036]

addr:地址信息

[0037]

dp1~dpn+2:读出数据

[0038]

s110~s150、s310~s3110:读取步骤

具体实施方式

[0039]

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

[0040]

请参照图1,图1绘示本发明一实施例的存储器的读取方法的流程图。在步骤s110中,对一存储单元阵列执行一读取动作,并由存储单元阵列中读出一页数据。其中,步骤s110中的读取动作,可以针对存储单元阵列中的一个存储页(memory page)来进行,并用以

读取一个页数据。细节上,可预先产生一页地址,并依据页地址来由存储单元阵列中选出一选中存储页,并针对选中存储页进行读取动作。选中存储页所传出的数据可通过感测放大器(sense amplifier)进行感测动作,以产生上述的页数据。在本实施例中,页数据例如具有2k或4k个位组(byte)。

[0041]

接着,在步骤s120中,将所读出的页数据区分为多个块(chunk)数据。在本实施例中,可将页数据均分多个具有相对小尺寸的块数据。在本实施例中,各个块数据例如具有256个位组。以页数据具有2k位组为范例,步骤s120中可区分一页数据为8个块数据,以页数据具有4k位组为范例,步骤s120中则可区分一页数据为16个块数据。

[0042]

在步骤s130中,则依序针对各个块数据与对应的奇偶校验数据(parity data)执行第一错误纠正(error correction code,ecc)动作,并分别产生多个纠正后块数据。在本实施例中,基于步骤s130中所执行的错误纠正动作,是针对具有较小尺寸的块数据来进行的,因此单一块数据中所可能发生的错误位数可能不多。也因此,本发明实施例中,步骤s130中可以针对各个块数据执行具有小纠错位数(例如1个位)的错误纠正动作,并用以减低执行错误纠正动作中所需要的时间。

[0043]

在本实施例中,步骤s130中的第一错误纠正动作可以依据汉明码(hamming code)的方式来实施,或其他为本领域技术人员的纠错码及其演算法来实施,没有固定的限制。

[0044]

步骤s140则在当第一错误纠正动作发生错误时,针对页数据执行第二错误纠正动作以产生纠正后页数据。在本实施例中,针对块数据所执行的第一错误纠正动作的速度,快于针对页数据所执行的第二错误纠正动作的速度。此外,第一错误纠正动作的能力,则低于第二错误纠正动作的能力。例如,第二错误纠正动作可以依据bch码、rs码或低密度奇偶检查码(low-density parity-check code,ldpc code)的演算方式来执行。

[0045]

在步骤s150中,纠正后页数据以及纠正后块数据的其中之一可以通过参照指示信号,被输出以产生存储器的读出数据。在细节上,若所有的纠正后块数据都是正确的,各个块数据可以被立刻输出以产生读出数据。例如,第一块数据(块0)可以首先被纠正,在当第一纠正后块数据被输出时,第二块数据(块1)可以同时被纠正。如此一来,多个纠正后块数据可以连续被输出而没有延迟。相反的,若第一个无法被纠正块数据出现时,则变更选择纠正后页数据以作为读出数据。另外,存储器可产生指示信号来指示读出数据是否已备妥。读出数据可基于指示信号以被送出。

[0046]

在此,步骤s130以及s140可以同时被执行,或者也可以依序被执行。且上述的指示信号可以是独立的信号。

[0047]

以下请参照图2,图2绘示本发明实施例的存储器的读取方法的动作示意图。其中,存储单元阵列210具有多个存储页pg0~pgn+1。在进行读取动作时,可设定其中的存储页pgn为选中存储页,并针对选中存储页(存储页pgn)进行数据读取以及感测动作,并用以获得存储页pgn中所储存的页数据。在本实施例中,页数据可以暂存于页缓冲器220中。而页缓冲器220中所储存的页数据,则可以被分割为多个块数据ch0~ch3。

[0048]

块数据ch0~ch3可以依序被提供以执行错误纠正动作,并依序产生纠正后块数据cch0~cch3。纠正后块数据cch0~cch3可被传送至传输界面230,以传出由纠正后块数据cch0~cch3所组成的纠正后页数据,以作为读出数据。

[0049]

在本实施例中,存储单元阵列210可以为非易失性存储单元阵列,例如闪存存储单

元阵列。

[0050]

当然,图2中将单一页数据分割出的四个块数据ch0~ch3仅只是说明用的范例,本发明其他实施例中的块数据的数量可以由设计者自行决定,并没有一定的限制。

[0051]

以下请参照图3a以及图3b,图3a以及图3b绘示本发明另一实施例的存储器的读取方法的流程图。在步骤s310中,读取动作被执行,并在步骤s320中,通过感测放大器的感测动作,来感测出一存储页(例如第n个存储页)中的页数据。步骤s330中,则使页数据被锁存在例如页缓冲器310的数据储存元件中。步骤s340中,则使页数据被转移至第一缓存320中,并在步骤s350中,使被选中页地址被变更至下一个页地址。其中,在第一缓存320中,页数据可以被分为多个块数据ch0~ch5。

[0052]

接着,在步骤s361中,则依序使块数据ch0~ch5的其中之一执行一错误纠正(ecc)动作,并在当每一块数据ch0~ch5的ecc动作的过程中,判断是否可以通过1位的ecc动作来完成每一块数据ch0~ch5的错误纠正动作(步骤s371),若判断结果为是,则执行步骤s381;相对的,若判断结果为否,则执行步骤s372。在此,步骤s361中执行的ecc动作的错误纠正位数是1。

[0053]

值得注意的,在本实施例中,步骤s362并同时针对页缓冲器310中所储存的页数据执行另一ecc动作,而步骤s362中的ecc动作可以针对页数据中多个位的错误进行纠正。

[0054]

当步骤s371中,发现有任一块数据中的错误位数超过一位时,而无法通过步骤s361中的ecc动作完成错误纠正时,则可通过执行步骤s372,以针对页数据中的多个错误位执行错误纠正的动作。

[0055]

通过步骤s381,可以依序获得对应块数据的多个纠正后块数据,并据以获得纠正后页数据。而通过步骤s372,则可以直接获得纠正后页数据。而在步骤s390中,则可以将步骤s381中所获得的纠正后块数据,转移至第二缓存330中。并且,在步骤s390后,则改选中下一个块数据(步骤s3100)并重新执行步骤s340。

[0056]

在步骤s390中,也可将步骤s372中所获得的纠正后页数据转移至第二缓存330。并在步骤s3110中,通过读出第二缓存330中的纠正后页数据至传输界面340来传送出读出数据。

[0057]

为了加快读取动作的速率,在当步骤s340完成将页数据转移至第一缓存320中,步骤s350可使选中的页地址变更至下一个页地址,并通过步骤s320以执行下一个页地址的存储页(例如第n+1个存储页,或主机预先设置的存储页)的页数据执行读取及感测动作,并使第n+1个存储页的页数据被储存至页缓冲器310中。

[0058]

此外,本发明实施例中,步骤s361以及步骤s362所分别执行的不同的ecc动作,可以同时进行,或也可以在步骤s371的判断结果发生否的状态下,才启动步骤s362的进行。没有一定的限制。

[0059]

附带一提的,步骤s361的ecc动作可以依据汉明码(hamming)的演算方式来进行,而步骤s362的ecc动作则可以依据bch码、rs码或低密度奇偶检查码(low-density parity-check code,ldpc code)的演算方式来执行。请特别注意的,步骤s361的ecc动作的操作速度总是快于步骤s362的ecc动作的操作速度。

[0060]

在此请注意,步骤s3110中,存储器所送出的读出数据是参照指示信号来进行的。指示信号的产生是依据读出数据是否备妥来进行的。如此一来,数据接收器(例如主机)可

正确的获得读出数据而不会产生数据漏失。

[0061]

以下请参照图4,图4绘示本发明一实施例的存储器装置的示意图。存储器装置400包括存储单元阵列410、页缓冲器420、第一错误纠正码(ecc)电路431、第二ecc电路432、数据暂存器440、控制逻辑450、暂存器460以及传输界面470。存储单元阵列410具有多个存储页,并耦接至页缓冲器420。在针对存储单元阵列410进行读取动作时,可选中存储单元阵列410中的一存储页进行读取,并将读出的页数据暂存于页缓冲器420中。其中,页数据可以被区分为多个块数据。

[0062]

数据暂存器440耦接至页缓冲器420。数据暂存器440中具有第一缓存441以及第二缓存442。页缓冲器420中的页数据可先被转存至第一缓存441。并且,第一ecc电路431可针对第一缓存441中的每一块数据,依序的执行ecc动作,并依序产生多个纠正后块数据。而每一纠正后块数据则可依序的被储存至第二缓存442中。

[0063]

在另一方面,当第一个无法被纠正的块数据发生时,可通过第二ecc电路432来执行错误纠正动作。在此方法下,剩余未被纠正的块数据可通过纠正后页数据来完成错误纠正动作并进行输出。在本实施例中,第一ecc电路431的纠错能力低于第二ecc电路432的纠错能力。例如,第一ecc电路431的纠错位数可以为1位,第二ecc电路432的纠错位数可以为大于1的多个位。另一方面,作用在各个块数据上的ecc动作的速度,则快于作用在页数据上的ecc动作的速度。

[0064]

控制逻辑450耦接至存储单元阵列410、页缓冲器420、数据暂存器440、第一ecc电路431以及第二ecc电路432。控制逻辑450可用以执行存储单元阵列410的数据存取动作。控制逻辑450并可用以控制第一缓存441中块数据的转移动作,以及控制第一ecc电路431以及第二ecc电路432的启动时间点。

[0065]

在部分实施例中,存储器装置400可还包括第三ecc电路433。第三ecc电路433耦接在控制逻辑450以及数据暂存器440间。第三ecc电路433可对页数据执行另一ecc动作。其中第三ecc电路433可以第二ecc电路纠正更多的位。

[0066]

本实施例中,控制逻辑450可用以执行图3所绘示的动作流程,相关细节可参照图3实施例的说明内容。

[0067]

控制逻辑450并耦接至暂存器460。暂存器460提供控制逻辑450在执行各种动作程序中的暂存数据的存取。控制逻辑450以及暂存器460并耦接至传输界面470。传输界面470收发数据或命令信号i/o,接收时脉信号clk,传收芯片选择信号cs#以及传送数据提取信号dqs。

[0068]

传输界面470作为存储器装置400对外部电子装置间的信号传输界面。传输界面470可以为并行的传输界面;可以是串行的传输界面;或也可以是并行串行共存的传输界面。值得注意的,本发明实施例中,存储器装置400的传输界面,在传输协议上,并没有特定的限制。在本实施例中,芯片选择信号cs#以及数据提取信号dqs的其中之一可选择以作为指示信号。传输界面470可告知外部电子装置以接收读出数据。指示信号可以由控制逻辑450以依据读出数据是否已备妥来产生。在部分实施例中,传输界面470可提供芯片选择信号cs#以及数据提取信号dqs以外的中断信号rdy/by#来作为指示信号。

[0069]

以下请参照图5a至图7c,图5a至图7c分别绘示本发明不同实施例的存储器装置的读取动作的波形图。在图5a至图7c中,存储器装置可依据时脉信号slck来执行工作。

[0070]

在图5a至图5c中,数据提取信号dqs被选择以作为指示信号数据。并且,数据读取命令rd以及对应的地址信息addr可以由主机通过数据或命令信号io[7:0]被传送至存储器装置。在第一页的读出数据dp1,数据提取信号dqs被维持为静态的状态。在延迟时间t1,操作于读出数据dp1的ecc动作完成后,数据提取信号dqs被启动并开始在逻辑高、低电平间转态。主机可对应数据提取信号dqs来获得读出数据dp1。

[0071]

在图5b中,第二页至第n页的读出数据dp2-dpn可连续被读出。由于读出数据dp2-dpn可由仅需短的错误纠正时间的纠正后块数据来获得,读出数据dp2-dpn可在没有延迟时间的情况下被送出。数据提取信号dqs可以持续转态。

[0072]

在图5c中,读出数据dpn+1被送出,数据提取信号dqs在当有无法被纠正的块数据发生时可以被维持在低电平,直到针对页数据所执行的错误纠正动作完成。在这个页数据中,一但针对页数据的错误纠正动作被完成,上述无法被纠正的块数据以及剩下的块数据对应的读出数据dpn+2可以随着重新转态的数据提取信号dqs被送出。在此,需要一较长的延迟时间t2以执行页数据的错误纠正动作。然后,读出数据dpn+2可以依据纠正后页数据来获得。

[0073]

在此可以看见,在本实施例中,读出数据可以依据指示信号来发送,使主机可以正确的获得读出数据。并且,数据提取信号dqs可以基于ecc动作的执行来动态调整。以及,存储装置的读出延迟可以为主机所得知。

[0074]

在图6a至图6c中,芯片选择信号cs#被选择以作为指示信号数据。并在当读出数据备妥时,芯片选择信号cs#上可产生一正脉波,而主机可通过识别芯片选择信号cs#上的正脉波来接收读出数据。在图6a中,数据读取命令rd以及对应的地址信息addr可以由主机通过数据或命令信号io[7:0]被传送至存储器装置。然后,在延迟时间t1后,读出数据dp1被备妥,芯片选择信号cs#上产生正脉波。接着,主机可基于时脉信号slck来获得读出数据dp1。

[0075]

在图6b中,连续的第1页至第n页的读出数据dp1-dpn可依据纠正后块数据来依序被送出,而不需要额外的读出延迟。读出数据dp2-dpn可在没有延迟时间的情况下被送出。图6b中的芯片选择信号cs#维持在逻辑低电平。

[0076]

在图6c中,读出数据dpn+1被送出,第n+2页的读出数据dpn+2由纠正后页数据来获得。在延迟时间t2后,主机可通过识别芯片选择信号cs#上另一正脉波来获得读出数据dpn+2。

[0077]

在图7a至图7c中,中断信号rdy/by#被产生,并被选择以作为指示信号数据。在本实施例中,中断信号rdy/by#被拉低至逻辑低电平以指示读出数据尚未备妥。在另一方面,当读出数据被备妥时,中断信号rdy/by#则被拉高至逻辑高电平,以指示读出数据已备妥并可基于时脉信号slck来获得。

[0078]

在图7a中,数据读取命令rd以及对应的地址信息addr可以由主机通过数据或命令信号io[7:0]被传送至存储器装置。然后,中断信号rdy/by#被拉低至逻辑低电平来告知主机,读出数据dp1尚未备妥。在延迟时间dp1后,中断信号rdy/by#被拉高至逻辑高电平,主机可接收存储装置第一页的读出数据dp1。

[0079]

在图7b中,连续的第1页至第n页的读出数据dp1-dpn可依据纠正后块数据来依序被送出,而不需要额外的读出延迟。读出数据dp2-dpn可在没有延迟时间的情况下被送出。图7b中的中断信号rdy/by#维持在逻辑高电平。

[0080]

在图6c中,在读出数据dpn+1被送出后,第n+2页的读出数据dpn+2由纠正后页数据来获得,且中断信号rdy/by#被拉低。在延迟时间t2后,中断信号rdy/by#被重新拉高,主机可依据时脉信号slck来获得读出数据dpn+2。

[0081]

综上所述,本发明使页数据区分为多个块数据以降低执行错误纠正动作的数据的尺寸。并且,通过高速且具有低错误纠正位数的第一错误纠正动作来针对各个块数据进行错误纠正动作。如此一来,在存储器的读取动作中,因为错误纠正动作所产生的读出数据的传输延迟可以被避免,有效提升存储器的工作效率。并且,通过提供指示信号,可在因不同ecc动作的条件而具有不同数据延迟的条件下,来确定读出数据可被获得。如此,主机可正确的依据指示信号来获得读出数据。

[0082]

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1