具有内容可寻址存储器缓冲器的内容可寻址存储器系统中的写入和查询操作的制作方法

1.本公开大体上涉及内容可寻址存储器,并且更具体地说,涉及具有内容可寻址存储器缓冲器的内容可寻址存储器系统中的写入和查询操作。

背景技术:

2.存储器系统可实施于电子系统中,例如计算机、蜂窝电话、手持式电子装置等等。一些存储器系统,例如固态驱动器(ssd)、嵌入式多媒体控制器(emmc)装置、通用快闪存储(ufs)装置等等,可包含用于存储来自主机的主机(例如,用户)数据的非易失性存储存储器。非易失性存储存储器通过在无供电时保持所存储的数据来提供永久性数据,并且可包含nand快闪存储器、nor快闪存储器、只读存储器(rom)、电可擦除可编程rom(eeprom)、可擦除可编程rom(eprom)和电阻可变存储器,例如相变随机存取存储器(pcram)、三维交叉点存储器(例如,3d xpoint)、电阻性随机存取存储器(rram)、铁电随机存取存储器(feram)、磁阻随机存取存储器(mram)和可编程导电存储器,以及其它类型的存储器。

3.一些存储器单元,例如各个电阻可变存储器单元,可以交叉点架构布置,使得存储器单元位于用于存取单元的信号线的相交点(例如,字线和位线的相交点)。例如,电阻可变存储器单元的状态(例如,所存储数据值)可取决于存储器单元的经编程电阻。

4.存储器通常响应于由主机供应的地址将用户数据返回到主机(例如,在读取操作期间)。存储器的另一形式是内容可寻址存储器(cam),也被称为联合模式存储器(apm)。在一些实例中,cam可经查询以确定输入数据(例如,输入数据向量)是否存储在cam中。例如,cam可接收输入数据,并且可执行搜索以确定cam中所存储的数据(例如,所存储的数据向量)是否匹配输入数据。

5.在需要快速搜索或模式匹配的应用中,例如在计算机系统、数据库、图像或语音辨识、生物特征、数据压缩、高速缓存存储器控制器或计算机和通信网络中(例如,在网络交换机、媒体存取控制器、网络路由器等等中),cam可用作基于硬件的搜索装置。

附图说明

6.图1a是根据本公开的若干实施例的设备的简化框图。

7.图1b示出根据本公开的若干实施例的数据结构的实例。

8.图2a是根据本公开的若干实施例的对应于特定写入阶段的非易失性cam的一部分的框图。

9.图2b是根据本公开的若干实施例的对应于在图2a的所述特定写入阶段之后的特定写入阶段的非易失性cam的一部分的框图。

10.图3a是根据本公开的若干实施例的对应于特定写入阶段的缓冲器cam的一部分的框图。

11.图3b是根据本公开的若干实施例的对应于在图3a的所述特定写入阶段之后的特

定写入阶段的缓冲器cam的一部分的框图。

12.图4是根据本公开的若干实施例的cam的简化框图。

13.图5示出根据本公开的若干实施例的非易失性cam的一部分。

14.图6示出根据本公开的若干实施例的存储在非易失性cam中的数据查询。

具体实施方式

15.在各种情况下,非易失性存储器可用作cam。提供非易失性存储器cam可具有优于易失性cam(例如,sram cam)的各种益处。举例来说,非易失性cam不需要电力来维持其数据,且非易失性存储器单元相比于易失性存储器单元通常具有更小的覆盖区,因此可以提供更大的存储密度。相比于非易失性cam,易失性cam通常可提供更快的数据写入时间,使得写入到易失性cam的数据可以比写入非易失性cam的数据更早得用于查询。

16.在一些实例中,当数据正在写入到cam时,非易失性cam不可存取用于查询。例如,当额外数据正在写入到非易失性cam中时,非易失性cam中先前存储的数据不可存取用于查询。此问题可能会因为与非易失性cam相关联的相对较长写入时间而加剧,原因在于先前写入的数据在写入时间期间不可存取用于查询。

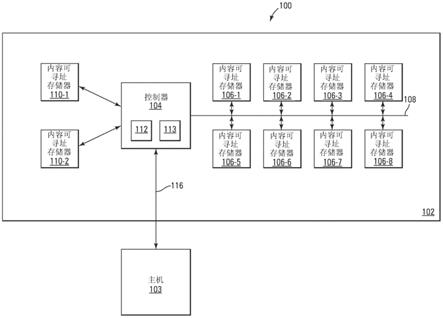

17.如在本文中进一步描述,本公开的各种实施例提供可考虑到与非易失性存储器单元相关联的写入时间的cam实施方案。因此,实施例可以提供相比于先前方法具有改进的查询时间以及其它益处的非易失性cam。

18.作为实例,数个实施例可采用非易失性第一cam作为主要cam,并采用第二cam作为缓冲器cam,例如易失性cam(例如,sram缓冲器cam)。数据可以写入主要cam和缓冲器cam,并且在主要cam中继续写入数据时,在缓冲器cam中写入的数据可以进行查询。例如,这可以消除与等待数据写入到主要cam才查询主要cam中的数据相关联的延迟。

19.在一些实例中,主要cam中先前写入的数据可以复制到缓冲器cam中,使得当在主要cam中写入额外数据时,先前写入的数据可以在缓冲器cam中查询。例如,这可以消除当在主要cam中写入额外数据时主要cam中先前写入的数据不可存取用于查询的问题。

20.相比于结合主要cam使用dram缓冲器或作为缓冲器的表,结合主要非易失性cam使用缓冲器cam可以降低获得可靠比较结果所需的能量要求、成本和时间。例如,使用dram或表可涉及扫描dram或表的全部内容以识别对应于与输入数据比较的主要cam中的数据的数据的耗时过程。

21.图1a是根据本公开的若干实施例的呈计算系统100形式的设备的简化框图。计算系统100包含呈cam系统102形式的设备,它可以是例如外围组件互连高速(pcie)cam系统,以及其它类型的cam系统。

22.cam系统102可包含控制器104、通过总线108耦合到控制器104的cam 106

‑

1到106

‑

8,以及耦合到控制器104的cam 110

‑

1和110

‑

2。尽管示出八个cam 106和两个cam 110,但是可存在任何数目个cam 106和cam 110。在一些实例中,cam 106可被称为主要(例如,主)cam,cam 110可被称为缓冲器cam(例如,因为cam 110可以充当cam 106的缓冲器)。在一些实例中,可存在可包含cam 106

‑

1到106

‑

8的单个主要cam 106,并且可存在可包含cam 110

‑

1和110

‑

2的单个缓冲器cam 110。本文中,“cam 106”和/或“主要cam”将用于指代cam 106

‑

1到106

‑

8中的一或多个,“cam 110”和/或“缓冲器cam”将用于指代cam 110

‑

1和110

‑

2中的一

或多个。

23.控制器104可使主要cam将数据(例如,一或多个数据向量)写入在主要cam中,使缓冲器cam将数据写入在缓冲器cam中,并在主要cam继续将数据写入在主要cam中时使缓冲器cam查询在缓冲器cam中写入的数据。在一些实例中,查询主要cam和/或缓冲器cam中的数据可包含比较输入数据(例如,输入数据向量)与主要cam和/或缓冲器cam中的数据。在一些实例中,控制器104可响应于确定主要cam已结束在主要cam中写入数据而使缓冲器cam去除在缓冲器cam中写入的数据,并且随后可使主要cam查询主要cam中的数据。

24.在各种实例中,控制器104可包含可用于验证输入数据向量和存储在缓冲器cam或主要cam中的数据向量之间的匹配的匹配验证电路系统。例如,响应于接收到输入数据向量匹配所存储的数据向量的指示,匹配验证电路系统可使缓冲器cam或主要cam读取所存储的数据向量,并将从缓冲器cam或主要cam读取的数据向量返回到控制器104。然后,匹配验证电路系统可以比较返回的数据向量与输入数据向量,以确定先前指示的匹配是否有效。

25.在一些实例中,主要cam和缓冲器cam可包含可用于验证输入数据向量和所存储向量之间的匹配的匹配验证电路系统。例如,响应于输入数据向量匹配所存储的数据向量,匹配验证电路系统可读取所存储的数据向量,并比较读取的数据向量与输入数据向量,以确定先前指示的匹配是否有效。如果匹配无效,那么匹配验证电路系统可以将比较结果从匹配变成不匹配,并将结果发送到控制器104。

26.控制器104可使主要和缓冲器cam并行地在主要cam中和在缓冲器cam中写入数据,直到缓冲器cam结束在缓冲器cam中写入数据为止,并且可在主要cam继续在主要cam中写入数据时使缓冲器cam查询在缓冲器cam中写入的数据。例如,主要cam可在第一时间段内将数据写入在主要cam中;缓冲器cam可在与第一时间段的初始部分重叠的第二时间段内将数据写入在缓冲器cam中,并且缓冲器cam可在第一时间段的其余部分期间查询在缓冲器cam中写入的数据。在一些实例中,缓冲器cam将数据写入在缓冲器cam中的速度可快于主要cam将数据写入在主要cam中的速度。

27.在一些实例中,主要cam可以是非易失性cam,缓冲器cam可以是易失性cam,例如sram cam。例如,在缓冲器cam中写入和/或存储的数据可写入和/或存储在sram存储器单元中,且在主要cam中写入和/或存储的数据可写入和/或存储在非易失性存储器单元中。在一些实例中,主要cam可以是可包含电阻可变存储器单元的交叉点装置,例如3d xpoint装置。但是,本公开不限于此,并且主要cam可包含其它类型的非易失性存储器单元。

28.控制器104可在每次数据向量写入在主要cam中时(例如,响应于主要cam将数据向量写入在主要cam中)创建数据结构,例如查找(例如,映射)表112(例如,在控制器104中)。应注意,缓冲器cam可在每次主要cam将数据向量写入在主要cam中时将对应数据向量写入在缓冲器cam中。在一些实例中,控制器104可管理查找表112。

29.在一些实例中,控制器104可包含逻辑到物理(l2p)映射表113,其可将数据向量的从主机103接收的逻辑地址映射到主要cam中的数据向量的物理地址。

30.控制器104可以是现场可编程门阵列(fpga)和/或专用集成电路(asic),以及其它类型的控制器。主机103可以是例如主机系统,如个人膝上型计算机、台式计算机、数码相机、移动装置(例如,蜂窝电话)、网络服务器、支持物联网(iot)的装置或存储卡读卡器,以及各种其它类型的主机。举例来说,主机103可包含能够通过接口116存取cam系统102(例

如,经由控制器104)的一或多个处理器,所述接口可包含总线。接口116可以是标准化接口,例如串行高级技术附件(sata)、pcie或通用串行总线(usb),以及各种其它接口。

31.在一些实例中,cam系统102可以是计算系统100的存储器系统的部分。例如,存储器系统可以是存储系统,例如ssd、ufs装置、emmc装置等等。在其中cam系统102可以是存储器系统的部分的各种实例中,控制器104可以是耦合到存储器系统且配置成控制存储器系统的各种存储器装置的存储器系统控制器(例如,ssd控制器、专用集成电路asic、处理器等等)(例如,集成在其中的控制逻辑)的部分。

32.图1b示出根据本公开的若干实施例的呈查找表112形式的数据结构的实例。查找表112可包含条目114

‑

1到114

‑

n,它们可将主要cam中的位置(例如,位置的地址)映射到缓冲器cam中的位置(例如,位置的地址)。例如,查找表112可将主要cam地址映射到缓冲器cam地址。

33.在一些实例中,主要cam地址可以是其中写入数据向量的主要cam中的存储器单元群组的位置的物理地址,缓冲器地址可以是存储对应于在主要cam中写入的数据向量的数据向量的缓冲器cam中的存储器单元群组的位置的物理地址。例如,条目114

‑

1到114

‑

n可将在主要cam中写入的主要cam中的数据向量的位置的地址映射到缓冲器cam中的对应数据向量的位置的地址。控制器104可管理查找表112,例如,通过在条目114中写入主要cam中的数据向量的地址和缓冲器cam中的数据向量的地址。当主要cam正在主要cam中的位置中写入对应数据向量时,条目114中的映射可以是有效的,并且控制器104可管理查找表112,例如通过响应于确定主要cam已结束在主要cam中的位置中写入数据而使映射无效。

34.在一些实例中,主要cam地址可以是主要cam中的存储器拼片的物理地址,缓冲器地址可以是缓冲器cam中的区域的物理地址。例如,条目114

‑

1到114

‑

n可将主要cam中的存储器拼片的位置的地址映射到缓冲器cam中的区域的位置的地址。在一些实例中,存储器拼片地址中的每一个可映射到对应于缓冲器cam中的区域的地址范围。在一些实例中,只要对应存储器拼片被数据部分地填充(例如,不完全地填充),条目114中的映射就可为有效的,并且控制器104可响应于确定对应存储器拼片被完全填充而使映射无效。

35.图2a是根据本公开的若干实施例的对应于特定写入阶段的非易失性cam的一部分的框图。图2b是根据本公开的若干实施例的对应于在图2a的所述特定写入阶段之后的特定写入阶段的非易失性cam的一部分的框图。例如,图2a和2b示出主要cam的非易失性cam阵列218,例如可以是cam 106的cam 206。cam阵列218可包含数个存储器拼片220(例如,存储器拼片220

‑

1到220

‑

m)。在一些实例中,存储器拼片可以是在写入操作期间不可用于查询的最小存储器单元分组。例如,当数据向量正在写入到存储器拼片220时,所述存储器拼片可能不可用于查询。

36.存储器拼片220

‑

1到220

‑

m中的每一个可包含在相应位置225

‑

1到225

‑

k的相应存储器单元群组。存储器拼片220

‑

1到220

‑

m中的每一个中的相应位置225

‑

1到225

‑

k可分别具有物理地址addr 1到addr k。相应数据向量可以写入在存储器拼片220

‑

1到220

‑

m中的每一个的相应位置225

‑

1到225

‑

k中。在一些实例中,l2p表113可将来自主机103的相应逻辑地址映射到相应主要cam中的相应存储器拼片220中的相应地址addr。

37.每个相应位置225可通过指定cam系统中的相应主要cam(例如,cam系统102中的cam 106)的位置、相应主要cam中的相应存储器拼片(例如,存储器拼片220)的位置和相应

存储器拼片中的相应位置225来指定。例如,cam 106

‑

3中的存储器拼片220

‑

1中的位置225

‑

2可通过指定cam系统102中的cam 106

‑

3的位置、cam 106

‑

3中的存储器拼片220

‑

1的位置和存储器拼片220

‑

1中的位置225

‑

2来指定。

38.相应物理地址addr可指定相应数据向量的位置,例如通过指定cam系统中的相应主要cam的位置、相应主要cam中的相应存储器拼片的位置和相应存储器拼片中的相应数据向量的位置。例如,物理地址addr 2可通过指定cam 106

‑

3的位置、cam 106

‑

3中的存储器拼片220

‑

1的位置和存储器拼片220

‑

1中的vector 2的位置225

‑

1来指定数据向量vector 2的位置。

39.在一些实例中,每个存储器拼片220中的位置225

‑

1到225

‑

k可以是有序序列,其中位置225

‑

1到225

‑

k分别是有序序列中的第一个到第k个位置。此外,地址addr 1到addr k可以是有序序列,其中地址addr 1到addr k分别是有序序列中的最低到最高地址。例如,数据向量可以按数据向量从主机103接收的次序依序(例如,相继)写入到空闲位置225

‑

1到225

‑

k的序列。

40.相应数据向量可以依序写入在相应的第一可用空闲位置的序列中。例如,vector 1和vector 2可以从主机103依序接收,且位置225

‑

1到225

‑

k的序列可以是存储器拼片220

‑

1中的可用空闲位置。因而,vector 1可以写入到第一可用空闲位置225

‑

1,且vector 2可以随后写入到在位置225

‑

1之后的第一可用空闲位置225

‑

2。应注意,从主机103连续接收的接下来的k

‑

2个数据向量vector 3到vector k可以分别依序写入到位置225

‑

3到225

‑

k,即位置225

‑

2之后的后续可用空闲位置,如图2b中所示。

41.在一些实例中,存储器拼片220

‑

1到220

‑

m可以是有序序列,其中存储器拼片220

‑

1到220

‑

m分别是有序序列中的第一个到第m个存储器拼片。例如,存储器拼片220

‑

1到220

‑

m可依序写入。

42.vector(k+1)可以在vector k在位置225

‑

k中写入之后接收,且因此在拼片220

‑

1全满之后接收。例如,vector(k+1)可以在存储器拼片序列中的第一可用空闲存储器拼片220

‑

2中写入,例如,在存储器拼片220

‑

2中的位置225

‑

1到225

‑

k的序列中的第一可用空闲位置225

‑

1中写入,如图2b中所示。

43.在一些实例中,k+1个数据向量vector 1到vector(k+1)可以响应于在控制器104处从主机103依序接收的k+1个写入命令而分别写入。例如,写入命令可分别指定逻辑地址,且l2p映射表113可分别将前k个逻辑地址映射到拼片220

‑

1中的物理地址addr 1到addr k,并将第k+1逻辑地址映射到拼片220

‑

2中的地址addr 1。

44.在一些实例中,控制器104可响应于接收到写入命令,例如来自主机103的前述k+1个写入命令中的第一写入命令,使cam 206写入启用序列存储器拼片220

‑

1到220

‑

m中的第一可用存储器拼片220。例如,第一可用存储器拼片可以是具有至少一个空闲位置的序列中的第一存储器拼片。

45.接着,控制器104可以使先前在写入启用的存储器拼片中写入的所有数据向量复制到缓冲器cam的对应区域。例如,控制器可使cam 206读取先前在写入启用的存储器拼片中写入的所有数据向量,并将读取的数据向量输出到控制器104。然后,控制器104可将从cam 206读取的数据向量发送到缓冲器cam,并使缓冲器cam在缓冲器cam的对应区域中写入数据向量。

46.控制器104可使cam 206随后将在命令中指定的数据向量写入在写入启用的存储器拼片中的第一可用空闲位置中,并使缓冲器cam将在命令中指定的数据向量写入到缓冲器cam中的区域,使得cam 206和缓冲器cam并行写入数据向量,直到缓冲器cam结束在缓冲器cam中的区域中写入数据向量为止。控制器104可将拼片的位置的地址映射到区域的地址,并在cam 206继续在写入启用的存储器拼片中写入数据向量时查询区域而不是拼片。响应于结束在写入启用的存储器拼片中写入数据向量,控制器104可使拼片的位置的地址到区域的地址的映射无效,和/或从区域中去除数据向量。

47.在实例中,vector 1和vector 2先前可能已经写入在拼片220

‑

1中,如图2a中所示。随后,控制器104可接收写入vector 3到vector k的写入命令。控制器104可使vector 1和vector 2复制到缓冲器cam中的区域,并使cam 206和缓冲器cam并行地在拼片220

‑

1中和在缓冲器cam中的区域中写入vector 3到vector k,直到缓冲器cam结束在缓冲器cam中的区域中写入vector 3到vector k为止。

48.控制器104可将拼片220

‑

1的位置的地址映射到区域的地址,并在cam 206继续在存储器拼片220

‑

1中写入vector 3到vector k时查询区域而不是拼片220

‑

1。响应于cam 206结束在拼片220

‑

1中写入vector 3到vector k,控制器104可使拼片220

‑

1的位置的地址到区域的地址的映射无效和/或从区域中去除数据向量。

49.替代地,响应于确定存储器拼片220

‑

1被数据向量完全填充,控制器104可使拼片220

‑

1的位置的地址到区域的地址的映射无效和/或从区域中去除数据向量,如图2b中所示。例如,控制器104可跟踪拼片220

‑

1的填充程度(例如,通过跟踪拼片220

‑

1的使用百分比)。控制器104可使缓冲器cam查询缓冲器cam中的区域而不是使cam 206查询拼片220

‑

1,只要拼片220

‑

1被数据向量部分地填充即可,不管拼片220

‑

1是不是写入启用和/或有源地写入。例如,控制器104可使缓冲器cam在缓冲器cam的区域中维持数据向量的副本,直到拼片220

‑

1被完全填充为止。

50.应注意,在拼片220

‑

1的位置的地址到缓冲器cam中的区域的地址的映射无效和/或从缓冲器cam中的区域去除vector 1到vector k之后,控制器可使cam 206并行地向存储器拼片220

‑

2中的位置225

‑

1和缓冲器cam中的区域写入vector(k+1),直到vector(k+1)写入在缓冲器cam中为止。控制器104可将存储器拼片220

‑

2映射到缓冲器cam中的区域。当cam 206继续在存储器拼片220

‑

2中写入vector(k+1)时和/或在存储器拼片220

‑

2被数据向量完全地填充之前,控制器104可使缓冲器cam查询缓冲器cam中的vector(k+1)。此外,cam 206可查询完全填充的拼片220

‑

1,并且缓冲器cam可并行地查询对应于存储器拼片220

‑

2的缓冲器cam中的区域。

51.在一些实例中,主机103可发送在存储先前写入的数据向量的存储器拼片中的位置中写入新数据向量的写入命令,例如,以便更新(例如,重写)先前写入的数据向量。例如,写入命令可包含通过l2p表113映射到存储vector 1的位置225

‑

1的逻辑地址。响应于写入命令,控制器104可在第一可用空闲位置写入新数据向量。例如,第一可用空闲位置可以是图2a的存储器拼片220

‑

1中的位置225

‑

3或图2b的存储器拼片220

‑

2中的位置225

‑

2。接着,控制器104可以修改l2p表113,以将逻辑地址重新映射到图2a的拼片220

‑

1中的位置225

‑

3或图2b的拼片220

‑

2中的位置225

‑

2。

52.图3a是根据本公开的若干实施例的对应于特定写入阶段的缓冲器cam 310的一部

分的框图。图3b是根据本公开的若干实施例的对应于在图3a的所述特定写入阶段之后的特定写入阶段的缓冲器cam 310的一部分的框图。例如,缓冲器cam 310可以是cam 110。在一些实例中,图3a的特定写入阶段可对应于图2a的特定写入阶段,且图3b的特定写入阶段可对应于图2b的特定写入阶段。

53.缓冲器cam 310可具有易失性存储器单元的cam阵列331,例如sram存储器单元,其可存储来自各种主要cam中的各种存储器拼片的向量,例如cam 106

‑

1到106

‑

8和/或cam 206。来自相应存储器拼片的向量可以存储在相应区域330

‑

1到330

‑

4中。例如,区域可存储来自当前正在写入和/或部分填充的存储器拼片的数据向量。尽管在图3a和3b的实例中示出四个区域,但是可存在任何数目个区域,例如,取决于其数据向量可能需要存储在缓冲器cam 310中的存储器拼片的数目。

54.区域330

‑

1到330

‑

4可分别对应于缓冲器cam 310中的地址范围332

‑

1到332

‑

4。相应存储器拼片的地址可分别映射到地址范围332

‑

1到332

‑

4。例如,应注意,来自图2a和2b的存储器拼片220

‑

1的向量可以存储在区域330

‑

1中,且存储器拼片220

‑

1的地址可以映射到地址范围332

‑

1。

55.来自相应存储器拼片的相应数据向量可以存储在对应于相应存储器拼片的相应区域中的相应位置中。例如,每个相应位置可包含可存储相应数据向量的相应易失性存储器单元群组。每个相应区域中的相应位置可具有地址范围332中对应于相应区域的地址。每个相应区域中的位置可对应于相应存储器拼片中的位置。

56.例如,区域330

‑

1中的位置335

‑

1到335

‑

k可分别对应于存储器拼片220

‑

1中的位置225

‑

1到225

‑

k,并且可分别具有地址范围332

‑

1中的地址addr bc1到addr bck。在一些实例中,存储器拼片220

‑

1的地址addr 1到addr k可分别映射到区域330

‑

1的地址addr bc1到addr bck。

57.应注意,vector 1和vector 2可以并行地在拼片220

‑

1和区域330

‑

1中写入,直到结束在区域330

‑

1中写入vector 1和vector 2为止。当继续在存储器拼片220

‑

1中写入vector 1和vector 2时和/或只要存储器拼片220

‑

1被数据向量部分地填充,可以查询区域330

‑

1中的vector 1和vector 2,如图2a中所示。

58.在一些实例中,响应于写入启用存储器拼片220

‑

1以在存储器拼片220

‑

1中写入vector 3到vector k,vector 1和vector 2可以复制到区域330

‑

1中,如先前结合图2b所论述。在将vector 1和vector 2复制到区域330

‑

1中之后,vector 3到vector k可以并行地在存储器拼片220

‑

1和区域330

‑

1中写入,如图2b和3b中所示,直到结束在区域330

‑

1中写入vector 3到vector k为止。

59.例如,vector 3到vector k可以并行地在位置225

‑

3到225

‑

k和位置335

‑

3到335

‑

k中分别写入,直到完成在位置335

‑

3到335

‑

k中写入vector 3到vector k为止。当继续在拼片220

‑

1中写入vector 3到vector k时和/或在结束在存储器拼片220

‑

1中写入vector 3到vector k使得存储器拼片220

‑

1被数据向量完全地填充之前,可以查询区域330

‑

1中的vector 3到vector k,如图2b中所示。响应于存储器拼片220

‑

1被数据向量完全地填充,控制器104可使拼片220

‑

1的地址和地址范围332

‑

1之间的映射无效,和/或可使缓冲器cam 310从区域330

‑

1中去除vector 3到vector k。

60.图4是根据本公开的若干实施例的cam 440的简化框图。例如,cam 440可配置为主

要cam或缓冲器cam。cam 440包含可耦合到输入数据寄存器444的cam阵列442。例如,cam阵列442可以是例如其中cam 440是主要cam的cam阵列218,或例如其中cam 440是缓冲器cam的cam阵列331。cam阵列442可存储数据(例如,呈所存储的数据向量形式),并且输入数据寄存器444可从控制器404(例如,可以是控制器104)接收输入数据向量,以与所存储的数据向量比较。例如,所存储的数据向量可通过输入数据向量查询。在cam 440是缓冲器cam的实例中,cam阵列222可以是具有sram单元的sram存储器阵列。在cam 440是主要cam的实例中,cam阵列442可以是具有非易失性存储器单元的非易失性存储器阵列,例如电阻可变存储器单元(例如,以交叉点方式布置)。

61.cam 440可具有可引导cam 440的内部操作并且可管理cam阵列442的控制电路系统445(例如,控制状态机)。控制电路系统445可通过控制接口446从控制器404接收控制信号。例如,通过使控制电路系统445比较输入数据向量与存储在cam阵列442中的数据向量,控制器404可使控制电路系统445利用输入数据向量查询存储在cam阵列442中的数据向量。控制器404还可使控制电路系统445将数据向量写入在cam阵列442中。在一些实例中,控制器445可包含先前结合图1a描述的匹配验证电路系统。

62.检测器449可通过线450

‑

1到450

‑

k(例如,匹配线)耦合到cam阵列442。例如,相应线450

‑

1到450

‑

k中的每一个可对应于存储在cam阵列442中的相应数据向量。例如,在cam 440是主要cam的实例中,相应线450

‑

1到450

‑

k可分别对应于拼片的相应数据向量,例如拼片220

‑

1的vector 1到vector k。在cam 440是缓冲器cam的实例中,相应线450

‑

1到450

‑

k可分别对应于缓冲器cam中的区域中的相应数据向量,例如区域330

‑

1中的vector 1到vector k。

63.检测器449可检测所存储的数据向量是否匹配输入数据向量,并且可针对每个相应的所存储数据向量生成指示相应的所存储数据向量是否匹配输入数据向量的相应结果(例如,数据位)。

64.例如,如图4中所示,检测器449可生成具有值逻辑一(1)的数据位,指示相应的所存储数据向量匹配输入数据向量,以及具有值逻辑零(0)的数据位,指示相应的所存储数据向量与输入数据向量失配(例如,不匹配)。但是,本公开不限于此,并且逻辑1和逻辑0的作用可以反过来。在一些实例中,向量比较结果可以组合以形成具有对应于每个所存储向量的分量(例如,1或0)的结果(例如,输出)向量452。

65.检测器449可配置成使每个相应的所存储向量的地址与结果向量452(例如,其相应分量的)相应结果相关联(例如,相联系)。在一些实例中,检测器449可具有耦合到线450

‑

1到450

‑

k中的每一个的感测放大器(例如,在图4中未示出)。例如,每个感测放大器可配置成生成逻辑1或0,这取决于感测放大器检测到匹配还是不匹配。结果向量452和分量的相关联地址可以发送到输入/输出(i/o)缓冲器454以通过接口455输出到控制器404。

66.在cam 440是缓冲器cam的实例中,结果向量452可响应于查询的是缓冲器cam而不是主要cam而输出到控制器404。应注意,与结果向量452的分量相关联的地址可以映射到主要cam中的数据向量的地址。在一些实例中,控制器404可使相应逻辑地址与主要cam中的数据向量的地址相关联,并且可将结果向量输出到主机,例如主机103。

67.图5示出根据本公开的若干实施例的非易失性cam的一部分。例如,图5示出主要cam的非易失性cam阵列的部分,例如可以是拼片220的存储器拼片520。存储器拼片520可具

有一定数量的数据平面,例如数据向量平面560

‑

1到560

‑

j。

68.每个数据向量平面560可具有字线562

‑

1到562

‑

8。字线562

‑

1到562

‑

8中的每一个可跨越位线563

‑

1到563

‑

8。因而,每个数据向量平面560可以是交叉点数据向量平面。在字线和位线的每个交叉点处可存在存储器单元564,例如电阻可变存储器单元。在一些实例中,共同耦合到位线563的存储器单元群组(例如,存储器单元列)可存储数据向量。例如,分别共同耦合到位线563

‑

1到563

‑

8的存储器单元列可分别存储数据向量565

‑

1到565

‑

8。尽管示出八个位线和八个字线,但是可存在任何数目个位线和字线。

69.每个向量平面560中的位线563

‑

1到563

‑

8可分别耦合到感测放大器567

‑

1到567

‑

8。感测放大器567

‑

1到567

‑

8可分别生成输入数据向量568与所存储的向量565

‑

1到565

‑

8的比较结果。例如,结果可以是结果向量569的分量。在一些实例中,可以每次针对一个平面将拼片中所存储的数据向量与输入数据向量466比较(例如,逐平面进行)。

70.图6示出根据本公开的若干实施例的存储在非易失性主要cam中的数据查询。例如,通过比较输入数据与所存储的数据来借助输入数据查询所存储的数据。例如,在图6中,输入数据向量668并行地与主要cam的向量平面660(例如,其可以是存储器拼片)中的数据向量665

‑

1到665

‑

8比较。例如,输入数据向量668可具有分别对应于位bit1到bit8的分量数据(例如,位)值00110011。

71.向量平面660可具有字线662

‑

1到662

‑

8。字线662

‑

1到662

‑

8中的每一个可跨越位线663

‑

1到663

‑

8。在字线和位线的每个交叉点处可存在存储器单元664,例如电阻可变存储器单元。尽管在图6的实例中示出八个位线和八个字线,但是实施例不限于特定数目的字线和/或位线。

72.数据向量665

‑

1到665

‑

8可分别存储在分别共同耦合到位线663

‑

1到663

‑

8的存储器单元列中。例如,每个相应列中的存储器单元664

‑

1到664

‑

8可分别耦合到字线662

‑

1到662

‑

8。在此实例中,数据向量665

‑

1(01111111)存储在耦合到位线663

‑

1的单元中,数据向量665

‑

2(11110111)存储在耦合到位线663

‑

2的单元中,数据向量665

‑

3(11111111)存储在耦合到位线663

‑

3的单元中,数据向量665

‑

4(11111101)存储在耦合到位线663

‑

4的单元中,数据向量665

‑

5(00110011)存储在耦合到位线663

‑

5的单元中,数据向量665

‑

6(00000000)存储在耦合到位线663

‑

6的单元中,数据向量665

‑

7(11111110)存储在耦合到位线663

‑

7的单元中,且数据向量665

‑

8(00000000)存储在耦合到位线665

‑

8的单元中。应注意,相应数据向量665

‑

1到665

‑

8中的每一个的相应数据值(例如,分量)分别存储在存储器单元664

‑

1到664

‑

8中。

73.位线663

‑

1到663

‑

8可分别耦合到感测放大器667

‑

1到667

‑

8。感测放大器667

‑

1到667

‑

8可分别生成输入数据向量668与所存储的向量665

‑

1到665

‑

8的比较结果。例如,结果可以是结果向量669(00001000)的分量。

74.输入数据向量668的bit1到bit8可分别与分别存储在耦合到数据线663

‑

1到663

‑

8中的每一个的存储器单元664

‑

1到664

‑

8中的数据比较。位值逻辑0可通过跨存储器单元施加电压差(例如分界电压vdm1)与存储在存储器单元664中的数据比较。位值逻辑1可通过跨存储器单元施加分界电压vdm2与存储在存储器单元664中的数据比较。

75.例如,vdm1可对应于输入位值逻辑0,vdm2可对应于输入位值逻辑1。在一些实例中,分界电压可以是施加到耦合到存储器单元的位线的电压减去施加到耦合到存储器单元

的字线的电压。应注意,在本实例中,vdm1和vdm2具有相反极性,其中vdm1具有负极性,vdm2具有正极性。但是,本公开不限于此。

76.在一些实例中,存储器单元664可经历响应于跨存储器单元664施加vdm1的切换事件,例如阈值事件(例如,转折事件),或响应于跨存储器单元664施加vdm2的切换事件。例如,存储器单元664可从一种导电性状态例如低导电性状态(例如,高电阻状态)切换到另一导电性状态,例如高导电性状态(例如,低电阻状态)。

77.在一些实例中,经历响应于分界电压的切换事件的存储器单元可被视为存储与对应于分界电压的输入数据值不匹配的数据值。例如,存储逻辑1的存储器单元可经历响应于跨存储器单元施加vdm1(例如,对应于输入逻辑0)的切换事件,存储逻辑0的存储器单元可经历响应于跨所述存储器单元施加vdm2(例如,对应于输入逻辑1)的切换事件。

78.在此实例中,不经历响应于分界电压的切换事件的存储器单元可被视为存储与对应于分界电压的输入数据值匹配的数据值。例如,存储逻辑0的存储器单元可不经历响应于跨所述存储器单元施加vdm1的切换事件,存储逻辑1的存储器单元可不经历响应于跨所述存储器单元施加vdm2的切换事件。但是,应注意,在其它实例中,切换事件可指示匹配,无切换事件可指示不匹配。

79.应注意,如果存储在数据向量665的至少一个存储器单元中的数据不匹配输入数据向量668的对应位,那么数据向量665可被视为与输入数据向量668不匹配。通过感测可在感测放大器的输出电压中反映的电流变化,感测放大器667可感测对应数据向量665的一或多个存储器单元所经历的切换事件。因此,感测放大器可通过感测切换事件而感测耦合到感测放大器的数据向量和输入数据向量668之间的不匹配。例如,感测放大器可响应于感测到切换事件而生成(例如,输出)逻辑0,指示耦合到感测放大器的数据向量和输入数据向量668之间不匹配。感测放大器可响应于没有感测到切换事件而生成逻辑1,指示耦合到感测放大器的数据向量和输入数据向量668之间匹配。

80.在一些实例中,在对应于第一比较阶段的第一时间段期间,输入数据向量668的一部分可与数据向量665

‑

1到665

‑

8的对应部分比较,并且在对应于第二比较阶段的第二时间段期间,输入数据向量668的其余部分可与数据向量665

‑

1到665

‑

8的对应部分比较。在第一阶段期间,具有逻辑0的输入数据向量668的bit1、bit2、bit5和bit6可分别与存储在数据向量665

‑

1到665

‑

8中的每一个的存储器单元664

‑

1、664

‑

2、664

‑

5和664

‑

6中的数据值通过跨那些存储器单元施加vdm1同时跨其余存储器单元664

‑

3、664

‑

4、664

‑

7和664

‑

8施加例如零伏特来进行比较。

81.在第二阶段期间,具有逻辑1的输入数据向量668的bit3、bit4、bit7和bit8可分别与存储在数据向量665

‑

1到665

‑

8中的每一个的存储器单元664

‑

3、664

‑

4、664

‑

7和664

‑

8中的数据值通过跨那些存储器单元施加vdm2同时跨其余存储器单元664

‑

1、664

‑

2、664

‑

5和664

‑

6施加例如零伏特来进行比较。但是,本公开不限于此,且vdm1和vbm2可以并行施加(例如,在同一阶段期间)。

82.在一些实例中,vdm1可替换为将存储器单元写入(例如,编程)到对应于逻辑0的电阻状态的写入电压。例如,写入电压在负义上可大于vdm1。在一些实例中,vdm2可替换为将存储器单元写入到对应于逻辑1的电阻状态的写入电压。例如,写入电压在正义上可大于vdm2。在一些实例中,可以在第一阶段期间施加写入逻辑0的写入电压,并且可以在第二阶

段期间施加写入逻辑1的写入电压。但是,本公开不限于此,并且相应写入电压可以并行施加(例如,在同一阶段期间)。

83.主要cam的cam阵列可包含二维(2d)和/或三维(3d)阵列结构,例如交叉点阵列结构。存储器单元(例如,存储器单元564和664)可包含例如各种类型的电阻可变存储元件和/或切换元件。例如,单元可以是相变随机存取存储器(pcram)单元或电阻性随机存取存储器(rram)单元。

84.如本文中所使用,存储元件是指存储器单元的可编程部分。举例来说,主要cam可以是3d交叉点装置,其单元可包含其中存储元件与开关元件串联耦合的“堆叠”结构,并且其可在本文中称为3d相变材料和开关(pcms)装置。3d pcms单元可包含例如与二端子硫族化物基开关元件(例如,双向阈值开关(ots))串联耦合的二端子硫族化物基存储元件。在一些实例中,存储器单元可以是自选存储器(ssm)单元,其中单个材料可同时用作开关元件和存储元件。ssm单元可包含硫族化物合金;但是,实施例不限于此。

85.作为非限制性实例,所公开的非易失性cam的存储器单元可包含相变材料(例如,相变硫族化物合金),例如铟(in)

‑

锑(sb)

‑

碲(te)(ist)材料(例如,in2sb2te5、in1sb2te4、in1sb4te7等)或锗(ge)

‑

锑(sb)

‑

碲(te)(gst)材料(例如,ge2sb2te5、ge1sb2te4、ge1sb4te7等)。如本文中所使用,加连字符的化学组合物符号指示包含在特定混合物或化合物中的元素,并且意在表示涉及所指示的元素的所有化学计量。其它存储器单元材料可包含gete、in

‑

se、sb2te3、gasb、insb、as

‑

te、al

‑

te、ge

‑

sb

‑

te、te

‑

ge

‑

as、in

‑

sb

‑

te、te

‑

sn

‑

se、ge

‑

se

‑

ga、bi

‑

se

‑

sb、ga

‑

se

‑

te、sn

‑

sb

‑

te、in

‑

sb

‑

ge、te

‑

ge

‑

sb

‑

s、te

‑

ge

‑

sn

‑

o、te

‑

ge

‑

sn

‑

au、pd

‑

te

‑

ge

‑

sn、in

‑

se

‑

ti

‑

co、ge

‑

sb

‑

te

‑

pd、ge

‑

sb

‑

te

‑

co、sb

‑

te

‑

bi

‑

se、ag

‑

in

‑

sb

‑

te、ge

‑

sb

‑

se

‑

te、ge

‑

sn

‑

sb

‑

te、ge

‑

te

‑

sn

‑

ni、ge

‑

te

‑

sn

‑

pd和ge

‑

te

‑

sn

‑

pt,以及各种其它材料。

86.在本公开的先前详细描述中,参考形成本公开的一部分的附图,并且在附图中通过图示的方式示出可以如何实践本公开的数个实施例。足够详细地描述这些实施例,使得所属领域的一般技术人员能够实践本公开的实施例,并且应理解,可利用其它实施例且可在不脱离本公开的范围的情况下进行过程、电气和/或结构性改变。

87.如本文中所使用,“数个”或“一定数量的”某物可指这类事物中的一或多个。例如,数个或一定数量的存储器单元可指一或多个存储器单元。“多个”某物意指两个或更多个。如本文中所使用,术语“耦合”可包含在没有中间元件的情况下电耦合、直接耦合和/或直接连接(例如,通过直接物理接触),或在有中间元件的情况下间接耦合和/或连接,或无线耦合。术语耦合可进一步包含彼此协作或相互作用(例如,成因果关系)的两个或更多个元件。如本文所用,同时执行的多个动作指至少部分地在特定时间段内重叠的动作。

88.尽管已在本文中说明并描述了具体实施例,但所属领域的一般技术人员应了解,经计算以实现相同结果的布置可取代所示的具体实施例。本公开意在涵盖本公开的数个实施例的调适或变化。应理解,以上描述是以说明方式而非限制方式进行的。在查阅以上描述后,以上实施例和本文未具体描述的其它实施例的组合对于所属领域的技术人员来说将是显而易见的。本公开的若干实施例的范围包含其中使用上述结构和方法的其它应用。因此,本公开的数个实施例的范围应当参考所附权利要求书连同此类权利要求有权享有的等效物的完整范围来确定。

89.在实前述具体实施方式中,出于简化本公开的目的,将一些特征一并归到单个实

施例中。本公开的这一方法不应被理解为反映以下意图:本公开的所公开实施例必须使用比每个权利要求中明确陈述的特征更多的特征。相反,如所附权利要求书所反映,本发明主题在于单个所公开实施例的不到全部的特征。因此,所附权利要求书特此并入于具体实施方式中,其中每项权利要求就其自身而言作为单独实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1