用于非易失性存储器系统的自定时感测架构的制作方法

用于非易失性存储器系统的自定时感测架构

1.优先权声明

2.本技术要求于2020年5月20日提交的标题为

″

self-timed sensing architecture for a non-volatile memory system

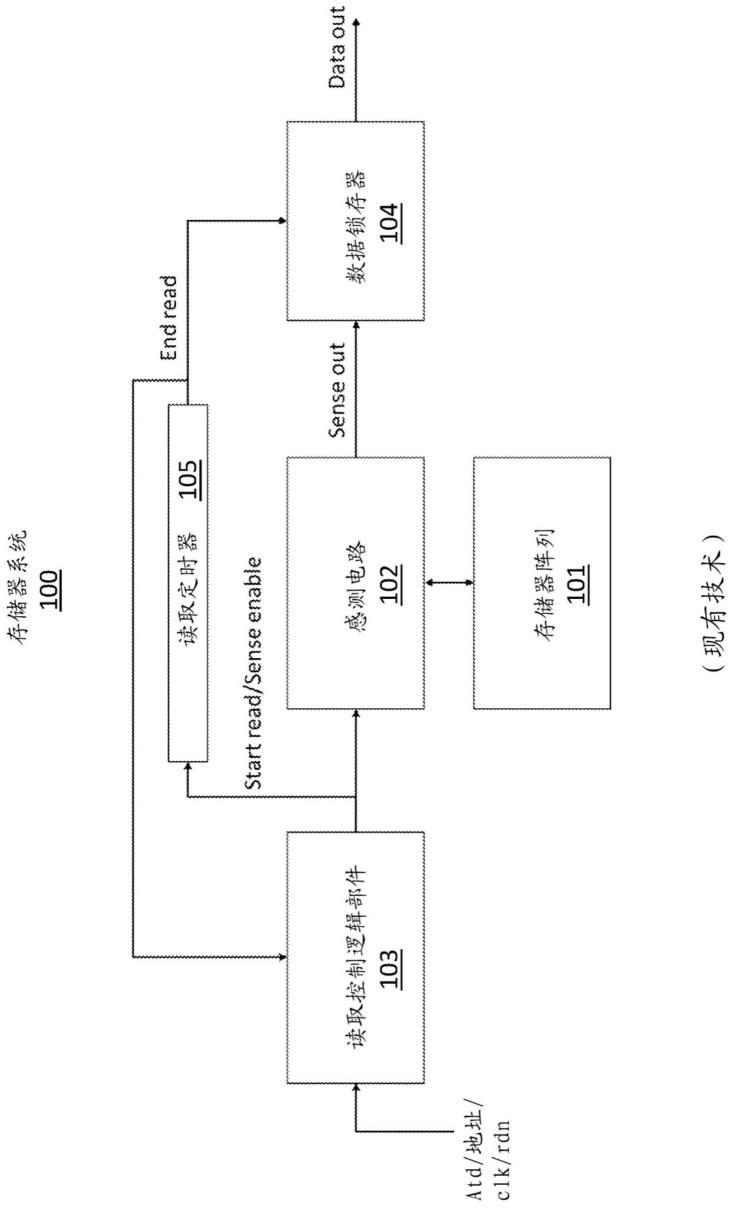

″

的美国临时专利申请号63/027,472和2020年11月11日提交的标题为

″

self-timed sensing architecture for a non-volatile memory system

″

的美国专利申请号17/095,331的优先权。

技术领域

3.公开了用于读取非易失性单元阵列中所选单元的自定时感测架构。感测电路在已经从所选单元获得稳定的感测值时生成信号,其中稳定的感测值指示存储在所选单元中的值。所述信号指示感测操作的结束,导致稳定的感测值被输出,作为读取操作的结果。

背景技术:

4.在非易失性存储器系统中,读取操作用于确定已经存储在所选存储器单元中的数据值。这需要使用感测电路,所述感测电路常常通过将由所选存储器单元消耗的电流与参考电流或与由参考单元消耗的电流进行比较,来

″

感测

″

存储在所述单元中的值。此操作涉及定时事件的序列,所述定时事件的目标是将存储在所选存储器单元中的模拟信息转换成数字输出。

5.在现有技术中,读取定时是由试图匹配实际读取持续时间的定时器实施。然而,阵列中不同的所选存储器单元的实际读取持续时间可以由于电压供应、操作温度、半导体工艺和单元电流的差异而具有宽的变化。因此,读取定时器设计需要足够的裕度来适应这些变化。因此,现有技术中的读取速度比其实际能力慢。由于比所需读取持续时间长,所以功率消耗增加。

6.图1示出了现有技术存储器系统100的读取部分。读取控制逻辑部件103接收读取操作的地址、地址转换检测信号(atd)、时钟信号(clk)和读取使能信号(rdn),它们的某种组合通过由读取控制逻辑部件103输出的被标记为

″

start read/sense enable

″

的信号而并行地控制感测电路102和读取定时器105的使能。读取定时器105限定读取持续时间,并且利用被标记为

″

end read

″

的信号在给定预定义延迟之后在数据锁存器104中锁存存储器阵列101中所选单元的感测状态(标记为

″

sense out

″

)。数据锁存器104的数字输出指示感测电路102在存储器阵列101的所选单元中读取的值。过早锁存数据可能导致读取失败,而晚锁存数据导致性能差。读取定时器105所实施的读取持续时间在设计阶段期间被确定并且结合上述宽的裕度。

7.现有技术的存储器系统100是低效的,因为读取定时器105所施加的读取持续时间由于上文所描述的因素必然大于所需的读取持续时间。

8.克服这些挑战的一个现有技术努力是在制造过程的晶片分选阶段期间以逐个裸片为基础对裸片执行校准修整。然而,这对制造过程增加了显著的时间和成本。此外,所述修整是在具有特定温度和特定电压供应的一个环境设置中进行,因此一定的裕度仍然需要

被包括在读取定时器105的设计中,以适应在现场操作中将经历的温度和电压供应变化。

9.需要一种经改进的系统用于读取非易失性存储器阵列中的所选单元。具体地,需要具有改进的读取定时的系统,所述读取定时也使功率消耗最小化,并且优选地在制造过程期间不需要校准修整。

技术实现要素:

10.公开了用于读取非易失性单元阵列中所选单元的自定时感测架构。感测电路在已经从所选单元获得稳定的感测值时生成信号,其中稳定的感测值指示存储在所选单元中的值。所述信号指示感测操作的结束,导致稳定的感测值被输出,作为读取操作的结果。

附图说明

11.图1示出了现有技术存储器系统。

12.图2示出了根据某些实施方案的存储器系统的实施方案。

13.图3示出了使用图2的存储器系统的读取操作的时序图。

14.图4示出了电流-电压电路。

15.图5示出了图4的电流-电压电路的时序图。

16.图6示出了比较器。

17.图7示出了自定时器的一个实施方案。

18.图8示出了图6a、图6b和图7的系统的时序图。

19.图9示出了图6a、图6b和图7的系统的另一时序图。

具体实施方式

20.图2示出了存储器系统200,其包括存储器阵列201、感测电路202、读取控制逻辑部件203、数据锁存器204和自定时器205。图3示出了由存储器系统200执行的典型读取操作的时序图300。

21.参考图2和图3,读取控制逻辑部件203接收读取操作的地址、地址转换检测信号(atd)、时钟信号(clk)和读取使能信号(rdn),它们的某种组合通过由读取控制逻辑部件203输出的被标记为

″

start read/sense enable

″

(sa_en)的信号而控制感测电路202的使能。感测电路202提供被标记为

″

sense out

″

的第一输出给数据锁存器204和自定时器205,并且提供被标记为

″

sense out_n

″

的第二输出给自定时器205。当信号start read/sense enable被读取控制逻辑部件203设置为活动(图示为活动高)时,感测电路202变为活动的。

22.在读取操作的初始阶段,sense out和sense out_n均等于

″0″

,因为这两个信号在该时间点不稳定,因为驱动sense out和sense out_n的内部信号被初始化在0v。如果存储器阵列201中的所选单元包含

″1″

,则sense out将变为

″1″

值并且sense out_n将保持在

″0″

。如果所选单元包含

″0″

,则sense out_n将变为

″1″

值,而sense out将保持在

″0″

。因此,一旦那些信号达到稳定状态,sense out_n和sense out就将处于相反的值。

23.在另选方案中,sense out和sense out_n可被初始化为vdd处的

″1″

,而不是

″0″

。如果存储器阵列201中的所选单元包含

″1″

,则sense out将保持在

″1″

值并且sense out_n将变为

″0″

。如果所选单元包含

″0″

,则sense out_n将保持在

″1″

值,而sense out将变为

″0″

。因此,一旦那些信号达到稳定状态,sense out_n和sense out就将处于相反的值。

24.在一个实施方案中,自定时器205用xor逻辑部件实施并且接收sense out和sense out_n。xor逻辑部件初始地在sense out和sense out_n均处于

″0″

时输出

″0″

,并且在sense out或sense out_n任一者响应于存储在存储器阵列201的所选单元中的值而变为

″1″

时输出

″1″

,这在图2和图3中被图示为被标记为

″

end read

″

的控制信号。当这种情况发生时,自定时器205的xor逻辑部件所输出的

″1″

将触发数据锁存器204,所述数据锁存器将锁存感测电路202所输出的sense out信号,并且将其呈现作为指示存储在存储器阵列201的所选单元中的值的数字形式的最终输出data out。此时,读取操作完成,并且感测电路202中的感测放大器可通过禁用信号se_en而被关断,从而与现有技术相比节省功率。

25.图4、图5和图6示出了感测电路202的实施方案的附加细节。

26.图4示出了电流-电压电路400,其是感测电路202的一部分。电流-电压电路400包括如图所示配置的nmos晶体管401、402、407和408以及pmos晶体管403、404、405和406。nmos晶体管401和402的栅极由读取控制逻辑部件203所生成的感测使能信号

″

sa_en

″

驱动,并且nmos晶体管407和408的栅极由读取控制逻辑部件203所生成的所述sa_en信号的逆反

″

sa_en_n

″

驱动。pmos晶体管403和404的栅极由读取控制逻辑部件203所生成的信号

″

charge_n

″

驱动,所述读取控制逻辑部件通过对地址转换检测信号atd和信号sa_en执行逻辑操作来生成charge_n。nmos晶体管401通过被标记为

″

bl_dwn

″

的位线耦接到存储器阵列201中的所选存储器单元409,并且nmos晶体管402通过被标记为

″

bl_up

″

的位线耦接到参考存储器单元410,所述参考存储器单元可位于存储器阵列201中或位于单独的参考存储器阵列中。在另选方案中,所选存储器单元409和参考存储器单元410的角色可颠倒(意味着单元409变为参考存储器单元,并且单元410变为所选存储器单元),这可能是有用的,例如如果所选存储器单元的位置改变到另一存储器单元库的话。

27.所选存储器单元409在其存储

″0″

值时消耗零电流,并且在其存储

″1″

值时,其消耗电流ir1。参考存储器单元410被编程为在读取操作期间消耗0与ir1之间的预定电流,诸如0.5*ir1。

28.在读取操作期间,晶体管401、402、403和404通过信号sa_en被设置为高电平并且charge_n被设置为低电平而被接通,如图5中所示,并且因此,节点mirror_dwn和mirror_up分别通过pmos晶体管403、404而被预充电到供电电压vdd附近的某一电压。sa_en被设置为高电平和charge_n被设置为低电平之间的时间差响应于atd脉冲持续时间或其衍生物。nmos晶体管407、408通过信号sa_en_n保持关断。然后,pmos晶体管403和404通过信号charge_n被设置为高电平而被关断,并且感测阶段开始。

29.所选存储器单元409和参考存储器单元410以反映存储在每一者中的值的量消耗电流。这使pmos晶体管405和406的栅极(分别连接到节点

″

mirror_dwn

″

和

″

mirror_up

″

)放电。如果所选存储器单元409处于

″1″

状态,则节点mirror_dwn将比节点mirror_up更快地放电。如果所选存储器单元409处于

″0″

状态,则节点mirror_up将比节点mirror_dwn更快地放电。图5示出了在所选存储器单元409包含

″0″

以及其包含

″1″

的情况下节点mirror_dwn和mirror_up的电压。

30.在图6中,感测电路202还包括比较器600。比较器包括nmos晶体管601、602、605、606、607、608、611和612以及pmos晶体管603、604、609、610、613和614,如图所示配置。图4的

节点mirror_dwn连接到pmos晶体管603的栅极,并且图4的节点mirror_up连接到pmos晶体管604的栅极,使得图4中的pmos晶体管405和图6中的pmos晶体管603形成一个电流镜,并且图4中的pmos晶体管406和图6中的pmos晶体管604形成另一电流镜。nmos晶体管601和602连接形成半锁存器。节点vdo和vdo_n初始地通过相应的下拉晶体管605和606通过读取控制逻辑部件203所生成的信号sa_latch_sa被设置为0v,所述信号sa_latch_sa具有与图5中的charge_n相同的定时,但相位相反,所述下拉晶体管一旦感测阶段开始就被关断。在另选实施方案中,信号sa_latch_sa由感测电路202响应于信号charge_n而生成。

31.如果所选存储器单元409处于

″1″

状态,则节点vdo将比节点vdo_n更快地被上拉至供电电压vdd,因为节点mirror_dwn将比节点mirror_up更快地放电。如果所选存储器单元409处于

″0″

状态,则节点vdo_n将比节点vdo更快地被上拉至供电电压vdd,因为节点mirror_up将比节点mirror_dwn更快地放电。

32.vdo和vdo_n中第一者被上拉至vdd将通过切换nmos晶体管601和602的半锁存状态而使另一节点放电。

33.晶体管对607和609、611和613、608和610、以及612和614各自形成反相器。比较器600的输出是sense out和sense out_n。

34.图7示出了xor逻辑功能的具体实施。xor逻辑部件700是自定时器205的实施方案。xor逻辑部件700包括反相器701和多路复用器702。反相器701和多路复用器702各自接收sense out作为输入。多路复用器702还接收反相器输出(其将是sense_out的逆反)作为输入。来自比较器600的sense out_n控制多路复用器702,并且多路复用器702输出控制信号end read。控制信号end_read在sense out和sense out_n是稳定的不同值时将等于1。也就是说,只有sense out和sense out_n相位相反持续长到足以传播通过xor逻辑部件700的时间,xor输出才将是稳定的

″1″

。xor逻辑部件是优选的,以拒绝sense out和sense out_n两者都为高或都为低的错误状态。这在图8中在时序图800中对于所选存储器单元409包含

″1″

的情况并且在图9中作为时序图900对于所选存储器单元409包含

″0″

的情况进行描绘。end read是自定时器205在读取操作稳定时生效的控制信号,并且来自感测电路202的数据可被数据锁存器204准确地锁存以用于输出。

35.控制信号end read可被发送给图2中的数据锁存器204,以锁存最终输出信号data out。控制信号end read还被馈送给读取控制逻辑部件203,并且作为响应,读取控制逻辑部件203禁用信号sa_en(图示为低),从而禁用感测电路202。

36.因此,与现有技术存储器系统100不同,存储器系统200的读取定时是自定义的,使得一旦读取数据稳定,数据就可从读取电路输出。与现有技术不同,不需要为每个读取操作添加定时裕度,这使得读取操作快得多。功率消耗被最小化,因为每当读取完成,感测放大器就被关断。测试时间被减少,因为不需要在制造期间执行读取定时的逐裸片修整。

37.应当指出,如本文所用,术语

″

在...上方

″

和

″

在...上

″

两者包容地包括

″

直接在...上

″

(之间未设置中间材料、元件或空间)和

″

间接在...上

″

(之间设置有中间材料、元件或空间)。类似地,术语

″

相邻

″

包括

″

直接相邻

″

(之间没有设置中间材料、元件或空间)和

″

间接相邻

″

(之间设置有中间材料、元件或空间),

″

安装到

″

包括

″

直接安装到

″

(之间没有设置中间材料、元件或空间)和

″

间接安装到

″

(之间设置有中间材料、元件或空间),并且

″

电耦接至

″

包括

″

直接电耦接至

″

(之间没有将元件电连接在一起的中间材料或元件)和

″

间接电

耦接至

″

(之间有将元件电连接在一起的中间材料或元件)。例如,

″

在衬底上方

″

形成元件可包括在两者间没有中间材料/元件的情况下在衬底上直接形成元件,以及在两者间有一个或多个中间材料/元件的情况下在衬底上间接形成元件。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1