闪存存储器的操作方法及装置与流程

1.本发明涉及集成电路设计领域,特别是涉及一种闪存存储器的操作方法及装置。

背景技术:

2.根据nand闪存中单个存储单元(cell)中可存放bit数量的差异,其可分为单级单元(slc)、多级单元(mlc)、三级单元(tlc)或四级单元(qlc)等不同类型。针对不同存储单元的数据操作需要调整对应的数据操作参数。例如,在对nand闪存进行数据读取操作时,需要针对不同类型或属于不同读取速度的页(page)的存储单元,选用不同的读取补偿特征值(read offset feature),以优化闪存的读操作性能,确保存储数据的稳定性。

3.目前,在设置nand闪存的读取补偿特征值等特征值时,一般可以根据onfi4.1协议的特征值表,通过专门的特征值设置序列写入特征值设置命令,以改变nand闪存的特征寄存器中所设特征值,使nand闪存在各类数据操作中都工作在最佳状态。例如,对于读取补偿特征值的设置,在兼有slc单元和tlc单元的nand闪存中,针对slc中的页和tlc中不同操作速度的页,通过特征值设置序列分别设置不同的读取补偿特征值,从而调整读取电平的分辨率及扫描范围等参数,以期维持较好的读操作性能。

4.然而,采用上述方法设置读取补偿特征值等特征值时,需要引入额外的特征值设置序列,这将使nand闪存在进行数据操作时耗费额外的操作时间,不利于提升器件的运行速率。

5.因此,有必要提出一种新的闪存存储器的操作方法及装置,解决上述问题。

技术实现要素:

6.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种闪存存储器的操作方法及装置,用于解决现有技术中设置特征值时需要额外的特征值设置序列并耗费额外操作时间的问题。

7.为实现上述目的及其它相关目的,本发明提供了一种闪存存储器的操作方法,其特征在于:

8.在对所述闪存存储器进行数据操作时,向所述闪存存储器写入操作命令;所述操作命令至少包括地址信息;所述地址信息包括数据地址和补偿特征值;

9.所述闪存存储器包括外围电路和存储单元阵列;所述外围电路根据所述补偿特征值调节数据操作参数并对所述存储单元阵列中所述数据地址处的数据执行所述数据操作。

10.作为本发明的一种可选方案,所述数据操作包括数据读取、数据写入或数据擦除。

11.作为本发明的一种可选方案,当所述数据操作为数据读取时,所述补偿特征值包括读取补偿特征值,所述数据操作参数包括读取电平及其分辨率和扫描范围。

12.作为本发明的一种可选方案,所述存储单元阵列中的存储单元包括单级单元和三级单元;所述三级单元包括下层页存储单元、中层页存储单元和上层页存储单元。

13.作为本发明的一种可选方案,所述读取补偿特征值包括:

14.对所述单级单元的读取的数据操作参数进行调节的单层读取补偿特征值;

15.对所述下层页存储单元的读取的数据操作参数进行调节的第一读取补偿特征值和第五读取补偿特征值;

16.对所述中层页存储单元的读取的数据操作参数进行调节的第二读取补偿特征值、第四读取补偿特征值和第六读取补偿特征值;

17.对所述上层页存储单元的读取的数据操作参数进行调节的第三读取补偿特征值和第七读取补偿特征值。

18.作为本发明的一种可选方案,所述读取补偿特征值在地址写入周期中依次排列为第一补偿区间、第二补偿区间和第三补偿区间;所述第一补偿区间用于写入所述单层读取补偿特征值、所述第一读取补偿特征值、所述第二读取补偿特征值和所述第三读取补偿特征值;所述第二补偿区间用于写入所述第四读取补偿特征值、所述第五读取补偿特征值和所述第七读取补偿特征值;所述第三补偿区间用于写入所述第六读取补偿特征值。

19.作为本发明的一种可选方案,在所述第三补偿区间后还设置有预留区间。

20.作为本发明的一种可选方案,所述数据地址包括行地址和列地址;在地址写入周期中,所述地址信息的序列依次排列为列地址、行地址和补偿特征值。

21.本发明还提供了一种闪存存储器装置,其特征在于,包括:外围电路和存储单元阵列;

22.所述外围电路包括数据寄存器和特征寄存器;

23.当所述闪存存储器进行数据操作时,向所述外围电路写入操作命令,所述操作命令至少包括地址信息,所述地址信息包括数据地址和补偿特征值;

24.所述数据寄存器用于存储所述数据地址;所述特征寄存器用于存储所述补偿特征值;

25.所述外围电路根据所述补偿特征值调节数据操作参数并对所述存储单元阵列中所述数据地址处的数据执行所述数据操作。

26.作为本发明的一种可选方案,所述外围电路还包括第一数据选择器和第二数据选择器;

27.所述第一数据选择器的输入端连接数据输入时钟信号和特征值输入时钟信号,输出端连接操作命令时钟信号;所述第二数据选择器的输入端连接数据信号和特征值信号,输出端连接操作命令信号。

28.如上所述,本发明提供一种闪存存储器的操作方法及装置,具有以下有益效果:

29.本发明在对闪存存储器进行数据操作时,将补偿特征值设置于地址信息中,无需额外引入特征值设置序列,从而大幅节省了闪存存储器数据操作时间,提升了器件性能。

附图说明

30.图1显示为本发明实施例一中执行读取操作前的地址写入周期的时序图。

31.图2显示为本发明实施例一中写入读取补偿特征值的时序示意图。

32.图3显示为本发明实施例二中提供的第一数据选择器的信号连接示意图。

33.图4显示为本发明实施例二中提供的第二数据选择器的信号连接示意图。

34.元件标号说明

35.101

ꢀꢀꢀꢀ

第一数据选择器

36.102

ꢀꢀꢀꢀ

第二数据选择器

具体实施方式

37.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其它优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

38.请参阅图1至图4。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,虽图示中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的形态、数量及比例可为一种随意的改变,且其组件布局形态也可能更为复杂。

39.实施例一

40.请参阅图1至图2,本实施例提供了一种闪存存储器的操作方法,其特征在于:

41.在对所述闪存存储器进行数据操作时,向所述闪存存储器写入操作命令;所述操作命令至少包括地址信息;所述地址信息包括数据地址和补偿特征值;

42.所述闪存存储器包括外围电路和存储单元阵列;所述外围电路根据所述补偿特征值调节数据操作参数并对所述存储单元阵列中所述数据地址处的数据执行所述数据操作。

43.在本实施例提供的闪存存储器的操作方法中,在对闪存存储器进行数据操作时,将补偿特征值设置于地址信息中,通过地址信息序列写入闪存存储器缓存中,因而无需引入额外的特征值设置序列。这将大幅节省闪存存储器的数据操作时间,提升器件性能。

44.作为示例,所述数据操作包括数据读取、数据写入或数据擦除。在本实施例中,所述数据操作为数据读取,即,当连接闪存存储器的主机(host)对闪存存储器发出读取命令时,闪存存储器的外围电路通过施加读取电平从存储单元阵列中读取数据。则所述补偿特征值包括读取补偿特征值(read offset feature),所述数据操作参数包括读取电平及其分辨率(resolution)和扫描范围(scan range)。通过闪存存储器的特征寄存器(feature register)中读取补偿特征值的变化,用于从存储单元阵列读取数据的数据操作参数将通过补偿调整为合适的值,从而增加读取操作成功率,确保存储器维持较好的读操作性能。

45.作为示例,在本实施例中,所述存储单元阵列中的存储单元包括单级单元(slc,single level cell)和三级单元(tlc,trinary level cell);所述三级单元包括下层页(lower page)存储单元、中层页(middle page)存储单元和上层页(upper page)存储单元。采用三级单元作为存储单元的nand闪存存储器具有体积小、价格便宜的优势,但其也存在读写速度较慢的劣势。与之相对,单级单元则具有读写速度快但体积大、成本高的特点。现有的nand闪存存储器一般会将三级单元作为主要存储单元,并设置部分单级单元作为缓存,以提升短时突发写入速度。因此,在现有的nand闪存存储器中一般都兼有单级单元和三级单元,其需要根据不同类型的存储单元,调整读取电平等数据操作参数。可选地,为了进一步降低nand闪存存储器的体积和成本,三级单元还可以被四级单元(qlc,quad level cell)所替代,则此类存储单元阵列中的存储单元将同时包括单级单元和四级单元。

46.在三级单元中,单个存储单元需要存放3bit数据,其二进制信息对应于8种状态,

需要7种参考电压(分别记为p1至p7)以隔离区分上述8种状态,单个存储单元在进行数据操作时将在上述8种状态内变化。根据不同存储单元在进行数据操作时速度的快慢,可以进一步将三级单元区分为下层页(lower page)存储单元、中层页(middle page)存储单元和上层页(upper page)存储单元。其中,下层页(lower page)存储单元的速度最快,中层页(middle page)存储单元次之,而上层页(upper page)存储单元的速度最慢。此外,当三级单元被替换为存放4bit数据的四级单元时,二进制信息对应于16种状态,则参考电压及分页的数量也将对应变化。

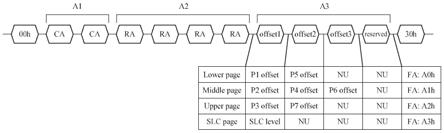

47.作为示例,如图1所示,在本实施例中,所述读取补偿特征值包括:

48.对所述单级单元的读取的数据操作参数进行调节的单层读取补偿特征值(slc level);

49.对所述下层页存储单元的读取的数据操作参数进行调节的第一读取补偿特征值(p1offset)和第五读取补偿特征值(p5 offset);

50.对所述中层页存储单元的读取的数据操作参数进行调节的第二读取补偿特征值(p2offset)、第四读取补偿特征值(p4 offset)和第六读取补偿特征值(p6 offset);

51.对所述上层页存储单元的读取的数据操作参数进行调节的第三读取补偿特征值(p3offset)和第七读取补偿特征值(p7 offset)。

52.闪存存储器在进行数据读取时,会先由主机向外围电路写入所读数据的地址并设置读取补偿特征值。如图1所示,是本实施例中执行读取操作前的地址写入周期的时序图。闪存存储器在00h至30h之间的多个时钟信号区间内执行地址写入操作。在图1中,在a1区间,将执行列地址(ca,column address)的写入;在a2区间,将执行行地址(ra,row address)的写入;在a3区间,将执行读取补偿特征值的写入。按照上述a1~a3的顺序将数据地址和补偿特征值依次写入外围电路缓存中。具体地,在a3区间中,所述读取补偿特征值在地址写入周期中依次排列为第一补偿区间(offset1)、第二补偿区间(offset2)和第三补偿区间(offset3)。如图1中的表格所示,所述第一补偿区间(offset1)用于写入所述单层读取补偿特征值(slc level)、所述第一读取补偿特征值(p1 offset)、所述第二读取补偿特征值(p2offset)和所述第三读取补偿特征值(p3 offset);所述第二补偿区间(offset2)用于写入所述第四读取补偿特征值(p4 offset)、所述第五读取补偿特征值(p5 offset)和所述第七读取补偿特征值(p7 offset);所述第三补偿区间(offset3)用于写入所述第六读取补偿特征值(p6offset)。此外,图1中通过特征值地址(fa,feature address),如a0h~a3h等,可对特征寄存器中上述地址对应的读取补偿特征值进行调整。由于所述闪存存储器中不同区域和类型的各存储单元在执行读取数据操作时都可以共享上述特征寄存器中的读取补偿特征值设置,因此本实施例提供的操作方法对于系统资源的占用也可以控制在较低水平。

53.作为示例,在所述第三补偿区间(offset3)后还设置有预留区间(reserved)。由于本实施例采用的是三级单元作为主要存储单元,因此offset1~3的三个补偿区间足以容纳所有的读取补偿特征值,表中还留有未使用空间(nu)。

54.此外,当后续产品更换为四级单元时,单个存储单元中将存在16种状态,对应的参考电压为15种,则通过本实施例所设置的offset1~3的三个补偿区间以及预留区间(reserved)也足以容纳四级单元的读取补偿特征值的写入。以此类推,在后续新开发的闪

存存储器中如进一步采用五层存储单元(flc)或更多层的存储单元替代四级单元,则所述预留区间(reserved)的数量还可以相应增加。

55.如图2所示,是写入读取补偿特征值的时序示意图。在图2中,dq信号代表了输入/输出信号;r/b代表了就绪/繁忙信号,外围电路在其低电平阶段将数据写入存储单元中;roic_offset1[7:0]、roic_offset2[7:0]和roic_offset3[7:0]等三路信号分别是在dq信号的oa1、oa2和oa3阶段输入并写入特征寄存器的读取补偿特征值数据。dq信号的oa1、oa2和oa3阶段分别对应于图1中的offset1、offset2和offset3区间。roic_offset1[7:0]、roic_offset2[7:0]和roic_offset3[7:0]中的8’h0代表无数据,而oa1、oa2和oa3分别代表了输入dq信号中的oa1、oa2和oa3的读取补偿特征值数据。wefeat_clk_sw信号代表了用于同步上述三路信号写入特征寄存器的时钟信号。在dq信号的oa3至30h的区间内,以wefeat_clk_sw信号作为时钟信号,同步roic_offset1[7:0]、roic_offset2[7:0]和roic_offset3[7:0]等三路信号写入特征寄存器。

[0056]

在完成00h至30h之间的地址写入操作后,所述闪存存储器的外围电路将根据所述数据地址从所述存储单元阵列读取数据,而读取数据所用的数据操作参数也将根据读取补偿特征值进行调整。

[0057]

在本实施例中,在对闪存存储器进行数据操作时,将补偿特征值设置于地址信息中,无需额外引入特征值设置序列,从而大幅节省了闪存存储器数据操作时间,提升了器件性能。

[0058]

实施例二

[0059]

请参阅图2至图4,本实施例提供了一种闪存存储器装置,其特征在于,包括:外围电路和存储单元阵列;所述外围电路包括数据寄存器和特征寄存器。

[0060]

其中,所述存储单元阵列中包含用于存储数据的存储单元,所述外围电路包含能够控制所述存储单元阵列进行读取、写入或擦除等数据操作的cmos逻辑电路。

[0061]

当所述闪存存储器进行数据操作时,向所述外围电路写入操作命令,所述操作命令至少包括地址信息,所述地址信息包括数据地址和补偿特征值。具体地,所述操作命令包括读取、写入或擦除等命令。当所述闪存存储器装置从主机(host)接收到所述数据操作命令时,所述外围电路将根据包含地址的数据操作命令对所述存储单元阵列进行读取、写入或擦除等数据操作。

[0062]

所述外围电路至少包括数据寄存器和特征寄存器。所述数据寄存器用于存储所述数据地址,所述特征寄存器用于存储所述补偿特征值。所述外围电路根据所述补偿特征值调节数据操作参数并对所述存储单元阵列中所述数据地址处的数据执行所述数据操作。

[0063]

作为示例,如图3和图4所示,所述外围电路还包括用于选择时钟信号的第一数据选择器101和用于选择数据信号的第二数据选择器102。

[0064]

如图3所示,是所述第一数据选择器101的信号连接示意图。所述第一数据选择器101的输入端连接数据输入时钟信号和特征值输入时钟信号,输出端连接操作命令时钟信号。具体地,所述第一数据选择器101用于控制所述外围电路中不同路时钟信号的切换。所述第一数据选择器101的地址输入端为wefeat_clk_sw信号,输入端分别为web clock信号和set_feat_lat_clk信号,输出端为we_feat_clk信号。根据wefeat_clk_sw信号的控制,输出端的we_feat_clk信号可从web clock信号和set_feat_lat_clk信号中选择一路信号输

出。

[0065]

如图4所示,是所述第二数据选择器102的信号连接示意图。所述第二数据选择器102的输入端连接数据信号和特征值信号,输出端连接操作命令信号。具体地,所述第二数据选择器102用于控制所述外围电路中不同路数据信号的切换。所述第二数据选择器102的地址输入端为wefeat_clk_sw信号,输入端分别为roic_offset<31:0>信号和db_io2lg<31:0>信号,输出端为roic_db_io2lg<31:0>信号。根据wefeat_clk_sw信号的控制,输出端的roic_db_io2lg<31:0>信号可从roic_offset<31:0>信号和db_io2lg<31:0>信号中选择一路信号输出。

[0066]

结合图2至图4可以看出,当wefeat_clk_sw信号为1时,所述第一数据选择器101的输入端切换为web clock信号,所述第二数据选择器102的输入端切换为roic_offset<31:0>信号,所述外围电路以web clock信号作为时钟信号,将包含读取补偿特征值的roic_offset<31:0>信号,即图2中的roic_offset1[7:0]、roic_offset2[7:0]和roic_offset3[7:0]写入特征寄存器。

[0067]

综上所述,本发明提供了一种闪存存储器的操作方法及装置,操作方法的特征在于:在对所述闪存存储器进行数据操作时,向所述闪存存储器写入操作命令;所述操作命令至少包括地址信息;所述地址信息包括数据地址和补偿特征值;所述闪存存储器包括外围电路和存储单元阵列;所述外围电路根据所述补偿特征值调节数据操作参数并对所述存储单元阵列中所述数据地址处的数据执行所述数据操作。本发明在对闪存存储器进行数据操作时,将补偿特征值设置于地址信息中,无需额外引入特征值设置序列,从而大幅节省了闪存存储器数据操作时间,提升了器件性能。

[0068]

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1