存储器装置的操作方法与流程

1.本发明是有关于一种存储器装置的操作方法,特别是有关于一种存储器装置的读取操作方法。

背景技术:

2.对于三维(3d)存储器装置而言,在对被选字线很多次读取周期后(例如100k读取周期后),该被选字线的相邻字线可能会遇到读取干扰(read disturbance)的问题。

3.经由分析后可得知,在该目标字线的预导通(pre-turn-on)期间被关闭时,如果该目标字线的通过电压(pass voltage,vpass)低于该目标字线的阈值的话,将会发生向下耦合效应(down-coupling effect)。这将会在该目标字线与其相邻字线之间很大造成通道电位差异(channel potential difference),且在其相邻字线造成很高的垂直电场(vertical electronic field)。导致热载子注入(hot carrier injection)更容易发生,进而造成读取干扰。

技术实现要素:

4.根据本发明一实施例,提出一种存储器装置的操作方法,包括:在一预导通期间,一相邻字线电压上升至一第一相邻字线电压;以及在该预导通期间结束后,该相邻字线电压从该第一相邻字线电压上升至一第二相邻字线电压。该第一相邻字线电压低于该第二相邻字线电压。该相邻字线电压施加到至少一相邻字线,该至少一相邻字线系相邻于一被选字线。

5.根据本发明另一实施例,提出一种存储器装置的操作方法,包括:在一预导通期间内,一被选字线电压上升到一第一被选字线电压,以及该被选字线电压从该第一被选字线电压以多阶下降,在多阶下降时,阶数多于2阶。

6.根据本发明又一实施例,提出一种存储器装置的操作方法,包括:在一预导通期间,一被选字线电压上升至一第一被选字线电压;以及从一第一时序至一第二时序,该被选字线电压从该第一被选字线电压以一平滑曲线下降。

7.为了对本发明的上述及其他方面有更好的了解,下文特举实施例,并配合所附附图详细说明如下:

附图说明

8.图1绘示根据本发明一实施例的存储器装置的功能方块图。

9.图2显示本发明一实施例的存储器阵列的三维(3d)电路图。

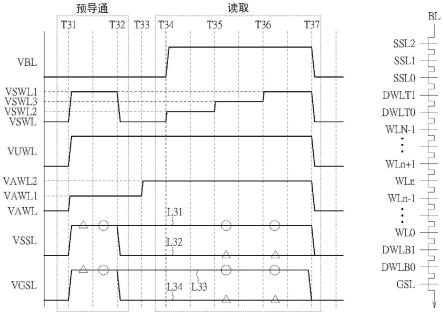

10.图3显示本发明第一实施例的存储器装置的读取操作波形图。

11.图4显示已知技术与本发明第一实施例的水平电场与垂直电场比较图。

12.图5显示已知技术与本发明第一实施例的阈值电压变化量对读取次数的关系曲线图。

13.图6a与图6b显示本发明第二实施例的存储器装置的两种读取操作波形图。

14.图7显示已知技术与本发明第二实施例的水平电场与垂直电场比较图。

15.图8显示已知技术与本发明第二实施例的阈值电压变化量对读取次数的关系曲线图。

16.图9显示本发明第三实施例的存储器装置的读取操作波形图。

17.图10显示已知技术与本发明第三实施例的水平电场与垂直电场比较图。

18.图11显示已知技术与本发明第三实施例的阈值电压变化量对读取次数的关系曲线图。

19.【符号说明】

20.100:存储器装置

21.110:控制器

22.120:存储器阵列

23.ssl0_0~ssl2_3:串选择线

24.dwlt1、dwlt0、dwlb1、dwlt1:冗余字线

25.wl0~wln-1:字线

26.bl0~bl3:位线

27.gsl0~gsl3:整体选择线

28.vbl:位线电压

29.vswl:被选字线电压

30.vuwl:未选字线电压

31.vawl:相邻字线电压

32.vssl:串选择线电压

33.vgsl:整体选择线电压

34.vswl1:第一被选字线电压

35.vswl2:第二被选字线电压

36.vswl3:第三被选字线电压

37.vawl1:第一相邻字线电压

38.vawl2:第二相邻字线电压

39.t31~t37:时序

40.bl:位线

41.ssl0~ssl2:串选择线

42.gsl:整体选择线

43.l31~l34、l41~l48:曲线

44.t601~t618:时序

45.vswl601:第一被选字线电压

46.vswl602:第二被选字线电压

47.vswl603:第三被选字线电压

48.vswl611:第一被选字线电压

49.vswl612:第二被选字线电压

50.vswl613:第三被选字线电压

51.vswl614:第四被选字线电压

52.vswl615:第五被选字线电压

53.l71~l78:曲线

54.t91~t97:时序

55.vswl91:第一被选字线电压

56.vswl92:第二被选字线电压

57.vswl93:第三被选字线电压

58.l101~l104:曲线

具体实施方式

59.本发明的技术用语系参照本领域的习惯用语,如本发明对部分用语有加以说明或定义,该部分用语的解释系以本发明的说明或定义为准。本发明的各个实施例分别具有一或多个技术特征。在可能实施的前提下,本领域技术人员可选择性地实施任一实施例中部分或全部的技术特征,或者选择性地将这些实施例中部分或全部的技术特征加以组合。

60.请参照图1,其绘示根据本发明一实施例的存储器装置的功能方块图。存储器装置100包括:控制器110与存储器阵列120。控制器110耦接至存储器阵列120。控制器110控制存储器阵列120的操作,例如读取操作等。

61.图2显示本发明一实施例的存储器阵列120的三维(3d)电路图。存储器阵列120包括:多条串选择线(ssl)(ssl0_0~ssl2_3)、多条冗余字线(dwlt1、dwlt0、dwlb1、dwlb0)、多条字线(wl0~wln-1,n为正整数)、多条位线(bl0~bl3)、多条整体选择线(gsl0~gsl3)与多个存储器单元。当知,图2乃是示范例,本发明并不受限于此。

62.通常而言,存储器阵列120会包括多个存储器方块(memory block)。各存储器方块包括,举例但不受限于,4个子方块(sub-block)。以图2而言,这些子方块sb0~sb3可分别被这些串选择线ssl0_0~ssl2_3与这些整体选择线gsl0~gsl3所独立选择。

63.图3显示本发明第一实施例的存储器装置的读取操作波形图。vbl代表位线电压;vswl代表被选字线电压;vuwl代表未选字线电压;vawl代表相邻字线电压;vssl代表串选择线电压;以及vgsl代表整体选择线电压。在底下说明中,以字线wln(n为整数,介于0~n-1之间)为「被选字线(目标字线)」,而相邻于被选字线wln的字线wln+1与wln-1则被称为「相邻字线」。被选字线电压vswl施加至被选字线,而相邻字线电压vawl则施加至相邻字线。

64.在本发明第一实施例中,在预导通期间,位线电压vbl处于低电压(亦可称为参考电压)(例如但不受限于,0v),而在读取期间,位线电压vbl转态至高电压(t34),且在读取期间结束时(t37),位线电压vbl转态至低电压。

65.在本发明第一实施例中,在预导通期间,被选字线电压vswl在时序t31上升至第一被选字线电压vswl1且在时序t32下降。在读取期间,被选字线电压vswl具有多阶电压(亦可称为多阶增加电压):第一阶电压(亦即第二被选字线电压vswl2),系从低电压在时序t34上升而得;以及第二阶电压(亦即第三被选字线电压vswl3)从第一阶电压(亦即第二被选字线电压vswl2)在时序t35上升而得。在时序t36时,被选字线电压vswl从第三被选字线电压vswl3上升至第一被选字线电压vswl1。在读取期间结束时,被选字线电压vswl转态至低电

压(时序t37)。第二被选字线电压vswl2与第三被选字线电压vswl3乃是读取电压。

66.在本发明第一实施例中,在预导通期间,未选字线电压vuwl在时序t31上升;在读取期间结束时,未选字线电压vuwl转态至低电压。

67.在本发明第一实施例中,在预导通期间,相邻字线电压vawl在时序t31上升至第一相邻字线电压vawl1。在预导通期间结束后,相邻字线电压vawl在时序t33从第一相邻字线电压vawl1上升至第二相邻字线电压vawl2。在读取期间结束时,相邻字线电压vawl转态至低电压。第一相邻字线电压vawl1低于第二相邻字线电压vawl2;第二相邻字线电压vawl2则相同于未选字线电压vuwl。

68.在本发明第一实施例中,在预导通期间,相邻字线的电压(第一相邻字线电压vawl1)低于被选字线的被选字线电压vswl,可减少在预导通期间的相邻字线的垂直电场。

69.在本发明第一实施例中,让相邻字线电压vawl上升至第二相邻字线电压vawl2的时序(t33)晚于预导通期间的结束,可减少在读取期间的相邻字线的水平电场。

70.在本发明第一实施例中,第一相邻字线电压vawl1的值,例如但不受限于,大于相邻字线的存储器单元的阈值电压,可介于2v~5v之间。

71.在本发明第一实施例中,第二相邻字线电压vawl2的值相关于通过电压(vpass)。例如,第二相邻字线电压vawl2的值,例如但不受限于,为足够高的通过电压(vpass),可介于6v~9v(或6v~10v)之间。

72.在本发明第一实施例中,在预导通期间,被选子方块的串选择线电压vssl(由曲线l31所标示)与未选子方块的串选择线电压vssl(由曲线l32所标示)在时序t31上升。而且,在预导通期间结束时,未选子方块的串选择线电压vssl(由曲线l32所标示)在时序t32下降。在读取期间结束时,被选子方块的串选择线电压vssl(由曲线l31所标示)下降。在读取期间内,未选子方块的串选择线电压vssl(由曲线l32所标示)则持续保持低电压。

73.在本发明第一实施例中,在预导通期间,被选子方块的整体选择线电压vgsl(由曲线l33所标示)与未选子方块的整体选择线电压vgsl(由曲线l34所标示)在时序t31上升。而且,在预导通期间结束时,未选子方块的整体选择线电压vgsl(由曲线l34所标示)在时序t32下降。在读取期间结束时,被选子方块的整体选择线电压vgsl(由曲线l33所标示)下降。在读取期间内,未选子方块的整体选择线电压vgsl(由曲线l34所标示)则持续保持低电压。

74.图4显示已知技术与本发明第一实施例的水平电场与垂直电场比较图。曲线l41代表在预导通期间结束时,于已知技术存储器装置中(未应用本发明第一实施例的读取操作),在被选字线wln与相邻字线wln-1、wln+1的通道与ono(oxide-nitride-oxide,氧化物-氮化物-氧化物)之间的水平电场曲线图。曲线l42代表在相邻字线电压vawl上升至第二相邻字线电压vawl2(时序t33)时,于已知技术存储器装置中(未应用本发明第一实施例的读取操作),在被选字线wln与相邻字线wln-1、wln+1的通道与ono之间的水平电场曲线图。

75.曲线l43代表在预导通期间结束时,于已知技术存储器装置中(未应用本发明第一实施例的读取操作),在被选字线wln与相邻字线wln-1、wln+1处的ono与栅极之间的垂直电场曲线图。曲线l44代表在相邻字线电压vawl上升至第二相邻字线电压vawl2(时序t33)时,于已知技术存储器装置中(未应用本发明第一实施例的读取操作),在被选字线wln与相邻字线wln-1、wln+1处的ono与栅极之间的垂直电场曲线图。

76.曲线l45代表在预导通期间结束时,于本发明第一实施例中,在被选字线wln与相

邻字线wln-1、wln+1的通道与ono之间的水平电场曲线图。曲线l46代表在相邻字线电压vawl上升至第二相邻字线电压vawl2(时序t33)时,于本发明第一实施例中,在被选字线wln与相邻字线wln-1、wln+1的通道与ono之间的水平电场曲线图。

77.曲线l47代表在预导通期间结束时,于本发明第一实施例中,在被选字线wln与相邻字线wln-1、wln+1处的ono与栅极之间的垂直电场曲线图。曲线l48代表在相邻字线电压vawl上升至第二相邻字线电压vawl2(时序t33)时,于本发明第一实施例中,在被选字线wln与相邻字线wln-1、wln+1处的ono与栅极之间的垂直电场曲线图。

78.比较曲线l43与曲线l47可知,本发明第一实施例的读取操作可以有效减少相邻字线的垂直电场,进而减少读取干扰。

79.图5显示已知技术与本发明第一实施例的阈值电压变化量对读取次数的关系曲线图。由图5可看出,本发明第一实施例可以减少阈值电压变化量,进而减少读取干扰。

80.图6a与图6b显示本发明第二实施例的存储器装置的两种读取操作波形图。在图6a与图6b中,位线电压vbl、未选字线电压vuwl、串选择线电压vssl与整体选择线电压vgsl的波形原则上相同或相似于图3的位线电压vbl、未选字线电压vuwl、串选择线电压vssl与整体选择线电压vgsl的波形,故其细节在此省略。

81.请参考图6a。在本发明第二实施例中,在预导通期间,被选字线电压vswl在时序t601上升到第一被选字线电压vswl601且在时序t602以多阶电压下降(亦可称为多阶降低电压)。被选字线电压vswl在时序t602从第一被选字线电压vswl601下降至第二被选字线电压vswl602,被选字线电压vswl在时序t603从第二被选字线电压vswl602下降至第三被选字线电压vswl603,被选字线电压vswl在时序t604从第三被选字线电压vswl603下降至低电压,被选字线电压vswl在时序t605从低电压上升至第一被选字线电压vswl601。其中,时序603、604与605位于读取期间内。在读取期间结束时(t606),被选字线电压vswl转态至低电压。其中,第二被选字线电压vswl602与第三被选字线电压vswl603亦可当成读取电压。

82.请参考图6a。在本发明第二实施例中,在预导通期间开始时,相邻字线电压vawl上升且在读取期间结束时下降。

83.请参考图6b。在本发明第二实施例中,在预导通期间,被选字线电压vswl在时序t611上升到第一被选字线电压vswl611且在时序t612以多阶下降。被选字线电压vswl在时序t612从第一被选字线电压vswl611下降至第二被选字线电压vswl612,被选字线电压vswl在时序t613从第二被选字线电压vswl612下降至第三被选字线电压vswl613,被选字线电压vswl在时序t614从第三被选字线电压vswl613下降至低电压。图6b的被选字线电压vswl的多阶下降乃是相似于图6a的被选字线电压vswl的多阶下降。

84.被选字线电压vswl在时序t615从低电压上升至第四被选字线电压vswl614。被选字线电压vswl在时序t616从第四被选字线电压vswl614上升至第五被选字线电压vswl615。被选字线电压vswl在时序t617从第五被选字线电压vswl615上升至第一被选字线电压vswl611。图6b的被选字线电压vswl的多阶上升(在读取期间)乃是相似于图3的被选字线电压vswl的多阶上升(在读取期间)。

85.在读取期间结束时(t618),被选字线电压vswl转态至低电压。其中,第二被选字线电压vswl612、第三被选字线电压vswl613、第四被选字线电压vswl614与第五被选字线电压vswl615亦可当成读取电压。

86.图6b的相邻字线电压vawl波形相同或相似于图6a的相邻字线电压vawl波形,故其细节在此省略。

87.在本发明第二实施例中,第一被选字线电压/vswl611高于被选字线wln的多个存储器单元的最高阈值电压,例如,第一被选字线电压vswl601/vswl611可为6v~10v之间。

88.在本发明第二实施例中,在多阶下降时,第二被选字线电压vswl602/vswl612低于第一被选字线电压vswl601/vswl611,第三被选字线电压vswl603/vswl613低于第二被选字线电压vswl602/vswl612,其余可依类推。

89.在本发明第二实施例中,在多阶下降时,阶段至少要多于2阶。

90.图7显示已知技术与本发明第二实施例的水平电场与垂直电场比较图。曲线l71代表在预导通期间结束时,于已知技术存储器装置中(未应用本发明第二实施例的读取操作),在被选字线wln与相邻字线wln-1、wln+1处的通道与ono之间的水平电场曲线图;曲线l72代表在时序t605/t615处,于已知技术存储器装置中(未应用本发明第二实施例的读取操作),在被选字线wln与相邻字线wln-1、wln+1处的通道与ono之间的水平电场曲线图。曲线l73代表在预导通期间结束时,于已知技术存储器装置中(未应用本发明第二实施例的读取操作),在被选字线wln与相邻字线wln-1、wln+1处的ono与栅极之间的垂直电场曲线图;曲线l74代表在时序t605/t615处,于已知技术存储器装置中(未应用本发明第二实施例的读取操作),在被选字线wln与相邻字线wln-1、wln+1处的ono与栅极之间的垂直电场曲线图。曲线l75代表在预导通期间结束时,于本发明第二实施例存储器装置中,在被选字线wln与相邻字线wln-1、wln+1处的通道与ono之间的水平电场曲线图;曲线l76代表在时序t605/t615时,于本发明第二实施例存储器装置中,在被选字线wln与相邻字线wln-1、wln+1处的通道与ono之间的水平电场曲线图。曲线l77代表在预导通期间结束时,于本发明第二实施例存储器装置中,在被选字线wln与相邻字线wln-1、wln+1处的ono与栅极之间的垂直电场曲线图;曲线l78代表在时序t605/t615处,于本发明第二实施例存储器装置中,在被选字线wln与相邻字线wln-1、wln+1处的ono与栅极之间的垂直电场曲线图。

91.比较曲线l71与l75可知,本发明第二实施例的读取操作可以有效减少在被选字线wln的水平电场,进而减少读取干扰。比较曲线l73与l77可知,本发明第二实施例的读取操作可以有效减少被选字线wln的垂直电场,进而减少读取干扰。

92.图8显示已知技术与本发明第二实施例的阈值电压变化量对读取次数的关系曲线图。由图8可看出,本发明第二实施例可以减少阈值电压变化量,进而减少读取干扰。

93.图9显示本发明第三实施例的存储器装置的读取操作波形图。在图9中,位线电压vbl、未选字线电压vuwl、相邻字线vawl、串选择线电压vssl与整体选择线电压vgsl的波形原则上相同或相似于图6a或图6b的位线电压vbl、未选字线电压vuwl、相邻字线vawl、串选择线电压vssl与整体选择线电压vgsl的波形,故其细节在此省略。

94.在本发明第三实施例中,在预导通期间,被选字线电压vswl在时序t91上升至第一被选字线电压vswl91。从时序t92至时序t93,被选字线电压vswl从第一被选字线电压vswl91以平滑曲线下降至低电压。在本发明一可能实施例中,平滑曲线例如但不受限于,为直线。

95.在本发明第三实施例中,时序t92至时序t93之间的时间间隔大于1μs,例如,是介于1μs~10μs之间。

96.在本发明第三实施例中,在读取期间,被选字线电压vswl有多阶电压:第一阶电压(亦即第二被选字线电压vswl92),系从低电压在时序t94上升;以及第二阶电压(亦即第三被选字线电压vswl93)从第一阶电压(亦即第二被选字线电压vswl92)在时序t95上升。在时序t96时,被选字线电压vswl上升至第一被选字线电压vswl91。在读取期间结束时,被选字线电压vswl转态至低电压(时序t97)。第二被选字线电压vswl92与第三被选字线电压vswl93乃是读取电压。

97.图10显示已知技术与本发明第三实施例的水平电场与垂直电场比较图。曲线l101代表在预导通期间结束时,于已知技术存储器装置中(未应用本发明第三实施例的读取操作),在被选字线wln与相邻字线wln-1、wln+1处的通道与ono之间的水平电场曲线图。曲线l102代表在预导通期间结束时,于已知技术存储器装置中(未应用本发明第三实施例的读取操作),在被选字线wln与相邻字线wln-1、wln+1处的ono与栅极之间的垂直电场曲线图。曲线l103代表在时序t93处,于本发明第三实施例存储器装置中,在被选字线wln与相邻字线wln-1、wln+1处的通道与ono之间的水平电场曲线图。曲线l104代表在时序t93处,于本发明第三实施例存储器装置中,在被选字线wln与相邻字线wln-1、wln+1处的ono与栅极之间的垂直电场曲线图。

98.比较这些曲线l101~l104可知,本发明第三实施例的读取操作可以有效减少被选字线wln的水平电场与垂直电场,进而减少读取干扰。

99.图11显示已知技术与本发明第三实施例的阈值电压变化量对读取次数的关系曲线图。由图11可看出,本发明第三实施例可以减少阈值电压变化量,进而减少读取干扰。

100.上述该第一至第三实施例可以分别独立实施,或者组合实施。亦即,第一与第二实施例可以组合实施;或者,第一与第三实施例可以组合实施。此皆在本发明保护范围内。

101.由上述说明可知,本发明上述这些实施例可以有效减缓被选字线的不正常读取干扰。

102.至此,已经结合附图对本公开实施例进行了详细描述。

103.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1