记忆体阵列与记忆体系统的制作方法

1.本揭露是关于一种记忆体,特别是关于一种记忆体阵列与一种记忆体系统。

背景技术:

2.诸如计算机、可携式装置、智能电话、物联网(internet of thing;iot)装置等电子装置的发展促使了对于记忆体装置的需求增加。大体而言,记忆体装置可为挥发性记忆体装置及非挥发性记忆体装置。挥发性记忆体装置可在提供电力时储存数据,但一旦切断电力则可能丢失所储存的数据。不同于挥发性记忆体装置,非挥发性记忆体装置即使在切断电力之后亦能保留数据,但速率比挥发性记忆体装置慢。

技术实现要素:

3.本揭露的一态样是提供一种记忆体阵列,包含:第一记忆体单元组(set)与第二记忆体单元组、第一开关群(group)、第二开关群、以及第三开关群。其中,每一记忆体单元组延伸而越过记忆体阵列的多个层,每一层包含第一记忆体单元组的记忆体单元与第二记忆体单元组的记忆体单元。第一开关群包含多个开关,每一开关包含连接至第一记忆体单元子集(subset)的多个第一电极的第一电极,以及第二电极。第二开关群包含多个开关,每一开关包含连接至第二记忆体单元子集的多个第一电极的第一电极,以及第二电极。第三开关群包含多个开关,每一开关包含连接至第一全域位元线的第一电极,以及连接至第一开关群的第二电极以及第二开关群的第二电极的第二电极。

4.本揭露的另一态样是提供一种记忆体阵列,包含:第一记忆体单元组与第二记忆体单元组、第一开关群、第二开关群、第三开关群、以及第四开关群。其中,每一记忆体单元组延伸而越过记忆体阵列的多个层,每一层包含第一记忆体单元组的记忆体单元与第二记忆体单元组的记忆体单元。第一开关群包含多个开关,每一开关包含第一电极,以及连接至全域选择线的第二电极。第二开关群包含多个开关,每一开关包含:第一电极,以及连接至全域选择线的第二电极。第三开关群包含多个开关,每一开关包含:连接至第一开关群的第一电极的第一电极,以及连接至第一记忆体单元子集的多个第一电极的第二电极。第四开关群包含多个开关,每一开关包含:连接至第二开关群的第一电极的第一电极,以及连接至第二记忆体单元子集的多个第一电极的第二电极。

5.本揭露的又一态样是提供一种记忆体系统,包含记忆体阵列以及控制器。其中,记忆体阵列包含:具有多个开关的第一开关群;具有耦接至第一区域选择线的多个第一电极与耦接至第一开关群的开关的多个第二电极的第一记忆体单元组;以及具有耦接至第二区域选择线的多个第一电极与耦接至第一开关群的开关的多个第二电极的第二记忆体单元组。控制器是连接至此记忆体阵列,且控制器是用以捺跳(toggle)第一开关群的这些开关中的至少一开关,以电性耦接全域位元线至第一记忆体单元组的第二电极。

附图说明

6.下文参考以下附图或示图详细地描述本解决方案的各个示例性实施例。仅出于图示的目的提供示图,且示图仅描绘本解决方案的示例性实施例,以便于读者理解本解决方案。因此,示图不应限制本解决方案的广度、范畴或适用性。应指出,出于清晰及易于图示的目的,这些示图未按比例绘制。

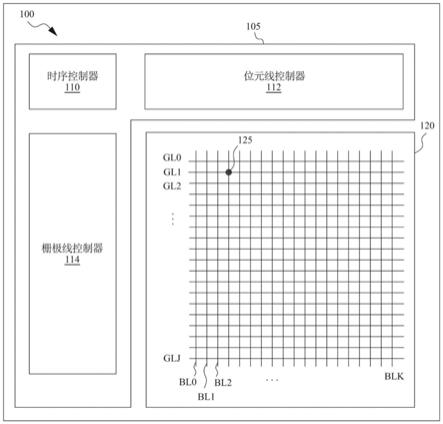

7.图1是根据本揭露的一实施例的记忆体系统的示意图;

8.图2是根据本揭露的一实施例的三维记忆体阵列的示意图;

9.图3a是根据一实施例的三维记忆体阵列210的部分的示意图,此三维记忆体阵列210包含耦接至全域位元线(global bit line;gbl)及全域选择线(global select line;gsl)以降低电容负载的开关;

10.图3b是根据一实施例的三维记忆体阵列210的部分的示意图,此三维记忆体阵列210包含耦接至全域位元线gbl以降低电容负载的开关;

11.图3c是根据一实施例的三维记忆体阵列210的部分的示意图,此三维记忆体阵列210包含耦接至区域选择线lsl以降低电容负载的开关;

12.图4是根据一实施例的三维记忆体阵列400的部分的示意图,此三维记忆体阵列400包含将位元格阵列分成多个单元以降低电容负载的开关;

13.图5是根据一实施例的三维记忆体阵列500的部分的示意图,此三维记忆体阵列500包含设计为用于bl/sl驱动器增强的一或多者的选择器输入及选择器输出;

14.图6是根据一些实施例的存取及/或操作记忆体单元及/或记忆体阵列的方法的流程图;

15.图7是根据本揭露的一些实施例的计算系统700的例示性方块图。

16.【符号说明】

17.100:记忆体系统

18.105:记忆体控制器

19.110:时序控制器

20.112:位元线控制器

21.114:栅极线控制器

22.120:记忆体阵列

23.125:记忆体单元

24.210a、210n-1、210n:记忆体阵列

25.310[00]、310[01]、310[02]、310[03]、310[04]、310[05]、310[06]、310[07]、310[08]:记忆体单元的子集

[0026]

400、500:记忆体阵列

[0027]

402、410、418、426、434、502、510、516、524:选择器输出

[0028]

404、408、412、416、420、424、428、432、504、508、512、514、518、522:选择器输入

[0029]

406、414、422、430、506、520:位元格阵列

[0030]

600:方法

[0031]

602、604、606、608、610:操作

[0032]

700:计算系统

[0033]

705:主机装置

[0034]

710:记忆体装置

[0035]

715:输入装置

[0036]

720:输出装置

[0037]

725a、725b、725c:接口

[0038]

730a、730n:中央处理单元核心

[0039]

735:标准单元应用

[0040]

740:记忆体控制器

[0041]

745:记忆体阵列

[0042]

bl、bl0、bl1、bl2、blk:位元线

[0043]

gbl[0]:全域位元线

[0044]

gl0、gl1、gl2、glj:栅极线

[0045]

gsl[0]:全域选择线

[0046]

lbl_l[0]、lbl_r[0]:区域位元线

[0047]

lsl_l[0]、lsl_r[0]:区域选择线

[0048]

m:记忆体单元

[0049]

set_l、set_r:第一记忆体单元组

[0050]

ss1_l、ss1_r:第一垂直串开关

[0051]

ss2_l、ss2_r:第二垂直串开关

[0052]

sb_l、sb_c、sb_r:开关

[0053]

sl:选择线

[0054]

wl:字元线

具体实施方式

[0055]

以下揭露提供用于实现所提供标的物的不同特征的许多不同的实施例或实例。为简化本揭露,下文描述元件和布置的特定实例。当然,这些仅为实例,且不意欲具有限制性。举例而言,在下文的描述中,在第二特征上方或其上形成第一特征可包含第一及第二特征直接相接触而形成的实施例,亦可包含第一及第二特征之间形成额外特征以使得第一及第二特征可不直接相接触的实施例。此外,本揭露可在各个实例中重复元件符号及/或字母。这种重复是出于简洁和清晰的目的,且本身并未规定所论述的各个实施例及/或构造具有关系。

[0056]

另外,为便于描述,在本文可使用诸如“在...之下”、“在...下方”、“下部”、“在...上方”、“上部”及类似者的空间相对性术语,以表述如图中所示的一元件或特征与另一(或另一些)元件或特征的关系。除附图中所描绘的定向外,空间相对性术语意欲涵盖使用中或操作中装置的不同定向。设备可以其他方式经定向(旋转90度或以其他定向),因此可同样地解读本文中使用的空间相对性描述词。

[0057]

根据一些实施例,记忆体系统包含一或多个开关(有时称为“选择栅极”)以耦接(couple)或去耦接(decouple)区域线与全域线。区域线可为连接至二个或多个记忆体单元的金属轨道。举例而言,区域线可为连接至记忆体单元的第一电极(例如:漏极(或源极)电

极)的区域选择线(例如:图3a中的lsl[00])。举例而言,区域线可为连接至记忆体单元的第二电极(例如:源极(或漏极)电极)的区域位元线(例如:图3a中的lbl[00])。全域线可为金属轨道,其可通过开关电性耦接至一或多个所选择的区域线。举例而言,全域线可为全域选择线(例如图3a中的gsl[0]),其可通过开关电性耦接至二个或多个区域选择线。举例而言,全域线可为全域位元线(例如:图3a中的gbl[0]),其可通过开关电性耦接至二个或多个区域位元线。

[0058]

有利地,采用所揭露的开关的记忆体系统可具有若干益处。在一态样中,全域线与区域线之间的开关可单独地配置或操作以电性耦接或去耦接各别的区域线与全域线。通过耦接所选择的区域线至全域线,连接至所选择的区域线的一组记忆体单元的子集可电性耦接至全域线,而连接至未选择的区域线的此组记忆体单元的另一子集可从全域线电性去耦接。由此,全域线可具有对应至此组记忆体单元的所选择的子集的电容负载,而非对应至整组记忆体单元的电容负载。据此,具有许多记忆体单元的记忆体单元组可通过全域线来配置或操作以具有对应至记忆体单元组的子集的低电容负载。

[0059]

通过降低电容负载,记忆体系统的运行速率可被提升,同时降低记忆体系统的电力消耗。此外,本揭露的技术及/或特征亦可提高位元线及/或选择线之间的屏蔽,并且降低布线复杂性。

[0060]

以下针对记忆体架构进行更进一步地叙述。

[0061]

图1是根据本揭露的实施例的记忆体系统100的示意图。在一些实施例中,记忆体系统100是实施为集成电路。在一些实施例中,记忆体系统100包含记忆体控制器105与记忆体阵列120。记忆体阵列120可包含以二维或三维阵列排列的多个储存电路或记忆体单元125。每一记忆体单元125可连接至对应的栅极线gl与对应的位元线bl。每一栅极线gl可包含任何导电性材料。记忆体控制器105可通过栅极线gl与位元线bl并根据电子信号写入数据至记忆体阵列120或自记忆体阵列120读取数据。在其他实施例中,记忆体系统100包含相较图1中所示的元件较多或较少或相等数量的元件。

[0062]

记忆体阵列120为储存数据的硬件元件。在一态样中,记忆体阵列120是实施为半导体记忆体装置。记忆体阵列120包含多个储存电路或记忆体单元125。在一些实施例中,记忆体阵列120包含栅极线gl0、gl1...glj,每一栅极线沿第一方向延伸,以及包含位元线bl0、bl1...blk,每一位元线沿第二方向延伸。栅极线gl与位元线bl可为导电性金属或导电性轨道。每一栅极线gl可包含字元线与控制线。在一态样中,每一记忆体单元125是连接至对应的栅极线gl与对应的位元线bl,且可通过对应的栅极线gl与对应的位元线bl并根据电压或电流来操作。在一态样中,每一记忆体单元125可为非挥发性记忆体单元。在一些实施例中,记忆体阵列120包含额外的线(例如:感测线、参考线、参考控制线、或电力轨道等)。

[0063]

记忆体控制器105为控制记忆体阵列125的操作的硬件元件。在一些实施例中,记忆体控制器105包含位元线控制器112、栅极线控制器114、以及及时序控制器110。在一配置中,栅极线控制器114是通过记忆体阵列120的一或多个栅极线gl来提供电压或电流的电路。在一态样中,位元线控制器112是通过记忆体阵列120的一或多个位元线bl来提供电压或电流的电路,且通过一或多个感测线感测来自记忆体阵列120的电压或电流。在一配置中,时序控制器110为一电路,其向栅极线控制器114与位元线控制器112提供控制信号或时脉信号,以同步化位元线控制器112与栅极线控制器114的操作。位元线控制器112可连接至

记忆体阵列120的位元线bl与感测线,栅极线控制器114可连接至记忆体阵列120的栅极线gl。在一实例中,为将数据写入至记忆体单元125,栅极线控制器114通过连接至记忆体单元125的栅极线gl对记忆体单元125施加电压或电流,且位元线控制器112通过连接至记忆体单元125的位元线bl对记忆体单元125施加对应于待储存数据的电压或电流。在一实例中,为了从记忆体单元125读取数据,栅极线控制器114通过连接至记忆体单元125的栅极线gl对记忆体单元125施加电压或电流,且位元线控制器112通过连接至记忆体单元125的感测线或位元线感测对应于由记忆体单元125所储存的数据的电压或电流。在一些实施例中,记忆体控制器105包含相较图1中所示的元件较多、较少或不等数量的元件。

[0064]

图2是根据一实施例的三维记忆体阵列210a...210n的示意图。在一些实施例中,记忆体阵列120包含记忆体阵列210a...210n。每一记忆体阵列210包含以三维阵列排列的多个记忆体单元125。在一些实施例中,每一记忆体阵列210可包含同样数量的记忆体单元125。在一些实施例中,二个或多个记忆体阵列210可包含不同数量的记忆体单元125。在一配置中,记忆体阵列210a...210n沿着z方向堆叠。每一记忆体阵列210可具有在记忆体阵列210的一侧上的位元线bl以及具有在记忆体阵列210的相对侧上的选择线sl。在一些实施例中,二个相邻的记忆体阵列210可共用选择线sl。在一些实施例中,二个相邻的记忆体阵列210可共用位元线bl。举例而言,记忆体阵列210n-1、210n共用一组选择线sl或电性耦接至此组选择线sl。举例而言,记忆体阵列210n-2、210n-1共用一组位元线bl或电性耦接至此组位元线bl。通过共用选择线sl及/或位元线bl,可减少以通过选择线sl及/或位元线bl来施加信号的记忆体控制器105的驱动器的数量,以实现面积效率。在一些实施例中,记忆体阵列120包含额外的记忆体阵列,其可具有与图2中所示的选择线sl及/或位元线bl不同的选择线sl及/或位元线bl。

[0065]

以下针对具有嵌入式开关的记忆体系统进行更进一步地叙述。

[0066]

图3a是根据一实施例的三维记忆体阵列210的部分的示意图,此三维记忆体阵列210包含耦接至全域位元线gbl与全域选择线gsl以降低电容负载的开关(有时称为“选择器”)。在图3a中,记忆体阵列可包含(例如:嵌入、植入或内固式)开关ss_l的群组(有时称为“开关ss_l”)、开关ss_r的群组(有时称为“开关ss_r”)及/或开关sb的群组(有时称为“开关sb”)。记忆体阵列210可包含第一记忆体单元组(例如:图3a中以“set_l”所示)以及第二记忆体单元组(例如:图3a中以“set_r”所示)。在一配置中,第一记忆体单元组包含记忆体单元的子集310[00]...310[03],其可经由开关sb的群组电性耦接至沿着y方向延伸的全域位元线gbl[0],且经由开关ss_l的群组耦接至亦沿着y方向延伸的全域选择线gsl[0]。在一配置中,第二记忆体单元组包含记忆体单元的子集310[04]...310[08],其可经由开关sb的群组电性耦接至全域位元线gbl[0],且经由开关ss_r的群组耦接至全域选择线gsl[0]。

[0067]

记忆体单元的每一子集310可包含沿z方向设置的f个数量的记忆体单元m(例如:图1中的记忆体单元125),其中f亦对应于记忆体210中平层(floors)或层(layers)的总数。每一组记忆体单元(例如:set_r、set_l)可包含比图3a中沿着y方向所示的数量更多的记忆体单元子集310。记忆体阵列210可包含比图3a中沿着x方向堆叠所示的数量更多的记忆体单元组。通过如图3a中所示来排列记忆体单元,可增加记忆体阵列210的储存密度。

[0068]

在一配置中,开关ss_l的群组(例如:网络、集合、多个)的一或多个开关可置于开关ss_l的群组的左侧,此开关的群组的其他开关可置于开关ss_l的群组的右侧。在一配置

中,开关ss_l的群组可包含沿着z方向设置的第一垂直串开关ss_l(图3a中以“ss1_l”表示)以及沿着z方向设置的第二垂直串开关ss_l(图3a中以“ss2_l”表示)。在一配置中,第一垂直串开关ss_l是置于开关ss_l的群组的左侧,第二垂直串开关ss_l是置于开关ss_l的群组的右侧,使得第一及第二垂直串彼此互相平行(或并排)。

[0069]

开关ss_l的群组的每一开关ss_l可根据其在开关的群组中的位置以及其在记忆体阵列210中的x-y-z位置来识别(例如:索引、参考、或标记等)。举例而言,如图3a所示,第一垂直串开关ss_l包含ss1_l[0][0][0]、ss1_l[0][0][1]、ss1_l[0][0][f-2]、以及ss1_l[0][0][f];第二垂直串开关ss_l包含ss2_l[0][0][0]、ss2_l[0][0][1]、ss2_l[0][0][f-2]、以及ss2_l[0][0][f]。

[0070]

在一配置中,开关ss_r的群组的一或多个开关可置于开关ss_r的群组的左侧,此开关的群组的其他开关可置于开关ss_r的群组的右侧。在一配置中,开关ss_r的群组可包含沿着z方向设置的第一垂直串开关ss_r(图3a中以“ss1_r”表示)以及沿着z方向设置的第二垂直串开关ss_r(图3a中以“ss2_r”表示)。在一配置中,第一垂直串开关ss_r是置于开关ss_r的群组的左侧,第二垂直串开关ss_r是置于开关ss_r的群组的右侧,使得第一及第二垂直串互相平行(或并排)。

[0071]

开关ss_r的群组的每一开关ss_r可根据其在开关的群组中的位置以及其在记忆体阵列210中的x-y-z位置来识别(例如:索引、参考、或标记等)。举例而言,图3a所示,第一垂直串开关ss_r包含ss1_r[0][0][0]、ss1_r[0][0][1]、ss1_r[0][0][f-2]、以及ss1_r[0][0][f];第二垂直串开关ss_r包含ss2_r[0][0][0]、ss2_r[0][0][1]、ss2_r[0][0][f-2]、以及ss2_r[0][0][f]。

[0072]

在一配置中,开关sb的群组的一或多个开关sb可置于开关sb的群组的左侧、开关sb的群组的右侧、或开关的群组的中央(例如:其他开关位于左侧,且其他开关位于右侧)。在一配置中,开关sb的群组可包含沿着z方向设置的第一垂直串开关sb(图3a中以“sb_l”表示)、沿着z方向设置的第二垂直串开关sb(图3a中以“sb_c“表示)以及沿着z方向设置的第三垂直串开关sb(图3a中以“sb_r”表示)。在一配置中,第一垂直串开关sb是置于开关sb的群组的左侧,第二垂直串开关sb是置于开关sb的群组的中心,第三垂直串开关是置于开关sb的群组的右侧,使得第一、第二、以及第三垂直串互相平行(或并排)。

[0073]

开关sb的群组的每一开关sb可根据其在开关的群组中的位置以及其在记忆体阵列210中的x-y-z位置来识别(例如:索引、参考、或标记等)。举例而言,如图3a所示,第一垂直串开关sb包含sb_l[0][0][0]、sb_l[0][0][1]、sb_l[0][0][f-2]及sb_l[0][0][f];第二垂直串开关sb包含sb_c[0][0][0]、sb_c[0][0][1]、sb_c[0][0][f-2]、以及sb_c[0][0][f];第三垂直串开关sb包含sb_r[0][0][0]、sb_r[0][0][1]、sb_r[0][0][f-2]、以及sb_r[0][0][f]。

[0074]

每一记忆体单元m可为挥发性记忆体单元、非挥发性记忆体单元、或可储存数据的任何记忆体单元。每一记忆体单元m可实施为晶体管,诸如:金属氧化物半导体场效晶体管(metal-oxide-semiconductor field effect transistor;mosfet)、全环绕式栅极fet(gate-all-around fet;gaafet)、或鳍式场效晶体管(fin field-effect transistor;finfet)。每一记忆体单元m可包含耦接至区域选择线lsl(例如:lsl_l[x]或lsl_r[x])的第一电极(例如:漏极电极)、耦接至区域位元线lbl(例如:lbl_l[x]或lbl_r[x])的第二电极

(例如:源极电极)、以及耦接至对应字元线(例如:字元线wl[x][z])的第三电极(例如:栅极电极)。每一记忆体单元m可根据施加于记忆体单元m的栅极电极的电压来储存数据或传导电流。字元线wl[x][y]可沿着x方向延伸,以连接在不同组(例如:set_l、set_r)中的对应记忆体单元m的栅极电极至记忆体控制器(例如:栅极线控制器114)。

[0075]

在一配置中,记忆体单元m的子集310是平行连接在区域选择线lsl(例如:lsl_l[x]或lsl_r[x])与区域位元线lbl(例如:lbl_l[x]或lbl_r[x])之间。区域选择线lsl可为金属轨道,可在此处连接记忆体单元子集310的第一电极(例如:漏极电极)。区域位元线lbl可为金属轨道,可在此处连接记忆体单元子集310的第二电极(例如:源极电极)。

[0076]

参考图3a中的第一记忆体单元组(例如:set_l),记忆体单元m的子集310[00]是平行连接在区域选择线lsl_l[0]与区域位元线lbl_l[0]之间;记忆体单元m的子集310[01]是平行连接在区域选择线lsl_l[0]与区域位元线lbl_l[0]之间;记忆体单元m的子集310[02]是平行连接在区域选择线lsl_l[0]与区域位元线lbl_l[0]之间;以及记忆体单元m的子集310[03]是平行连接在区域选择线lsl_l[0]与区域位元线lbl_l[0]之间。

[0077]

参考图3a中的第一记忆体单元组(例如:set_r),记忆体单元m的子集310[04]是平行连接在区域选择线lsl_r[0]与区域位元线lbl_r[0]之间;记忆体单元m的子集310[05]是平行连接在区域选择线lsl_r[0]与区域位元线lbl_r[0]之间;记忆体单元m的子集310[06]是平行连接在区域选择线lsl_r[0]与区域位元线lbl_r[0]之间;记忆体单元m的子集310[07]是平行连接在区域选择线lsl_r[0]与区域位元线lbl_r[0]之间;以及记忆体单元m的子集310[08]是平行连接在区域选择线lsl_r[0]与区域位元线lbl_r[0]之间。

[0078]

区域选择线lsl(例如:lsl_l、lsl_r)可沿着z方向延伸且连接至开关ss_l的群组或开关ss_r的群组。在一配置中,lsl_l[0]是连接至开关ss_l的群组中的第二垂直串开关ss_l(例如:ss2_l[0][0][0]、ss2_l[0][0][1]、ss2_l[0][0][f-2]、以及ss2_l[0][0][f])。在一配置中,记忆体单元m的子集310[00]...310[03]是经由lsl_l[0]连接至第二垂直串开关ss_l。

[0079]

在一配置中,lsl_r[0]是连接至开关ss_r的群组中的第一垂直串开关ss_l(例如:ss1_r[0][0][0]、ss1_r[0][0][1]、ss1_r[0][0][f-2]、以及ss1_r[0][0][f])。在一配置中,记忆体单元m的子集310[00]...310[03]是经由lsl_l[0]连接至第二垂直串开关ss_l。

[0080]

区域位元线lbl可沿着平行于区域位元线lbl的z方向延伸且连接至开关sb的群组。在一配置中,lbl_l[0]是连接至开关sb的群组中的第一垂直串开关sb(例如:sb_l[0][0][0]、sb_l[0][0][1]、sb_l[0][0][f-2]、以及sb_l[0][0][f])。在一配置中,记忆体单元m的子集310[00]...310[03]是经由lbl_l[0]连接至第一垂直串开关sb。

[0081]

在一配置中,lsl_r[0]是连接至开关sb的群组中的第三垂直串开关sb(例如:sb_r[0][0][0]、sb_r[0][0][1]、sb_r[0][0][f-2]、以及sb_r[0][0][f])。在一配置中,记忆体单元m的子集310[04]...310[08]是经由lbl_r[0]连接至第三垂直串开关sb。

[0082]

每一开关sb(例如:sb_l、sb_c、sb_r)可实施为晶体管(例如:mosfet、gaafet、finfet等)。第一垂直串开关sb(例如:sb_l[0][0][0]、sb_l[0][0][1]、sb_l[0][0][f-2]、以及sb_l[0][0][f])的每一开关可包含:第一电极(例如漏极电极),其连接至区域位元线lbl(例如lbl_l[0]);第二电极(例如:源极电极),其连接至第二垂直串开关sb(例如:sb_c[0][0][0]、sb_c[0][0][1]、sb_c[0][0][f-2]、以及sb_c[0][0][f])的第二电极(例如源极

电极)与第三垂直串开关sb(例如:sb_r[0][0][0]、sb_r[0][0][1]、sb_r[0][0][f-2]、以及sb_r[0][0][f])的第二电极(例如源极电极);以及第三电极(例如:栅极电极),其连接至对应的开关控制线sbl。

[0083]

第二垂直串开关sb(例如:sb_c[0][0][0]、sb_c[0][0][1]、sb_c[0][0][f-2]、以及sb_c[0][0][f])的每一开关可包含:第一电极(例如:漏极电极),其连接至全域位元线gbl(例如:gbl[0]);第二电极(例如:源极电极),其连接至第一垂直串开关sb与第三垂直串开关sb的第二电极(例如:源极电极);以及第三电极(例如:栅极电极),其连接至对应的开关控制线sbl。

[0084]

第三垂直串开关sb(例如:sb_r[0][0][0]、sb_r[0][0][1]、sb_r[0][0][f-2]、以及sb_r[0][0][f])的每一开关可包含:第一电极(例如:漏极电极),其连接至区域位元线lbl(例如:lbl_r[0]);第二电极(例如:源极电极),其连接至第一垂直串开关sb与第二垂直串开关sb的第二电极(例如:源极电极);以及第三电极(例如:栅极电极),其连接至对应的开关控制线sbl。

[0085]

开关控制线sbl可为沿x方向延伸的金属轨道,以连接记忆体控制器105(例如:栅极线控制器114)至对应开关sb的栅极电极。根据通过开关控制线sbl所施加的电压或信号,可捺跳(toggle)(例如:启用或禁用)连接至开关控制线sbl的一或多个开关sb。

[0086]

在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘1’

的电压,可启用第二垂直串开关sb(例如:sb_c[0][0][0]、sb_c[0][0][1]、sb_c[0][0][f-2]、以及sb_c[0][0][f])中的开关sb,以电性耦接(例如:连接、接合等)第一垂直串开关sb及第三垂直串开关sb的第二电极(例如:源极电极)至全域位元线gbl。在一配置中,若需要额外的驱动电流来存取(例如:读取、写入、程序化)记忆体阵列的更大区域,可启用第二垂直串开关sb中一个以上的开关sb。在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘0’

的电压,可禁用第二垂直串开关sb中的开关sb,以将第一垂直串开关sb及第三垂直串开关sb的第二电极(例如:源极电极)从全域位元线gbl电性去耦接(例如:断开、脱离等)。

[0087]

在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘1’

的电压,可启用第一垂直串开关sb(例如:sb_l[0][0][0]、sb_l[0][0][1]、sb_l[0][0][f-2]、以及sb_l[0][0][f])中的开关sb,以电性耦接第二垂直串开关sb及第三垂直串开关sb的第二电极(例如:源极电极)至区域位元线lbl_l(例如:lbl_l[0])。在一配置中,若需要额外的驱动电流来存取(例如:读取、写入、程序化)记忆体阵列的更大区域,可启用第一垂直串开关sb中一个以上的开关sb。在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘0’

的电压,可禁用第一垂直串开关sb中的开关sb,以将第二垂直串开关sb及第三垂直串开关sb的第二电极从区域位元线lbl_l(例如:lbl_l[0])电性去耦接。

[0088]

在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘1’

的电压,可启用第三垂直串开关sb(例如:sb_r[0][0][0]、sb_r[0][0][1]、sb_r[0][0][f-2]、以及sb_r[0][0][f])中的开关sb,以电性耦接第一垂直串开关sb及第二垂直串开关sb的第二电极(例如:源极电极)至区域位元线lbl_r(例如:lbl_r[0])。在一配置中,若需要额外的驱动电流来存取记忆体阵列的更大区域,可启用第三垂直串开关sb中的一个以上的开关sb。在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘0’

的电压,可禁用第三垂直串开关sb中的开关sb,以将第一垂直串开关sb及第二垂直串开关sb的第二电极从区域

位元线lbl_r(例如:lbl_r[0])电性去耦接。

[0089]

每一开关ss可实施为晶体管(例如:mosfet、gaafet、finfet等)。第一垂直串开关ss1_l(例如:ss1_l[0][0][0]、ss1_l[0][0][1]、ss1_l[0][0][f-2]、以及ss1_l[0][0][f])的每一开关可包含:第一电极(例如:漏极电极),其连接至第二垂直串开关ss2_l(例如:ss2_l[0][0][0]、ss2_l[0][0][1]、ss2_l[0][0][f-2]、ss1_l[0][0][f])的第一电极(例如漏极电极);第二电极(例如:源极电极),其连接至全域选择线(例如:gsl[0]);以及第三电极(例如:栅极电极),其连接至对应的开关控制线sbl。

[0090]

第二垂直串开关ss2_l(例如:ss2_l[0][0][0]、ss2_l[0][0][1]、ss2_l[0][0][f-2]、以及ss2_l[0][0][f])的每一开关可包含:第一电极(例如:漏极电极),其连接至第一垂直串开关ss1_l的第一电极(例如:漏极电极);第二电极(例如:源极电极),其连接至对应的区域选择线(例如:lsl_l[0]);以及第三电极(例如:栅极电极),其连接至对应的开关控制线sbl。

[0091]

第一垂直串开关ss1_r(例如:ss1_r[0][0][0]、ss1_r[0][0][1]、ss1_r[0][0][f-2]、以及ss1_r[0][0][f])的每一开关可包含:第一电极(例如:漏极电极),其连接至第二垂直串开关ss2_r(例如:ss2_r[0][0][0]、ss2_r[0][0][1]、ss2_r[0][0][f-2]、ss1_r[0][0][f])的第一电极(例如:漏极电极);第二电极(例如:源极电极),其连接至对应的区域选择线(例如:lsl_r[0]);以及第三电极(例如:栅极电极),其连接至对应的开关控制线sbl。

[0092]

第二垂直串开关ss2_r(例如:ss2_r[0][0][0]、ss2_r[0][0][1]、ss2_r[0][0][f-2]、以及ss2_r[0][0][f])的每一开关可包含:第一电极(例如:漏极电极),其连接至第一垂直串开关ss1_r的第一电极(例如:漏极电极);第二电极(例如:源极电极),其连接至对应的全域选择线(例如:gsl[0]);以及第三电极(例如:栅极电极),其连接至对应的开关控制线sbl。

[0093]

开关控制线sbl可为沿x方向延伸的金属轨道,以连接记忆体控制器105(例如:栅极线控制器114)至对应的开关ss的栅极电极。根据通过开关控制线sbl所施加的电压或信号,可捺跳(例如:启用或禁用)连接至开关控制线sbl的一或多个开关ss。

[0094]

在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘1’

的电压,可启用垂直串开关ss1_l中的开关,以电性耦接(例如:连接、接合等)垂直串开关ss2_l的第一电极(例如:漏极电极)至全域选择线gsl(例如:gsl[0])。在一配置中,若需要额外的电流来存取(例如:读取、写入、程序化)记忆体阵列的更大区域,可启用垂直串开关ss1_l中一个以上的开关。在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘0’

的电压,可禁用垂直串开关ss1_l中的开关,以将垂直串开关ss2_l的第一电极(例如:漏极电极)从全域选择线gsl电性去耦接(例如:断开、脱离等)。

[0095]

在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘1’

的电压,可启用垂直串开关ss2_l中的开关,以电性耦接(例如:连接、接合等)垂直串开关ss1_l的第一电极(例如:漏极电极)至区域选择线lsl_l(例如lsl_l[0])。在一配置中,若需要额外的电流来存取(例如:读取、写入、程序化)记忆体阵列的更大区域,可启用垂直串开关ss2_l中一个以上的开关。在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘0’

的电压,可禁用垂直串开关ss2_l中的开关,以将垂直串开关ss1_l的第一电极(例如:漏极电极)从区域选择线lsl_l电性去耦接(例如:断开、脱离等)。

[0096]

在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘1’

的电压,可启用垂直串开关ss2_r中的开关,以电性耦接(例如:连接、接合等)垂直串开关ss1_r的第一电极(例如:漏极电极)至全域选择线gsl(例如gsl[0])。在一配置中,若需要额外的电流来存取(例如:读取、写入、程序化)记忆体阵列的更大区域,可启用垂直串开关ss2_r中一个以上的开关。在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘0’

的电压,可禁用垂直串开关ss2_r中的开关,以将垂直串开关ss1_r的第一电极(例如:漏极电极)从全域选择线gsl电性去耦接(例如:断开、脱离等)。

[0097]

在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘1’

的电压,可启用垂直串开关ss1_r中的开关,以电性耦接(例如:连接、接合等)垂直串开关ss2_r的第一电极(例如:漏极电极)至区域选择线lsl_r(例如:lsl_r[0])。在一配置中,若需要额外的电流来存取(例如:读取、写入、程序化)记忆体阵列的更大区域,可启用垂直串开关ss1_r中一个以上的开关。在一配置中,为了回应通过开关控制线sbl所提供的对应于逻辑状态

‘0’

的电压,可禁用垂直串开关ss1_r中的开关,以将垂直串开关ss2_r的第一电极(例如:漏极电极)从区域选择线lsl_r电性去耦接(例如:断开、脱离等)。

[0098]

在一配置中,全域选择线gsl为金属轨道,可在此处连接对应的开关ss_l与ss_r。全域选择线gsl可沿着y方向延伸。在一实施中,全域选择线gsl可连接至记忆体控制器105(例如:位元线控制器112)。全域位元线gbl可为金属轨道,可在此处连接对应的开关sb(例如:sb_c)。全域位元线gbl可平行于全域选择线gsl沿着y方向延伸。在一实施中,全域位元线gbl可连接至记忆体控制器105(例如:位元线控制器112)。

[0099]

因此,根据来自记忆体控制器105(例如:栅极线控制器114)的电压或信号,一或多个开关ss_l、一或多个开关ss_r、以及一或多个开关sb可操作或配置以选择性地电性耦接(有时称为“耦接方法”)记忆体单元的子集310至对应的全域线gbl与全域选择线gsl。举例而言,可启用一或多个开关sb_c与一或多个开关sb_l,以电性耦接记忆体单元的子集310[00]...310[03]至gbl[0];以及可启用一或多个开关ss1_l与ss2_l,以连接记忆体单元的子集310[00]...310[03]至gsl[0]。同时,可禁用开关sb_r以将记忆体单元的子集310[04]...310[08]从gbl[0]电性去耦接(有时称为“去耦接方法”);以及可禁用开关ss1_r与ss2_r以从gsl[0]断开记忆体单元的子集310[04]...310[08]。通过将记忆体单元的所选子集310[xy]透过开关sb、ss_l、以及ss_r电性耦接至全域位元线gbl[x]及全域选择线gsl[x],全域位元线gbl[x]与全域选择线gsl[x]可具有对应于记忆体单元的所选子集310[xy],而非记忆体单元的子集310[x1]...310[x3](例如:多个或全部)的电容负载。据此,全域位元线gbl[x]与全域选择线gsl[x]可实现不增加电容负载来提供电压或电流。

[0100]

在一配置中,记忆体阵列可为非对称记忆体阵列。举例而言,如图3a所示,第一记忆体单元组(例如:set_l)的子集(例如:310[00]...310[03])的数量少于第二记忆体单元组(例如:set_r)的子集(例如:310[04]...310[08])的数量。据此,对于使用低密度记忆体单元及/或高速存取记忆体单元的应用,记忆体控制器可选择第一记忆体单元组。相对地,对于使用高密度记忆体单元的应用及/或不在意低速存取记忆体单元的状况,记忆体控制器可选择第二记忆体单元组。

[0101]

在一配置中,记忆体阵列可为对称记忆体阵列。举例而言,第一记忆体单元组的子集(例如:310[00]...310[03])的数量可等于第二记忆体单元组的子集(例如:310[04]

...310[07])的数量。对称记忆体阵列可有助于降低bl负载。

[0102]

虽然图3a中所示的开关sb、开关ss_l、以及开关ss_r以特定方式排列,对于bl降低负载(例如:set_l)或高密度设计(例如:set_r),可在记忆体阵列210的任何位置中插入开关。为了提高效率及/或gbl/gsl的负载降低,gbl及/或gsl可置于记忆体阵列210的任何位置(例如左边、中心、右边)。

[0103]

在一些实施例中,记忆体阵列210包含开关sb,但可能缺少开关ss_l及/或开关ss_r。举例而言,图3b是根据一实施例的三维记忆体阵列210的部分的示意图,此三维记忆体阵列210包含耦接至全域位元线gbl用以降低电容负载的开关。如图所示,记忆体阵列210包含如图3a所示的开关sb,但省略开关ss_l与ss_r,且区域选择线lsl_l(例如:lsl_l[0])与lsl_r(例如:lsl_r[0])是连接至记忆体阵列210的各别端口,从而允许记忆体控制器210独立地驱动区域选择线。在一配置中,区域选择线lsl_l(例如:lsl_l[0])与lsl_r(例如:lsl_r[0])可连接至记忆体阵列210的同一端口,由此允许记忆体控制器210使用最少的端口及/或驱动器来驱动区域选择线。

[0104]

在一些实施例中,记忆体阵列210包含开关ss_l与ss_r,但可能缺少开关sb。举例而言,图3c是根据一实施例的三维记忆体阵列210的部分的示意图,此三维记忆体阵列210包含耦接至区域选择线用以降低电容负载的开关。如图所示,记忆体阵列210包含如图3a所示的开关ss_l与ss_r,但省略开关sb,且区域选择线lbl_l(例如:lbl_l[0])与lbl_r(例如:lbl_r[0])是连接至全域位元线(例如:gbl[0])。在设计中省略开关ss_l与ss_r可有助于降低布线复杂性及/或在高速(例如:快速存取记忆体阵列210)应用中实现sl负载降低。

[0105]

在一些实施例中,图3a、图3b、以及图3c中的任一者所描述的记忆体阵列210中的m单元及/或开关sb、ss_l、以及ss_r可被实施为p型金属氧化物半导体场效晶体管(pmos)。在一些实施例中,图3a、图3b、以及图3c中的任一者所描述的记忆体阵列210中的m单元及/或开关sb、ss_l、以及ss_r可被实施为n型金属氧化物半导体场效晶体管(nmos)。

[0106]

在一些实施例中,为了降低位元线负载(例如:低密度设计及/或高速存取)或高密度设计(例如:低速存取)的目的,图3a、图3b、以及图3c中的任一者所描述的记忆体阵列210中的开关sb、ss_l、以及ss_r可插入至记忆体阵列210中的任一位置。在一些实施例中,图3a、图3b、以及图3c的任一记忆体阵列中的位元线bl(区域或全域)及/或选择线sl(区域或全域)的尺寸可等同、小于、或大于记忆体位元格的尺寸。在一些实施例中,图3a、图3b、以及图3c中的任一者所描述的记忆体阵列210的位元线bl(区域或全域)及/或选择线sl(区域或全域)可为一或多个,以增强驱动电流。在一些实施例中,图3a、图3b、以及图3c中的任一者所描述的记忆体阵列210的位元线bl(区域或全域)及/或选择线sl(区域或全域)可为独立的控制器。

[0107]

图4是根据一实施例的三维记忆体阵列400的部分的示意图,此三维记忆体阵列400包含将位元格阵列分成多个位元用以降低电容负载的选择器。如图所示,记忆体阵列400包含多个选择器输出(例如:开关ss_l、开关ss_r、开关sb)、多个选择器输入(例如:开关ss_l、开关ss_r、开关sb)、以及多个位元格阵列(例如:记忆体阵列210)。举例而言,选择器输出402的第一电极是耦接至全域选择线gsl[0]。选择器输出402的第二电极是耦接至选择器输入404的第二电极,选择器输入404的第一电极是耦接至lsl_l1[0],lsl_l1[0]是耦接至位元格阵列406的第一电极,位元格阵列406的第二电极是耦接至lbl_l1[0],lbl_l1[0]

是耦接至选择器输入408的第二电极,选择器输入408的第一电极是耦接至选择器输出410与选择器输入412的第一电极。选择器输出410的第二电极是耦接至gbl[0],gbl[0]是耦接至选择器输出426的第二电极,选择器输出426的第一电极是耦接至选择器输入424与选择器输入428的第一电极。

[0108]

选择器输入412的第二电极是耦接至lbl_l2[0],lbl_l2[0]是耦接至位元格阵列414的第二电极,位元格阵列414的第一电极耦接至lsl_l2[0],lsl_l2[0]是耦接至选择器输入416的第一电极,选择器输入416的第二电极是耦接至选择器输出418与选择器输入420的第二电极。选择器输入412的第一电极是耦接至lsl_r1[0],lsl_r1[0]是耦接至位元格阵列422的第一电极,位元格阵列422的第二电极是耦接至lbl_r1[0],lbl_r1[0]是耦接至选择器输入424的第二电极,选择器输入424的第一电极是耦接至选择器输出426与选择器输入428的第一电极。选择器输入428的第二电极是耦接至lbl_r2[0],lbl_r2[0]是耦接至位元格阵列430的第二电极,位元格阵列430的第一电极是耦接至lsl_r2[0],lsl_r2[0]是耦接至选择器输入432的第一电极,选择器输入432的第二电极是耦接至选择器输出434的第二电极,选择器输出434的第一电极是耦接至gsl[0]。

[0109]

通过将位元格阵列经由多选择器(例如:开关sb、ss_l及/或ss_r)分成多个单元,bl/sl负载显著地降低使得极高速记忆体可被实现,且不会有严重的布线损失。bl/sl负载的降低亦实现极高速记忆体。

[0110]

图5是根据一实施例的三维记忆体阵列500的部分的示意图,此三维记忆体阵列500包含为了bl/sl驱动器增强而设计的一或多者的选择器输入与选择器输出。如图所示,记忆体阵列500包含多个选择器输出(例如:开关ss_l、开关ss_r、开关sb)、多个选择器输入(例如:开关ss_l、开关ss_r、开关sb)、以及多个位元格阵列(例如:记忆体阵列210)。举例而言,选择器输出502的第一电极是耦接至全域选择线gsl[0]。选择器输出502的第二电极是耦接至选择器输入504的第二电极,选择器输入504的第一电极是耦接至lsl_l[0],lsl_l[0]是耦接至位元格阵列506的第一电极,位元格阵列506的第二电极是耦接至lbl_l[0],lbl_l[0]是耦接至选择器输入508与选择器输入510的第二电极。选择器输入508与选择器输入510的第一电极是耦接至选择器输出512、选择器输出514、选择器输入516、以及选择器输入518的第一电极。选择器输出512与选择器输出514的第二电极是耦接至gbl[0]。选择器输入516与选择器输入518的第二电极耦接至lbl_r[0],lbl_r[0]是耦接至位元格阵列520的第二电极,位元格阵列520的第一电极是耦接至lsl_r[0],lsl_r[0]是耦接至选择器输入522的第一电极,选择器输入522的第二电极是耦接至选择器输出524的第二电极,选择器输出524的第一电极是耦接至gsl[0]。

[0111]

在一配置中,选择器输出512、514、以及524中的任一者可合并为单一的选择器输出。在一配置中,选择器输入516、518、以及522中的任一者可合并为单一的选择器输入。在一配置中,任何选择器输入516、518、以及522与任何选择器输出512、514、以及524可合并为单一的选择器输入/选择器输出。通过合并(或共用)选择器输入及/或选择器输出,增强的bl/sl驱动器可被实现。此外,合并选择器输入及/或选择器输出可使得面积效率提升。

[0112]

以下针对说明性实施例的实施方法进行更进一步地叙述。

[0113]

图6是根据一些实施例的存取及/或操作记忆体单元(例如:记忆体单元125)及/或记忆体阵列(例如:记忆体阵列210)的方法600的流程图。可通过图1中的记忆体控制器105

进行方法600。在一些实施例中,可通过其他实体进行方法600。在一些实施例中,方法600包含相较于图6中所示的操作更多、更少、或不同的操作。

[0114]

在操作602中,记忆体控制器105在第一时间周期期间启用(例如:选择)一或多个开关,以将第一记忆体单元子集的第一电极耦接至第一全域选择线。举例而言,记忆体控制器可启用一或多个开关ss2_l,以电性耦接开关ss1_l的第一电极至记忆体单元m的第一子集(例:如310[00]...310[03])的第一电极;及/或启用对应的一或多个开关ss1_l,以电性耦接ss1_l的第一电极至全域选择线(例如:gsl[0])。

[0115]

在操作604中,记忆体控制器105在第一时间周期期间禁用(例如:取消选择)一或多个开关,以将第二记忆体单元子集的第一电极从第一全域选择线去耦接。举例而言,记忆体控制器可禁用一或多个开关ss1_r,以将开关ss2_r的第一电极从记忆体单元m的第二子集(例如:310[04]...310[08])的第一电极电性去耦接(例如:断开);及/或禁用对应的一或多个开关ss2_r,以将开关ss2_r的第一电极从全域选择线(例如:gsl[0])电性去耦接。

[0116]

在操作606中,记忆体控制器105在第一时间周期期间启用一或多个开关,以耦接第一记忆体单元组的第二电极至全域位元线。举例而言,记忆体控制器可启用一或多个开关sb_c,以电性耦接全域位元线(例如:gbl[0])至开关sb_l的第二电极与开关sb_r的第二电极;及/或启用一或多个开关sb_l,以电性耦接第一记忆体单元子集的第二电极至全域位元线(例如:gbl[0])。

[0117]

在操作608中,记忆体控制器105在第一时间周期期间禁用一或多个开关,以将第二记忆体单元组的第二电极从全域位元线去耦接。举例而言,记忆体控制器可禁用一或多个开关sb_c,以将全域位元线(例如:gbl[0])从开关sb_l的第二电极与开关sb_r的第二电极电性去耦接;及/或禁用一或多个开关sb_r,以将第二记忆体单元子集的第二电极从全域位元线(例如:gbl[0])电性去耦接。

[0118]

在操作610中,记忆体控制器105在第一时间周期期间存取(例如:配置、程序化、读取、写入)第一记忆体单元子集的一或多个记忆体单元。举例而言,记忆体控制器105可通过其各别字元线(例如:wl[x][y]或wl[x][y])对第一记忆体单元子集施加电压、电流或脉冲,以程序化第一记忆体单元子集,或使第一记忆体单元子集根据程序化数据来传导电流。由于第二记忆体单元子集未耦接至全域位元线及/或全域选择线,记忆体控制器105可在不被第二记忆体单元子集的电容施加负载的情况下存取第一记忆体单元子集。

[0119]

以下针对实施说明性实施例的计算系统进行更进一步的叙述。

[0120]

图7是根据本揭露的一些实施例的计算系统700的例示性方块图。计算系统700可被电路或布局设计者使用在集成电路设计。本文使用的“电路”是经配置以实施所要功能性的诸如电阻器、晶体管、开关、电池、电感器或其他类型半导体装置的电子元件互连。计算系统700包含与记忆体装置710相关的主机装置705。主机装置705是配置以从一或多个输入装置715接收输入,以及提供输出至一或多个输出装置720。主机装置705是配置以经由适当的接口725a、725b、以及725c各别地与记忆体装置710、输入装置715、以及输出装置720沟通。计算系统700可在诸如计算机(例如:桌上型计算机、笔记型计算机、服务器、数据中心等)、平板计算机、个人数字助理、移动装置、其他手持式或可携式装置、或适合使用主机装置705来进行示意设计及/或布局设计的任何其他计算单元的各种计算装置中实施。

[0121]

输入装置715可包含各种输入技术中的任一者,诸如键盘、电笔、触控屏幕、鼠标、

轨迹球、小键盘、麦克风、语音辨识、动作辨识、遥控器、输入端口、一或多个按钮、刻度盘、控制杆、以及与主机装置705相关的任何其他周边输入装置,并且允许诸如使用者(例如:电路或布局设计者)的外部来源键入信息(例如:数据)至主机装置与发送指令至主机装置。类似地,输出装置720可包含各种输出技术,诸如外部记忆体、印表机、扬声器、显示器、麦克风、发光二极管、耳机、视频装置、以及配置以接收来自主机装置705的信息(例如:数据)的任何其他周边输出装置。输入至主机装置705及/或从主机装置输出的“数据”可包含适合使用计算系统700来处理的各种文本数据、电路数据、信号数据、半导体装置数据、图形数据、其组合、或其他类型的模拟及/或数字数据中的任一者。

[0122]

主机装置705包含诸如中央处理单元(central processing unit;cpu)核心730a-730n的一或多个处理单元/处理器,或与其相关。cpu核心730a-730n可实施为特殊应用集成电路(application specific integrated circuit;asic)、现场可程序逻辑门阵列(field programmable gate array;fpga)、或其他类型的处理单元。cpu核心730a-730n中的任一者是配置以执行运行主机装置705的一或多个应用的指令。在一些实施例中,用以运行一或多个应用的指令与数据可储存于主机装置710内。主机装置705亦可配置以储存记忆体装置710内一或多个应用的运行结果。由此,主机装置705是配置以请求记忆体装置710执行各种操作。举例而言,主机装置705可请求记忆体装置710读取数据、写入数据、更新或删除数据、及/或进行管理或其他操作。一个可配置主机装置705来运行的类似应用为标准单元应用735。标准单元应用735可为计算机辅助设计或电子设计自动化套装软件的一部分,其可由主机装置705的使用者使用以建立或修改电路的标准单元。在一些实施例中,执行或运行标准单元应用的指令可储存于记忆体装置710内。标准单元应用735可由一或多个cpu核心730a-730n使用来自记忆体装置710与标准单元应用相关的指令来执行。在一实例中,标准单元应用735允许使用者使用记忆体系统100或部分记忆体系统100的预生成的示意及/或布局设计来辅助集成电路设计。在完成集成电路的布局设计后,多个集成电路(例如:包含记忆体系统100或部分记忆体系统100)可由制造设施根据布局设计来制造。

[0123]

仍参考图7,记忆体装置710包含记忆体控制器740,记忆体控制器740是配置以从记忆体阵列745读取数据或写入数据至记忆体阵列745。记忆体阵列745可包含各种挥发性及/或非挥发性记忆体。举例而言,在一些实施例中,记忆体阵列745可包含nand快闪记忆体核心。在其他实施例中,记忆体阵列745可包含nor快闪记忆体核心、静态随机存取记忆体(static random access memory;sram)核心、动态随机存取记忆体(dynamic random access memory;dram)核心、磁阻式随机存取记忆体(magnetoresistive random access memory;mram)核心、相变化记忆体(phase change memory;pcm)核心、电阻式随机存取记忆体(resistive random access memory;reram)核心、3d xpoint记忆体核心、铁电式随机存取记忆体(ferroelectric random-access memory;feram)核心、及其他适合使用于记忆体阵列内的类型的记忆体核心。记忆体阵列745内的记忆体可由记忆体控制器740单独且独立地控制。换言之,记忆体控制器740是配置以与记忆体阵列745内的每一记忆体单独且独立地沟通。通过与记忆体阵列745沟通,记忆体控制器740可配置以回应所接收到来自主机装置705的指令,而从记忆体阵列读取数据或写入数据至记忆体阵列。虽然图示为记忆体装置710的一部分,但在一些实施例中,记忆体控制器740可为主机装置705的一部分,或计算系统700中与记忆体装置有关的另一元件的一部分。记忆体控制器740可实现为软件、硬件、固

件或其组合中的逻辑电路以执行本文所描述的功能。举例而言,在一些实施例中,记忆体控制器740是配置以在接收到来自主机装置705的要求后提取储存于记忆体装置710的记忆体阵列745中与标准单元应用735相关的指令。

[0124]

应理解的是,图7中仅图示及描述计算系统700的一些元件。然而,计算系统700可包含其他元件,诸如各种电池及电源、网络接口、路由器、开关、外部记忆体系统、以及控制器等。一般而言,计算系统700可包含执行本文描述的功能时所需要或认为需要的各种硬件、软件及/或固件元件中的任一者。类似地,主机装置705、输入装置715、输出装置720、以及包含记忆体控制器740与记忆体阵列745的记忆体装置710,可包含执行本文描述的功能时所需要或理想的其他硬件、软件及/或固件部件。

[0125]

本揭露的一态样是提供一种记忆体阵列,包含:第一记忆体单元组(set)与第二记忆体单元组、第一开关群(group)、第二开关群、以及第三开关群。其中,每一记忆体单元组延伸而越过记忆体阵列的多个层,每一层包含第一记忆体单元组的记忆体单元与第二记忆体单元组的记忆体单元。第一开关群包含多个开关,每一开关包含连接至第一记忆体单元子集(subset)的多个第一电极的第一电极,以及第二电极。第二开关群包含多个开关,每一开关包含连接至第二记忆体单元子集的多个第一电极的第一电极;以及第二电极。第三开关群包含多个开关,每一开关包含连接至第一全域位元线的第一电极,以及连接至第一开关群的第二电极以及第二开关群的第二电极的第二电极。在一些实施例中,记忆体阵列还包含第四开关群以及第五开关群。其中,第四开关群包含多个开关,每一开关包含第一电极,以及连接至第一全域选择线的第二电极。第五开关群包含多个开关,每一开关包含连接至第四开关群的这些开关的第一电极的第一电极,以及连接至第一记忆体单元子集的多个第二电极的第二电极。在一些实施例中,记忆体阵列还包含第六开关群以及第七开关群。其中,第六开关群包含多个开关,每一开关包含第一电极,以及连接至第一全域选择线的第二电极。第七开关群包含多个开关,每一开关包含:连接至第六开关群的这些开关的第一电极的第一电极,以及连接至第二记忆体单元子集的多个第二电极的第二电极。在一些实施例中,第一记忆体单元子集的第二电极是连接至一第一区域选择线;以及第二记忆体单元子集的第二电极是连接至一第二区域选择线。在一些实施例中,第一记忆体单元组的数量不同于第二记忆体单元组的数量。在一些实施例中,第一开关群的每一开关的每一栅极电极是连接至多个开关控制线中的一各别开关控制线;第二开关群的每一开关的每一栅极电极是连接至这些开关控制线中的一各别开关控制线;以及第三开关群的每一开关的每一栅极电极是连接至这些开关控制线中的一各别开关控制线。在一些实施例中,第一开关群的这些开关的栅极电极是连接至一第一开关控制线;第二开关群的这些开关的栅极电极是连接至一第二开关控制线;以及第三开关群的这些开关的栅极电极是连接至一第三开关控制线。在一些实施例中,第一记忆体单元组与第一开关对应至类型匹配的晶体管,其中晶体管的类型包含n型金属氧化物半导体场效晶体管(nmos)或p型金属氧化物半导体场效晶体管(pmos)。

[0126]

本揭露的另一态样是提供一种记忆体阵列,包含:第一记忆体单元组与第二记忆体单元组、第一开关群、第二开关群、第三开关群、以及第四开关群。其中,每一记忆体单元组延伸而越过记忆体阵列的多个层,每一层包含第一记忆体单元组的记忆体单元与第二记忆体单元组的记忆体单元。第一开关群包含多个开关,每一开关包含第一电极,以及连接至

全域选择线的第二电极。第二开关群包含多个开关,每一开关包含:第一电极,以及连接至全域选择线的第二电极。第三开关群包含多个开关,每一开关包含:连接至第一开关群的第一电极的第一电极,以及连接至第一记忆体单元子集的多个第一电极的第二电极。第四开关群包含多个开关,每一开关包含:连接至第二开关群的第一电极的第一电极,以及连接至第二记忆体单元子集的多个第一电极的第二电极。在一些实施例中,第一记忆体单元子集的多个第二电极是连接至全域位元线;以及第二记忆体单元子集的多个第二电极是连接至全域位元线。在一些实施例中,第一开关群的每一开关的每一栅极电极是连接至多个开关控制线中的一各别开关控制线;第二开关群的每一开关的每一栅极电极是连接至这些开关控制线中的一各别开关控制线;第三开关群的每一开关的每一栅极电极是连接至这些开关控制线中的一各别开关控制线;以及第四开关群的每一开关的每一栅极电极是连接至这些开关控制线中的一各别开关控制线。在一些实施例中,第一开关群的这些栅极电极是连接至一第一开关控制线;第二开关群的这些栅极电极是连接至一第二开关控制线;第三开关群的这些栅极电极是连接至一第三开关控制线;以及第四开关群的这些栅极电极是连接至一第四开关控制线。

[0127]

本揭露的又一态样是提供一种记忆体系统,包含记忆体阵列以及控制器。其中,记忆体阵列包含:具有多个开关的第一开关群;具有耦接至第一区域选择线的多个第一电极与耦接至第一开关群的开关的多个第二电极的第一记忆体单元组;以及具有耦接至第二区域选择线的多个第一电极与耦接至第一开关群的开关的多个第二电极的第二记忆体单元组。控制器是连接至记忆体阵列,且控制器是用以捺跳(toggle)第一开关群的这些开关中的至少一开关,以电性耦接全域位元线至第一记忆体单元组的第二电极。在一些实施例中,记忆体系统还包含具有多个开关的第二开关群,且其中控制器还用以:捺跳第二开关群的这些开关中的至少一开关,以将全域位元线从第二记忆体单元组的第二电极电性去耦接(decouple)。在一些实施例中,记忆体系统还包含具有多个开关的第三开关群,且其中控制器还用以:捺跳第三开关群的这些开关中的至少一开关,以将全域位元线从第一记忆体单元组的第二电极电性去耦接。在一些实施例中,记忆体系统还包含具有多个开关的第二开关群,且其中控制器还用以:捺跳第二开关群的这些开关中的至少一开关,以电性耦接第一区域选择线至全域选择线。在一些实施例中,记忆体系统还包含具有多个开关的第三开关群,且其中控制器还用以:捺跳第三开关群的这些开关中的至少一开关,以将第一区域选择线从全域选择线电性去耦接。在一些实施例中,记忆体系统还包含具有多个开关的第三开关群,且其中控制器还用以:捺跳第三开关群的这些开关中的至少一开关,以将第二区域选择线从全域选择线电性去耦接。在一些实施例中,记忆体系统还包含具有多个开关的第四开关群,且其中控制器还用以:捺跳第四开关群的这些开关中的至少一开关,以电性耦接第三开关群的这些开关中的至少一开关至全域选择线。在一些实施例中,第一记忆体单元组与第一开关对应至类型匹配的晶体管,其中晶体管的类型包含n型金属氧化物半导体场效晶体管(nmos)或p型金属氧化物半导体场效晶体管(pmos)。

[0128]

本说明的一态样是关于一种记忆体系统的操作方法。在一些实施例中,此方法包含在第一时间周期期间耦接第一记忆体单元组的第一电极至第一全域选择线。在一些实施例中,此方法包含在第一时间周期期间从第一全域选择线去耦接第二记忆体单元组的第一电极。在一些实施例中,此方法包含在第一时间周期期间耦接第一记忆体单元组的第二电

极至全域位元线。在一些实施例中,此方法包含在第一时间周期期间从全域位元线去耦接第二记忆体单元组的第二电极。在一些实施例中,此方法包含在第一时间周期期间存取第一记忆体单元组的一或多个栅极电极。

[0129]

上文概述若干实施例的特征,使得熟悉此项技术者可较佳地理解本揭露的态样。熟悉此项技术者应理解他们可容易地以本揭露为基础来设计或修改其他制程或结构,以达到本文所介绍的实施例的相同目的及/或获得相同优点。熟悉此项技术者亦应认识到,这些等效构造不脱离本揭露的精神及范畴,并且他们可在不脱离本揭露的精神及范畴的情况下作出各种改变、替换及更改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1