非易失性存储器的读出放大器和操作方法与流程

1.本发明的实施例涉及非易失性存储器的读出放大器和操作方法。

背景技术:

2.由于缩小半导体工艺节点,已经提高了集成电路(ic)中电子元件(例如,晶体管、二极管、电阻器、电容器等)的集成密度,这引起在半导体工艺节点中开发的电子电路的操作电压和电流消耗的降低。因此,期望存储器集成电路的访问速度变得更快。例如,一些存储器具有非常小的读窗口,这需要低偏移读出放大器来成功进行读操作。

3.由于不可避免的工艺变化,在读出放大器电路中经常存在元件之间的失配或偏移。根据现有方法,读出放大器在实际的读操作之前经历偏移采样或消除阶段,以消除读出放大器电路的失配。此外,偏移补偿读出放大器不能消除参考单元的变化,参考单元通常在读路径设计中使用,并且经历工艺变化。

技术实现要素:

4.根据本发明实施例的一个方面,提供了一种读出放大器,包括:电压比较器,具有偏移补偿,分别经由读出放大器的第一i/o节点和第二i/o节点耦合到位线和参考位线,并且被配置为比较第一输入电压和第二输入电压以输出读出信号;第一钳位电路,耦合在第一i/o节点与位线之间;以及第二钳位电路,耦合在第二i/o节点与参考位线之间,其中,第一钳位电路和第二钳位电路分别微调对应于位线的电压和对应于参考位线的电压,以使对应于参考位线的电压与对应于位线的电压匹配。

5.根据本发明实施例的另一个方面,提供了一种读出放大器,包括:电压比较器,耦合到位线和参考位线,并且被配置为比较第一输入电压和第二输入电压以输出读出信号;以及钳位电路,耦合在电压比较器、位线和参考位线之间,其中,电压比较器和钳位电路中的一个具有偏移补偿,其中,电压比较器还被配置为微调对应于位线的第一电压和对应于参考位线的第二电压,以将对应于参考位线的电压与对应于位线的电压进行匹配。

6.根据本发明实施例的又一个方面,提供了一种用于非易失性存储器的操作方法,非易失性存储器包括存储器阵列和读出放大器,其中,读出放大器包括具有偏移补偿的电压比较器、第一钳位电路和第二钳位电路,第一钳位电路耦合在读出放大器的第一i/o节点与位线之间,并且第二钳位电路耦合在读出放大器的第二i/o节点与参考位线之间,其中,操作方法包括:电压比较器分别经由读出放大器的第一i/o节点和第二i/o节点比较第一输入电压和第二输入电压,以输出读出信号;以及第一钳位电路和第二钳位电路分别微调对应于位线的电压和对应于参考位线的电压,以使对应于参考位线的电压与对应于位线的电压匹配。

7.根据本发明实施例的又一个方面,提供了一种非易失性存储器的操作方法,非易失性存储器包括存储器阵列和读出放大器,其中,读出放大器包括电压比较器和钳位电路,钳位电路与读出放大器的第一i/o节点、位线、读出放大器的第二i/o节点和参考位线耦合,

并且电压比较器和钳位电路中的一个具有偏移补偿,其中,操作方法包括:电压比较器分别经由读出放大器的第一i/o节点和第二i/o节点比较第一输入电压和第二输入电压,以输出读出信号;以及电压比较器分别微调对应于位线的电压和对应于参考位线的电压,以使对应于参考位线的电压与对应于位线的电压匹配。

附图说明

8.当与附图一起阅读时,从以下详细描述最好地理解本公开的实施例。应当注意,根据工业中的标准实践,各个部件没有被按比例绘制。实际上,为了清楚地讨论,各个部件的尺寸可以任意地增大或减小。

9.图1示出了根据本公开的一些实施例的具有读出放大器的非易失性存储器的示意图。

10.图2示出了根据本公开的一些实施例的读出放大器的示意框图。

11.图3a示出了根据本公开的一些实施例的读出放大器的示意图。

12.图3b示出了根据一个实施例的读出放大器的电压比较器的电路。

13.图3c示出了根据本公开的一些实施例的读出放大器的电压比较器的示例性电路。

14.图3d示出了根据本公开的一些实施例的读出放大器的电压比较器的示例性电路。

15.图3e示出了根据本公开的一些实施例的读出放大器的电压比较器的示例性电路。

16.图4a示出了根据本公开的一些实施例的可微调的第一钳位电路的示意图。

17.图4b示出了根据本公开的一些实施例的可微调的第二钳位电路的示意图。

18.图5示出了根据本公开的一些实施例的读出放大器的示意框图。

19.图6示出了根据本公开的一些实施例的读出放大器的示意图。

20.图7a示出了根据本公开的一些实施例的可微调的电压比较器的示例性电路。

21.图7b示出了根据本公开的一些实施例的可微调的电压比较器的示例性电路。

22.图8a示出了根据本公开的一些实施例的偏移补偿钳位器件的示意图。

23.图8b示出了根据本公开的一些实施例的通过图8a中的偏移补偿钳位器件对钳位电压进行充电的流程图。

24.图8c示出了根据本公开的一些实施例的通过图8a中的偏移补偿钳位器件对钳位电压进行放电的流程图。

25.图9示出了根据本公开的一些实施例的通过微调支路来调节钳位器件尺寸的示意图。

26.图10示出了根据本公开的一些实施例的具有偏移补偿和可微调的电压比较器的读出放大器的示意框图。

27.图11示出了根据本公开的一些实施例的具有偏移补偿和可微调的钳位器件的读出放大器的示意框图。

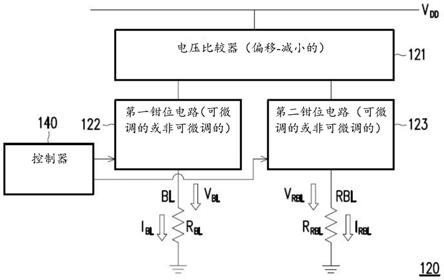

具体实施方式

28.以下公开提供了用于实施所提供主题的不同部件的许多不同的实施例或实例。以下描述了元件和布置的具体实例,以简化本公开。当然,这些仅仅是实例,而不旨在限制本公开。例如,在以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二

部件直接接触形成的实施例,并且也可以包括在第一部件与第二部件之间可以形成另外的部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本公开可在各个实例中重复参考标号和/或字符。这种重复是为了简化和清楚的目的,并且其本身不指示所讨论的各个实施例和/或配置之间的关系。

29.此外,为了便于描述,本文中可使用如“在

…

之下”、“在

…

下方”、“下部”、“在

…

之上”、“上部”等空间关系术语来描述如图所示的一个元件或部件与另一个元件或部件的关系。除了附图所示的取向之外,空间相对术语旨在涵盖在使用或操作中的器件的不同取向。可以以其它方式对装置进行取向(旋转90度或处于其它取向),而且可以相应地解释其中所使用的空间相关描述符。如“附接”、“粘接”、“连接”和“互连”等术语是指结构通过中间结构直接或间接地彼此固定或附接的一种关系,以及可移动的或刚性的附件或关系两者,除非另有明确说明。

30.参考图1,非易失性存储器100包括存储器阵列110和读出放大器120。存储器阵列110包括位于字线与位线之间的相交区域中的多个存储器单元。存储器阵列110可还包括至少一个参考存储器单元。存储器阵列110的存储器单元包括耦合到位线bl和字线wl的存储器单元112,以及耦合到参考字线rwl和参考位线rbl的参考存储器单元114。读出放大器120分别经由位线bl和参考位线rbl耦合到存储器单元112和参考存储器单元114。

31.读出放大器120被配置为执行读操作或读出操作以读出存储在存储器单元112中的数据的值。例如,读出放大器120可以将存储在存储器单元112中的数据与参考值(例如,参考存储器单元114的参考数据)进行比较以输出指示存储在存储器单元112中的数据的值的读出信号。

32.参考图2,读出放大器120包括电压比较器121(偏移补偿电压比较器)、第一钳位电路122和第二钳位电路123。理论上,因为第一钳位电路122和第二钳位电路123的电路结构相同,所以这两个钳位电路122和123具有相同的阈值电压vth。并且,理论上,如果位线bl上的电阻器r

bl

和参考位线rbl上的电阻器r

rbl

相同,并且电流i

bl

和i

rbl

相同(即,位线bl的电压v

bl

和参考位线rbl的电压v

rbl

匹配),电压比较器121可以检测到第一钳位电路122提供的电压与第二钳位电路123提供的电压相同。但是,取决于用于制造晶体管的半导体制造工艺,每个晶体管的物理特性可能略有不同,因此可能出现第一钳位电路122中晶体管(即金属氧化物半导体场效应晶体管,mos)的阈值电压vth与第一钳位电路123中mos的阈值电压vth之间的失配。

33.为了补偿第一钳位电路122中mos的阈值电压vth与第二钳位电路123中mos的阈值电压vth之间的失配,第一钳位电路122和第二钳位电路123中的至少一个具有微调校正功能(例如,可微调的),用于使第一钳位电路122中mos的阈值电压vth与mos的阈值电压vth匹配。因此,在本公开的实施例中具有微调校正功能的第一钳位电路122和第二钳位电路123中的至少一个匹配了由微调电路122和123提供的位线bl的电压v

bl

和参考位线rbl的电压v

rbl

。第一钳位电路122和第二钳位电路123中的至少一个的一个或多个微调校正功能可以由控制器140控制。具有一个或多个微调校正功能的第一钳位电路122和第二钳位电路123中的至少一个意指第一钳位电路122、第二钳位电路123或第一钳位电路122和第二钳位电路123两者具有微调校正功能。

34.例如,在存储器单元处于复位状态(即,当前i

bl

为低)的同时,可以通过第一钳位电

路或/和第二钳位电路将对应于位线bl的电压(例如,v

bl

)和对应于参考位线rbl的电压(例如,v

rbl

)微调到相同的电压电平。详细地,具有一个或多个微调校正功能的第一钳位电路122和第二钳位电路123(例如,可微调的钳位电路122和/或123)具有主分支电路和多个微调分支电路。每个微调分支电路具有电流路径和开关,开关用于传导或不传导电流路径并且由控制器140控制。控制器140控制微调分支电路中的许多开关,并且读出对应于位线bl的电压v

bl

和对应于参考位线rbl的v

rbl

相同或不相同,以便将电压v

bl

和v

bl

微调到相同的电压电平。电压比较器120可以显示对应于v

bl

的位线电流i

bl

与对应于v

rbl

的参考位线电流i

rbl

之间的变化,电压比较器可以输出位线电流i

bl

与参考位线电流i

rbl

之差。可以认为,比较器120也可以用于测量位线bl与参考位线rbl的电压差,而不是电流差。读出放大器120还包括控制器140。控制器140可以耦合到电压比较器121、第一钳位电路122和第二钳位电路123,用于控制到电压比较器121、第一钳位电路122和第二钳位电路123的切换,以便实施电压比较器121、第一钳位电路122和第二钳位电路123的功能。

35.参考图2和图3a,读出放大器220包括电压比较器221、第一钳位电路222和第二钳位电路223。电压比较器221是本公开的实施例的图2中的电压比较器121的一个实例,第一钳位电路222是本公开的实施例的图2中第一钳位电路122的一个实例,并且第二钳位电路223是本公开的实施例中的图2中第二钳位电路123的一个实例。电压比较器221经由读出放大器220的第一i/o节点ion1和第二i/o节点ion2耦合到位线bl和参考位线rbl。读出放大器被配置为比较(经由第一i/o节点ion1和第二i/o节点ion2输入的)第一输入电压和第二输入电压以输出(从第一i/o节点ion1和第二i/o节点ion2输出的)读出信号。

36.第一钳位电路222耦合在第一i/o节点ion1与位线bl之间。第一钳位电路222被配置为微调对应于位线的电压(v

bl

)。第二钳位电路223耦合在第二i/o节点ion2与参考位线rbl之间。第二钳位电路223被配置为微调对应于参考位线的电压(v

rbl

)。详细地,具有一个或多个微调校正功能的第一钳位电路222和第二钳位电路223(例如,可微调的钳位电路222和/或223)包括主分支电路和多个微调分支电路。每个微调分支电路具有电流路径和开关,每个开关用于传导或不传导图1中的电流路径并且由控制器140控制。图1中的控制器140控制微调分支电路中的许多开关,并且读出对应于位线bl的电压v

bl

和对应于参考位线rbl的v

rbl

相同或不相同,以便微调电压v

bl

和v

rbl

到相同的电压电平。

37.在本公开的实施例中,对应于读出信号的第一输出电压与第二输出电压之差值大于第一输入电压与第二输入电压之差值。此外,第一输入电压经由第一i/o节点ion1输入到电压比较器,第二输入电压经由第二i/o节点ion2输入到电压比较器,第一输出电压经由第一i/o节点ion1从电压比较器输出,并且第二输出电压经由第二i/o节点ion2从电压比较器输出。

38.在本公开的实施例中,电压比较器221包括第一电路310和第二电路320,其中,第一电路和第二电路耦合到第一i/o节点ion1和第二i/o节点ion2。

39.第一电路310包括第一晶体管m1、第二晶体管m2和第三晶体管m3,其中,第一晶体管m1的第一端子和第二晶体管m2的第一端子耦合到第一参考电压电平(例如,v

dd

),第一晶体管m1的控制端子、第二晶体管m2的控制端子和第三晶体管m3的控制端子耦合为接收预充电信号preb,第一晶体管m1的第二端子和第三晶体管m3的第二端子耦合到第一i/o节点ion1、第一晶体管m1和第三晶体管m3之间的连接节点,并且第二晶体管m2的第二端子和第

三晶体管m3的第一端子耦合到第二i/o节点ion2、第二晶体管m2和第三晶体管m3之间的另外的连接节点。

40.第二电路320包括第四晶体管m4、第五晶体管m5、第一p型晶体管pm1和pm2对、第一n型晶体管nm1和nm2对、第二p型晶体管pm3和pm4对和第二n型晶体管nm3和nm4对。第一p型晶体管pm1和pm2对和第一n型晶体管nm1和nm2对形成第三电路321。第二p型晶体管pm3和pm4对和第二n型晶体管nm3和nm4对形成第四电路322。第三电路321交叉耦合到第四电路322,并且第三电路321和第四电路322的输出分别耦合到第一i/o节点ion1和第二i/o节点ion2。

41.更详细地,第四晶体管m4耦合到第三电路321和第四电路322,其中,第四晶体管m4的第一端子耦合到第一参考电压电平(例如,v

dd

),第四晶体管m4的第二端子耦合到第四晶体管m4、第三电路321和第四电路322之间的连接节点,并且第四晶体管m4的控制端子耦合为接收第一使能信号en1。

42.此外,第五晶体管m5耦合到第三电路321和第四电路322,其中,第五晶体管m5的第一端子耦合到第五晶体管m5、第三电路321和第四电路322之间的连接节点。第五晶体管m5的第二端子耦合到第二参考电压电平(例如,接地),并且第五晶体管m5的控制端子耦合为接收第二使能信号en2。

43.而且,在本公开的实施例中,如图3a所示,开关sw1到sw3耦合在第三电路321与第一i/o节点ion1之间,并且开关sw4到sw6耦合在第四电路322与第二i/o节点ion2之间。可以通过控制信号swen将开关sw1到sw6闭合(接通)/断开,并且可以将开关sw1到sw6闭合(接通)以将第二电路320电耦合到位线bl和参考位线rbl。

44.在图3a中的本公开的实施例中,将第二电路320称为具有偏移补偿功能的电压比较器,其中,减小了对应于读出信号的相同电压差所需的偏移。例如,当闭合开关sw1到sw6以连接其两个端子时,连接到开关sw1到sw6的晶体管pm1到pm4和nm1到nm4接收经由第一i/o节点ion1输入的第一输入电压和经由第二i/o节点ion2输入的第二输入电压。并且,当断开开关sw1到sw6以断开其两个端子时,第三电路321和第四电路322通过使用第一电路310和具有使能信号preb、en1和en2的晶体管m4和m5,使经由第一i/o节点ion1输出的第一输出电压与经由经由第二i/o节点ion2输出的第二输出电压之差加倍。因此,在(经由第一i/o节点ion1和第二i/o节点ion2输入的)第一输入电压与第二输入电压之间的电压差为5mv的情况下,获得的(经由第一i/o节点ion1和第二i/o节点ion2输出的)第一输出电压与第二输出电压之差将为10mv,同时由具有相同输入电压差的电压比较器的第二电路的电路结构(图3b所示)输出的电压差为5mv。

45.图3b中的电路结构是电压比较器。详细地,在第一时段中,将使能信号en1和en2使能为通过晶体管m4和m5将晶体管pm1、pm2、nm1和nm2的源极端子连接到vdd/vss。在第二时段中,闭合开关sw1和sw2(即,开关sw1和sw2连接到其两个端子),并且将经由第一i/o节点ion1的第一输入电压与经由第二i/o节点ion2的第二输入电压之间的输入电压差输入到晶体管pm1、pm2、nm1和nm2,以便产生第一i/o节点ion1和第二i/o节点ion2的输出电压。即,图3b中的电路结构的偏移补偿功能可以小于图3a和图3c中的电压比较器320的偏移补偿功能。由于电压比较器320的更好的偏移补偿功能,所以更容易确定由第一钳位电路122/222提供的电压与由第二钳位电路123/223提供的电压之间的电压差。因此,因为容易确定由第

一钳位电路和第二钳位电路提供的电压之间的电压差,所以将减小发生读干扰的风险。并且,因为电压比较器121/221对于确定由第一钳位电路和第二钳位电路提供的电压之间的电压差是敏感的,所以第一钳位电路122/222和第二钳位电路123/223不需要具有大量的微调分支电路,因此微调电路(即,第一钳位电路122/222和第二钳位电路123/223)的微调范围和面积开销将对应地减少。

46.在另外的实施例中,图3b中的电压比较器的电路结构包括第一p型晶体管pm1和pm2对、第一n型晶体管nm1和nm2对、第四晶体管m4、第五晶体管m5以及开关sw1到sw2。例如,在经由第一i/o节点ion1和第二i/o节点ion2输入第一输入电压与第二输入电压之间的电压差(例如,δv),并且输入第一使能信号en1和第二使能信号en2以闭合第四晶体管m4和第五晶体管m5之后,第四晶体管m4上拉p型晶体管pm1和pm2的源极端子,并且第五晶体管m5下拉n型晶体管nm1和nm2的源极端子。此外,在触发第一使能信号/第二使能信号en1/en2之后,激活来自晶体管pm1、pm2、nm1和nm2的正反馈。因此,图3b中的电压比较器的偏移将是4.6mv。即,图3b中的电路结构的偏移补偿功能可以小于图3a和图3c中的电压比较器320的偏移补偿功能。

47.在另外的实施例中,还可以通过用电容器代替晶体管,改善图3a的第二电路320。具体地,参考图3c,第二电路320包括第四晶体管m4、第五晶体管m5、p型晶体管pm1到pm5、n型晶体管nm1到nm5、电容器c1到c4,其中,电容器c1和c3,例如,代替了图3a中的第二电路320的p型晶体管pm1和pm3,并且电容器c2和c4,例如,代替图3a中的第二电路320的n型晶体管nm2和nm4。p型晶体管pm1和n型晶体管nm1形成第三电路。p型晶体管pm2和n型晶体管nm2形成第四电路。第三电路交叉耦合到第四电路,并且第三电路和第四电路的输出分别耦合到第一i/o节点ion1和第二i/o节点ion2。p型晶体管pm3到pm5形成第五电路,并且n型晶体管nm3到nm5形成第六电路。

48.更详细地,在第五电路中,p型晶体管pm3的第一端子和p型晶体管pm5的第一端子耦合到第一参考电压电平(例如,v

dd

),p型晶体管pm3到pm5的控制端子耦合为接收第一预定信号,p型晶体管pm3的第二端子和p型晶体管pm4的第二端子耦合到第一i/o节点ion1、电容器c1和p型晶体管pm1的第一端子之间的连接节点,并且p型晶体管pm5的第二端子和p型晶体管pm4的第一端子耦合到第二i/o节点ion2、电容器c3和p型晶体管pm2之间的另外的连接节点。

49.第四晶体管m4耦合到第三电路、第四电路和第五电路,其中,第四晶体管m4的第一端子耦合到第一参考电压电平(例如,v

dd

),第四晶体管m4的第二端子耦合到电容器c1与电容器c3之间的连接节点,并且第四晶体管m4的控制端子耦合为接收第一使能信号en1。

50.此外,第五晶体管m5耦合到第三电路、第四电路和第六电路,其中,第五晶体管m5的第一端子耦合到电容器c2与电容器c4之间的连接节点。第五晶体管m5的第二端子耦合到第二参考电压电平(例如,接地),并且第五晶体管m5的控制端子耦合为接收第二使能信号en2。

51.而且,在第六电路中,n型晶体管nm3的第二端子和n型晶体管nm5的第二端子耦合到第二参考电压电平(例如,接地),n型晶体管nm3到nm5的控制端子耦合为接收第二预定信号,n型晶体管nm3的第一端子和n型晶体管nm4的第二端子耦合到第一i/o节点ion1、电容器c2和n型晶体管nm1的第二端子之间的连接节点,并且n型晶体管nm5的第一端子和n型晶体

管nm4的第一端子耦合到第二i/o节点ion2、电容器c4和n型晶体管nm2之间的另外的连接节点。

52.此外,如图3c所示,开关sw1到sw3耦合在第三电路与第一i/o节点ion1之间,并且开关sw4到sw5耦合在第四电路与第二i/o节点ion2之间。可以通过控制信号swen将开关sw1到sw6闭合(接通)/断开,并且可以将开关sw1到sw6闭合(接通)以将第二电路320电耦合到位线bl和参考位线rbl。

53.在本公开的实施例中,可以将第二电路320称为偏移补偿电路,其中,还减小了对应于读出信号的相同电压差所需的偏移。例如,在经由第一i/o节点ion1和第二i/o节点ion2输入第一输入电压与第二输入电压之间的电压差(例如,δv),并且输入第一使能信号en1和第二使能信号en2以闭合第四晶体管m4和第五晶体管m5之后,第四晶体管m4经由电容器c1和c3上拉p型晶体管pm1和pm2的源极端子,并且第五晶体管m5经由电容器c2和c4下拉n型晶体管nm1和nm2的源极端子。此外,在触发第一使能信号/第二使能信号en1/en2之后,激活来自晶体管pm1、pm2、nm1和nm2的正反馈,以扩大输入的电压差(例如,δv),以便经由第一i/o节点ion1和第二i/o节点ion2输出更大的电压差。而且,提供第一使能延迟信号en1d和第二使能延迟信号en2d以向晶体管pm1、pm2、nm1和nm2的源极端子提供vdd/vss,以使输出的电压差轨对轨。

54.以下描述了本公开实施例中图3c的电压比较器320的操作。在第一时段中,将使能信号en1和en2使能为通过晶体管m4和m5以及电容器c1到c4将晶体管pm1、pm2、nm1和nm2的源极端子连接到vdd/vss。在第一时间段中,断开开关sw1到sw6(即,断开开关sw1和sw2与其两个端子),并且禁用使能信号en1d和ed2d。在第二时段中,闭合开关sw1到sw6(即,开关sw1和sw2连接到其两个端子),禁用使能信号en1、en2、en1d和en2d,并且将经由第一i/o节点ion1的第一输入电压与经由第二i/o节点ion2的第二输入电压之间的输入电压差输入到晶体管pm1、pm2、nm1和nm2。在第三时段中,将第一使能延迟信号en1d和第二使能延迟信号en2d使能,闭合开关sw1到sw6(即,开关sw1和sw2连接到其两个端子)并且禁用使能信号en1和en2,并且电容器c1到c4以及晶体管pm1到pm5和nm1到nm5产生第一i/o节点ion1和第二i/o节点ion2的输出电压。换句话说,电容器c1到c4以及晶体管pm1到pm5和nm1到nm5的电路结构形成电荷泵功能的结构,并且经由第一i/o节点ion1输出的第一输出电压与经由第二i/o节点ion2输出的第二输出电压之间的输出电压差在第一时段到第三时段加倍。在实施例中,期望的偏移还将减小8%(例如,从3.8mv/σ减小到3.5mv/σ)。即,图3b中的电路结构的偏移补偿功能可能小于图3c中电压比较器320的偏移补偿功能。

55.在本公开的一些实施例中,一个或多个电容器用于存储对应于输入电压差的电荷,并且将存储在一个或多个电容器中的电荷放电以消除器件在读出阶段期间的失配。详细地,尽管不触发第一使能信号/第二使能信号en1/en2(即,禁用第一使能信号/第二使能信号en1/en2),但是为了保持电容器c1到c4的两个端子的电压,电容器c1到c4存储对应于输入电压差的电荷。并且,尽管触发第一使能信号/第二使能信号en1/en2(即,将第一使能信号/第二使能信号en1/en2使能),将存储在电容器c1到c4中的电荷放电以消除器件在读出阶段期间的失配。

56.参考图3d,在实施例中,第二电路320包括第四晶体管m4、第五晶体管m5、p型晶体管pm1和pm2、n型晶体管nm1和nm2、电容器c1和c2以及开关sw1到sw8。电容器c1、p型晶体管

pm1和n型晶体管nm1形成第三电路321。电容器c2、p型晶体管pm2和n型晶体管nm2形成第四电路322。第三电路通过开关sw7和sw8交叉耦合到第四电路,并且第三电路和第四电路的输出分别耦合到第一i/o节点ion1和第二i/o节点ion2。

57.更详细地,第四晶体管m4耦合到第三电路321和第四电路322,其中,第四晶体管m4的第一端子耦合到第一参考电压电平(例如,v

dd

),第四晶体管m4的第二端子耦合到第四晶体管m4、第三电路321和第四电路322之间的连接节点,并且第四晶体管m4的控制端子耦合为接收第一使能信号en1。此外,第五晶体管m5耦合到第三电路321和第四电路322,其中,第五晶体管m5的第一端子耦合到第五晶体管m5、第三电路321和第四电路322之间的连接节点。第五晶体管m5的第二端子耦合到第二参考电压电平(例如,接地),并且第五晶体管m5的控制端子耦合为接收第二使能信号en2。

58.电容器c1的第一端子经由开关sw8耦合到p型晶体管pm2与n型晶体管nm2之间的第一连接节点,并且电容器c1的第二端子经由开关sw2耦合到p型晶体管pm1与n型晶体管nm1之间的第二连接节点,并耦合到n型晶体管nm1的控制端子。电容器c2的第一端子经由开关sw7耦合到p型晶体管pm1与n型晶体管nm1之间的第二连接节点,电容器c2的第二端子经由开关sw5耦合到p型晶体管pm2与n型晶体管nm2之间的第一连接节点,并耦合到n型晶体管nm2的控制端子。

59.开关sw1耦合在第一i/o节点ion1与第二连接节点之间,并且开关sw4耦合在第二i/o节点ion2与第一连接节点之间。此外,开关sw3耦合在第二参考电压电平(例如,接地)与电容器c1的第一端子之间,并且开关sw6耦合在第二参考电压电平(例如,接地)与电容器c2的第一端子之间。

60.以下描述了图3d中电路结构的操作。在第一时段中,将使能信号en1和en2使能为通过晶体管m4和m5将晶体管pm1、pm2、nm1和nm2的源极端子连接到vdd/vss,并且闭合开关sw2到sw3和sw5到sw8。在第二时段中,闭合开关sw1和sw4(即,开关sw1和sw2连接到其两个端子),并且将经由第一i/o节点ion1的第一输入电压与经由第二i/o节点ion2的第二输入电压之间的输入电压差输入到晶体管pm1、pm2、nm1和nm2,以便产生第一i/o节点ion1和第二i/o节点ion2的输出电压。在第二时段中,闭合开关sw2到sw3和sw5到sw8。在第三时段中,断开开关sw2到sw3和sw5到sw8,闭合开关sw1和sw4,禁用使能信号en1和en2,并且由电容器c1到c4以及晶体管pm1到pm5和nm1到nm5向第一i/o节点ion1和第二i/o节点ion2产生输出电压。换句话说,电容器c1到c2以及晶体管pm1到pm2和nm1到nm2的电路结构形成电荷泵功能的结构,并且经由第一i/o节点ion1输出的第一输出电压与经由第二i/o节点ion2输出的第二输出电压之间的输出电压差在第一时段到第三时段加倍。

61.参考图3e,在另外的实施例中,第二电路320包括p型晶体管pm1和pm2、n型晶体管nm1和nm2、电容器c1以及开关sw1到sw10。电容器c1、p型晶体管pm1和n型晶体管nm1形成第三电路321。p型晶体管pm2和n型晶体管nm2形成第四电路322。第三电路通过开关sw7和sw8交叉耦合到第四电路,并且第三电路和第四电路的输出分别耦合到第一i/o节点ion1和第二i/o节点ion2。

62.更详细地,开关sw1耦合到第三电路321和第四电路322,其中,开关sw1的第一端子耦合到第一参考电压电平(例如,v

dd

),开关sw1的第二端子耦合到第三电路321(p型晶体管pm1)与第四电路322(p型晶体管pm2)之间的连接节点。此外,开关sw2耦合到第三电路321和

第四电路322,其中,开关sw2的第二端子耦合到第二参考电压电平(例如,接地),开关sw2的第一端子耦合到第三电路321(n型晶体管nm1)与第四电路322(n型晶体管nm2)之间的连接节点。

63.电容器c1的第一端子经由开关sw7耦合到p型晶体管pm2与n型晶体管nm2之间的第一连接节点,并且电容器c1的第二端子耦合到p型晶体管pm1、n型晶体管nm1和开关sw9之间的连接节点

64.开关sw3耦合在第一i/o节点ion1与第二连接节点之间,并且开关sw4耦合在第二i/o节点ion2与第一连接节点之间。此外,开关sw5耦合在第二参考电压电平(例如,接地)与第二连接节点之间,并且开关sw6耦合在第二参考电压电平(例如,接地)与第一连接节点之间。

65.此外,开关sw10耦合在第一连接节点与p型晶体管pm2的控制端子与n型晶体管nm2的控制端子之间的连接节点之间;并且开关sw9耦合在第二连接节点与p型晶体管pm1的控制端子与n型晶体管nm1的控制端子之间的连接节点之间。

66.在图3e中,第二电路320还包括p型晶体管pm3和pm4、n型晶体管nm3到nm5、参考电流产生器、电阻器r

ap1

、r

ap2

和r

p

。参考电流产生器的输出节点耦合到p型晶体管pm3和pm4的控制端子。p型晶体管pm3和pm4分别根据参考电流产生器的输出节点产生的偏置电压v

偏置_r

产生i

读

和2i

读

。第一i/o节点ion1耦合到第三开关sw3的一个节点和位线bl,并且第二i/o节点ion2耦合到第四开关sw4的一个节点和参考位线rbl。n型晶体管nm3到nm5的控制端子耦合到字线wl。n型晶体管nm3的漏极端子通过电阻器r

ap1

耦合到位线bl,并且n型晶体管nm3的源极端子通过第十一开关sw11耦合到接地端子。n型晶体管nm4的漏极端子通过电阻器r

ap2

耦合到参考位线rbl,并且n型晶体管nm4的源极端子耦合到接地端子。n型晶体管nm5的漏极端子通过电阻器r

p

耦合到参考位线rbl,并且n型晶体管nm5的源极端子耦合到接地端子。

67.以下描述了本公开的实施例中图3e的电压比较器320的操作。在第一时段中,闭合开关sw1到sw2和sw5到sw6,以将晶体管pm1、pm2、nm1和nm2的源极端子连接到vdd/vss。在第一时段中,闭合开关sw3到sw4和sw7到sw10。在第二时段中,i

参考

产生器产生偏压v

偏置_r

,以根据偏压v

偏置_r

分别产生电流i

读

和2i

读

,以便产生经由第一i/o节点ion1和第二i/o节点ion2输入的第一输入电压和第二输入电压。在第二时段中,开关sw7到sw10仍然闭合。在第三时段中,开关sw7到sw10断开,并且开关sw3到sw4闭合。在第三时段期间,因为电容器c1的两个端子之间存在电压差,所以根据电容器c1的电压差,推开了经由i/o节点ion1的第一输出电压与经由i/o节点ion2的第二输出电压之差值,使得更容易确定位线bl与参考位线rbl的电压差。

68.如图3a所示,可微调的钳位电路中的每个可以具有主分支电路和多个微调分支电路。每个微调分支电路具有电流路径和开关,每个开关用于传导或不传导图1中的电流路径并且由控制器140控制。图1中的控制器140控制微调分支电路中的许多开关,并且读出对应于位线bl的电压v

bl

和对应于参考位线rbl的v

rbl

相同或不相同,以便将电压v

bl

和v

rbl

微调到相同的电压电平。

69.例如,参考图4a,第一钳位电路222包括第一主分支电路mb1和多个第一微调分支电路tb1(1)-tb1(n)。第一主分支电路mb1包括具有第一端子、第二端子和控制端子的第一主晶体管mt1以及第一主开关ms1。第一主晶体管mt1的第一端子耦合到第一i/o节点ion1与

第一钳位电路222之间的第一连接节点n1,并且第一主晶体管mt1的控制端子耦合为接收钳位电压(v

钳位

)。第一主开关ms1耦合在第一主晶体管mt1的第二端子与位线bl之间,其中,将第一主开关ms1导通以将位线bl电耦合到第一主晶体管mt1,并且将第一主开关ms1截止以使位线bl与第一主晶体管mt1电隔离。

70.第一微调分支电路tb1(1)-tb1(n)中的每个包括具有第一端子、第二端子和控制端子的第一微调晶体管tt1以及第一微调开关ts1。第一微调晶体管tt1的第一端子耦合到第一连接节点n1,并且第一微调晶体管tt1的控制端子耦合为接收钳位电压(v

钳位

)。第一微调开关ts1耦合在第一微调晶体管tt1的第二端子与第一主开关ms1与位线bl之间的第二连接节点n2之间,其中,将第一微调开关ts1导通以将位线bl电耦合到第一微调晶体管tt1,并且将第一微调开关ts1截止以将位线bl与第一微调晶体管tt1电隔离。

71.类似地,参考图4b,第二钳位电路223包括第二主分支电路mb2和多个第二微调分支电路tb2(1)-tb2(n)。第二主分支电路mb2包括具有第一端子、第二端子和控制端子的第二主晶体管mt2以及第二主开关ms2。第二主晶体管mt2的第一端子耦合到第二i/o节点ion2与第二钳位电路223之间的第一连接节点n1,并且第二主晶体管mt2的控制端子耦合为接收钳位电压(v

钳位

)。第二主开关ms2耦合在第二主晶体管mt2的第二端子与参考位线rbl之间,其中,将第二主开关ms2导通以将参考位线rbl电耦合到第二主晶体管mt2,并且将第二主开关ms2截止以将位线bl与第二主晶体管mt2电隔离。

72.第二微调分支电路tb2(1)-tb2(n)中的每个包括具有第一端子、第二端子和控制端子的第二微调晶体管tt2以及第二微调开关ts2。第二微调晶体管tt2的第一端子耦合到第一连接节点n1,并且第二微调晶体管tt2的控制端子耦合为接收钳位电压(v

钳位

)。第二微调开关ts2耦合在第二微调晶体管tt2的第二端子与第二主开关ms2与参考位线rbl之间的第二连接节点n2之间,其中,将第二微调开关ts2导通以将参考位线rbl电连接到第二微调晶体管tt2,并且将第二微调开关ts2截止以将参考位线rbl与第二微调晶体管tt2电隔离。

73.应当提及的是,在本公开的实施例中,n表示微调分支电路的总量,p是表示闭合的微调分支电路的预定量的默认值。在本公开的一个实施例中,可以将p设置为

‘8’

并且可以将n设置为

‘

16’。换句话说,第一钳位电路222中初始闭合的第一微调分支电路的数量为8,即,第一微调分支电路tb1(1)-tb1(8)闭合;第二钳位电路222中初始闭合的第二微调分支电路的数量为8,即,第二微调分支电路tb2(1)-tb2(8)闭合。实施本公开的实施例的那些人可以将p和n设置为其它数字。例如,可以将p设置为数字

‘1’

到

‘

16’中的一个,而将n设置为

‘

16’。在其它实施例中,可以将p设置为数字

‘1’

到

‘

32’中的一个,并且可以将n设置为

‘

32’。

74.在实施例中,第一主分支mb1可以不包括第一主开关ms1,并且第二主分支mb2可以不包括第二主开关ms2。换句话说,在此实施例中,第一主晶体管/第二主晶体管mt1/mt2的第二端子耦合到第二连接节点n2。

75.在实施例中,通过闭合或断开第一微调开关ts1

1-ts1n中的一个或多个来微调对应于位线bl的电压(例如,v

bl

),并且对应于位线bl的微调的电压与第一钳位电路222的当前闭合的第一微调开关的总数成比例。此外,通过闭合或断开第二微调开关ts2

1-ts2n中的一个或多个来微调对应于参考位线rbl的电压(例如,v

rbl

),并且对应于参考位线rbl的微调的电压与第二钳位电路223的当前闭合的第二微调开关的总数成比例。在实施例中,图2中的控制器120可以读出从第一i/o节点ion1和第二i/o节点ion2输出的读出信号,以控制图4a和

图4b中第一微调开关ts1

1-ts1n和第二微调开关ts2

1-ts2n,用于根据读出信号调节/微调第一i/o节点ion1和第二i/o节点ion2上的电压。在实施例中,图2中的控制器120可以使用逐步微调方案或二进制近似微调方案来确定第二微调开关ts2

1-ts2n是闭合还是断开,换句话说,用于确定闭合的第二微调开关ts2

1-ts2n的数量和断开的其它第二微调开关ts2

1-ts2n。

76.再次参考图3a,读出放大器220还包括第一电阻器r

bl

和第二电阻器r

rbl

。第一电阻器rbl耦合在第一钳位电路222与位线bl之间,并且第二电阻器rrbl耦合在第二钳位电路223与参考位线rbl之间。第一电阻器r

bl

可以是图1中的存储器单元112的等效电阻,并且第二电阻器r

bl

可以是图1中的参考单元114的等效电阻。

77.参考图5和图6,在本公开的实施例中,读出放大器120包括具有微调校正功能的电压比较器124(例如,可微调的电压比较器)和具有减小的偏移功能的钳位器件125(例如,偏移补偿钳位器件)。更具体地,读出放大器120包括电压比较器124和钳位器件125。电压比较器124耦合到位线bl和参考位线rbl,并被配置为比较第一输入电压和第二输入电压以输出读出信号。钳位器件125耦合在电压比较器124、位线bl和参考位线rbl之间。读出放大器120还包括控制器140。控制器140可以耦合到电压比较器124和钳位器件125,用于控制到电压比较器124和钳位器件125的切换,以便实施电压比较器124和钳位器件125的功能。详细地,电压比较器124的一个实例是图6中的电压比较器524,并且在第一微调分支电路和第二微调分支电路中存在多个开关。图2中的控制器120可以使用逐步微调方案或二进制近似微调方案来确定第一微调分支电路中的每个和第二微调分支电路中的每个是闭合还是断开。

78.此外,参考图5,电压比较器124还被配置为微调对应于位线bl的第一电压v1,并微调对应于参考位线rbl的第二电压v2,并且钳位器件125被配置为根据输入到钳位器件125的偏置电压v

偏置

提供第一钳位电压和第二钳位电压。详细地,钳位器件125需要参考电压来根据偏置电压v

偏置

了解位线bl和参考位线rbl上的电压具有或不具有偏移电压差,以实施偏移补偿功能。第一输入电压和第二输入电压分别输入到第一i/o节点和第二i/o节点,并且分别从读出放大器120的第一i/o节点和第二i/o节点输出对应于读出信号的第一输出电压和第二输出电压。

79.在本公开的实施例中,电压比较器524包括:第一电路610、第二电路620和第三电路630。第二电路620经由第一i/o节点ion1、第二i/o节点ion2、第一连接节点cn1和第二连接节点cn2交叉耦合到第三电路630。

80.第一电路包括第一晶体管m1、第二晶体管m2和第三晶体管m3。第一晶体管m1的第一端子和第二晶体管m2的第一端子耦合到第一参考电压电平(例如,v

dd

),第一晶体管m1的控制端子、第二晶体管m2的控制端子和第三晶体管m3的控制端子耦合为接收预充电信号preb,第一晶体管m1的第二端子和第三晶体管m3的第二端子耦合到第一节点n1、第一晶体管m1和第三晶体管m3之间的连接节点,并且第二晶体管m2的第二端子和第三晶体管m3的第一端子耦合到第二节点n2、第二晶体管m2和第三晶体管m3之间的另外的连接节点。

81.第二电路620包括第四晶体管m4、第一主分支电路(如图6所示,n型晶体管);以及多个第一微调分支电路。第四晶体管m4的第一端子耦合到第一参考电压电平,第四晶体管m4的控制端子耦合到第一节点n1,并且第四晶体管m4的第二端子经由第一i/o节点ion1耦合到第一主分支电路。第一微调分支电路的第二端子经由第三节点n3耦合到第一主分支电路的第二端子,第一微调分支电路的控制端子耦合到第一主分支电路的n型晶体管的控制

端子。

82.第三电路630包括第五晶体管m5、第二主分支电路(如图6所示,第三电路630中的n型晶体管);以及多个第二微调分支电路。第五晶体管m5的第一端子耦合到第一参考电压电平,第五晶体管m5的控制端子耦合到第二节点n2,并且第五晶体管m5的第二端子经由第二i/o节点ion2耦合到第二主分支电路。第二微调分支电路的第二端子经由第四节点n4耦合到第二主分支电路的第二端子,第二微调分支电路的控制端子耦合到第二主分支电路的n型晶体管的控制端子。

83.应当提及的是,电压比较器524的第三电路620和第四电路630两者具有微调电路(例如,第一微调分支电路和第二微调分支电路),但是本公开并不限于此。例如,在另一个实施例中,仅第三电路620或第四电路630可以具有微调电路。换句话说,在另一个实施例中,电压比较器524可以仅通过具有微调电路的第三电路620或第四电路630来提供微调校正功能。下面参考图7a和图7b描述微调电路的细节。

84.参考图7a,第三电路620的第一主分支电路mt1包括第一主晶体管mt1,其中,第一主晶体管mt1的第一端子耦合到第一i/o节点ion1,第一主晶体管mt1的控制端子耦合到第一节点n1与第二i/o节点ion2之间的第一连接节点cn1,并且第一主晶体管mt1的第二端子耦合到第三节点n3。

85.第一微调分支电路tb1(1)-tb1(m)中的每个包括第一微调开关ts1和第一微调晶体管tt1,其中,第一微调晶体管tt1的第一端子耦合到第一微调开关ts1,第一微调晶体管tt1的控制端子耦合到第一连接节点cn1,并且第一微调晶体管tt1的第二端子耦合到第三节点n3。

86.第一微调开关ts1耦合在第一微调晶体管tt1的第一端子与第一参考电压电平(例如,v

dd

)之间,其中,第一微调开关ts1导通以将第一参考电压电平电耦合到第一微调晶体管tt1,并且第一微调开关ts1截止以将第一参考电压电平与第一微调晶体管tt1电隔离。通过闭合或断开第一微调开关ts1中的一个或多个来微调对应于第三节点n3的电压,并且对应于第三节点n3的微调的电压与第三电路620的当前闭合的第一微调开关ts1的总数成比例。

87.类似地,参考图7b,第四电路630的第二主分支电路mt2包括第二主晶体管mt2,其中,第二主晶体管mt2的第一端子耦合到第二i/o节点ion2,第二主晶体管mt2的控制端子耦合到第二节点n2与第一i/o节点ion1之间的第二连接节点cn2,并且第二主晶体管mt2的第二端子耦合到第四节点n4。

88.第二微调分支电路tb2(1)-tb2(m)中的每个包括第二微调开关ts2和第二微调晶体管tt2,其中,第二微调晶体管tt2的第一端子耦合到第二微调开关ts2,第二微调晶体管tt2的控制端子耦合到第二连接节点cn2,并且第二微调晶体管tt2的第二端子耦合到第四节点n4。

89.第二微调开关ts2耦合在第二微调晶体管tt2的第一端子与第一参考电压电平(例如,v

dd

)之间,其中,将第二微调开关ts2导通以将第一参考电压电平电耦合到第二微调晶体管tt2,并且将第二微调开关ts2截止以将第一参考电压电平与第二微调晶体管tt2电隔离。通过闭合或断开第二微调开关ts2中的一个或多个来微调对应于第四节点n4的电压,并且对应于第四节点n4的微调的电压与第四电路630的当前闭合的第二微调开关ts2的总数成比例。

90.应当提及的是,在本公开的实施例中,m表示微调分支电路的总量,q是表示闭合的微调分支电路的预定量的默认值。在一个实施例中,可以将q设置为

‘4’

,并且可以将m可以设置为

‘8’

。换句话说,第三电路620中初始闭合的第一微调分支电路的数量为4,即,第一微调分支电路tb1(1)-tb1(4)闭合;第四电路630中初始闭合的第二微调分支电路的数量为4,即,第二微调分支电路tb2(1)-tb2(4)闭合。实现本公开的实施例的那些人可以将q和m设置为其它数字。例如,可以将q设置为数字

‘1’

到

‘8’

中的一个,而将m设置为

‘8’

。在其它实施例中,可以将q设置为数字

‘1’

到

‘

16’中的一个,并且可以将m设置为

‘

16’。

91.在实施例中,通过闭合或断开第一微调开关ts1

1-ts1n中的一个或多个来微调对应于位线bl的电压(例如,对应于第三节点n3的电压),并且对应于位线bl的微调的电压与第三电路620的第一微调分支电路tb1(1)-tb1(m)的当前闭合的第一微调开关的总数成比例。此外,通过闭合或断开第二微调开关ts2

1-ts2n中的一个或多个来微调对应于参考位线rbl的电压(例如,对应于第四节点n4的电压),并且对应于参考位线rbl的微调的电压与第四电路630的第二微调分支电路tb2(1)-tb2(m)的当前闭合的第二微调开关的总数成比例。

92.应当注意,在逐步精细调整方案或二进制近似精细调整方案的情况下,由于钳位器件525提供减小的偏移功能以补偿由图5中由控制器140控制的晶体管nm1与晶体管nm2之间的失配,可以减少所需的微调步骤/范围。因此,可以将图6中可微调的电压比较器中的微调分支电路(即,m)的总数设置为小于图3a中可微调的钳位电路中的微调分支电路(即,n)的总数;并且可以将图6中可微调的电压比较器中的初始闭合的微调分支电路(即,q)的量设置为小于图3a中可微调的钳位电路中的初始闭合的微调分支电路(即,p)的量的值。

93.参考图6和图8a,钳位器件525包括第一钳位电路640、第二钳位电路650和运算放大器op。第一钳位电路640耦合在电压比较器524与位线bl之间。第二钳位电路650耦合在电压比较器524与参考位线rbl之间。

94.运算放大器op具有输出端子、第一输入端子和第二输入端子,其中,输出端子耦合到第一钳位电路640与第二钳位电路650之间的连接节点,第一输入端子耦合为接收偏置电压(例如,v

偏置

),并且第二输入端子耦合到第一钳位电路640与第二钳位电路650之间的另外的连接节点。

95.第一钳位电路640包括第一晶体管nm1、第一开关sw1、第二开关sw2和第一电容器c1。第一晶体管nm1的第一端子耦合到第二电路620的第三节点n3,第一晶体管nm1的控制端子耦合到第一开关sw1与第一电容器c1的第一端子之间的第一连接节点,其中,第一电容器c1的第二端子耦合到第二参考电压电平(例如,接地)。第一开关sw1耦合在第一连接节点cn1与第一钳位电路640与第二钳位电路650之间的连接节点之间,其中,将第一开关sw1导通以将连接节点电耦合到第一晶体管nm1和第一电容器c1,并且将第一开关sw1截止以将连接节点与第一晶体管nm1和第一电容器c1电隔离。

96.第二开关sw2耦合在第一晶体管nm1的第二端子与第一钳位电路640与第二钳位电路650之间的另外的连接节点之间,其中,将第二开关sw2导通以将另外的连接节点电耦合到第一晶体管nm1,并且将第二开关sw2截止以将另外的连接节点与第一晶体管电隔离。第一电容器c1被配置为将对应于电压的电荷存储到第一晶体管nm1的控制端子。

97.第二钳位电路650包括第二晶体管nm2、第三开关sw3、第四开关sw4和第二电容器c2。第二晶体管nm2的第一端子耦合到第三电路630的第四节点n4,第二晶体管nm2的控制端

子耦合到第三开关sw3与第二电容器c2的第一端子之间的第二连接节点cn2,并且第二电容器c2的第二端子耦合到第二参考电压电平(例如,接地)。第三开关sw3耦合在第二连接节点cn2与第一钳位电路640与第二钳位电路650之间的连接节点之间,其中,将第三开关sw3导通以将连接节点电耦合到第二晶体管nm2第二电容器c2,并且将第三开关sw3截止以将连接节点与第二晶体管nm2和第二电容器c2电隔离。

98.第四开关sw4耦合在第二晶体管nm2的第二端子与第一钳位电路640与第二钳位电路650之间的另外的连接节点之间,其中,将第四开关sw4导通以将另外的连接节点电耦合到第二晶体管nm2,并且将第四开关sw4截止以将另外的连接节点与第二晶体管nm2电隔离。第二电容器c2被配置存储将对应于第二晶体管c2的控制端子的电压的电荷。在图8b中的步骤s810到s850中描述本公开实施例中图8a电压比较器的操作。

99.以下描述本公开的实施例中图7a和7b的电压比较器的操作。以图7a为例,图7a中的第二电路620包括具有晶体管m4和mt1的主分支电路和多个第一微调分支电路。每个第一微调分支电路具有经由每个第一微调晶体管tt11到tt1m和第一微调开关ts11到ts1m的电流路径。每个第一微调开关ts11到ts1m用于传导或不传导电流路径,并且由图5中的控制器140控制。图5中的控制器140控制微调分支电路中的许多开关,并且读出对应于位线bl的电压v

bl

和对应于参考位线rbl的v

rbl

相同或不相同,以便将电压v

bl

和v

rbl

微调到相同的电压电平。图5中的控制器140可以使用逐步微调方案或二进制近似微调方案来确定对应于位线bl和对应于参考位线rbl的断开的第一微调开关ts11到ts1m的数量和闭合的其它第一微调开关ts11到ts1m的数量相同或不同。并且,图7b中的第三电路630包括具有晶体管m5和mt2的主分支电路以及多个第二微调分支电路。每个第二微调分支电路具有经由每个第二微调晶体管tt21到tt2m和第二微调开关ts21到ts2m的电流路径。每个第二微调开关ts21到ts2m用于导通或不导通电流路径,并且由图5中的控制器140控制。图7b中的第三电路630的操作可以与图7a中的第二电路620的操作相同。

100.图8b示出了根据本公开的一些实施例的通过图8a中的偏移补偿钳位器件对钳位电压进行充电的流程图。图8b的流程图的步骤可以由图5中的控制器140实施,同时执行钳位器件525的偏移补偿功能,以根据图8a中的v

bl

和v

rbl

对钳位电压进行充电。可以由处理器、集成电路、微控制器(mcu)或其它类型的控制电路模块来实施图5中的控制器140。参考图8a和图8b,在步骤s810中,通过控制信号se1(例如,在高电平处)闭合钳位器件525的第一钳位电路640的第一开关sw1和第二开关sw2,并且通过控制信号se2(例如,在低电平处)断开钳位器件525的第二钳位电路650的第三开关sw3和第四开关sw4,以便对第一钳位电路640的第一电容器c1充电。当运算放大器op进入稳态时,将第一电容器c1充电到第一钳位电压v

钳位1

。即,在位线bl上的电压大于偏置电压v

bl

的同时,运算放大器op进入稳态。

101.在步骤s820中,响应于确定运算放大器op进入稳态,确定第一电容器c1的充电完成,其中,输入到运算放大器op的偏置电压v

偏置

等于运算放大器op进入稳态时第一钳位电路640的第一晶体管nm1的第二端子的电压(例如,v

bl

)。换句话说,响应于在闭合第一开关sw1和第二开关sw2两者和断开第三开关sw3和第四开关sw4两者之后运算放大器op进入稳态,从图6的第一电阻器r

bl

获得的在第三节点cn3处的电压等于偏置电压v

偏置

,并且将对应于第一晶体管nm1的控制端子的电压(例如,v

钳位1

)的电荷存储在第一电容器c1中。

102.在步骤s830中,通过控制信号se1(例如,在低电平处)断开第一钳位电路640的第

一开关sw1和第二开关sw2,并且通过控制信号se2(例如,在高电平处)闭合第二钳位电路650的第三开关sw3和第四开关sw4,以便对第二钳位电路650的第二电容器c2充电。当运算放大器op进入另外的稳态时,将电容器c2充电到第二钳位电压v

钳位2

。即,在参考位线rbl上的电压大于偏置电压v

bl

的同时,运算放大器op进入另外的稳态。

103.在步骤s840中,响应于确定运算放大器op进入另外的稳态,确定第二电容器的充电完成,其中,输入到运算放大器op的偏置电压v

偏置

等于运算放大器op进入另外的稳态时第二钳位电路650的第二晶体管nm2的第二端子的电压(例如,v

rbl

)。换句换说,响应于在断开第一开关sw1和第二开关sw2以及闭合第三开关sw3和第四开关sw4两者之后运算放大器op进入另外的稳态,从图6的第二电阻器r

rbl

获得的在第四节点cn4处的电压等于偏置电压v

偏置

,并且将对应于第二晶体管nm2的控制端子的电压(例如,v

钳位2

)的电荷存储在第二电容器c2中。

104.换句话说,在步骤s810-s840之后,在向n型晶体管nm1和nm2的控制端子提供第一钳位电压v

钳位1

和第二钳位电压v

钳位2

的同时,通过电容器c1和c2获得第一钳位电压v

钳位1

和第二钳位电压v

钳位2

,并且与n型晶体管nm1和nm2的第二端子(即,第三节点cn3和第四节点cn4)相对应的电压将是相同的(例如,v

偏置

),以便消除由于不可避免的工艺变化而引起的n型晶体管nm1于nm2之间的失配的影响。

105.应当注意,偏置电压v

偏置

的值根据存储器单元的类型预定。例如,对于mram(磁阻随机存取存储器),可以将偏置电压v

偏置

设置为约200mv;对于rram(电阻式随机存取存储器),可以将偏置电压v

偏置

设置为约300mv。如果将偏置电压v

偏置

的值设置为比合适电平高得多的值(例如,对于mram为400mv,对于rram为600mv),则发生读干扰现象的可能性将大大增加。

106.图8c示出了根据本公开的一些实施例的通过图8a中的偏移补偿钳位器件对钳位电压进行放电的流程图。图8c的流程图的步骤可以由图5中的控制器140实施,同时执行钳位器件525的偏移补偿功能,以根据图8a中的v

bl

和v

rbl

对钳位电压进行放电。参考图8a和图8c,在步骤s850中,通过控制信号se1和se2将第一开关、第二开关、第三开关和第四开关断开。

107.接着,在步骤s860中,第一电容器c1通过使第一钳位电路640的第一电容器c1放电向第一钳位电路640的第一晶体管nm1的控制端子提供第一钳位电压v

钳位1

;在步骤s870中,通过使第二钳位电路650的第二电容器c2放电,向第二钳位电路650的第二晶体管nm2的控制端子提供第二钳位电压v

钳位2

。

108.接着,在步骤s880中,获得分别对应于位线bl和参考位线rbl的相同的位线电压v

bl

和参考位线电压v

rbl

,以便减小第一钳位电路640(例如,第一晶体管nm1)和第二钳位电路650(例如,第二晶体管nm2)的失配的影响。具体地,由于第一晶体管nm1和第二晶体管nm2的控制端子接收第一钳位电压v

钳位1

和第二钳位电压v

钳位2

,所以保持第一晶体管nm1和第二晶体管nm2,并且第一晶体管nm1和第二晶体管nm2的第二端子处的电压(例如,v

bl

和v

rbl

)将相同(例如,与偏置电压v

偏置

相同)。

109.图9示出了根据本公开的一些实施例的通过微调支路来调节钳位器件尺寸的示意图。参考图9和图4a(或图4b),建议曲线表示所提供的可微调的微调步骤/范围与钳位器件的尺寸之间的关系。中间钳位尺寸“100%”是对应于“100%”微调步骤(例如,闭合了8个微调分支电路)的钳位器件(例如,第一钳位电路/第二钳位电路)的默认尺寸。钳位器件尺寸

表示第一钳位电路/第二钳位电路的晶体管的宽度与长度之比的总量。微调分支电路的所有的晶体管的器件尺寸是预定的并且不同。

110.此外,如图9中的箭头所示,闭合更多的微调支路将增加钳位器件尺寸,而闭合更少的微调分支电路将减小钳位器件尺寸。每个微调步骤可能影响1.3%的默认位线电压或默认参考位线电压。

111.例如,如果需要降低第二钳位电路223的参考位线电压v

rbl

来补偿第一钳位电路222的失配,则将闭合的第二微调开关的量从8(默认闭合的第二微调开关的量)调节为7(例如,在断开第二微调开关ts18之后当前闭合第二微调开关ts1

1-ts17),并且将参考位线电压v

rbl

减小到参考位线电压v

rbl

的初始100%的98.7%。同时,将第二钳位电路的钳位器件尺寸减小到初始钳位器件尺寸(100%)的约92%。在本公开的实施例中,所提出的曲线的公式为:

112.y=55.258x

3-140.46x2+121.81x-35.609

113.y表示钳位器件尺寸,并且x表示与对应于参考位线的位线的初始100%电压(例如,v

bl

或v

rbl

)相比的预期百分比。例如,假设x等于1.013(闭合的微调分支电路的总量从8调节为9,则预期的微调电压为100%电压的101.3%(100%+1.3%))。根据以上公式,将钳位器件尺寸(y)调节为初始100%钳位器件尺寸的109%。

114.应当注意,在本公开的实施例中,微调步骤中的每个的间隔是初始电压的1.3%,但本发明不限于此。例如,在另一个实施例中,可以根据建议的曲线的公式将微调步骤中的每个的间隔设置为其它值。此外,一个可微调的钳位电路的微调分支电路的总量将增加到大于16的值(例如,如虚线所示)。

115.再次参考图6,读出放大器520还包括第一电阻器r

bl

和第二电阻器r

rbl

。第一电阻器r

bl

耦合在位线bl与第二开关sw2与第一晶体管nm1的第二端子之间的第三连接节点cn3之间。第二电阻器r

rbl

耦合在参考位线rbl与第四开关sw4与第二晶体管nm2的第二端子之间的第四连接节点cn4之间。此外,在闭合第一开关sw1和第二开关sw2两者并且断开第三开关sw3和第四开关sw4两者之后,获得对应于位线bl的第一电阻器r

bl

的电压(例如,v

bl

),并且在闭合第三开关sw3和第四开关sw4两者并且断开第一开关sw1和第二开关sw2两者之后,获得对应于参考位线rbl的第二电阻器r

rbl

的电压(例如v

rbl

)。而且,当开关sw1-sw4断开时,获得等于偏置电压v

偏置

的电压v

bl

和电压v

rbl

。

116.参考图10,在本公开的实施例中,读出放大器120包括偏移补偿和可微调的电压比较器126(例如,电压比较器具有偏移补偿功能和微调校正功能)、第一钳位电路127和第二钳位电路128。第一钳位电路127和第二钳位电路128可以是例如,图3a中具有主分支电路的钳位电路,并且,第一钳位电路127和第二钳位电路128不具有图3a中的多个微调分支电路。读出放大器120还包括控制器140。控制器140可以耦合到偏移补偿和可微调的电压比较器126,用于控制到偏移补偿和可微调的电压比较器126的切换,以便实施偏移补偿和可微调的电压比较器126的功能。

117.参考图11,在本公开的实施例中,读出放大器120包括常规的电压比较器129,以及偏移补偿和可微调的钳位器件130(例如,钳位器件具有偏移补偿功能和微调校正功能)。读出放大器120还包括控制器140。控制器140可以耦合到偏移补偿和可微调的钳位器件130,用于控制到偏移补偿和可微调的钳位器件130的切换,以便实施偏移补偿和可微调的钳位

器件130的功能。

118.基于前述实施例,所提供的具有偏移补偿功能和微调校正功能的读出放大器以及使用其的非易失性存储器能够减少所需的用于补偿与位线和参考位线相对应的晶体管的失配的调节偏移,并且微调对应于位线和参考位线的电压,以补偿对应于位线和参考位线的晶体管的失配。此外,由于所提供的偏移补偿钳位器件,因此可以减少对应于可微调的电压比较器的微调步骤/范围的总量。因此,通过所提供的读出放大器将提高在存储器单元上执行的读出操作(读操作)的效率和精度。

119.在本公开的一些实施例中,提供了一种读出放大器。所述读出放大器包括具有偏移补偿的电压比较器、第一钳位电路和第二钳位电路。具有偏移补偿的所述电压比较器分别经由所述读出放大器的第一i/o节点和第二i/o节点耦合到位线和参考位线,并且被配置为比较第一输入电压和第二输入电压以输出读出信号。所述第一钳位电路耦合在所述第一i/o节点与所述位线之间。所述第二钳位电路耦合在所述第二i/o节点与所述参考位线之间。所述第一钳位电路和所述第二钳位电路分别微调对应于所述位线的电压和对应于所述参考位线的电压,以使对应于所述参考位线的所述电压与对应于所述位线的所述电压进行匹配。

120.在上述读出放大器中,第一钳位电路包括第一主分支电路和多个第一微调分支电路,其中,第一主分支电路包括:第一主晶体管,具有第一端子、第二端子和控制端子,其中,第一主晶体管的第一端子耦合到第一i/o节点与第一钳位电路之间的第一连接节点,并且第一主晶体管的端子耦合为接收钳位电压;以及第一主开关,耦合在第一主晶体管的第二端子与位线之间,其中,将第一主开关导通以将位线电耦合到第一主晶体管,并且将第一主开关截止以将位线与第一主晶体管电隔离,并且第一微调分支电路中的每个包括:第一微调晶体管,具有第一端子、第二端子和控制端子,其中,第一微调晶体管的第一端子耦合到第一连接节点,并且第一微调晶体管的控制端子耦合为接收钳位电压;以及第一微调开关,耦合在第一微调晶体管的第二端子与第一主开关与位线之间的第二连接节点之间,其中,将第一微调开关导通以将位线电耦合到第一微调晶体管,并且将第一微调开关截止,以将位线与第一微调晶体管电隔离。

121.在上述读出放大器中,第二钳位电路包括第二主分支电路和多个第二微调分支电路,其中,第二主分支电路包括:第二主晶体管,具有第一端子、第二端子和控制端子,其中,第二主晶体管的第一端子耦合在第二i/o节点与第二钳位电路之间的第一连接节点,并且第二主晶体管的控制端子耦合为接收钳位电压;以及第二主开关,耦合在第二主晶体管的第二端子与参考位线之间,其中,将第二主开关导通以将参考位线电耦合到第二主晶体管,并且将第二主开关截止以将参考位线与第二主晶体管电隔离,并且,第二微调分支电路中的每个包括:第二微调晶体管,具有第一端子、第二端子和控制端子,其中,第二微调晶体管的第一端子耦合到第一连接节点,并且第二微调晶体管的控制端子耦合为接收钳位电压;以及第二微调开关,耦合在第二微调晶体管的第二端子与第二主开关与参考位线之间的第二连接节点之间,其中,将第二微调开关导通以将参考位线电耦合到第二微调晶体管,并且将第二微调开关截止以将参考位线与第二微调晶体管电隔离。

122.在上述读出放大器中,通过闭合或断开第一微调开关中的一个或多个来微调对应于位线的电压,并且对应于位线的微调的电压与第一钳位电路的当前闭合的第一微调开关

的总数成比例,并且,通过闭合或断开第二微调开关中的一个或多个来微调对应于参考位线的电压,并且对应于参考位线的微调的电压与第二钳位电路的当前闭合的第二微调开关的总数成比例。

123.在上述读出放大器中,电压比较器包括:第一电路;以及第二电路,其中,第一电路和第二电路耦合到第一i/o节点和第二i/o节点,其中,第一电路包括:第一晶体管、第二晶体管和第三晶体管,其中,第一晶体管的第一端子和第二晶体管的第一端子耦合到第一参考电压电平,第一晶体管的控制端子、第二晶体管的控制端子和第三晶体管的控制端子耦合为接收预充电信号,第一晶体管的第二端子和第三晶体管的第二端子耦合到第一i/o节点、第一晶体管和第三晶体管之间的连接节点,并且第二晶体管的第二端子和第三晶体管的第一端子耦合到第二i/o节点、第二晶体管和第三晶体管之间的另外的连接节点。

124.在上述读出放大器中,电压比较器的第二电路包括:第四晶体管、第五晶体管、第一p型晶体管对、第一n型晶体管对、第二p型晶体管对和第二n型晶体管对,其中,第一p型晶体管对和第一n型晶体管对形成第三电路,第二p型晶体管对和第二n型晶体管对形成第四电路,第三电路交叉耦合到第四电路,并且,第三电路和第四电路的输出耦合到第一i/o节点和第二i/o节点,其中,第四晶体管耦合到第三电路和第四电路,其中,第四晶体管的第一端子耦合到第一参考电压电平,第四晶体管的第二端子耦合到第四晶体管、第三电路和第四电路之间的连接节点,第四晶体管的控制端子耦合为接收第一使能信号,其中,第五晶体管耦合到第三电路和第四电路,其中,第五晶体管的第一端子耦合到第五晶体管、第三电路和第四电路之间的连接节点,第五晶体管的第二端子耦合到第二参考电压电平,并且第五晶体管的控制端子耦合为接收第二使能信号。

125.在上述读出放大器中,对应于读出信号的第一输出电压与第二输出电压之差大于第一输入电压与第二输入电压之差,其中,将第一输入电压经由第一i/o节点输入到电压比较器,将第二输入电压经由第二i/o节点输入到电压比较器,将第一输出电压经由第一i/o节点从电压比较器输出,并且将第二输出电压经由第二i/o节点从电压比较器输出,并且读出放大器还包括:第一电阻器,耦合在第一钳位电路与位线之间;以及第二电阻器,耦合在第二钳位电路与参考位线之间。

126.在本公开的一些实施例中,提供了一种读出放大器。另外的读出放大器包括电压比较器和钳位电路。电压比较器耦合到位线和参考位线,并被配置为比较第一输入电压和第二输入电压以输出读出信号。钳位电路耦合在电压比较器、位线和参考位线之间。电压比较器和钳位电路中的一个具有偏移补偿。电压比较器还被配置为微调对应于位线的第一电压和对应于参考位线的第二电压,以将对应于参考位线的电压与对应于位线的电压进行匹配。

127.在上述读出放大器中,电压比较器包括:第一电路;第二电路;以及第三电路,其中,第二电路经由第一i/o节点和第二i/o节点交叉耦合到第三电路,其中,第一电路包括:第一晶体管、第二晶体管和第三晶体管,其中,第一晶体管的第一端子和第二晶体管的第一端子耦合到第一参考电压电平,第一晶体管的控制端子、第二晶体管的控制端子和第三晶体管的控制端子耦合为接收预充电信号,第一晶体管的第二端子和第三晶体管的第二端子耦合到第一节点、第一晶体管和第三晶体管之间的连接节点,并且第二晶体管的第二端子和第三晶体管的第一端子耦合到第二节点、第二晶体管和第三晶体管之间的另外的连接节

点。

128.在上述读出放大器中,第二电路包括:第四晶体管;第一主分支电路;以及多个第一微调分支电路,其中,第四晶体管的第一端子耦合到第一参考电压电平,第四晶体管的控制端子耦合到第一节点,并且第四晶体管的第二端子经由第一i/o节点耦合到第一主分支电路,其中,第一微调分支电路经由第三节点耦合到第一主分支电路。

129.在上述读出放大器中,第一主分支电路包括:第一主晶体管,其中,第一主晶体管的第一端子耦合到第一i/o节点,第一主晶体管的控制端子耦合到第一节点与第二i/o节点之间的第一连接节点,并且第一主晶体管的第二端子耦合到第三节点,并且第一微调分支电路中的每个包括:第一微调开关;以及第一微调晶体管,其中,第一微调晶体管的第一端子耦合到第一微调开关,第一微调晶体管的控制端子耦合到第一连接节点,并且第一微调晶体管的第二端子耦合到第三节点,其中,第一微调开关耦合在第一微调晶体管的第一端子与第一参考电压电平之间,其中,将第一微调开关导通以将第一参考电压电平电耦合到第一微调晶体管,并且将第一微调开关截止以将第一参考电压电平与第一微调晶体管电隔离,其中,通过闭合或断开第一微调开关中的一个或多个来微调对应于第三节点的电压,并且对应于第三节点的微调的电压与第三电路的当前闭合的第一微调开关的总数成比例。

130.在上述读出放大器中,第三电路包括:第五晶体管;第二主分支电路;以及多个第二微调分支电路,其中,第五晶体管的第一端子耦合到第一参考电压电平,第五晶体管的控制端子耦合到第二节点,并且第五晶体管的第二端子经由第二i/o节点耦合到第二主分支电路,其中,第二微调分支电路经由第四节点耦合到第二主分支电路。

131.在上述读出放大器中,第二主分支电路包括:第二主晶体管,其中,第二主晶体管的第一端子耦合到第二i/o节点,第二主晶体管的控制端子耦合到第二节点与第一i/o节点之间的第二连接节点,并且第二主晶体管的第二端子耦合到第四节点,并且第二微调分支电路中的每个包括:第二微调开关;以及第二微调晶体管,其中,第二微调晶体管的第一端子耦合到第二微调开关,第二微调晶体管的控制端子耦合到第二连接节点,并且第二微调晶体管的第二端子耦合到第四节点,其中,第二微调开关耦合在第二微调晶体管的第一端子与第一参考电压电平之间,其中,将第二微调开关导通以将第一参考电压电平电耦合到第二微调晶体管,并且将第二微调开关截止以将第一参考电压电平与第二微调晶体管电隔离,其中,通过闭合或断开第二微调开关中的一个或多个来微调对应于第四节点的电压,并且对应于第四节点的微调的电压与第三电路的当前闭合的第二微调开关的总数成比例。

132.在上述读出放大器中,钳位电路包括:第一钳位电路,耦合在电压比较器与位线之间;第二钳位电路,耦合在电压比较器与参考位线之间;以及运算放大器,具有输出端子、第一输入端子和第二输入端子,其中,输出端子耦合到第一钳位电路与第二钳位电路之间的连接节点,第一输入端子耦合为接收偏置电压,并且第二输入端子耦合到第一钳位电路与第二钳位电路之间的另外的连接节点。

133.在上述读出放大器中,第一钳位电路包括第一晶体管、第一开关、第二开关和第一电容器,其中,第一晶体管的第一端子耦合到第二电路的第三节点,第一晶体管的控制端子耦合到第一开关与第一电容器的第一端子之间的第一连接节点,第一电容器的第二端子耦合到第二参考电压电平,第一开关耦合在第一连接节点与第一钳位电路与第二钳位电路之间的连接节点之间,其中,将第一开关导通以将连接节点电耦合到第一晶体管和第一电容

器,并且将第一开关截止以将连接节点与第一晶体管和第一电容器电隔离,第二开关耦合在第一晶体管的第二端子与第一钳位电路与第二钳位电路之间的另外的连接节点之间,其中,将第二开关导通以将另外的连接节点电耦合到第一晶体管,并且将第二开关截止以将另外的连接节点与第一晶体管电隔离,并且第一电容器被配置为存储与第一晶体管的控制端子的电压相对应的电荷。

134.在上述读出放大器中,第二钳位电路包括第二晶体管、第三开关、第四开关和第二电容器,其中,第二晶体管的第一端子耦合到第三电路的第四节点,第二晶体管的控制端子耦合到第三开关与第二电容器的第一端子之间的第二连接节点,第二电容器的第二端子耦合到第二参考电压电平,第三开关耦合在第二连接节点与第一钳位电路与第二钳位电路之间的连接节点之间,其中,将第三开关导通以将连接节点电耦合到第二晶体管和第二电容器,并且将第三开关截止以将连接节点与第二晶体管和第二电容器电隔离,第四开关耦合在第二晶体管的第二端子与第一钳位电路与第二钳位电路之间的另外的连接节点之间,其中,将第四开关导通以将另外的连接节点电耦合到第二晶体管,并且将第四开关截止以将另外的连接节点与第二晶体管电隔离,并且第二电容器被配置为存储与第二晶体管的控制端子的电压相对应的电荷。

135.在上述读出放大器中,还包括:第一电阻器,耦合在位线与第二开关与第一晶体管的第二端子之间的第三连接节点之间;以及第二电阻器,耦合在参考位线与第四开关与第二晶体管的第二端子之间的第四连接节点之间,其中,在闭合第一开关和第二开关两者并且断开第三开关和第四开关两者之后,获得对应于位线的对第一电阻器的电压,并且其中,在闭合第三开关和第四开关两者并且断开第一开关和第二开关两者之后,获得对应于位线的第二电阻器的电压。

136.在上述读出放大器中,响应于在闭合第一开关和第二开关两者和断开第三开关和第四开关之后运算放大器进入稳态,获得的第一电阻器的电压等于偏置电压,并且将与第一晶体管的控制端子的电压对应的电荷存储在第一电容器中,响应于在断开第一开关和第二开关两者和闭合第三开关和第四开关之后运算放大器进入另外的稳态,获得的第二电阻器的电压等于偏置电压,并且将与第二晶体管的控制端子的电压相对应的电荷存储在第二电容器中,并且在一起断开第一开关、第二开关、第三开关和第四开关后,第一电容器将存储的电荷放电到第一晶体管的控制端子,以向第一晶体管的控制端子提供第一钳位电压,并且第二电容器将存储的电荷放电到第二晶体管的控制端子,以向第二晶体管的控制端子提供第二钳位电压,使得第一电阻器的电压和第二电阻器的电压与偏置电压相同。在本公开的一些实施例中,提供了一种用于非易失性存储器的操作方法。所述非易失性存储器包括存储器阵列和读出放大器,其中,所述读出放大器包括具有偏移补偿的电压比较器、第一钳位电路和第二钳位电路,所述第一钳位电路耦合在所述读出放大器的第一i/o节点与位线之间,并且所述第二钳位电路耦合在所述读出放大器的第二i/o节点与参考位线之间。所述操作方法包括以下步骤:电压比较器分别经由所述读出放大器的所述第一i/o节点和所述第二i/o节点比较第一输入电压和第二输入电压,以输出读出信号;所述第一钳位电路和所述第二钳位电路分别微调对应于所述位线的电压和对应于所述参考位线的电压,以使对应于所述参考的所述电压与对应于所述位线的所述电压进行匹配。

137.在本公开的一些实施例中,提供了一种用于非易失性存储器的操作方法。所述非

易失性存储器包括存储器阵列和读出放大器。所述读出放大器包括电压比较器和钳位电路,所述钳位电路与所述读出放大器的第一i/o节点、位线、所述读出放大器的第二i/o节点和参考位线耦合,并且所述电压比较器和所述钳位电路中的一个具有偏移补偿。所述操作方法包括以下步骤:所述电压比较器分别经由所述读出放大器的所述第一i/o节点和所述第二i/o节点比较第一输入电压和第二输入电压,以输出读出信号;并且所述电压比较器分别微调对应于所述位线的电压和对应于所述参考位线的电压,以使对应于所述参考的所述电压与对应于所述位线的所述电压进行匹配。

138.前面概述了几个实施例的特征,使得本领域技术人员可以更好地理解本公开的方面。本领域普通技术人员应该理解,他们可以很容易地使用本公开作为设计或更改用于执行与本文所介绍的实施例相同的目的和/或实现相同的优点的其它处理和结构。本领域技术人员也应该意识到,这种等同构造不背离本公开的精神和范围,并且在不背离本公开的精神和范围的情况下,可以做出各种变化、替换和改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1