一种测试元件组及其测试方法与流程

1.本技术涉及半导体技术领域,具体涉及一种测试元件组及其测试方法。

背景技术:

2.对于半导体存储器器件,核心设置为由存储单元组成的二维阵列,并且每行的存储单元可以由字线wl进行选择,每列的存储单元可以由位线bl和参考位线blb进行选择,当某一存储单元执行读操作或写操作时,由相应的位线感测放大器(blsa,bit line sense amp)感应并放大位线和参考位线上的电压差,以将信息写入存储单元或从存储单元读出,因此位线感测放大器是影响读写速度的主要电路。

3.目前,对于存储器器件读写速度的测试是在产品生产出来(fab out)后进行芯片封装时进行的。这样,只能测试器件的整体读写速度,无法获得器件的局部差异数据,例如器件中影响读写速度的位线感测放大器的局部差异数据。

技术实现要素:

4.本技术的目的是针对上述现有技术的不足提出的一种测试元件组及其测试方法,该目的是通过以下技术方案实现的。

5.本技术的第一方面提出了一种测试元件组,所述测试元件组包括:位线感测放大器阵列,所述位线感测放大器阵列中每一位线测放大器均包括第一测试端、第二测试端和选择端;

6.每一所述位线感测放大器的第一测试端均与第一电压输入线电连接,且每一所述位线感测放大器的第二测试端均与第二电压输入线电连接;

7.其中,所述位线感测放大器阵列与半导体存储器器件中的位线感测放大器电路结构一致,且每一所述位线感测放大器的第一测试端和第二测试端在半导体存储器器件中分别用于与位线和参考位线连接,以及选择端用于与位线选择端连接。

8.本技术的第二方面提出了一种上述第一方面所述测试元件组的测试方法,所述方法包括:

9.向所述第一电压输入线和所述第二电压输入线分别施加预设电源电压信号,针对每一位线感测放大器,向该位线感测放大器的选择端施加所述预设电源电压信号,并测量该位线感测放大器的第一测试端输出的第一电流和第二测试端输出的第二电流;

10.向所述第一电压输入线和所述第二电压输入线分别施加预设接地电压信号,针对每一位线感测放大器,向该位线感测放大器的选择端施加所述预设电源电压信号,并测量该位线感测放大器的第一测试端输出的第三电流和第二测试端输出的第四电流。

11.基于上述第一方面和第二方面所述的测试元件组及其测试方法,本技术具有如下有益效果:

12.本技术在teg(test element group,测试元件组)阶段,通过将设计于半导体存储器器件中的位线感测放大器的电路结构复制到测试元件组模块中,并将每一位线感测放大

器中用于连接位线和参考位线的端子分别作为测试端的同时,将用于连接位线的端子合并起来连接到一电压输入线,将用于连接参考位线的端子合并起来连接到另一电压输入线,从而通过向两条电压输入线同时输入电源电压或接地电压,以选择性测量各个位线感测放大器在两种输入情况下的电流。由于位线感测放大器是影响半导体存储器器件读写速度的主要电路,因此使用本方案测量得到的电流分布可以反映半导体存储器器件的局部差异数据,由这些局部差异数据可以对半导体存储器器件的读写速度进行评估。由于本技术方案在teg阶段便能很早的检测出器件的读写速度问题,因此可以节省测试费用与时间,改善产品良率。

附图说明

13.此处所说明的附图用来提供对本技术的进一步理解,构成本技术的一部分,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。在附图中:

14.图1为本技术根据一示例性实施例示出的一种测试元件组的结构示意图;

15.图2为本技术根据一示例性实施例示出的一种测试元件组的测试方法的实施例流程图;

16.图3为本技术根据图1所示实施例示出的一种测试元件组的测试原理示意图;

17.图4为本技术根据图1所示实施例示出的另一种测试元件组的测试原理示意图。

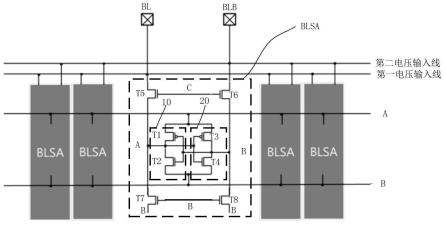

具体实施方式

18.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

19.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

20.在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。

21.目前,由于存储器器件读写速度的测试是在产品生产出来(fab out)后进行芯片封装时进行的,但是这样只能测试器件的整体读写速度,无法获得器件的局部差异数据,例如器件中影响读写速度的位线感测放大器的局部差异数据。而且如果在进行芯片封装时想获取位线感测放大器的局部差异数据,需要设计很复杂的测试模块获取,这也会导致测试开销增加。

22.为解决上述技术问题,本技术提出一种测试元件组,以在测试初期的teg阶段中获得存储器器件的局部差异数据,如图1所示,该测试元件组包括位线感测放大器阵列,所述位线感测放大器阵列中每一位线测放大器blsa均包括第一测试端bl、第二测试端blb和选

择端c(图1中给出其中一个blsa的具体电路结构),为了便于统一输入信号进行测量,通过将每一位线感测放大器的第一测试端bl均与第一电压输入线电连接,且每一位线感测放大器的第二测试端blb均与第二电压输入线电连接。

23.需要说明的是,所述位线感测放大器阵列与半导体存储器器件中的位线感测放大器电路结构一致,且每一位线感测放大器的第一测试端和第二测试端在半导体存储器器件中分别用于与位线和参考位线连接,以及每一位线感测放大器的选择端在半导体存储器器件中用于与位线选择端连接。

24.基于上述描述可知,在teg阶段,通过将设计于半导体存储器器件中的位线感测放大器的电路结构复制到测试元件组模块中,并将每一位线感测放大器中用于连接位线和参考位线的端子分别作为测试端的同时,将用于连接位线的端子合并起来连接到一电压输入线,将用于连接参考位线的端子合并起来连接到另一电压输入线,从而通过向两条电压输入线同时输入电源电压或接地电压,以选择性测量各个位线感测放大器在两种输入情况下的电流,从而在teg阶段便可获得存储器器件的局部差异数据,以在早期开发阶段检测出器件的读写速度问题,节省后期的测试费用与时间,改善产品良率。

25.在一些实施例中,如图1所示,每一位线感测放大器均还包括第一节点a、第二节点b、第一反相器10和第二反相器20。

26.进一步地,第一反相器10包括第一晶体管t1和第二晶体管t2,第一晶体管t1与第二晶体管t2的漏极相连接且均连接到第一节点a,以及第一晶体管t1与第二晶体管t2的栅极相连接且均连接到第二节点b。

27.第二反相器20包括第三晶体管t3和第四晶体管t4,第三晶体管t3与第四晶体管t4的漏极相连接且均连接到第二节点b,以及第三晶体管t3与第四晶体管t4的栅极相连接且均连接到第一节点a;第一晶体管t1和第三晶体管t3的源极均连接到第一节点a,第二晶体管t2和第四晶体管t4的源极均连接到第二节点b。

28.需要说明的是,在本实施例中,第一节点a是用于连接测试元件组的电源电压vdd端,第二节点b是用于连接测试元件组的接地vss端。

29.也就是说,本技术对半导体储存器中的每一位线感测放大器的第一节点a和第二节点b做了进一步处理,即为第一节点a始终提供的是电源电压vdd,为第二节点b始终提供的是接地电压vss。

30.优选的,上述所述的第一晶体管t1和第三晶体管t3均为p型晶体管,第二晶体管t2和第四晶体管t4均为n型晶体管。

31.在一些实施例中,继续参见图1所示,每一位线感测放大器均还包括第五晶体管t5和第六晶体管t6。

32.其中,第五晶体管t5和第六晶体管t6的栅极相连接且均连接到选择端c;第五晶体管t5的通道第一端连接第一测试端bl,以及第五晶体管t5的通道第二端连接第一节点a,也就是说,相互连接的第一晶体管t1和第二晶体管t2的漏极,相互连接的第三晶体管t3和第四晶体管t4的栅极,以及第五晶体管t5的通道第二端,这三者均形成于第一节点a。

33.第六晶体管t6的通道第一端连接第二测试端blb,以及第六晶体管t6的通道第二端连接第二节点b,也就是说,相互连接的第一晶体管t1和第二晶体管t2的栅极,相互连接的第三晶体管t3和第四晶体管t4的漏极,以及第六晶体管t6的通道第二端,这三者均形成

于第二节点b。

34.需要说明的是,本实施例中,第五晶体管t5和第六晶体管t6的通道第一端和通道第二端是晶体管的源极或漏极,即如果通道第一端为源极,那么通道第二端为漏极。

35.在一优选实施例中,第五晶体管t5和第六晶体管t6可以均为n型晶体管。

36.在一些实施例中,继续参见图1所示,每一位线感测放大器均还包括第七晶体管t7和第八晶体管t8。

37.其中,第七晶体管t7的通道第一端连接第一节点a,第七晶体管t7的通道第二端和栅极均连接第二节点b,第八晶体管t8的通道第一端、通道第二端和栅极均连接第二节点b。

38.与前述测试元件组实施例相对应,本技术还提供了测试元件组的测试方法的实施例。

39.图2为本技术根据一示例性实施例示出的一种测试元件组的测试方法的实施例流程图,本实施例基于上述图1所示的测试元件组结构进行测试,该测试元件组的测试方法包括如下步骤:

40.步骤201:向第一电压输入线和第二电压输入线分别施加预设电源电压信号,针对每一位线感测放大器,向该位线感测放大器的选择端施加预设电源电压信号,并测量该位线感测放大器的第一测试端输出的第一电流和第二测试端输出的第二电流。

41.在本实施例中,参见图1所示,当向第一电压输入线和第二电压输入线分别施加预设电源电压信号(vdd)时,相当于向第五晶体管t5和第六晶体管t6的通道第一端分别施加预设电源电压信号,在测量时,需要依次选通位线感测放大器进行测量,即通过向其中一个位线感测放大器的选择端c施加vdd,以选通该位线感测放大器。

42.参见图3所示,为被选通的位线感测放大器的测量原理示意图,在此种情况下,位线感测放大器中的第四晶体管t4和第六晶体管t6均导通,有饱和电流流过(图3中实线箭头所指),其余的第一晶体管t1、第二晶体管t2、第三晶体管t3、第五晶体管t5均处于关闭状态,有很小的泄漏电流流过(图3中虚线箭头所指),通过测量第一测试端的第一电流,可以得到第四晶体管t4的饱和电流,测量第二测试端的第二电流,可以得到第二晶体管t2的泄漏电流。

43.步骤202:向第一电压输入线和第二电压输入线分别施加预设接地电压信号,针对每一位线感测放大器,向该位线感测放大器的选择端施加预设电源电压信号,并测量该位线感测放大器的第一测试端输出的第三电流和第二测试端输出的第四电流。

44.在本实施例中,参见图1所示,当向第一电压输入线和第二电压输入线分别施加预设接地电压信号(vss)时,相当于向第五晶体管t5和第六晶体管t6的通道第一端分别施加预设接地电压信号,在测量时,同样需要依次选通位线感测放大器进行测量,即通过向其中一个位线感测放大器的选择端c施加vdd,以选通该位线感测放大器。

45.参见图4所示,为被选通的位线感测放大器的测量原理示意图,在此种情况下,位线感测放大器中的第一晶体管t1和第五晶体管t5均导通,有饱和电流流过(图4中实线箭头所指),其余的第二晶体管t2、第三晶体管t3、第四晶体管t4、第六晶体管t6均处于关闭状态,有很小的泄漏电流流过(图4中虚线箭头所指),通过测量第一测试端的第三电流,可以得到第一晶体管t1的饱和电流,测量第二测试端的第四电流,可以得到第三晶体管t3的泄漏电流。

46.可以理解的是,本发明对上述步骤201和步骤202的执行顺序不进行具体限定。

47.需要说明的是,在测量完成后,针对位线感测放大器阵列中的每一位线感测放大器均可以得到4个电流值:第一电流、第二电流、第三电流以及第四电流。

48.进一步地,可以通过对各个位线感测放大器的第一电流、第二电流、第三电流以及第四电流分别进行统计,以获得第一电流的误差值、第二电流的误差值、第三电流的误差值以及第四电流的误差值,从而将第一电流的误差值、第二电流的误差值、第三电流的误差值以及第四电流的误差值作为半导体存储器器件的局部差异数据,以用于对半导体存储器器件的读写速度进行评估。

49.其中,第一电流的误差值、第二电流的误差值、第三电流的误差值以及第四电流的误差值可以均是sigma值。

50.至此,完成上述图2所示的测试流程,通过向两条电压输入线同时输入电源电压或接地电压,以选择性测量各个位线感测放大器在两种输入情况下的电流。由于位线感测放大器是影响半导体存储器器件读写速度的主要电路,因此使用本方案测量得到的电流分布可以反映半导体存储器器件的局部差异数据,由这些局部差异数据可以对半导体存储器器件的读写速度进行评估。由于本技术方案在teg阶段便能很早的检测出器件的读写速度问题,因此可以节省测试费用与时间,改善产品良率。

51.在以上的描述中,对于各层的构图、刻蚀等技术细节并没有做出详细的说明。但是本领域技术人员应当理解,可以通过各种技术手段,来形成所需形状的层、区域等。另外,为了形成同一结构,本领域技术人员还可以设计出与以上描述的方法并不完全相同的方法。另外,尽管在以上分别描述了各实施例,但是这并不意味着各个实施例中的措施不能有利地结合使用。

52.以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。本公开的范围由所附权利要求及其等价物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1