组控制电路及包括该组控制电路的半导体存储器设备的制作方法

1.本公开的各种实施方式总体上涉及组控制电路及包括该组控制电路的半导体存储器设备,并且更具体地,涉及能够生成用于依次控制多个电路的控制信号的组控制电路及包括该组控制电路的半导体存储器设备。

背景技术:

2.通常,包括半导体设备和半导体存储器设备的集成电路在其内具有多个内部电路以执行各种功能。多个内部电路被设计为根据预设时间点被激活并且执行预设操作。在多个内部电路当中,存在具有基本相同的激活点的内部电路。此外,在多个内部电路当中,存在具有不同激活点的内部电路。

3.此外,集成电路接收电源电压并控制多个内部电路的各种操作。在这种情况下,当在相同的时间点激活多个内部电路时,由于瞬时提供给多个内部电路的电流量的突然增加,导致电源电压突然下降。近来,由于施加到集成电路的电源电压的电压电平变得越来越低,因此电源电压的下降导致集成电路故障。

技术实现要素:

4.在本公开的实施方式中,一种组控制电路可以包括:选择信号生成电路,其被配置为通过使进入控制信号与第一边沿时钟信号和第二边沿时钟信号之一同步,来生成源极选择信号;第一激活选择电路,其被配置为通过使源极选择信号与第一边沿时钟信号同步,来生成被依次激活的多个第一激活选择信号;以及第二激活选择电路,其被配置为通过使源极选择信号与第二边沿时钟信号同步,来生成被依次激活的多个第二激活选择信号,其中,第一激活选择电路和第二激活选择电路具有并行结构,并且第一边沿时钟信号和第二边沿时钟信号具有不同的相位。

5.在本公开的实施方式中,一种组控制电路可以包括:选择时钟生成电路,其被配置为基于模式控制信号,分别按原顺序或以相反顺序从第一边沿时钟信号和第二边沿时钟信号生成第一选择时钟信号和第二选择时钟信号;选择信号生成电路,其被配置为通过使进入控制信号与第一边沿时钟信号和第二边沿时钟信号之一同步,来生成源极选择信号;第一激活选择电路,其被配置为通过使源极选择信号交替地与第一边沿时钟信号和第一选择时钟信号同步,来生成被依次激活的多个第一激活选择信号;以及第二激活选择电路,其被配置为通过使源极选择信号交替地与第二边沿时钟信号和第二选择时钟信号同步,来生成被依次激活的多个第二激活选择信号,其中,第一激活选择电路和第二激活选择电路具有并行结构,并且第一边沿时钟信号和第二边沿时钟信号具有不同的相位。

6.在本公开的实施方式中,一种半导体存储器设备可以包括组控制电路和多个页缓冲器电路,该组控制电路包括:选择信号生成电路,其被配置为通过使进入控制信号与第一边沿时钟信号和第二边沿时钟信号之一同步,来生成源极选择信号;第一激活选择电路,其被配置为通过使源极选择信号与第一边沿时钟信号同步,来生成被依次激活的多个第一激

活选择信号;以及第二激活选择电路,其被配置为通过使源极选择信号与第二边沿时钟信号同步,来生成被依次激活的多个第二激活选择信号,并且多个页缓冲器电路基于多个第一激活选择信号和多个第二激活选择信号而被激活并且被配置为控制存储器阵列电路的读取操作和写入操作,其中,第一激活选择电路和第二激活选择电路具有并行结构,并且第一边沿时钟信号和第二边沿时钟信号具有不同的相位。

7.在本公开的实施方式中,一种半导体存储器设备可以包括组控制电路和多个页缓冲器电路,该组控制电路包括:选择时钟生成电路,其被配置为基于模式控制信号,分别按原顺序或以相反顺序从第一边沿时钟信号和第二边沿时钟信号生成第一选择时钟信号和第二选择时钟信号;选择信号生成电路,其被配置为通过使进入控制信号与第一边沿时钟信号和第二边沿时钟信号之一同步,来生成源极选择信号;第一激活选择电路,其被配置为通过使源极选择信号交替地与第一边沿时钟信号和第一选择时钟信号同步,来生成被依次激活的多个第一激活选择信号;以及第二激活选择电路,其被配置为通过使源极选择信号交替地与第二边沿时钟信号和第二选择时钟信号同步,来生成被依次激活的多个第二激活选择信号,并且多个页缓冲器电路基于多个第一激活选择信号和多个第二激活选择信号而被激活并且被配置为控制存储器阵列电路的读取操作和写入操作,其中,第一激活选择电路和第二激活选择电路具有并行结构,并且第一边沿时钟信号和第二边沿时钟信号具有不同的相位。

8.在本公开的实施方式中,一种集成电路可以包括:源极脉冲电路,其被配置为在具有彼此相反的相位的第一源极时钟和第二源极时钟之一的边沿处从控制脉冲生成源极脉冲;一系列第一电路,其被配置为被激活以从源极脉冲依次生成第一脉冲;以及一系列第二电路,其被配置为被激活以从源极脉冲依次生成第二脉冲,其中,第一电路中的偶数第一电路在第一偶数时钟的每个周期被依次激活,而第一电路中的奇数第一电路在第一奇数时钟的每个周期被激活,并且其中,第二电路中的偶数第二电路在第二偶数时钟的每个周期被依次激活,并且第二电路的奇数第二电路在第二奇数时钟的每个周期被激活。

附图说明

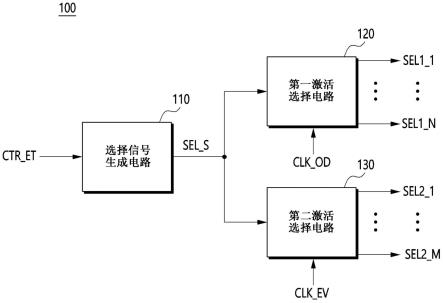

9.图1是例示了根据本公开的实施方式的组控制电路的构造的框图。

10.图2是例示了根据本公开的实施方式的组控制电路的构造的框图。

11.图3是例示了根据本公开的实施方式的图2中的组控制电路的电路操作的波形图。

12.图4是例示了根据本公开的实施方式的组控制电路的构造的框图。

13.图5是例示了根据本公开的实施方式的图4中的选择时钟生成电路的构造的图。

14.图6是例示了根据本公开的实施方式的图4中的选择信号生成电路以及第一激活选择电路和第二激活选择电路的构造的框图。

15.图7是例示了根据本公开的实施方式的图4中的组控制电路的4-分割操作模式的波形图。

16.图8是例示了根据本公开的实施方式的间隔控制电路的构造的框图。

17.图9是例示了根据本公开的实施方式的应用了图8中的间隔控制电路的图4中的组控制电路的电路操作的波形图。

18.图10是例示了根据本公开的实施方式的半导体存储器设备的构造的框图。

具体实施方式

19.本公开提供了针对各种实施方式的结构和功能细节。然而,本发明的范围不限于任何公开的实施方式或不受任何公开的实施方式的限制,也不限于本文提供的任何特定细节。即,本领域技术人员根据本公开将理解,可以以各种方式修改任何实施方式并且任何实施方式可以具有各种形式。因此,本发明涵盖落入权利要求书(包括其等同物)的范围内的所有此类变型。此外,特定实施方式并非必须包括所提及的全部目的或效果,也并非仅包括这样的目的或效果。因此,本发明的范围不限于此。

20.贯穿说明书,对于“(一个)实施方式”等的引用并非必须仅是一个实施方式,并且对任何这样短语的不同引用并非必须是相同实施方式。当在本文中使用术语“(多个)实施方式”时并非必须指代全部实施方式。

21.诸如“第一”和“第二”之类的术语用于将一个元件与具有相同或相似名称的另一元件区分开。一个实例中的第一元件可以在另一实例中被命名为第二元件,而不指示该元件本身的任何实质性变化。

22.单数旨在包括复数,除非另外明确地说明或者从上下文中清楚地表示意指仅一个。诸如“包括”或“具有”之类的开放式术语应理解为指示所提及的特征、数量、步骤、操作、元件、部件或其组合的存在,但不排除存在或可以添加一个或更多个其它的特征、数量、步骤、操作、元件、部件或其组合的可能性。

23.在每个步骤中,为了便于描述,使用符号(例如,a、b和c),不一定是指示步骤或操作的任何特定次序。根据本文的教导,步骤/操作可以以任何合适的次序执行,除非明确描述了特定次序或通过上下文指示了这种次序。在一些情况下,可以基本上同时执行两个或更多个步骤/操作。

24.除非另外定义,否则本文中使用的所有术语(包括技术术语或科学术语)具有与本领域技术人员通常理解的含义相同的含义。除非在申请中明确定义,否则常用词典中定义的术语应在相关技术的上下文中进行解释,而不应被解释为理想的或以过于形式的方式来解释。

25.本公开的各种实施方式旨在提供具有并行结构并且能够生成被依次激活的多个激活选择信号的组控制电路。

26.本公开的各种实施方式旨在提供一种半导体存储器设备,该半导体存储器设备能够依次激活多个页缓冲器电路或以页缓冲器电路的激活点的预设数量的分割来激活多个页缓冲器电路。

27.图1是例示了根据本公开的实施方式的组控制电路100的构造的框图。

28.参照图1,组控制电路100具有并行结构,并且可以被配置为基于进入控制信号ctr_et生成被依次激活的多个激活选择信号sel1_1至sel1_n和sel2_1至sel2_m(n和m各自是等于或大于1的自然数)。更详细地,组控制电路100可以包括选择信号生成电路110、第一激活选择电路120和第二激活选择电路130。

29.首先,选择信号生成电路110可以被配置为通过使进入控制信号ctr_et与时钟信号同步,来生成源极选择信号sel_s。进入控制信号ctr_et可以是在组控制电路100的激活控制操作的进入点处被激活的脉冲信号。

30.作为参考,选择信号生成电路110可以使用与进入控制信号ctr_et同步的时钟信

号。如将在图3中所示的,进入控制信号ctr_et可以与时钟信号同步,使得在进入控制信号ctr_et或脉冲信号被使能时时钟信号转变。例如,时钟信号可以是将在下面描述的第一边沿时钟信号clk_od或第二边沿时钟信号clk_ev。作为参考,在本说明书中,作为示例,进入控制信号ctr_et与第二边沿时钟信号clk_ev同步。

31.接下来,第一激活选择电路120可以被配置为通过使源极选择信号sel_s与第一边沿时钟信号clk_od同步,来生成被依次激活的多个第一激活选择信号sel1_1至sel1_n。

32.接下来,第二激活选择电路130可以被配置为通过使源极选择信号sel_s与第二边沿时钟信号clk_ev同步,来生成被依次激活的多个第二激活选择信号sel2_1至sel2_m。

33.第一激活选择电路120和第二激活选择电路130可以分别具有接收源极选择信号sel_s的并行结构。此外,第一边沿时钟信号clk_od和第二边沿时钟信号clk_ev可以具有不同的相位。例如,第一边沿时钟信号clk_od和第二边沿时钟信号clk_ev可以具有180

°

的相位差。即,第一边沿时钟信号clk_od的相位和第二边沿时钟信号clk_ev的相位可以为反相关系。

34.图2是例示了根据本公开的实施方式的组控制电路200的构造的框图。

35.参照图2,组控制电路200可以包括选择信号生成电路210、第一激活选择电路220和第二激活选择电路230。选择信号生成电路210、第一激活选择电路220和第二激活选择电路230可以分别对应于图1中的选择信号生成电路110、第一激活选择电路120和第二激活选择电路130。

36.首先,选择信号生成电路210可以包括第一同步电路211。

37.第一同步电路211可以被配置为通过基于第二边沿时钟信号clk_ev对进入控制信号ctr_et的同步操作,输出源极选择信号sel_s。第二边沿时钟信号clk_ev可以由反相电路inv反相并输入到第一同步电路211。第一同步电路211可以由例如能够基于反相电路inv的输出信号执行同步操作的d触发器组成。

38.接下来,第一激活选择电路220可以被配置为通过基于第一边沿时钟信号clk_od对源极选择信号sel_s的移位操作来生成多个第一激活选择信号。作为示例,多个第一激活选择信号的数量例如为三个。即,第一激活选择电路220可以通过基于第一边沿时钟信号clk_od对源极选择信号sel_s的移位操作,来生成第一激活选择信号sel1_1至第三激活选择信号sel1_3。

39.更详细地,第一激活选择电路220可以包括第二同步电路221至第四同步电路223。第二同步电路221可以通过使源极选择信号sel_s与第一边沿时钟信号clk_od同步,来输出第一激活选择信号sel1_1。第三同步电路222可以通过使第一激活选择信号sel1_1与第一边沿时钟信号clk_od同步,来输出第二激活选择信号sel1_2。第四同步电路223可以通过使第二激活选择信号sel1_2与第一边沿时钟信号clk_od同步,来输出第三激活选择信号sel1_3。第二同步电路221至第四同步电路223可以各自包括例如能够基于第一边沿时钟信号clk_od执行同步操作的d触发器。

40.接下来,第二激活选择电路230可以被配置为通过基于第二边沿时钟信号clk_ev对源极选择信号sel_s的移位操作,生成多个第二激活选择信号。作为示例,多个第二激活选择信号的数量例如为四个。即,第二激活选择电路230可以通过基于第二边沿时钟信号clk_ev对源极选择信号sel_s的移位操作,生成第四激活选择信号sel2_1至第七激活选择

信号sel2_4。

41.更详细地,第二激活选择电路230可以包括第五同步电路231至第八同步电路234。第五同步电路231可以通过使源极选择信号sel_s与第二边沿时钟信号clk_ev同步,来输出第四激活选择信号sel2_1。第六同步电路232可以通过使第四激活选择信号sel2_1与第二边沿时钟信号clk_ev同步,来输出第五激活选择信号sel2_2。第七同步电路233可以通过使第五激活选择信号sel2_2与第二边沿时钟信号clk_ev同步,来输出第六激活选择信号sel2_3。第八同步电路234可以通过使第六激活选择信号sel2_3与第二边沿时钟信号clk_ev同步,来输出第七激活选择信号sel2_4。第五同步电路231至第八同步电路234可以各自包括例如能够基于第二边沿时钟信号clk_ev执行同步操作的d触发器。

42.图3是例示了图2中的组控制电路200的电路操作的波形图。图3例示了第一边沿时钟信号clk_od、第二边沿时钟信号clk_ev、进入控制信号ctr_et、第一激活选择信号sel1_1至第三激活选择信号sel1_3以及第四激活选择信号sel2_1至第七激活选择信号sel2_4。

43.在下文中,为了便于描述,将参照图2和图3描述组控制电路200的电路操作。

44.首先,第一边沿时钟信号clk_od和第二边沿时钟信号clk_ev可以是具有彼此相反的相位的时钟信号。图2中的选择信号生成电路210的第一同步电路211可以通过使进入控制信号ctr_et与第二边沿时钟信号clk_ev同步,来生成源极选择信号sel_s。此时,第二边沿时钟信号clk_ev可以由反相电路inv进行反相并输入到第一同步电路211。因此,可以与第二边沿时钟信号clk_ev的下降沿同步地输出进入控制信号ctr_et,作为源极选择信号sel_s。

45.接下来,图2中的第二同步电路221可以通过使源极选择信号sel_s与第一边沿时钟信号clk_od同步,来生成第一激活选择信号sel1_1。此时,第二同步电路221可以基于第一边沿时钟信号clk_od的上升沿来执行同步操作。因此,可以与第一边沿时钟信号clk_od的上升沿同步地输出源极选择信号sel_s,作为第一激活选择信号sel1_1。随后,第三同步电路222可以通过使第一激活选择信号sel1_1与第一边沿时钟信号clk_od的上升沿同步,来输出第二激活选择信号sel1_2。然后,第四同步电路223可以通过使第二激活选择信号sel1_2与第一边沿时钟信号clk_od的上升沿同步,来输出第三激活选择信号sel1_3。

46.即,包括第二同步电路221至第四同步电路223的第一激活选择电路220可以与第一边沿时钟信号clk_od同步地移位源极选择信号sel_s。即,第一激活选择电路220可以通过基于第一边沿时钟信号clk_od对源极选择信号sel_s的移位操作,生成被依次激活的第一激活选择信号sel1_1至第三激活选择信号sel1_3。

47.接下来,图2中的第五同步电路231可以通过使源极选择信号sel_s与第二边沿时钟信号clk_ev同步,来生成第四激活选择信号sel2_1。此时,第五同步电路231可以基于第二边沿时钟信号clk_ev的上升沿来执行同步操作。因此,可以与第二边沿时钟信号clk_ev的上升沿同步地输出源极选择信号sel_s,作为第四激活选择信号sel2_1。随后,第六同步电路232可以通过使第四激活选择信号sel2_1与第二边沿时钟信号clk_ev的上升沿同步,来输出第五激活选择信号sel2_2。然后,第七同步电路233可以通过使第五激活选择信号sel2_2与第二边沿时钟信号clk_ev的上升沿同步,来输出第六激活选择信号sel2_3。然后,第八同步电路234可以通过使第六激活选择信号sel2_3与第二边沿时钟信号clk_ev的上升沿同步,来输出第七激活选择信号sel2_4。

48.包括第五同步电路231至第八同步电路234的第二激活选择电路230可以与第二边沿时钟信号clk_ev同步地移位源极选择信号sel_s。即,第二激活选择电路230可以通过基于第二边沿时钟信号clk_ev对源极选择信号sel_s的移位操作,生成被依次激活的第四激活选择信号sel2_1至第七激活选择信号sel2_4。

49.在下文中,为了便于描述并且作为示例,第一边沿时钟信号clk_od和第二边沿时钟信号clk_ev各自具有100ns的周期。在这种情况下,第一激活选择信号sel1_1至第三激活选择信号sel1_3中的每一个从逻辑“低”转变为逻辑“高”的激活间隔可以为100ns。此外,第四激活选择信号sel2_1至第七激活选择信号sel2_4中的每一个从逻辑“低”转变为逻辑“高”的激活间隔也可以是100ns。因此,如从图3可以看出的,作为多个第一激活选择信号的第一激活选择信号sel1_1至第三激活选择信号sel1_3中的每一个的激活间隔以及作为多个第二激活选择信号的第四激活选择信号sel2_1至第七激活选择信号sel2_4中的每一个的激活间隔可以各自为50ns。

50.因此,根据实施方式的组控制电路200具有并行结构,并且可以生成被依次激活的第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4。

51.图4是例示了根据本公开的实施方式的组控制电路400的构造的框图。

52.参照图4,组控制电路400可以包括选择时钟生成电路410、选择信号生成电路420、第一激活选择电路430和第二激活选择电路440。

53.在描述组控制电路400的构造之前,组控制电路400可以如图1中所示生成多个第一激活选择信号sel1_1至sel1_n和多个第二激活选择信号sel2_1至sel2_m。然而,在图4中,作为示例,多个第一激活选择信号的数量为三个,并且多个第二激活选择信号的数量为4个,如图2所示。即,图4中的组控制电路400可以生成第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4。

54.首先,选择时钟生成电路410可以被配置为基于模式控制信号ctr_md,分别按原顺序或以相反顺序从第一边沿时钟信号clk_od和第二边沿时钟信号clk_ev生成第一选择时钟信号clk_s1和第二选择时钟信号clk_s2。模式控制信号ctr_md可以是用于控制第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4的激活的分割的信号。

55.更详细地,在图3中,第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4的激活点可以彼此不同。即,第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4可以将用于多个内部电路的激活点分割为七个。如以下将要描述的,第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4可以将用于多个内部电路的激活点分割成少于七个的数量(例如,四个)并控制经分割的激活点。

56.在下文中,为了便于描述,将激活点分割为七个的模式定义为“7-分割操作模式”,并且将激活点分割为四个的模式定义为“4-分割操作模式”。根据实施方式的组控制电路400可以基于模式控制信号ctr_md以7-分割操作模式或4-分割操作模式,控制第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信

号sel2_4。即,模式控制信号ctr_md可以是用于控制第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4的分割操作模式的信号。

57.接下来,选择信号生成电路420可以被配置为通过使进入控制信号ctr_et与第二边沿时钟信号clk_ev同步,来生成源极选择信号sel_s。选择信号生成电路420可以对应于图2中的选择信号生成电路210。因此,图4中的选择信号生成电路420可以通过基于第二边沿时钟信号clk_ev对进入控制信号ctr_et的同步操作,生成源极选择信号sel_s。

58.接下来,第一激活选择电路430可以被配置为通过使源极选择信号sel_s交替地与第一边沿时钟信号clk_od和第一选择时钟信号clk_s1同步,来生成被依次激活的第一激活选择信号sel1_1至第三激活选择信号sel1_3。

59.接下来,第二激活选择电路440可以被配置为通过使源极选择信号sel_s交替地与第二边沿时钟信号clk_ev和第二选择时钟信号clk_s2同步,来生成被依次激活的第四激活选择信号sel2_1至第七激活选择信号sel2_4。

60.如以下将描述的,根据实施方式的组控制电路400可以基于模式控制信号ctr_md生成第一选择时钟信号clk_s1和第二选择时钟信号clk_s2。此外,组控制电路400可以基于第一选择时钟信号clk_s1和第二选择时钟信号clk_s2选择性地控制7-分割操作模式和4-分割操作模式。

61.图5是例示了根据本公开的实施方式的图4中的选择时钟生成电路410的构造的图。

62.参照图5,选择时钟生成电路410可以包括多路复用电路510和反相电路520。

63.首先,多路复用电路510可以被配置为基于模式控制信号ctr_md输出第一边沿时钟信号clk_od或第二边沿时钟信号clk_ev作为第一选择时钟信号clk_s1。多路复用电路510可以包括例如多路复用器mux。

64.接下来,反相电路520可以被配置为通过使第一选择时钟信号clk_s1反相,来输出第二选择时钟信号clk_s2。反相电路520可以包括反相电路inv,该反相电路inv接收第一选择时钟信号clk_s1并对第一选择时钟信号clk_s1进行反相,并且输出反相后的信号作为第二选择时钟信号clk_s2。

65.图6是例示了根据本公开的实施方式的图4中的选择信号生成电路420以及第一激活选择电路430和第二激活选择电路440的构造的框图。

66.参照图6,选择信号生成电路420可以包括第一同步电路421。

67.第一同步电路421可以被配置为通过基于第二边沿时钟信号clk_ev对进入控制信号ctr_et的同步操作,输出源极选择信号sel_s。第二边沿时钟信号clk_ev可以由反相电路inv反相并输入到第一同步电路421。

68.接下来,第一激活选择电路430可以被配置为通过基于第一边沿时钟信号clk_od和第一选择时钟信号clk_s1对源极选择信号sel_s的移位操作,生成多个第一激活选择信号。多个第一激活选择信号可以包括第一激活选择信号sel1_1至第三激活选择信号sel1_3。

69.更详细地,第一激活选择电路430可以包括作为多个激活电路的第二同步电路431至第四同步电路433。第二同步电路431可以通过使源极选择信号sel_s与第一选择时钟信

号clk_s1同步,输出第一激活选择信号sel1_1。第三同步电路432可以通过使第一激活选择信号sel1_1与第一边沿时钟信号clk_od同步,输出第二激活选择信号sel1_2。第四同步电路433可以通过使第二激活选择信号sel1_2与第一选择时钟信号clk_s1同步,输出第三激活选择信号sel1_3。

70.接下来,第二激活选择电路440可以被配置为通过基于第二边沿时钟信号clk_ev和第二选择时钟信号clk_s2对源极选择信号sel_s的移位操作,生成多个第二激活选择信号。多个第二激活选择信号可以包括第四激活选择信号sel2_1至第七激活选择信号sel2_4。

71.更详细地,第二激活选择电路440可以包括第五同步电路441至第八同步电路444。第五同步电路441可以通过使源极选择信号sel_s与第二边沿时钟信号clk_ev同步,输出第四激活选择信号sel2_1。第六同步电路442可以通过使第四激活选择信号sel2_1与第二选择时钟信号clk_s2同步,输出第五激活选择信号sel2_2。第七同步电路443可以通过使第五激活选择信号sel2_2与第二边沿时钟信号clk_ev同步,输出第六激活选择信号sel2_3。第八同步电路444可以通过使第六激活选择信号sel2_3与第二选择时钟信号clk_s2同步,输出第七激活选择信号sel2_4。

72.在下文中,将描述根据实施方式的图4中的组控制电路400的7-分割操作模式和4-分割操作模式。

73.首先,将描述7-分割操作模式。

74.参照图4,基于模式控制信号ctr_md,选择时钟生成电路410可以生成与第一边沿时钟信号clk_od相对应的第一选择时钟信号clk_s1和与第二边沿时钟信号clk_ev相对应的第二选择时钟信号clk_s2。如从图5可以看出的,在7-分割操作模式中,选择时钟生成电路410的多路复用电路510可以基于模式控制信号ctr_md,输出第一边沿时钟信号clk_od作为第一选择时钟信号clk_s1。因此,第一选择时钟信号clk_s1可以对应于第一边沿时钟信号clk_od,并且第二选择时钟信号clk_s2可以对应于第二边沿时钟信号clk_ev。

75.因此,类似于图2中的第二同步电路221至第四同步电路223,图6中的第二同步电路431至第四同步电路433可以基于第一边沿时钟信号clk_od执行移位操作。此外,类似于图2中的第五同步电路231至第八同步电路234,第五同步电路441至第八同步电路444可以基于第二边沿时钟信号clk_ev执行移位操作。

76.因此,如图3所示,可以依次激活作为从第二同步电路431至第四同步电路433输出的多个第一激活选择信号的第一激活选择信号sel1_1至第三激活选择信号sel1_3。此外,如图3所示,也可以依次激活作为从第五同步电路441至第八同步电路444输出的多个第二激活选择信号的第四激活选择信号sel2_1至第七激活选择信号sel2_4。

77.因此,根据实施方式的组控制电路400可以基于模式控制信号ctr_md,生成其七个转变点被依次激活的第一激活选择信号sel1_1至第三激活选择信号sel1_3以及第四激活选择信号sel2_1至第七激活选择信号sel2_4。此外,组控制电路400可以通过第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4来控制用于多个内部电路的7-分割操作模式。

78.接下来,将描述4-分割操作模式。

79.参照图4,基于模式控制信号ctr_md,选择时钟生成电路410可以生成与第二边沿

时钟信号clk_ev相对应的第一选择时钟信号clk_s1和与第一边沿时钟信号clk_od相对应的第二选择时钟信号clk_s2。如从图5可以看出的,在4-分割操作模式下,选择时钟生成电路410的多路复用电路510可以基于模式控制信号ctr_md输出第二边沿时钟信号clk_ev作为第一选择时钟信号clk_s1。因此,第一选择时钟信号clk_s1可以对应于第二边沿时钟信号clk_ev,并且第二选择时钟信号clk_s2可以对应于第一边沿时钟信号clk_od。

80.因此,图6中的第二同步电路431和第四同步电路433可以接收与第二边沿时钟信号clk_ev相对应的第一选择时钟信号clk_s1并执行激活操作,并且第三同步电路432可以接收第一边沿时钟信号clk_od并进行同步操作。此外,第五同步电路441和第七同步电路443可以接收第二边沿时钟信号clk_ev并执行同步操作,并且第六同步电路442和第八同步电路444可以接收与第一边沿时钟信号clk_od相对应的第二选择时钟信号clk_s2并执行同步操作。

81.图7是例示了根据本公开的实施方式的图4中的组控制电路400的4-分割操作模式的波形图。图7例示了第一边沿时钟信号clk_od、第二边沿时钟信号clk_ev、进入控制信号ctr_et以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4。

82.在下文中,为了便于描述,将参照图6和图7描述组控制电路400的4-分割操作模式。

83.首先,第一边沿时钟信号clk_od和第二边沿时钟信号clk_ev可以是具有彼此相反的相位的时钟信号。图6中的选择信号生成电路420的第一同步电路421可以通过使进入控制信号ctr_et与第二边沿时钟信号clk_ev同步,来生成源极选择信号sel_s。此时,第二边沿时钟信号clk_ev可以被反相电路inv反相并输入到第一同步电路421。因此,可以与第二边沿时钟信号clk_ev的下降沿同步地输出进入控制信号ctr_et,作为源极选择信号sel_s。

84.接下来,图6中的第二同步电路431可以通过使源极选择信号sel_s与对应于第二边沿时钟信号clk_ev的第一选择时钟信号clk_s1同步,来生成第一激活选择信号sel1_1。此时,第二同步电路431可以基于第一选择时钟信号clk_s1的上升沿执行同步操作。因此,可以与第一选择时钟信号clk_s1的上升沿同步地输出源极选择信号sel_s,作为第一激活选择信号sel1_1。随后,第三同步电路432可以通过使第一激活选择信号sel1_1与第一边沿时钟信号clk_od的上升沿同步,输出第二激活选择信号sel1_2。然后,第四同步电路433可以通过使第二激活选择信号sel1_2与第一选择时钟信号clk_s1的上升沿同步,输出第三激活选择信号sel1_3。

85.包括第二同步电路431至第四同步电路433的第一激活选择电路430可以通过使源极选择信号sel_s交替地与第一边沿时钟信号clk_od和第一选择时钟信号clk_s1同步,来使源极选择信号sel_s移位。即,第一激活选择电路430可以通过基于第一边沿时钟信号clk_od和第一选择时钟信号clk_s1对源极选择信号sel_s的移位操作,来生成被依次激活的第一激活选择信号sel1_1至第三激活选择信号sel1_3。

86.接下来,图6中的第五同步电路441可以通过使源极选择信号sel_s与第二边沿时钟信号clk_ev同步,来生成第四激活选择信号sel2_1。此时,第五同步电路441可以基于第二边沿时钟信号clk_ev的上升沿来执行同步操作。因此,可以与第二边沿时钟信号clk_ev的上升沿同步地输出源极选择信号sel_s,作为第四激活选择信号sel2_1。随后,第六同步

电路442可以通过使第四激活选择信号sel2_1与对应于第一边沿时钟信号clk_od的第二选择时钟信号clk_s2的上升沿同步,来输出第五激活选择信号sel2_2。然后,第七同步电路443可以通过使第五激活选择信号sel2_2与第二边沿时钟信号clk_ev的上升沿同步,输出第六激活选择信号sel2_3。然后,第八同步电路444可以通过使第六激活选择信号sel2_3与第二选择时钟信号clk_s2的上升沿同步,来输出第七激活选择信号sel2_4。

87.包括第五同步电路441至第八同步电路444的第二激活选择电路440可以通过使源极选择信号sel_s交替地与第二边沿时钟信号clk_ev和第二选择时钟信号clk_s2同步,使源极选择信号sel_s移位。即,第二激活选择电路440可以通过基于第二边沿时钟信号clk_ev和第二选择时钟信号clk_s2对源极选择信号sel_s的移位操作,来生成被依次激活的第四激活选择信号sel2_1至第七激活选择信号sel2_4。

88.在下文中,为了便于描述,第一边沿时钟信号clk_od和第二边沿时钟信号clk_ev各自具有100ns的周期。在这种情况下,第一激活选择信号sel1_1至第三激活选择信号sel1_3中的每一个从逻辑“低”转变为逻辑“高”的间隔可以是50ns。此外,第四激活选择信号sel2_1至第七激活选择信号sel2_4中的每一个从逻辑“低”转变为逻辑“高”的激活间隔也可以是50ns。此时,第一激活选择信号sel1_1和第四激活选择信号sel2_1可以具有基本上相同的转变点,第二激活选择信号sel1_2和第五激活选择信号sel2_2可以具有基本上相同的转变点,并且第三激活选择信号sel1_3和第六激活选择信号sel2_3可以具有基本上相同的转变点。即,第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4可以具有四个转变点。

89.因此,根据实施方式的组控制电路400可以基于模式控制信号ctr_md,生成其四个转变点被依次激活的第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4。此外,组控制电路400可以通过第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4来控制用于多个内部电路的4-分割操作模式。

90.如从图3和图7可以看出的,源极选择信号sel_s可以是在第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4之前首先被激活的信号。此外,源极选择信号sel_s可以是与第二边沿时钟信号clk_ev同步的信号。因此,类似于第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4,源极选择信号sel_s可以用于对多个内部电路的分割操作。

91.更详细地,如从图3可以看出的,源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4可以在八个转变点处被依次激活。因此,图4中的组控制电路400可以通过源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4来控制用于多个内部电路的8-分割操作模式。

92.随后,如从图7可以看出的,源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4可以在五个转变点处被依次激活。因此,图4中的组控制电路400可以通过源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七

激活选择信号sel2_4来控制用于多个内部电路的5-分割操作模式。

93.根据实施方式的图1中的组控制电路100可以调整源极选择信号sel_s以及多个第一激活选择信号sel1_1至sel1_n和多个第二激活选择信号sel2_1至sel2_m的各个激活间隔。此外,根据实施方式的图4中的组控制电路400可以调整源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4的各个激活间隔。根据实施方式的组控制电路可以进一步包括用于调整激活间隔的间隔控制电路。将参照图8描述间隔控制电路。

94.图8是例示了根据本公开的实施方式的间隔控制电路800的构造的框图。

95.参照图8,间隔控制电路800可以包括第一时钟控制电路810和第二时钟控制电路820。

96.首先,第一时钟控制电路810可以被配置为按原样输出第一边沿时钟信号clk_od,或者可以基于分频控制信号ctr_dv分频并输出第一边沿时钟信号clk_od。在此,分频可以意指将第一边沿时钟信号clk_od的周期调整为例如两倍或例如0.5倍。即,第一时钟控制电路810可以被配置为基于分频控制信号ctr_dv来调整第一边沿时钟信号clk_od的周期。更详细地,第一时钟控制电路810可以包括第一分频电路811和第一选择电路812。

97.第一分频电路811可以被配置为对第一边沿时钟信号clk_od进行分频并输出。即,第一分频电路811可以被配置为改变第一边沿时钟信号clk_od以具有与原始周期不同的周期。第一选择电路812可以被配置为基于分频控制信号ctr_dv来选择性地输出第一分频电路811的输出信号或第一边沿时钟信号clk_od。第一选择电路812的输出信号out_od可以被提供为图1中的组控制电路100的第一边沿时钟信号clk_od,并且可以被提供为图4中的组控制电路400的第一边沿时钟信号clk_od。

98.接下来,第二时钟控制电路820可以被配置为按原样输出第二边沿时钟信号clk_ev,或者基于分频控制信号ctr_dv对第二边沿时钟信号clk_ev进行分频并输出。即,第二时钟控制电路820可以被配置为基于分频控制信号ctr_dv来调整第二边沿时钟信号clk_ev的周期。更详细地,第二时钟控制电路820可以包括第二分频电路821和第二选择电路822。

99.第二分频电路821可以被配置为对第二边沿时钟信号clk_ev进行分频并输出。即,第二分频电路821可以被配置为改变第二边沿时钟信号clk_ev以具有与原始周期不同的周期。第二选择电路822可以被配置为基于分频控制信号ctr_dv来选择性地输出第二分频电路821的输出信号或第二边沿时钟信号clk_ev。第二选择电路822的输出信号out_ev可以被提供为图1中的组控制电路100的第二边沿时钟信号clk_ev,并且可以被提供为图4中的组控制电路400的第二边沿时钟信号clk_ev。

100.在图4中,模式控制信号ctr_md可以用作用于控制分割操作模式的控制信号。此外,在图8中,分频控制信号ctr_dv可以用作用于控制是否执行调整第一边沿时钟信号clk_od和第二边沿时钟信号clk_ev的周期的分频操作的控制信号。根据实施方式的组控制电路400可以通过将模式控制信号ctr_md和分频控制信号ctr_dv用作基本相同的控制信号,来同时控制图4的分割操作模式以及是否执行图8的分频操作。

101.图9是例示了根据本公开的实施方式的应用了图8中的间隔控制电路800的图4中的组控制电路400的电路操作的波形图。作为示例,模式控制信号ctr_md和分频控制信号ctr_dv是彼此对应的控制信号。

102.首先,参照图8和图9的(a),在8-分割操作模式下,图8中的间隔控制电路800可以基于分频控制信号ctr_dv输出第一边沿时钟信号clk_od和第二边沿时钟信号clk_ev。因此,图4中的组控制电路400可以执行电路操作,使得源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4具有八个转变点,如图9的(a)所示。因此,组控制电路400可以基于源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4来控制多个内部电路的8-分割操作模式。作为参考,图9的(a)可以对应于图3。

103.接下来,参照图8和图9的(b),在5-分割操作模式下,图8中的间隔控制电路800可以基于分频控制信号ctr_dv来对第一边沿时钟信号clk_od进行分频并输出以及对第二边沿时钟信号clk_ev进行分频并输出。即,第一时钟控制电路810可以生成通过调整第一边沿时钟信号clk_od的周期而获得的输出信号out_od,并且第二时钟控制电路820可以生成通过调整第二边沿时钟信号clk_ev的周期而获得的输出信号out_ev。

104.随后,图4中的组控制电路400可以基于第一时钟控制电路810的输出信号out_od和第二时钟控制电路820的输出信号out_ev,生成源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4。组控制电路400可以执行电路操作,使得源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4具有五个转变点,如图9的(b)所示。这里,与图9中的(a)相比,源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4的各个激活间隔可以被控制为两倍。因此,组控制电路400可以基于源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4,控制用于多个内部电路的5-分割操作模式。

105.在下文中,为了便于描述,第一边沿时钟信号clk_od和第二边沿时钟信号clk_ev各自具有100ns的周期。

106.在图9的(a)的情况下,源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4可以各自具有50ns的激活间隔。在图9的(b)的情况下,源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4可以各自具有100ns的激活间隔。通过这样的操作,根据实施方式的组控制电路400可以以各种方式将激活间隔与分割操作模式一起调整。

107.图10是例示了根据本公开的实施方式的半导体存储器设备1000的构造的框图。

108.参照图10,半导体存储器设备1000可以包括存储器阵列电路1010、多个页缓冲器电路1020和组控制电路1030。

109.首先,存储器阵列电路1010可以被配置为存储数据。存储器阵列电路1010可以包括多个存储器单元。半导体存储器设备1000可以在写入操作期间将数据存储在多个存储器单元中,并且可以在读操作期间输出多个存储器单元中所存储的数据。

110.接下来,多个页缓冲器电路1020可以电连接到存储器阵列电路1010中所包括的存储器单元。多个页缓冲器电路1020可以被配置为控制存储器阵列电路1010的读取操作和写

入操作。多个页缓冲器电路1020可以基于多个激活选择信号sel来激活。

111.接下来,组控制电路1030可以被配置为生成多个激活选择信号sel。组控制电路1030可以对应于参照图1至图9描述的构造和操作。多个激活选择信号sel可以包括图1中的多个激活选择信号sel1_1至sel1_n和sel2_1至sel2_m,并且可以包括参照图2至图9描述的源极选择信号sel_s以及第一激活选择信号sel1_1至第三激活选择信号sel1_3和第四激活选择信号sel2_1至第七激活选择信号sel2_4。由于已经参照图1至图9描述了多个激活选择信号sel,因此将省略其详细描述。

112.因此,根据实施方式的半导体存储器设备1000可以基于多个激活选择信号sel,以各种方式控制对与多个内部电路相对应的多个页缓冲器电路1020的激活操作。

113.根据实施方式,多个内部电路被依次激活,以防止电源电压下降,从而提高了电路操作的稳定性和可靠性。

114.本公开的效果不限于上述效果,并且本公开所属领域的技术人员从以上描述可以清楚地理解以上未描述的其它效果。

115.尽管已经出于示例性目的描述了各种实施方式,但是对于本领域技术人员将显而易见的是,在不脱离如所附权利要求所限定的本公开的精神和范围的情况下,可以进行各种改变和修改。

116.相关申请的交叉引用

117.本技术要求于2021年1月12日提交的韩国申请no.10-2021-0003948的优先权,通过引用将其全部内容合并于此。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1