存储系统以及半导体存储装置的制作方法

存储系统以及半导体存储装置

1.本技术享受以日本特许申请2020-124259号(申请日:2020年7月21日)为基础申请的优先权。本技术通过参照该基础申请来包含基础申请的全部内容。

技术领域

2.实施方式涉及存储系统以及半导体存储装置。

背景技术:

3.作为非易失性的半导体存储装置,例如已知以二维或者三维的方式排列有存储单元而成的nand型闪速存储器。由nand型闪速存储器和对nand型闪速存储器进行控制的控制器构成存储系统。

技术实现要素:

4.本发明的实施方式提供能够使擦除动作的性能提高的存储系统以及半导体存储装置。

5.实施方式的存储系统具备:半导体存储装置,其包括能够存储数据的第1存储单元;和控制器,其输出与在对于所述第1存储单元的第1擦除动作中使用的擦除电压有关的第1参数和命令进行所述第1擦除动作的第1命令,所述控制器在向所述半导体存储装置输出了所述参数之后,输出所述第1命令。

6.实施方式的半导体存储装置具备:存储单元,其能够存储数据;和控制电路,其对所述存储单元进行擦除动作,所述控制电路接收与在所述擦除动作中使用的擦除电压有关的参数,然后,接收命令进行所述擦除动作的第1命令,然后,使用所述参数来进行所述擦除动作。

附图说明

7.图1是表示第1实施方式的存储系统的结构的框图。

8.图2是表示半导体存储装置内的存储芯片的结构的框图。

9.图3是存储单元阵列内的块(block)的电路图。

10.图4是存储单元阵列内的块的一部分区域的剖视图。

11.图5a是表示存储单元晶体管可取的阈值电压分布与数据的关系的图。

12.图5b是表示擦除动作后的存储单元晶体管的擦除深度的图。

13.图6是表示第1实施方式的存储系统中的基本擦除动作的图。

14.图7是表示擦除动作中的各信号的电压波形的图。

15.图8是表示第1实施方式的存储系统中的擦除动作的第1例的流程图。

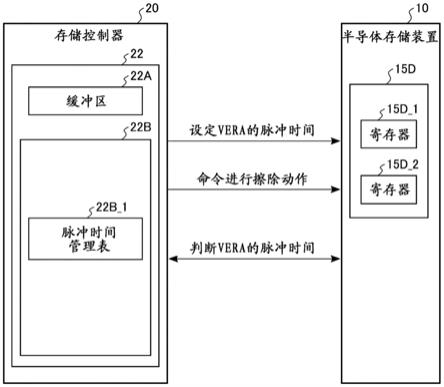

16.图9是表示在存储控制器与半导体存储装置之间进行的动作的交互(往来)的图。

17.图10是表示在存储控制器的存储器内设置的脉冲时间管理表的一个例子的图。

18.图11a是表示图8中的“对擦除电压vera的脉冲时间进行判断”的处理的流程图。

19.图11b是表示图11a中的基准值y1与写入动作/擦除动作的次数的关系的图。

20.图12是表示擦除动作的第1例中的擦除深度的判断方法的、表示阈值电压分布和判定电平的图。

21.图13是表示以判定电平进行了读出时存储于了缓冲区(buffer)的截止位数(number of off bits)的一个例子的图。

22.图14是表示以判定电平进行了读出时存储于了缓冲区的截止位数的其他例子的图。

23.图15是表示第1实施方式的擦除动作的第1例中的命令序列的图。

24.图16是表示第1例中的变形例的“对擦除电压vera的脉冲时间进行判断”的处理的流程图。

25.图17是表示第1实施方式的存储系统中的擦除动作的第2例的流程图。

26.图18是表示图17中的“对擦除电压vera的脉冲时间进行判断”的处理的流程图。

27.图19是表示擦除动作的第2例中的擦除深度的判断方法的、表示阈值电压分布和判定电平以及用于算出截止位数的数据的图。

28.图20是表示第1实施方式的擦除动作的第2例中的命令序列的图。

29.图21是表示作为比较例的写入/擦除的次数与基于擦除动作的存储单元的擦除深度之间的关系的图。

30.图22是表示第1实施方式中的写入/擦除的次数与基于擦除动作的存储单元的擦除深度之间的关系的图。

31.图23是表示第2实施方式的存储系统中的擦除动作的第1例的流程图。

32.图24是表示在存储控制器与半导体存储装置之间进行的动作的交互的图。

33.图25是表示在存储控制器的存储器内设置的电压值管理表的一个例子的图。

34.图26是表示图23中的“对擦除电压vera的初始电压值进行判断”的处理的流程图。

35.图27是表示第2实施方式的擦除动作的第1例中的命令序列的图。

36.图28是表示第2实施方式的存储系统中的擦除动作的第2例的流程图。

37.图29是表示图28中的“对擦除电压vera的初始电压值进行判断”的处理的流程图。

38.图30是表示第2实施方式的擦除动作的第2例中的命令序列的图。

39.图31是表示第3实施方式的存储系统中的擦除动作的第1例的流程图。

40.图32是表示在存储控制器与半导体存储装置之间进行的动作的交互的图。

41.图33是表示在存储控制器的存储器内设置的脉冲时间和电压值管理表的一个例子的图。

42.图34是表示第3实施方式的擦除动作的第1例中的命令序列的图。

43.图35是表示第3实施方式的存储系统中的擦除动作的第2例的流程图。

44.图36是表示第3实施方式的擦除动作的第2例中的命令序列的图。

45.图37是表示第4实施方式的擦除动作的第1例中的命令序列的图。

46.图38是表示第4实施方式的存储系统中的擦除动作的第2例的流程图。

47.图39是表示图38中的“对擦除电压vera的脉冲时间进行判断”的处理的流程图。

48.图40是表示相对于在图39所示的处理中使用的判定电平ar1~ar4的存储单元的阈值电压分布的图。

49.图41是表示以判定电平ar1~ar4取得的截止位数与擦除状态的关系的图。

50.图42是表示第4实施方式的擦除动作的第3例中的“对擦除电压vera的脉冲时间进行判断”的处理的流程图。

51.标号说明

52.1存储系统、2主机装置、10半导体存储装置、10_0~10_n存储芯片、11存储单元阵列、12输入输出电路、13逻辑控制电路、14就绪/忙电路、15寄存器组、15a状态寄存器、15b地址寄存器、15c命令寄存器、15d寄存器、16定序器、17电压生成电路、18驱动器、19行译码器模块、20存储控制器、21 cpu、22存储器、22a缓冲区、22b_1脉冲时间管理表、22b_2电压值管理表、22b_3脉冲时间以及电压值管理表、23主机接口、24 ecc电路、25 nand接口、26 ram接口、30缓冲存储器、31列译码器、32感测放大器模块、bl0~bli位线、blk0~blkm块、mt0~mt7存储单元晶体管、pd0~pdm脉冲时间、pa0~pam初始电压值、sgd0~sgd3选择栅极线、st1选择晶体管、st2选择晶体管、su0~su3串单元、wl0~wl7字线。

具体实施方式

53.以下,参照附图对实施方式进行说明。此外,在以下的说明中,对具有相同的功能以及结构的构成要素赋予共同的参照标号。另外,以下所示的各实施方式是对用于将该实施方式的技术思想具体化的装置、方法进行例示的,并非将构成部件的材质、形状、构造、配置等特定为下述的材质、形状、构造、配置等。

54.各功能块可以作为硬件、计算机软件中的任一者或者组合两者而得到的部分来实现。各功能块并非必须如以下的例子那样进行区别。例如,一部分功能也可以通过与例示的功能块不同的功能块来执行。进一步,例示的功能块也可以进一步分割为细分的功能子块。在此,作为存储系统包括的半导体存储装置,以在半导体基板的上方层叠有存储单元晶体管的三维层叠型的nand型闪速存储器为例来进行说明。

55.1.第1实施方式

56.以下,对第1实施方式的存储系统进行说明。

57.1.1构成

58.1.1.1存储系统的结构

59.首先,使用图1对第1实施方式的存储系统的结构进行说明。图1是表示第1实施方式的存储系统的结构的框图。存储系统1具备半导体存储装置10、存储控制器20以及缓冲存储器30。存储系统1与外部的主机装置2连接,能够相应于来自主机装置2的命令来执行各种动作。

60.半导体存储装置10包括一个或者多个存储芯片10_0、10_1、10_2、

……

、10_n(n为0以上的自然数)。存储芯片10_n具备多个存储单元,以非易失的方式存储数据。关于半导体存储装置10的详细,将在后面进行描述。

61.存储控制器20经由nand总线而连接于半导体存储装置10。nand总线进行遵循了nand接口的信号的收发。另外,存储控制器20经由主机总线而连接于主机装置2。存储控制器20对半导体存储装置10进行控制。另外,存储控制器20响应从主机装置2接收到的命令,对半导体存储装置10进行访问。

62.缓冲存储器30暂时性地保持在半导体存储装置10和主机装置2之间收发的写入数

据、读出数据。缓冲存储器30例如由dram(dynamic random access memory,动态随机访问存储器)、sram(static random access memory,静态随机访问存储器)等构成。

63.半导体存储装置10和存储控制器20例如也可以通过那些的组合构成一个半导体装置,可举出包括sd

tm

卡的存储卡、ssd(solid state drive,固态驱动器)等来作为其例子。另外,存储控制器20例如也可以是soc(system-on-a-chip,片上系统)等。

64.主机装置2例如是数码相机、个人计算机等,主机总线例如是遵循了sd

tm

接口的总线。

65.1.1.2存储控制器20的结构

66.接着,使用图1对存储控制器20的结构进行说明。存储控制器20具备cpu(central processing unit,中央处理单元)(或者处理器)21、存储器22、主机接口(主机i/f)23、ecc(error checking and correcting,错误检查和纠正)电路24、nand接口(nand i/f)25以及ram接口(ram i/f)26。

67.cpu21对存储控制器20整体的动作进行控制。例如,cpu21在从主机装置2接收到写入命令时,对其进行响应,对nand接口25发放写入命令。读出以及擦除时也是同样的。另外,cpu21执行损耗均衡(wear leveling)等的用于对半导体存储装置10进行管理的各种各样的处理。此外,以下说明的存储控制器20的动作既可以通过cpu21执行软件(或者固件)来实现,或者也可以由硬件来实现。

68.存储器22例如是dram、sram等的半导体存储器,被作为cpu21的工作区域来使用。存储器22保持:存储各种信息的缓冲区22a、用于对半导体存储装置10进行管理的固件以及各种管理表22b等。缓冲区22a例如存储与擦除动作后或者擦除动作后的写入动作后的存储单元的擦除结果有关的信息、即对擦除动作后或者写入动作后的擦除对象的存储单元组(例如块)的擦除状态进行表示的信息。管理表22b例如包含与每个块关联的擦除电压vera的参数。参数例如是擦除电压vera的脉冲时间或者初始电压值。管理表22b具有后述的管理表22b_1、22b_2以及22b_3。

69.主机接口23经由主机总线与主机装置2连接,负责与主机装置2的通信。主机接口23将从主机装置2接收到的命令和数据分别传送至cpu21、存储器22以及缓冲存储器30。另外,主机接口23响应来自cpu21的命令,向主机装置2传送缓冲存储器30内的数据。

70.ecc电路24执行数据的纠错处理。在写入动作时,ecc电路24基于从主机装置2接收到的写入数据来生成奇偶校验位(parity),对写入数据赋予所生成的奇偶校验位。在读出动作时,ecc电路24基于从半导体存储装置10接收到的读出数据来生成征状值(syndrome),基于所生成的征状值,对读出数据的错误进行检测以及纠正。

71.nand接口25经由nand总线与半导体存储装置10连接,负责与半导体存储装置10的通信。nand接口25基于从cpu21接收到的命令,向半导体存储装置10发送各种信号,另外,从半导体存储装置10接收各种信号。

72.1.1.3半导体存储装置10的结构

73.接着,对半导体存储装置10的结构进行说明。如图1所示,半导体存储装置10具有多个存储芯片10_n。存储芯片10_n例如包括能够以非易失的方式存储数据的nand型闪速存储器。

74.1.1.3.1存储芯片的结构

75.使用图2对存储芯片10_n的结构进行说明。图2是表示半导体存储装置10内的存储芯片10_n的结构的框图。存储芯片10_n具备存储单元阵列11、输入输出电路12、逻辑控制电路13、就绪/忙电路14、寄存器组15、定序器(或者控制电路)16、电压生成电路17、驱动器18、行译码器模块19、列译码器31以及感测放大器模块32。寄存器组15包括状态寄存器15a、地址寄存器15b、命令寄存器15c以及寄存器15d。

76.存储单元阵列11具备一个或者多个块blk0、blk1、blk2、

……

、blkm(m为0以上的整数)。多个块blk0~blkm各自包括与行和列关联的多个存储单元晶体管(以下也记载为存储单元)。存储单元晶体管是能够以电的方式擦除以及编程的非易失性存储单元。存储单元阵列11包括用于向存储单元晶体管施加电压的多条字线、多条位线以及源极线。以下,在记载为块blkr(r为0以上且m以下的整数)的情况下,设为表示块blk0~blkm中的各个。关于块blkr的具体结构,将在后面进行描述。

77.输入输出电路12以及逻辑控制电路13经由输入输出端子(或者nand总线)而连接于存储控制器20。输入输出电路12与存储控制器20之间经由输入输出端子来收发i/o信号dq(例如dq0、dq1、dq2、

……

、dq7)。i/o信号dq对命令、地址以及数据等进行通信。

78.逻辑控制电路13经由输入输出端子(或者nand总线)从存储控制器20接收外部控制信号。外部控制信号例如包括芯片使能信号cen、命令锁存使能信号cle、地址锁存使能信号ale、写入使能信号wen、读出使能信号ren以及写保护信号wpn。附注于信号名的“n”表示该信号是低态有效。

79.芯片使能信号cen能够实现存储芯片10_n的选择,在对该存储芯片10_n进行选择时被有效(assert)。命令锁存使能信号cle能够将被作为信号dq发送的命令锁存于命令寄存器15c。地址锁存使能信号ale能够将被作为信号dq发送的地址锁存于地址寄存器15b。写入使能信号wen能够将被作为信号dq发送的数据保持于输入输出电路12。读出使能信号ren能够输出从存储单元阵列11读出的数据来作为信号dq。写保护信号wpn在禁止对于存储芯片10_n的写入以及擦除时被有效。

80.就绪/忙电路14相应于来自定序器16的控制,生成就绪/忙信号r/bn。就绪/忙信号r/bn表示存储芯片10_n是处于就绪状态、还是处于忙状态。就绪状态表示处于能够受理来自存储控制器20的命令的状态。忙状态表示处于无法受理来自存储控制器20的命令的状态。存储控制器20通过从存储芯片10_n接收就绪/忙信号r/bn,能够获知存储芯片10_n是处于就绪状态、或是处于忙状态。

81.状态寄存器15a保持存储芯片10_n的动作所需要的状态信息sts,基于定序器16的指示来将该状态信息sts传送至输入输出电路12。地址寄存器15b保持从输入输出电路12传送来的地址add。地址add包括行地址和列地址。行地址例如包括指定动作对象的块blkr的块地址、和指定所指定的块内的动作对象的字线wl的页地址。命令寄存器15c保持从输入输出电路12传送来的命令cmd。命令cmd例如包括对定序器16命令进行写入动作的写入命令和命令进行读出动作的读出命令等。寄存器15d保持从存储控制器20发送、由输入输出电路12传送来的擦除电压vera的参数(例如脉冲时间或者初始电压值)。寄存器15d具有后述的寄存器15d_1、15d_2。在状态寄存器15a、地址寄存器15b、命令寄存器15c以及寄存器15d例如使用sram。

82.定序器16从命令寄存器15c接收命令,按照基于该命令的序列来统括地对存储芯

片10_n进行控制。定序器16对行译码器模块19、列译码器31、感测放大器模块32以及电压生成电路17等进行控制,执行写入动作、读出动作以及擦除动作。具体而言,定序器16基于从命令寄存器15c接收到的写入命令,对行译码器模块19、驱动器18以及感测放大器模块32进行控制,对由地址add指定的多个存储单元晶体管写入数据。另外,定序器16基于从命令寄存器15c接收到的读出命令,对行译码器模块19、驱动器18、列译码器31以及感测放大器模块32进行控制,从由地址add指定的多个存储单元晶体管读出数据。另外,定序器16基于从命令寄存器15c接收到的擦除命令,对行译码器模块19、驱动器18、列译码器31以及感测放大器模块32进行控制,对存储于由地址add指定的块的数据进行擦除。

83.电压生成电路17经由未图示的电源端子从存储芯片10_n的外部接收电源电压。使用该电源电压,生成写入动作、读出动作以及擦除动作所需要的多个电压。电压生成电路17向存储单元阵列11、驱动器18以及感测放大器模块32等供给所生成的电压。

84.驱动器18从电压生成电路17接收多个电压。驱动器18经由多条信号线向行译码器模块19供给从电压生成电路17供给的多个电压中的根据读出动作、写入动作以及擦除动作选择出的多个电压。驱动器18例如在擦除动作时向后述的阱布线cpwell供给擦除电压vera。

85.行译码器模块19从地址寄存器15b接收行地址,对该行地址进行译码。行译码器模块19基于行地址的译码结果,对多个块中的某一个进行选择,进一步对所选择的块blkr内的字线wl进行选择。进一步,行译码器模块19向所选择的块blkr传送从驱动器18供给的多个电压。

86.列译码器31从地址寄存器15b接收列地址,对该列地址进行译码。列译码器31基于列地址的译码结果,对位线进行选择。

87.感测放大器模块32在数据的读出动作时对从存储单元晶体管读出到位线的数据进行检测以及放大。进一步,感测放大器模块32暂时性地保持从存储单元晶体管读出的读出数据dat,并向输入输出电路12传送所保持的读出数据dat。另外,感测放大器模块32在数据的写入动作时暂时性地保持从输入输出电路12传送来的写入数据dat。进一步,感测放大器模块32向位线传送写入数据dat。

88.1.1.3.2块的结构

89.接着,使用图3对存储芯片10_n内的存储单元阵列11的电路结构进行说明。如前述的那样,存储单元阵列11具有多个块blk0~blkm。在此,对一个块blkr的电路结构进行说明,但其他块的电路结构也是同样的。

90.图3是存储单元阵列11内的块blkr的电路图。块blkr例如具备多个串单元su0、su1、su2、su3。以下,在记载为串单元su的情况下,设为表示串单元su0~su3的各个串单元。串单元su0~su3各自具备多个nand串(或者存储串)ns。

91.nand串ns包括多个存储单元晶体管mt0、mt1、mt2、

……

、mt7以及选择晶体管st1、st2。在此,为了使说明简明易懂,表示nand串ns具备8个存储单元晶体管mt0~mt7和2个选择晶体管st1、st2的例子。以下,在记载为存储单元晶体管mt的情况下,设为表示存储单元晶体管mt0~mt7中的各个。

92.存储单元晶体管mt0~mt7各自具备控制栅极和电荷蓄积层,以非易失性的方式存储数据。存储单元晶体管mt0~mt7串联连接在选择晶体管st1的源极与选择晶体管st2的漏

极之间。

93.存储单元晶体管mt能够存储1位的数据或者2位以上的数据。

94.串单元su0所包括的多个选择晶体管st1的栅极连接于选择栅极线sgd0。同样,串单元su1~su3各自的选择晶体管st1的栅极分别连接于选择栅极线sgd1~sgd3。选择栅极线sgd0~sgd3各自由行译码器模块19独立地进行控制。

95.串单元su0所包括的多个选择晶体管st2的栅极连接于选择栅极线sgs。同样地,串单元su1~su3各自的选择晶体管st2的栅极连接于选择栅极线sgs。此外,有时也在串单元su0~su3的选择晶体管st2的栅极分别连接个别的选择栅极线sgs。选择晶体管st1和st2被用于各种动作中的串单元su的选择。

96.块blkr所包括的存储单元晶体管mt0~mt7的控制栅极分别连接于字线wl0~wl7。字线wl0~wl7各自由行译码器模块19独立地进行控制。

97.位线bl0~bli(i为0以上的整数)中的各个连接于多个块blk0~blkm,与处于块blkr所包括的串单元su内的一个nand串ns连接。即,位线bl0~bli中的各个,连接于在块blkr内呈矩阵状配置的nand串ns中的、处于同一列的多个nand串ns的选择晶体管st1的漏极。另外,源极线sl连接于多个块blk0~blkm。即,源极线sl连接于块blkr所包括的多个选择晶体管st2的源极。

98.总而言之,串单元su包括多个连接于不同的位线bl并且与同一选择栅极线sgd连接的nand串ns。另外,块blkr包括共用字线wl的多个串单元su。进一步,存储单元阵列11包括共用位线bl的多个块blk0~blkm。

99.块blkr例如为数据的擦除单位。即,块blkr内所包含的存储单元晶体管mt保持的数据一并被擦除。此外,数据既可以以串单元su为单位来擦除,另外,也可以以小于串单元su的单位进行擦除。

100.将在一个串单元su内共有字线wl的多个存储单元晶体管mt称为单元组(cell unit)cu。将单元组cu所包括的多个存储单元晶体管mt分别存储的1位的数据的集合称为页。单元组cu的存储容量根据存储单元晶体管mt存储的数据的位数而变化。例如,在各存储单元晶体管mt存储1位数据的情况下,单元组cu存储1页数据,在存储2位数据的情况下,单元组cu存储2页数据,在存储3位数据的情况下,单元组cu存储3页数据。

101.以页为单位来进行对于单元组cu的写入动作和读出动作。换言之,对于配设于一个串单元su的与一条字线wl连接的多个存储单元晶体管mt一并进行读出和写入动作。

102.此外,块blkr具备的串单元的数量并不限于su0~su3,可以任意地进行设定。另外,串单元su所包括的nand串ns的数量、nand串ns具备的存储单元晶体管以及选择晶体管的数量也可以任意地进行设定。进一步,存储单元晶体管mt既可以是使用了绝缘膜来作为电荷蓄积层的monos(metal-oxide-nitride-oxide-silicon,金属氧化氮氧化硅)型,也可以是使用了导电层来作为电荷蓄积层的fg(floating gate,浮动栅极)型。

103.接着,使用图4对块blkr的截面构造进行说明。图4是块blkr的一部分区域的剖视图。如图所示,在半导体基板40上设置有p型阱区域40p。在p型阱区域40p上设置有多个nand串ns。即,在p型阱区域40p上依次层叠有布线层41、8层的布线层42、以及布线层43。布线层41作为选择栅极线sgs发挥功能,布线层42作为字线wl0~wl7发挥功能,布线层43作为选择栅极线sgd发挥功能。在所层叠的布线层间设置有未图示的绝缘层。

104.设置有贯通这些布线层41、42、43而到达p型阱区域40p的柱状的导电体44。在导电体44的侧面依次设置有栅极绝缘层45、电荷蓄积层(绝缘层)46以及块绝缘层47。通过这些来形成存储单元晶体管mt和选择晶体管st1以及st2。导电体44作为nand串ns的电流路径发挥功能,是形成各晶体管的沟道的区域。导电体44的上端经由过孔48而连接于金属布线层49。金属布线层49作为位线bl发挥功能。

105.在p型阱区域40p的表面区域内设置n+型杂质扩散层40s。在扩散层40s上设置接触插塞50。接触插塞50连接于金属布线层51。金属布线层51作为源极线sl发挥功能。

106.进一步,在p型阱区域40p的表面区域内设置p+型杂质扩散层40c。在扩散层40c上设置接触插塞52。接触插塞52连接于金属布线层53。金属布线层53作为阱布线cpwell发挥功能。阱布线cpwell是用于经由p型阱区域40p向导电体44施加电位的布线。

107.以上的结构在与记载了图4的纸面正交的方向(进深方向)上排列有多个,由在进深方向上排列的多个nand串ns的集合构成串单元su。

108.进一步,关于存储单元阵列11的结构,也可以是其他结构。即,存储单元阵列11的结构例如记载于“three dimensional stacked nonvolatile semiconductor memory”这一2009年3月19日申请的美国专利申请12/407,403号。另外,记载于“three dimensional stacked nonvolatile semiconductor memory”这一2009年3月18日申请的美国专利申请12/406,524号、“non-volatile semiconductor storage device and method of manufacturing the same”这一2010年3月25日申请的美国专利申请12/679,991号以及“semiconductor memory and method for manufacturing same”这一2009年3月23日申请的美国专利申请12/532,030号。这些专利申请的整体在本技术说明书中通过参照来援用。

109.另外,数据的擦除可以以块为单位或者以比块小的单位来进行。关于擦除方法,例如记载于“nonvolatile semiconductor memory device”这一2011年9月18日申请的美国专利申请13/235,389号。另外,记载于“non-volatile semiconductor storage device”这一2010年1月27日申请的美国专利申请12/694,690号。进一步,记载于“nonvolatile semiconductor memory device and data erase method thereof”这一2012年5月30日申请的美国专利申请13/483,610号。这些专利申请的整体在本技术说明书中通过参照来援用。

110.1.1.3.3存储单元晶体管的阈值电压分布

111.接着,对本实施方式中的存储单元晶体管mt可取的阈值电压分布与数据的关系进行说明。图5a是表示存储单元晶体管mt可取的阈值电压分布与数据的关系的图。在此,作为存储单元晶体管mt的存储方式,表示应用了能够在一个存储单元晶体管mt存储3位数据的tlc(triple-level cell,三层单元)方式的例子。此外,本实施方式也可以应用于:使用了能够在一个存储单元晶体管mt存储1位数据的slc(single-level cell,单层单元)方式、能够在一个存储单元晶体管mt存储2位数据的mlc(multi-level cell,多层单元)方式、能够在一个存储单元晶体管mt存储4位数据的qlc(quad-level cell,四层单元)方式等的其他存储方式的情况。

112.存储单元晶体管mt能够存储的3位(bit)数据由低位(lower)位(bit)、中位(middle)位以及高位(upper)位规定。在存储单元晶体管mt存储3位的情况下,存储单元晶体管mt可取与多个阈值电压相应的8个状态(state)中的任一状态。将8个状态从低的一方

起依次称为状态“er”、“a”、“b”、“c”、“d”、“e”、“f”、“g”。属于状态“er”、“a”、“b”、“c”、“d”、“e”、“f”、“g”的各个状态的多个存储单元晶体管mt形成如图5a所示那样的阈值电压的分布。

113.对状态“er”、“a”、“b”、“c”、“d”、“e”、“f”、“g”例如分别分配数据“111”、“110”、“100”、“000”、“010”、“011”、“001”、“101”。当设为低位位“x”、中位位“y”、高位位“z”时,位(bit)的排列为“z、y、x”。此外,阈值电压分布和数据的分配可以任意地进行设定。

114.为了对存储于读出对象的存储单元晶体管mt的数据进行读出,判定存储单元晶体管mt的阈值电压所属于的状态。为了进行状态的判定,可使用读出电压ar、br、cr、dr、er、fr、gr。

115.状态“er”例如相当于数据被擦除了的状态(擦除状态)。属于状态“er”的存储单元晶体管mt的阈值电压比电压ar低,例如具有负的值。

116.状态“a”~“g”相当于在电荷蓄积层注入电荷而在存储单元晶体管mt写入了数据的状态,属于状态“a”~“g”的存储单元晶体管mt的阈值电压例如具有正的值。属于状态“a”的存储单元晶体管mt的阈值电压比读出电压ar高且为读出电压br以下。属于状态“b”的存储单元晶体管mt的阈值电压比读出电压br高且为读出电压cr以下。属于状态“c”的存储单元晶体管mt的阈值电压比读出电压cr高且为读出电压dr以下。属于状态“d”的存储单元晶体管mt的阈值电压比读出电压dr高且为读出电压er以下。属于状态“e”的存储单元晶体管mt的阈值电压比读出电压er高且为读出电压fr以下。属于状态“f”的存储单元晶体管mt的阈值电压比读出电压fr高且为读出电压gr以下。属于状态“g”的存储单元晶体管mt的阈值电压比读出电压gr高且比电压vread低。

117.电压vread是施加于与非读出对象的单元组cu的存储单元晶体管mt连接的字线wl的电压,比处于任何状态的存储单元晶体管mt的阈值电压高。因此,在控制栅极被施加了电压vread的存储单元晶体管mt与所保持的数据无关地成为导通(on)状态。

118.另外,在相邻的阈值分布之间分别设定在写入动作中使用的校验电压。具体而言,与状态“a”、“b”、“c”、“d”、“e”、“f”、“g”对应地分别设定校验电压av、bv、cv、dv、ev、fv、gv。例如,校验电压av、bv、cv、dv、ev、fv、gv分别被设定为比读出电压ar、br、cr、dr、er、fr、gr高一些。

119.如上所述,各存储单元晶体管mt被设定为8个状态中的某一个,能够存储3位数据。另外,写入以及读出以一个单元组cu内的页为单位来进行。在存储单元晶体管mt存储3位数据的情况下,对一个单元组cu内的3个页分别分配低位位、中位位以及高位位。关于低位位、中位位以及高位位通过一次的写入动作进行写入或者通过一次的读出动作进行读出的页、即单元组cu保持的低位位的集合、中位位的集合以及高位位的集合,分别被称为低位(lower)页、中位(middle)页以及高位(upper)页。

120.在应用了上述数据的分配的情况下,低位页通过使用了读出电压ar、er的读出动作来确定。中位页通过使用了读出电压br、dr、fr的读出动作来确定。高位页通过使用了读出电压cr、gr的读出动作来确定。

121.1.2动作

122.以下,对第1实施方式的存储系统1中的擦除动作进行说明。擦除动作是将存储单元设定为擦除状态的动作。换言之,擦除动作是如下动作:抽出在存储单元晶体管mt的电荷

蓄积层中蓄积的电子,使存储单元晶体管mt的阈值电压转变为状态“er”的阈值电压分布内。

123.图5b是表示擦除动作后的存储单元晶体管mt的阈值电压分布的图。在对存储单元晶体管mt进行了擦除动作的情况下,属于状态“er”的存储单元晶体管mt的擦除状态转变为擦除不足状态、擦除适当状态、过擦除状态中的某一状态。

124.擦除不足状态是例如如图5b的(a)所示那样在阈值电压分布中状态“er”进入到状态“a”的下端(下摆)的状态,是在存储单元晶体管mt的电荷蓄积层中蓄积的电子的抽出不足的状态。擦除适当状态是如图5b的(b)所示那样在阈值电压分布中状态“er”与状态“a”之间以适当的距离隔开的状态,是在存储单元晶体管mt的电荷蓄积层中蓄积的电子的量适当的状态。过擦除状态是如图5b的(c)所示那样在阈值电压分布中状态“er”与状态“a”之间比适当的距离大地隔开的状态,是在存储单元晶体管mt的电荷蓄积层中蓄积的电子的抽出过多的状态。

125.在擦除动作后,存储单元晶体管mt的擦除状态处于擦除不足状态、擦除适当状态、过擦除状态中的某状态。将擦除动作后的存储单元晶体管mt的擦除状态定义为擦除深度。

126.通过避免存储单元晶体管mt成为过擦除状态,换言之,通过避免存储单元晶体管mt的擦除深度变深,能够减少在存储单元中产生的损伤。另外,通过避免存储单元晶体管mt成为擦除不足状态,换言之,通过避免存储单元的擦除深度变浅,能够减少页读取中的读取错误。

127.1.2.1存储系统的擦除动作

128.存储于半导体存储装置10的数据的擦除动作根据从存储控制器20输出至半导体存储装置10的擦除命令来执行。半导体存储装置10中的擦除动作如前述的那样例如能够以块为单位、或者以比块小的单位来进行。在此,示出以块为单位进行擦除动作的情况来作为例子。

129.以下,对存储系统1中的数据的基本擦除动作进行说明。图6是表示存储系统1中的基本擦除动作的图。在图6中,从存储控制器20通过i/o信号dq0~dq7输出的命令由六边形表现,地址由圆角四边形(或者长圆形)表现。

130.如图6所示,存储控制器20向半导体存储装置10输出擦去建立(set up)命令“60h”,接着,输出擦除对象块的地址“add”,然后,输出擦去执行命令“d0h”。定序器16根据在命令寄存器15c中保持了擦去建立命令“60h”这一状况,对接收到擦除命令这一情况进行识别。进一步,定序器16对接收到擦去执行命令“d0h”这一情况进行响应,开始擦除动作。如图6所示,擦除动作包括数据的擦除处理和擦除校验处理。定序器16与该擦除动作的开始一起,使就绪/忙信号r/bn从就绪状态转变为忙状态(r/bn=“l”)。此外,附记于命令(或者地址)的“h”表示其值为16进制表示。

131.擦除处理是对在擦除对象块内的存储单元晶体管mt中存储的数据进行擦除的动作。详细而言,擦除处理是如下动作:向阱布线cpwell施加擦除电压vera,从擦除对象块内的存储单元晶体管mt的电荷蓄积层抽出电子。所施加的擦除电压vera的脉冲时间可以设定为预先确定的值。脉冲时间是维持擦除电压vera的电压电平的时间,也称为脉冲宽度或者脉冲长度。擦除校验处理是如下动作:对通过擦除处理进行的对存储单元晶体管mt的数据擦除进行验证。换言之,擦除校验处理是如下的读出动作:确认存储单元晶体管mt的阈值电

压是否转变为了擦除状态的阈值电压。

132.擦除动作由擦除处理和在该擦除处理之后进行的擦除校验处理构成一个擦除循环。在图6的例子中图示了第一次和第二次的擦除循环。在通过擦除校验处理进行的验证中,在具有比某值高的阈值电压的存储单元晶体管mt的数量比预定数少的情况下判定为擦除校验已通过。另一方面,在具有比所述某值高的阈值电压的存储单元晶体管mt的数量比预定数多的情况下判定为擦除校验已失败。当这些判定结束时,定序器16结束擦除校验处理。以上说明的擦除处理和擦除校验处理的组对应于一次擦除循环。当擦除校验失败时,定序器16反复进行擦除循环,当擦除校验通过时,定序器16结束擦除动作。

133.在存储单元晶体管mt的电荷蓄积层中注入的电子不会在初次擦除循环中一下子变为比预定数少,通过多次擦除循环变为比预定数少。例如如图6所示,在第一次擦除循环中的擦除校验已失败的情况下,实施第二次擦除循环。反复进行的擦除循环的擦除处理中的擦除电压vera的电压被设定为增加了δvera的值。当擦除校验通过、该擦除动作结束时,定序器16使半导体存储装置10从忙状态转变为就绪状态。通过向就绪状态的转变,擦除处理结束。

134.图7是表示擦除动作中的各信号的电压波形的图。

135.首先,在时刻t0~t5执行擦除处理,然后,在时刻t5~t10执行擦除校验处理。这些t0~t10的一系列处理对应于一次擦除循环。

136.以下,对擦除处理进行描述。在时刻t0,位线bl、选择栅极线sgd及sgs、字线wl、源极线selsrc、以及阱布线cpwell被设定为电压vss(例如0v)。

137.接着,在时刻t1-t3,例如驱动器18向阱布线cpwell施加擦除电压vera。于是,在时刻t1-t3,存储单元晶体管mt的沟道区域被升压为擦除电压vera。进一步,通过由施加于阱布线cpwell的电压vera产生的电容耦合,位线bl、选择栅极线sgd及sgs、不是擦除对象的块(或者非选择块)的字线wl、以及源极线selsrc上升为电压vera。此外,选择栅极线sgs上升为比电压vera低电压δ的电压。

138.进一步,在时刻t1-t3,行译码器模块19向擦除对象的块(或者选择块)的字线wl施加比擦除电压vera低的电压vwl。由此,在存储单元晶体管mt的沟道区域的擦除电压vera和擦除对象块的字线wl的电压vwl产生电位差,从擦除对象块内的存储单元晶体管mt的电荷蓄积层向沟道层抽出电子。即,擦除对象块内的存储单元晶体管mt的数据被擦除。

139.然后,在时刻t3-t5,位线bl、选择栅极线sgd及sgs、字线wl、源极线selsrc、以及阱布线cpwell被设定为电压vss。通过以上,擦除处理结束。

140.接着,对时刻t5~t10中的擦除校验处理进行描述。

141.在时刻t6,行译码器模块19向选择块的选择栅极线sgd和sgs施加电压vsg。电压vsg是使选择晶体管st1和st2为导通状态的电压。

142.接着,在时刻t7-t9,行译码器模块19向擦除对象块的字线wl施加擦除校验电压vev。进一步,行译码器模块19向不是擦除对象的块的字线wl施加电压vread。擦除校验电压vev是用于判定擦除对象块内的存储单元晶体管mt的擦除状态的读出电压。

143.由此,感测放大器模块32对在位线bl所读出了的数据进行感测以及放大。按照其读出结果,定序器16判定对于擦除对象块的擦除动作是否已结束、即是擦除校验已通过还是已失败。若擦除动作未结束,则对于擦除对象块反复执行包括擦除处理和擦除校验处理

的擦除动作。

144.1.2.2第1实施方式的擦除动作

145.在第1实施方式的擦除动作中,基于擦除动作后的存储单元的擦除结果,或者基于擦除动作后的写入动作后的存储单元的擦除结果,对擦除电压vera的脉冲时间进行调整(或者变更)。例如,增长或者缩短擦除电压vera的脉冲时间。存储单元的擦除结果是指擦除动作后的存储单元的擦除深度的判断结果。换言之,存储单元的擦除结果是指在擦除动作后存储单元具有的擦除不足状态、擦除适当状态、过擦除状态中的某一状态。

146.1.2.2.1擦除动作的第1例

147.在第1例中,在擦除动作后,基于擦除对象块内的测定对象的字线wl以及串单元su所包含的存储单元的擦除结果,对擦除电压vera的脉冲时间进行更新。在此,示出基于存储单元的擦除结果来增长擦除电压vera的脉冲时间的例子。

148.图8是表示第1实施方式的存储系统1中的擦除动作的第1例的流程图。图9是表示在存储控制器20与半导体存储装置10之间进行的动作的交互的图。图10是表示在存储控制器20的存储器22内设置的脉冲时间管理表22b_1的一个例子的图。脉冲时间管理表22b_1对擦除电压vera的脉冲时间进行管理。在脉冲时间管理表22b_1中,对块blkr(r为0以上且m以下的整数)关联有在该块的擦除动作中使用的脉冲时间pdr。此外,图8所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

149.如图8和图9所示,当擦除动作开始时,首先,存储控制器20将脉冲时间管理表22b_1内的与擦除对象块blkr对应的擦除电压vera的脉冲时间pdr发送至半导体存储装置10而设定于半导体存储装置10的寄存器15d_1。详细而言,存储控制器20从脉冲时间管理表22b_1取得与擦除对象块blkr对应的擦除电压vera的脉冲时间pdr,并发送给半导体存储装置10,使之存储于寄存器15d_1(步骤s1)。例如,在擦除对象块为块blk0时,将与块blk0对应的脉冲时间pd0发送至半导体存储装置10,使之存储于寄存器15d_1。

150.接着,存储控制器20对半导体存储装置10命令进行擦除动作(步骤s2)。半导体存储装置10的定序器16使用存储于寄存器15d_1的擦除电压vera的脉冲时间pdr,对擦除对象块blkr执行擦除动作。

151.接着,存储控制器20在半导体存储装置10成为了就绪状态之后,从半导体存储装置10取得基于擦除动作的存储单元的擦除结果。存储控制器20基于从半导体存储装置10取得的存储单元的擦除结果,判断是否对擦除电压vera的脉冲时间pdr进行更新(以下也记载为“对擦除电压vera的脉冲时间进行判断”)(步骤s3)。例如该步骤s3的“对擦除电压vera的脉冲时间进行判断”的处理,每当进行擦除动作时、每当为预先设定的写入动作/擦除动作的执行次数时、或者写入动作/擦除动作的执行次数达到了预先设定的次数时,被执行。关于步骤s3的“对擦除电压vera的脉冲时间进行判断”的处理的详细,将在后面进行描述。

152.接着,存储控制器20基于步骤s3的“对擦除电压vera的脉冲时间进行判断”的判断结果,对存储器22的脉冲时间管理表22b_1内的与擦除对象块blkr对应的脉冲时间pdr进行更新,或者不进行更新而维持其不变(步骤s4)。通过以上,擦除动作结束。

153.接着,对图8所示的流程图中的步骤s3的“对擦除电压vera的脉冲时间进行判断”(步骤s3)的处理进行详细的描述。图11a是表示步骤s3的“对擦除电压vera的脉冲时间进行判断”的处理的流程图。图12是用于对擦除动作的第1例中的擦除深度的判断方法进行说明

的表示阈值电压分布和判定电平的图。此外,图11a所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

154.首先,进行用于对擦除动作后的存储单元的擦除深度进行判断的读出动作。如图11a的步骤s11所示,存储控制器20将读出电压设定为状态“a”的读出电压ar,进一步,设定使得从读出电压ar向低电压侧偏移的偏移值(电压值)。在此,如图12所示,将从读出电压ar偏移了偏移值后的读出电压定义为判定电平ar2。判定电平ar2是对擦除动作后的存储单元的擦除深度进行判断的电压电平。存储控制器20将从读出电压ar偏移了偏移值后的判定电平ar2设定于半导体存储装置10。此外,根据存储单元的擦除深度,既可以直接使用读出电压ar来作为判定电平ar2,也可以从读出电压ar向高电压侧偏移来作为判定电平ar2进行使用。进一步,存储控制器20指定擦除对象块内的测定对象的字线wl和串单元su(步骤s11)。此外,测定对象的字线wl既可以是一条字线,也可以是多条字线,另外,又可以是全部字线。

155.接着,存储控制器20对半导体存储装置10命令进行状态“a”的“单电平读取”(步骤s12)。“单电平读取”是取得表示对于状态之一的读出电压的阈值电压的大小的读出数据的处理。例如若是tlc的情况,则指定状态“a”~状态“g”中的某一个状态的读出电压。在此,使用从读出电压ar偏移了偏移值后的判定电平ar2来执行读出动作。当接收状态“a”的“单电平读取”的命令时,半导体存储装置10的定序器16以所设定的判定电平ar2对测定对象的存储单元执行读出动作。在该读出动作中,如图12所示,阈值电压比判定电平ar2高的存储单元不成为导通状态,而成为截止(off)状态。定序器16从半导体存储装置10向存储控制器20输出以判定电平ar2读出的结果ra2r。作为擦除动作后的擦除结果,存储控制器20对截止状态的存储单元的数量(以下记载为截止位数)“do1”进行计数。计数所得的截止位数被存储在存储器22内的缓冲区22a中。

156.接着,存储控制器20基于判定电平ar2下的读出结果,对擦除动作后的存储单元的擦除深度进行判断(步骤s13)。即,存储控制器20根据通过判定电平ar2下的读出动作取得的截止位数,判断擦除动作后的存储单元的擦除深度。详细而言,存储控制器20每当执行擦除对象块blkr的擦除动作时、或者以在几次的擦除动作中为一次的比例,执行判定电平ar2下的读出动作。当擦除动作中的ar2的读出动作达到次数x(例如4次)时,存储控制器20判断次数x的截止位数的平均值是否超过基准值y1(步骤s14)。在截止位数的平均值超过基准值y1的情况下(是),存储控制器20将擦除电压vera的脉冲时间pdr增长预定时间(步骤s15)。另一方面,在截止位数的平均值未超过基准值y1的情况下(否),存储控制器20结束“对擦除电压vera的脉冲时间进行判断”的处理。

157.此外,在步骤s14中,对次数x的截止位数的平均值和基准值y1进行了比较,但既可以对执行了次数x时的一条或者多条字线wl中的截止位数的最大值和基准值y1进行比较,或者也可以对执行了次数x时的全部字线wl中的截止位数的最大值和基准值y1进行比较。

158.另外,也可以根据存储单元的写入动作/擦除动作的次数,对基准值y1进行变更。在图11b中表示写入动作/擦除动作的次数与基准值y1的关系的一个例子。如图11b所示,也可以随着存储单元的写入动作/擦除动作的次数增加,使基准值y1减少。更具体而言,也可以每当写入动作/擦除动作的次数增加预定次数时,使基准值y1阶段性地减少。当写入动作/擦除动作的次数增加时,存储单元的疲敝会发展。通过根据写入动作/擦除动作的次数的增加来设定基准值y1,能够以更精细的单位使存储单元的擦除深度为一定。

159.接着,使用图13和图14对步骤s14中的截止位数是否超过基准值y1的判断进行说明。即,关于是否对脉冲时间pdr进行更新的判断的具体例进行说明。图13和图14是表示以判定电平ar2读出了测定对象的存储单元时存储于缓冲区22a的截止位数的图。t-3表示通过3次前的读出动作得到的截止位数,t-2表示通过2次前的读出动作得到的截止位数,t-1表示通过1次前(即上次)的读出动作得到的截止位数。进一步,t-0表示通过最新(本次)的读出动作得到的截止位数。此外,在此例如将基准值y1设为30。

160.图13是缓冲区22a的t-3、t-2、t-1分别存储了截止位数29、35、29且t-0存储了最新的截止位数23的例子。在该情况下,存储于t-3、t-2、t-1、t-0的截止位数的平均值成为29。截止位数的平均值29未超过基准值30,因此,存储控制器20不变更擦除电压vera的脉冲时间pdr,直接结束处理。例如,在存储控制器20的cpu21中安装有能够将截止位数的平均值和基准值作为参数来算出脉冲时间pdr的电路。由此,存储控制器20能够根据截止位数的平均值算出脉冲时间pdr,能够将该所算出的脉冲时间pdr反映在存储器22的脉冲时间管理表22b_1内。

161.进一步,在结束时,存储控制器20删除存储于缓冲区22a的t-3的最旧的截止位数,将t-2、t-1、t-0的值依次移位(shift)。移位后,缓冲区22a的t-3、t-2、t-1分别存储35、29、23。

162.图14是缓冲区22a的t-3、t-2、t-1分别存储了截止位数29、35、29且t-0存储了最新的截止位数32的例子。在该情况下,存储于t-3、t-2、t-1、t-0的截止位数的平均值成为31。截止位数的平均值31超过基准值30,因此,存储控制器20将擦除电压vera的脉冲时间pdr增长预定时间,然后,结束处理。

163.进一步,在结束时,存储控制器20将缓冲区22a的t3、t2、t1全部清除。

164.接着,对前述的擦除动作的第1例中的存储控制器20与半导体存储装置10之间的命令、地址以及数据的输入输出进行说明。

165.图15是表示第1实施方式的擦除动作的第1例中的命令序列的图。图15所示的命令序列包括命令、地址、数据输入输出周期(cycle)。命令由六边形表现,地址由圆角四边形(或者长圆形)表现,数据输入输出周期由四边形表现。从以下说明的存储控制器20向半导体存储装置10的命令和地址的输出、以及存储控制器20与半导体存储装置10之间的数据的输入输出,使用i/o信号dq0~dq7来进行。

166.如图15所示,命令序列具有与“设定擦除电压vera的脉冲时间(步骤s1)”对应的阶段(phase)p1、与“命令进行擦除动作(步骤s2)”对应的阶段p2、与单电平读取的偏移读取中的“设定判定电平ar2(步骤s11)”对应的阶段p3、以及与所述偏移读取中的“命令进行单电平读取(步骤s12)”对应的阶段p3、p4。

167.首先,在设定擦除电压vera的脉冲时间的阶段p1中,存储控制器20向半导体存储装置10依次输出命令“0xh”、地址“00h”以及数据“pdr”。命令“0xh”是指定擦除模式的命令。地址“00h”是设定擦除电压vera的脉冲时间的地址。数据“pdr”是表示与擦除对象块blkr对应的擦除电压vera的脉冲时间的数据,保持于寄存器15d_1。由此,存储控制器20对半导体存储装置10指定擦除模式,并且,将在对擦除对象块blkr的擦除动作中使用的擦除电压vera的脉冲时间pdr设定于半导体存储装置10的寄存器15d_1。

168.接着,在命令进行擦除动作的阶段p2中,存储控制器20向半导体存储装置10依次

输出擦去建立命令“60h”、擦除对象块blkr的地址“add”以及擦去执行命令“d0h”。由此,定序器16对阱布线cpwell施加脉冲时间pdr的擦除电压vera,执行对于擦除对象块blkr的擦除动作。定序器16在该擦除动作的执行期间中使就绪/忙信号r/bn从就绪状态转变为忙状态(r/bn=“l”)。

169.然后,存储控制器20向半导体存储装置10输出状态读取命令“70h”。接收状态读取命令“70h”,半导体存储装置10向存储控制器20输出表示擦除动作是已通过、还是已失败的数据。在此,例如半导体存储装置10向存储控制器20输出表示擦除动作已通过的数据“pass”。

170.接着,在设定判定电平ar2的阶段p3中,存储控制器20向半导体存储装置10依次输出单电平读取命令“x1h”和表示状态“a”的读出电压ar的地址“01h”。进一步,存储控制器20向半导体存储装置10依次输出偏移读取命令“x2h”、地址“01h”以及表示从读出电压ar的偏移值的数据“shift”。由此,存储控制器20将在单电平读取的偏移读取中使用的判定电平ar2设定于半导体存储装置10。

171.接着,在命令进行读取的阶段p4中,存储控制器20向半导体存储装置10依次输出读取建立命令“00h”、测定对象的地址“add1~add5”以及命令开始读出动作的读取执行命令“30h”。接收读取执行命令“30h”,半导体存储装置10的定序器16对于由地址“add1~add5”指定的测定对象的存储单元,执行判定电平ar2下的读出动作。定序器16在该读出动作的执行期间,使就绪/忙信号r/bn从就绪状态转变为忙状态(r/bn=“l”)。然后,定序器16在判定电平ar2下的读出动作中从半导体存储装置10向存储控制器20输出所读出的结果ra2r。存储控制器20对不成为导通状态而保持截止状态不变的存储单元的数量(即截止位数)“do1”进行计数。

172.如以上说明的那样,在第1例中,通过擦除动作后的读出动作,控制器20对擦除对象块blkr内的测定对象的存储单元中的截止位数进行计数。存储控制器20基于截止位数,对擦除电压vera的脉冲时间pdr进行更新,或者不进行更新而加以维持。

173.<第1例的变形例>

174.接着,对第1实施方式的擦除动作的第1例中的变形例进行说明。在该变形例中表示如下例子:基于擦除动作后的存储单元的擦除结果,缩短或者增长擦除电压vera的脉冲时间。

175.与前述的第1例同样地,变形例的擦除动作被按照图8所示的擦除动作的流程图加以执行。图8的流程图中的步骤s3的处理置换为图16所示的处理。图16是表示变形例的“对擦除电压vera的脉冲时间进行判断”(步骤s3)的处理的流程图。图16所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

176.图16所示的步骤s11~s15的处理与前述的图11a所示的步骤s11~s15的处理是同样的。即,存储控制器20将对擦除动作后的存储单元的擦除深度进行判断的判定电平ar2设定于半导体存储装置10。进一步,存储控制器20对擦除对象块blkr内的测定对象的字线wl和串单元su进行指定(步骤s11)。

177.接着,存储控制器20对半导体存储装置10命令进行“单电平读取”(步骤s12)。接收“单电平读取”的命令,半导体存储装置10的定序器16例如以所设定的判定电平ar2对测定对象的存储单元执行读出动作。

178.接着,存储控制器20根据从判定电平ar2下的读出结果ra2r计算出的截止位数,判断擦除动作后的存储单元的擦除深度(步骤s13)。详细而言,存储控制器20在擦除动作后判断存储单元的擦除深度的情况下,执行判定电平ar2下的读出动作。当判定电平ar2下的读出动作达到次数x时,存储控制器20判断次数x的截止位数的平均值是否超过基准值y1(步骤s14)。在步骤s14的判断中,次数x的截止位数的平均值超过基准值y1的情况下(是),存储控制器20将擦除电压vera的脉冲时间pdr增长预定时间(步骤s15),结束处理。另一方面,在次数x的截止位数的平均值未超过基准值y1的情况下(否),存储控制器20判断次数x的截止位数的平均值是否达到基准值y2(步骤s16)。

179.在步骤s16的判断中,次数x的截止位数的平均值未达到基准值y2的情况下(否),存储控制器20将擦除电压vera的脉冲时间pdr缩短预定时间(步骤s17),结束处理。另一方面,在次数x的截止位数的平均值达到基准值y2的情况下(是),存储控制器20不更新擦除电压vera的脉冲时间,直接结束处理。

180.如以上说明的那样,在第1例的变形例中,通过擦除动作后的读出动作,擦除对象块blkr内的测定对象的存储单元中的截止位数被从半导体存储装置10输出至存储控制器20。存储控制器20基于截止位数,判断存储单元处于擦除不足状态、擦除适当状态、过擦除状态中的哪个状态。存储控制器20在存储单元处于过擦除状态的情况下(步骤s16的“否”),缩短擦除电压vera的脉冲时间pdr(步骤s17)。在存储单元处于擦除适当状态的情况下(步骤s16的“是”),不更新脉冲时间pdr,另外,在存储单元处于擦除不足状态的情况下(步骤s14的“是”),增长脉冲时间pdr(步骤s15)。

181.1.2.2.2擦除动作的第2例

182.在第2例中,在擦除动作后的写入动作后,基于擦除对象块内的测定对象的字线wl和串单元su所包括的存储单元的擦除结果,对擦除电压vera的脉冲时间进行更新。在此,示出增长脉冲时间的例子。在第2例中,在擦除动作与是否更新脉冲时间的判断之间追加有写入动作。

183.图17是表示第1实施方式的存储系统1中的擦除动作的第2例的流程图。图17所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

184.与第1例同样地,存储控制器20将脉冲时间管理表22b_1内的与擦除对象块blkr对应的擦除电压vera的脉冲时间pdr发送至半导体存储装置10,设定于半导体存储装置10的寄存器15d_1(步骤s1)。进一步,存储控制器20对半导体存储装置10命令进行擦除动作(步骤s2)。接收擦除动作的命令,半导体存储装置10的定序器16对擦除对象块blkr执行擦除动作。

185.在对擦除对象块blkr执行了擦除动作之后,存储控制器20对半导体存储装置10命令进行写入动作(步骤s5)。接收写入动作的命令,半导体存储装置10的定序器16对擦除对象块blkr内的写入对象的存储单元执行写入动作。写入动作的命令被反复进行,直到满足完成块的一部分的写入、完成块的全面写入为止中的任一个(步骤s6)。

186.接着,存储控制器20基于写入动作后的存储单元的擦除状态,判断是否对擦除电压vera的脉冲时间pdr进行更新(步骤s3a)。例如,该步骤s3a的“对擦除电压vera的脉冲时间进行判断”的处理与第1例同样地,每当在擦除动作后进行写入动作时、每当为预先设定的写入动作/擦除动作的执行次数时、或者写入动作/擦除动作的执行次数达到了预先设定

的次数时,被加以执行。关于步骤s3a的“对擦除电压vera的脉冲时间进行判断”的处理的详细,将在后面进行描述。

187.接着,存储控制器20基于步骤s3a的“对擦除电压vera的脉冲时间进行判断”的判断结果,对存储器22的脉冲时间管理表22b_1内的与擦除对象块blkr对应的脉冲时间pdr进行更新,或者不进行更新而保持不变地加以维持(步骤s4)。通过以上,擦除动作结束。

188.接着,对图17所示的流程图中的步骤s3a的“对擦除电压vera的脉冲时间进行判断”的处理进行详细的描述。图18是表示步骤s3a的“对擦除电压vera的脉冲时间进行判断”的处理的流程图。图19是用于对擦除动作的第2例中的擦除深度的判断方法进行说明的表示阈值电压分布和判定电平以及用于算出截止位数的数据的图。此外,图18所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

189.首先,如图18所示,存储控制器20设定从读出电压ar偏移的偏移值。在此,如图19的(a)所示,将从读出电压ar偏移了偏移值后的读出电压定义为判定电平ar3。判定电平ar3是对写入动作后的存储单元的擦除深度进行判断的电压电平。存储控制器20将从读出电压ar偏移了偏移值后的判定电平ar3设定于半导体存储装置10。此外,根据存储单元的擦除深度,既可以将读出电压ar直接作为判定电平ar3进行使用,也可以从读出电压ar向高电压侧偏移来作为判定电平ar3进行使用。进一步,存储控制器20对擦除对象块blkr内的测定对象的字线wl和串单元su进行指定(步骤s21)。此外,测定对象的字线wl既可以是一条字线,也可以是多条字线,另外,又可以是全部字线。在以后的说明中,示出图5a所示的存储映射下的读取。在图5a中,读出电压ar被映射于“低位页”的读出。

190.接着,存储控制器20对半导体存储装置10命令进行包括ar的“低位页读取”(步骤s22)。“低位页读取”例如是通过使用了读出电压ar、er的读出动作对低位页的数据进行读出的动作,在此,代替读出电压ar而使用判定电平ar3。接收“低位页读取”的命令,半导体存储装置10的定序器16例如对测定对象的存储单元使用所设定的判定电平ar3和读出电压er来执行读出动作,得到图19的(b)所示的纠错前的低位页数据rlp。低位页数据rlp是刚使用判定电平ar3和读出电压er进行了读出之后的数据,是未实施纠错的数据。

191.接着,存储控制器20从半导体存储装置10接收在判定电平ar3和读出电压er的读出动作中得到的纠错前的低位页数据rlp。存储控制器20通过ecc电路24对纠错前的低位页数据rlp的错误进行纠正,得到图19的(b)所示的纠错后的低位页数据clp(步骤s23)。

192.接着,存储控制器20从所读出的低位页数据分离仅是判定电平ar3的读出数据。例如,将状态“c”的读出电压cr设定于半导体存储装置10。在本实施方式中,不拘泥于状态“c”,只要是状态“a”和状态“e”能分离的状态“b”、“c”、“d”,则都是可以的。进一步,存储控制器20对半导体存储装置10指定擦除对象块blkr内的测定对象的字线wl和串单元su(步骤s24)。

193.接着,存储控制器20对半导体存储装置10命令进行状态“c”的“单电平读取”(步骤s25)。接收“单电平读取”的命令,半导体存储装置10的定序器16例如以所设定的读出电压cr对测定对象的存储单元执行读出动作,得到图19的(b)所示的状态“c”的读出结果rcr。

194.存储控制器20进行对在步骤s22中得到的纠错前的低位页数据rlp实施了逻辑非运算而得到的数据rlp2与在步骤s23、s25中得到的两个数据clp、rcr的逻辑与运算,对用于判断擦除深度的截止位数进行计数。存储控制器20将所取得的截止位数存储于存储器22内

的缓冲区22a。

195.接着,存储控制器20基于写入动作后的存储单元的擦除状态,对写入动作后的擦除对象存储单元的擦除深度进行判断。即,存储控制器20根据存储于缓冲区22a的截止位数,对写入动作后的擦除对象存储单元的擦除深度进行判断(步骤s26)。详细而言,存储控制器20在擦除动作后的写入动作后判断存储单元的擦除深度的情况下,执行对于测定对象的存储单元的步骤s22、s23、s25的处理。当步骤s22、s23、s25的处理达到次数x(例如4次)时,存储控制器20判断次数x的截止位数的平均值是否超过基准值y1(步骤s27)。在次数x的截止位数的平均值超过基准值y1的情况下(是),存储控制器20将擦除电压vera的脉冲时间pdr增长预定时间(步骤s28)。另一方面,在次数x的截止位数的平均值未超过基准值y1的情况下(否),存储控制器20结束“对擦除电压vera的脉冲时间进行判断”的处理。

196.此外,在步骤s27中,对次数x的截止位数的平均值与基准值y1进行了比较,但既可以对执行了次数x时的一条或者多条字线wl中的截止位数的最大值与基准值y1进行比较,或者也可以对执行了次数x时的全部字线wl中的截止位数的最大值与基准值y1进行比较。

197.关于前述的步骤s27中的截止位数是否超过基准值y1的判断、即是否对脉冲时间进行更新的判断的具体例,与第1例是同样的。在存储于缓冲区22a的t-3、t-2、t-1、t-0的截止位数的平均值未超过基准值30的情况下,存储控制器20不更新擦除电压vera的脉冲时间,直接地结束处理。另一方面,在存储于缓冲区22a的t-3、t-2、t-1、t-0的截止位数的平均值超过基准值30的情况下,存储控制器20将擦除电压vera的脉冲时间增长预定时间,然后,结束处理。

198.接着,对第1实施方式的擦除动作的第2例中的存储控制器20与半导体存储装置10之间的命令、地址以及数据的输入输出进行说明。

199.图20是表示第1实施方式的擦除动作的第2例中的命令序列的图。对于以下说明的从存储控制器20向半导体存储装置10的命令和地址的输出、以及存储控制器20与半导体存储装置10之间的数据的输入输出,使用i/o信号dq0~dq7来进行。图20所示的命令序列包括命令、地址、数据输入输出周期。命令由六边形表现,地址由圆角四边形(或者长圆形)表现,数据输入输出周期由四边形表现。

200.如图20所示,命令序列具有:与“设定擦除电压vera的脉冲时间(步骤s1)”对应的阶段p1、与“命令进行擦除动作(步骤s2)”对应的阶段p2、与“命令进行写入动作(步骤s5)”对应的阶段p5、与低位页读取的偏移读取中的“设定判定电平ar3(步骤s21)”对应的阶段p3a、与所述偏移读取中的“命令进行低位页读取(步骤s22)”对应的阶段p4a以及与“命令进行单电平读取(步骤s25)”对应的阶段p6。此外,阶段p1、p2与前述的图15所示的阶段p1、p2是同样的。

201.首先,在设定擦除电压vera的脉冲时间的阶段p1中,存储控制器20向半导体存储装置10依次输出命令“0xh”、地址“00h”以及数据“pdr”。由此,存储控制器20对半导体存储装置10指定擦除模式,并且,将在对擦除对象块blkr的擦除动作中使用的擦除电压vera的脉冲时间pdr设定于半导体存储装置10的寄存器15d_1。

202.接着,在命令进行擦除动作的阶段p2中,存储控制器20向半导体存储装置10依次输出擦去建立命令“60h”、擦除对象块blkr的地址“add”以及擦去执行命令“d0h”。接收擦去执行命令“d0h”,半导体存储装置10的定序器16对阱布线cpwell施加脉冲时间pdr的擦除电

压vera,执行对于擦除对象块blkr的擦除动作。接着,存储控制器20向半导体存储装置10输出状态读取命令“70h”。接收状态读取命令“70h”,半导体存储装置10在此例如向存储控制器20输出表示擦除动作已通过的数据“pass”。

203.接着,在命令进行写入动作的阶段p5中,存储控制器20向半导体存储装置10依次输出写建立命令“80h”、写入对象的地址“add1~add5”、写入数据“di”以及写执行命令“10h”。接收写执行命令“10h”,半导体存储装置10的定序器16对由地址“add1~add5”指定的写入对象的存储单元,执行与写入数据“di”相应的写入动作。定序器16在该写入动作的执行期间,使就绪/忙信号r/bn从就绪状态转变为忙状态(r/bn=“l”)。此外,阶段p5是对于块内的特定地址的写入动作。存储控制器20也可以为了进行向块内的一部分的地址或者全部地址的写入动作而反复实施阶段p5。

204.接着,在设定判定电平ar3的阶段p3a中,存储控制器20向半导体存储装置10依次输出偏移读取命令“x2h”、表示读出电压ar的地址“01h”以及表示从读出电压ar的偏移值的数据“shift”。由此,存储控制器20将在低位页读取的偏移读取中使用的判定电平ar3设定于半导体存储装置10。

205.接着,在命令进行低位页读取的阶段p4a中,存储控制器20向半导体存储装置10依次输出表示低位页的命令“01h”、读取建立命令“00h”、测定对象的地址“add1~add5”以及读取执行命令“30h”。接收读取执行命令“30h”,半导体存储装置10的定序器16对由地址“add1~add5”指定的测定对象的存储单元执行判定电平ar3下的读出动作、和状态“e”的读出电压er下的读出动作。定序器16在该读出动作的执行期间,使就绪/忙信号r/bn从就绪状态转变为忙状态(r/bn=“l”)。然后,定序器16向存储控制器20输出通过判定电平ar3和读出电压er下的读出动作得到的纠错前的低位页数据rlp。存储控制器20通过ecc电路24对所接收到的纠错前的低位页数据rlp进行纠错,算出纠错后的低位页数据clp。

206.接着,在命令进行单电平读取的阶段p6中,存储控制器20向半导体存储装置10依次输出单电平读取命令“x1h”、表示状态“c”的读出电压cr的地址“03h”、读取建立命令“00h”、测定对象的地址“add1~add5”以及读取执行命令“30h”。接收读取执行命令“30h”,半导体存储装置10的定序器16对由地址“add1~add5”指定的测定对象的存储单元执行读出电压cr下的读出动作。定序器16在该读出动作的执行期间,使就绪/忙信号r/bn从就绪状态转变为忙状态(r/bn=“l”)。然后,半导体存储装置10向存储控制器20输出通过读出电压cr下的读出动作得到的读出结果rcr。

207.然后,如上所述,存储控制器20进行对纠错前的低位页数据rlp实施了逻辑非运算而得到的数据rlp2与两个数据clp、rcr的逻辑与运算,算出用于判断擦除深度的截止位数。

208.在第2例中,通过写入动作后的读出动作,存储控制器20取得擦除对象块blkr内的测定对象的存储单元中的截止位数。存储控制器20基于截止位数,对擦除电压vera的脉冲时间pdr进行更新,或者不更新而加以维持。

209.1.3第1实施方式的效果

210.根据第1实施方式,通过在擦除动作后或者写入动作后对擦除电压vera的脉冲时间进行调整或者更新,能够使得通过擦除动作实现的对于存储单元的擦除优化。换言之,通过对擦除电压vera的脉冲时间进行调整或者更新,能够避免因擦除动作而存储单元转变为擦除不足状态或者过擦除状态。

211.通过避免因擦除动作而存储单元向过擦除状态的转变,能够减少因擦除动作而产生于存储单元的损伤。进一步,通过避免因擦除动作而存储单元向擦除不足状态的转变,例如能够减少包括状态a的读出的页读取中的读取错误。

212.以下,示出比较例,对第1实施方式的效果进行详细的描述。图21是表示作为比较例的对于存储单元的写入/擦除的次数与通过擦除动作实现的存储单元的擦除深度的关系的图。当存储单元的写入/擦除的次数增加时,存储单元的疲敝会发展。因此,随着写入/擦除的次数增加,即使对存储单元进行擦除动作,对蓄积于存储单元的电荷蓄积层的电子进行抽出的量也逐渐减少,擦除深度逐渐变浅。因此,如图21所示,当使擦除循环的次数为一定来进行擦除动作时,存储单元的擦除深度会逐渐变浅,会接近擦除深度的容许范围的上限。于是,在超过擦除深度的容许范围之前,使擦除循环的次数增加。当使擦除循环的次数增加时,刚使次数增加之后,存储单元的擦除深度变深,成为存储单元的疲敝发展的原因。

213.在前述的第1实施方式中,基于擦除动作后或者写入动作后的擦除对象存储单元的擦除结果(或者擦除状态、擦除深度),对在对于所述擦除对象存储单元的下一次的擦除动作中使用的擦除电压vera的脉冲时间进行调整或者更新。

214.详细而言,根据擦除动作后或者写入动作后的状态“er”的存储单元的阈值电压分布状态,判断存储单元的擦除深度处于擦除不足状态、擦除适当状态和过擦除状态中的哪个状态。并且,基于擦除深度的状态,对擦除电压vera的脉冲时间进行调整或者更新。例如,在存储单元的擦除深度处于擦除不足状态的情况下,增长擦除电压vera的脉冲时间。另一方面,在存储单元的擦除深度处于过擦除状态的情况下,缩短擦除电压vera的脉冲时间。

215.将第1实施方式的擦除动作中的存储单元的写入/擦除的次数与通过擦除动作实现的存储单元的擦除深度的关系示于图22。在第1实施方式中,如上所述,通过对擦除电压vera的脉冲时间进行调整,能够实现对于存储单元的精细的擦除,如图22所示,与图21的比较例相比,能够避免存储单元的擦除深度变深以及变浅。通过避免存储单元的擦除深度变深,换言之,通过避免存储单元成为过擦除状态,能够减少产生于存储单元的损伤。进一步,通过避免存储单元的擦除深度变浅,换言之,通过避免存储单元成为擦除不足状态,能够减少页读取中的读取错误。

216.如以上说明的那样,根据第1实施方式,能够提供:能减少存储单元的损伤以及读取错误、能使擦除动作的性能提高的存储系统和半导体存储装置。

217.2.第2实施方式

218.以下,对第2实施方式的存储系统1中的擦除动作进行说明。第2实施方式的存储系统1具备的结构与第1实施方式的结构是同样的。在第2实施方式中,主要对与第1实施方式不同的点进行说明。

219.2.1第2实施方式的擦除动作

220.在第2实施方式的擦除动作中,基于擦除动作后的存储单元的擦除结果,或者基于擦除动作后的写入动作后的存储单元的擦除结果,对擦除电压vera的初始电压值进行调整(或者变更)。例如,提高或者降低擦除电压vera的初始电压值。在该第2实施方式中进行调整的擦除电压vera的初始电压值是第一次的擦除循环中的擦除电压vera的电压值。

221.2.1.1擦除动作的第1例

222.在第1例中,在擦除动作后,基于擦除对象块内的测定对象的字线wl和串单元su所

包括的存储单元的擦除结果,对擦除电压vera的初始电压值进行更新。在此,示出基于存储单元的擦除结果来提高擦除电压vera的初始电压值的例子。

223.图23是表示第2实施方式的存储系统1中的擦除动作的第1例的流程图。图24是表示在存储控制器20与半导体存储装置10之间进行的动作的交互的图。图25是表示在存储控制器20的存储器22内设置的电压值管理表22b_2的一个例子的图。电压值管理表22b_2对擦除电压vera的初始电压值进行管理。在电压值管理表22b_2中,与块blkr(r为0以上且m以下的整数)关联有在该块blkr的擦除动作中使用的初始电压值par。图23所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

224.如图23和图24所示,当擦除动作开始时,首先,存储控制器20将电压值管理表22b_2内的与擦除对象块blkr对应的擦除电压vera的初始电压值par发送给半导体存储装置10,并设定于半导体存储装置10的寄存器15d_2。详细而言,存储控制器20从电压值管理表22b_2取得与擦除对象块blkr对应的擦除电压vera的初始电压值par,并发送给半导体存储装置10,使之存储于寄存器15d_2(步骤s31)。例如在擦除对象块为块blk0时,向半导体存储装置10发送与块blk0对应的初始电压值pa0,使之存储于寄存器15d_2。

225.接着,存储控制器20对半导体存储装置10命令进行擦除动作(步骤s32)。半导体存储装置10的定序器16使用存储于寄存器15d_2的擦除电压vera的初始电压值par,对擦除对象块blkr执行擦除动作。

226.接着,存储控制器20从半导体存储装置10取得基于擦除动作的存储单元的擦除结果。存储控制器20基于从半导体存储装置10取得的存储单元的擦除结果,判断是否对擦除电压vera的初始电压值par进行更新(以下,也记载为“对擦除电压vera的初始电压值进行判断”)(步骤s33)。例如,该步骤s33的“对擦除电压vera的初始电压值进行判断”的处理在每当进行擦除动作时、每当为预先设定的写入动作/擦除动作的执行次数时、或者写入动作/擦除动作的执行次数达到了预先设定的次数时,被加以执行。关于步骤s33的“对擦除电压vera的初始电压值进行判断”的处理的详细,将在后面进行描述。

227.接着,存储控制器20基于步骤s33的“对擦除电压vera的初始电压值进行判断”的判断结果,对存储器22的电压值管理表22b_2内的与擦除对象块blkr对应的初始电压值par进行更新,或者不进行更新而保持不变地加以维持(步骤s34)。通过以上,擦除动作结束。

228.接着,对图23所示的流程图中的步骤s33的“对擦除电压vera的初始电压值进行判断”的处理进行详细的描述。图26是表示步骤s33的“对擦除电压vera的初始电压值进行判断”的处理的流程图。图26所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

229.图26所示的步骤s11~s14的处理与前述的图11a所示的步骤s11~s14的处理是同样的。

230.如图26的步骤s11所示,存储控制器20将读出电压设定为状态“a”的读出电压ar,进一步,设定从读出电压ar偏移的偏移值。在此,将从读出电压ar偏移了偏移值后的读出电压定义为判定电平ar2。判定电平ar2是对擦除动作后的存储单元的擦除深度进行判断的电压电平。存储控制器20将从读出电压ar偏移了偏移值后的判定电平ar2设定于半导体存储装置10。进一步,存储控制器20对半导体存储装置10指定擦除对象块内的测定对象的字线wl和串单元su(步骤s11)。

231.接着,存储控制器20对半导体存储装置10命令进行状态“a”的“单电平读取”(步骤

s12)。当接收状态“a”的“单电平读取”的命令时,半导体存储装置10的定序器16以所设定的判定电平ar2对测定对象的存储单元执行读出动作。定序器16从半导体存储装置10向存储控制器20输出以判定电平ar2读出的结果ra2r。作为擦除动作后的擦除结果,存储控制器20根据所读出的结果ra2r对截止位数进行计数。截止位数被存储于存储器22内的缓冲区22a。

232.接着,存储控制器20基于判定电平ar2下的读出结果,对擦除动作后的存储单元的擦除深度进行判断。即,存储控制器20根据所取得的截止位数,对擦除动作后的存储单元的擦除深度进行判断(步骤s13)。详细而言,存储控制器20在擦除动作后对存储单元的擦除深度进行判断的情况下,执行判定电平ar2下的读出动作。当读出动作达到次数x时,存储控制器20判断次数x的截止位数的平均值是否超过基准值y1(步骤s14)。

233.在步骤s14的判断中,截止位数的平均值超过基准值y1的情况下(是),存储控制器20将擦除电压vera的初始电压值par提高预定值(步骤s18)。另一方面,在截止位数的平均值未超过基准值y1的情况下(否),存储控制器20结束“对擦除电压vera的初始电压值进行判断”的处理。

234.关于步骤s14中的截止位数是否超过基准值y1的判断的具体例,与第1实施方式是同样的。在存储于缓冲区22a的t-3、t-2、t-1、t-0的截止位数的平均值未超过基准值30的情况下,存储控制器20不变更擦除电压vera的初始电压值par,直接结束处理。另一方面,在存储于缓冲区22a的t-3、t-2、t-1、t-0的截止位数的平均值超过基准值30的情况下,存储控制器20将擦除电压vera的初始电压值par提高预定值,然后,结束处理。

235.接着,对第2实施方式的擦除动作的第1例中的存储控制器20与半导体存储装置10之间的命令、地址以及数据的输入输出进行说明。

236.图27是表示第2实施方式的擦除动作的第1例中的命令序列的图。以下说明的从存储控制器20向半导体存储装置10的命令和地址的输出、以及存储控制器20与半导体存储装置10之间的数据的输入输出,使用i/o信号dq0~dq7来进行。图27所示的命令序列包括命令、地址、数据输入输出周期。命令由六边形表现,地址由圆角四边形(或者长圆形)表现,数据输入输出周期由四边形表现。

237.如图27所示,命令序列具有与“设定擦除电压vera的初始电压值(步骤s21)”对应的阶段p11、与“命令进行擦除动作(步骤s22)”对应的阶段p2、与单电平读取的偏移读取中的“设定判定电平ar2(步骤s11)”对应的阶段p3以及与所述偏移读取中的“命令进行单电平读取(步骤s12)”对应的阶段p3、p4。此外,阶段p2、p3、p4与前述的图15所示的阶段p2、p3、p4是同样的。

238.首先,在设定擦除电压vera的初始电压值的阶段p11中,存储控制器20向半导体存储装置10依次输出命令“0xh”、地址“01h”以及数据“par”。命令“0xh”是指定擦除模式的命令。地址“01h”是设定擦除电压vera的初始电压值的地址。数据“par”是表示与擦除对象块blkr对应的擦除电压vera的初始电压值的数据。由此,存储控制器20对半导体存储装置10指定擦除模式,并且,将在对擦除对象块blkr的擦除动作中使用的擦除电压vera的初始电压值par设定于半导体存储装置10的寄存器15d_2。

239.接着,在命令进行擦除动作的阶段p2中,存储控制器20向半导体存储装置10依次输出擦去建立命令“60h”、擦除对象块blkr的地址“add”以及擦去执行命令“d0h”。接收擦去执行命令“d0h”,半导体存储装置10的定序器16向阱布线cpwell施加初始电压值par的擦除

电压vera,执行对于擦除对象块blkr的擦除动作。

240.然后,存储控制器20向半导体存储装置10输出状态读取命令“70h”。接收状态读取命令“70h”,半导体存储装置10向存储控制器20输出表示擦除动作是已通过、还是已失败的数据。在此,例如半导体存储装置10向存储控制器20输出表示擦除动作已通过的数据“pass”。

241.接着,在设定判定电平ar2的阶段p3中,存储控制器20向半导体存储装置10依次输出状态“a”的单电平读取命令“x1h”、和表示状态“a”的读出电压ar的地址“01h”。进一步,存储控制器20向半导体存储装置10依次输出偏移读取命令“x2h”、地址“01h”以及表示从读出电压ar的偏移值的数据“shift”。由此,存储控制器20将在单电平读取的偏移读取中使用的判定电平ar2设定于半导体存储装置10。

242.接着,在命令进行读取的阶段p4中,存储控制器20向半导体存储装置10依次输出读取建立命令“00h”、测定对象的地址“add1~add5”以及读取执行命令“30h”。接收读取执行命令“30h”,半导体存储装置10的定序器16对于由地址“add1~add5”指定的测定对象的存储单元,执行判定电平ar2下的读出动作。然后,定序器16从半导体存储装置10向存储控制器20输出在判定电平ar2下的读出动作中得到的读出结果ra2r。存储控制器20根据读出结果ra2r,对不成为导通状态而保持截止状态不变的截止位数“do2”进行计数。

243.如前述那样,在第1例中,对提高擦除电压vera的初始电压值par的例子进行了说明,但与第1实施方式的第1例的变形例所示的同样地,也能够基于存储单元的擦除结果,提高或者降低擦除电压vera的初始电压值par。

244.在第1例中,通过擦除动作后的读出动作,半导体存储装置10向存储控制器20输出擦除对象块blkr内的测定对象的存储单元中的截止位数。存储控制器20基于截止位数,对擦除电压vera的初始电压值par进行更新,或者不进行更新而加以维持。

245.2.1.2擦除动作的第2例

246.在第2例中,在擦除动作后的写入动作后,基于擦除对象块内的测定对象的字线wl和串单元su所包括的存储单元的擦除结果,对擦除电压vera的初始电压值进行更新。在此,示出基于存储单元的擦除结果来提高擦除电压vera的初始电压值的例子。在第2例中,在擦除动作与是否对初始电压值进行更新的判断之间追加写入动作。

247.图28是表示第2实施方式的存储系统1中的擦除动作的第2例的流程图。图28所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

248.与第1例同样地,存储控制器20向半导体存储装置10发送电压值管理表22b_2内的与擦除对象块blkr对应的擦除电压vera的初始电压值par,使之存储于半导体存储装置10的寄存器15d_2(步骤s31)。进一步,存储控制器20对半导体存储装置10命令进行擦除动作(步骤s32)。接收擦除动作的命令,半导体存储装置10的定序器16对擦除对象块blkr执行擦除动作。

249.在对擦除对象块blkr执行了擦除动作之后,存储控制器20对半导体存储装置10命令进行写入动作(步骤s35)。接收写入动作的命令,半导体存储装置10的定序器16对擦除对象块blkr内的写入对象的存储单元执行写入动作。

250.接着,存储控制器20基于写入动作后的存储单元的擦除状态,判断是否对擦除电压vera的初始电压值par进行更新(以下,也记载为“对擦除电压vera的初始电压值进行判

断”)(步骤s33a)。例如,该步骤s33a的“对擦除电压vera的初始电压值进行判断”的处理与第1例同样地,每当在擦除动作后进行写入动作时、或者每当为预先设定的写入动作/擦除动作的执行次数时、或者写入动作/擦除动作的执行次数达到了预先设定的次数时,被加以执行。关于步骤s33a的“对擦除电压vera的初始电压值进行判断”的处理的详细情况,将在后面进行描述。

251.接着,存储控制器20基于步骤s33a的“对擦除电压vera的初始电压值进行判断”的判断结果,对存储器22的电压值管理表22b_2内的与擦除对象块blkr对应的初始电压值par进行更新,或者不进行更新而保持不变地加以维持(步骤s34)。通过以上,擦除动作结束。

252.接着,对图28所示的流程图中的步骤s33a的“对擦除电压vera的初始电压值进行判断”的处理进行详细的描述。图29是表示步骤s33a的“对擦除电压vera的初始电压值进行判断”的处理的流程图。此外,图29所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

253.图29所示的步骤s21~s27的处理与前述的图18所示的步骤s21~s27的处理是同样的。

254.如图29所示,存储控制器20将读出电压设定为状态“a”的读出电压ar,进一步,设定从读出电压ar偏移的偏移值。在此,将从读出电压ar偏移了偏移值后的读出电压定义为判定电平ar3。判定电平ar3是对擦除动作后的存储单元的擦除深度进行判断的电压电平。存储控制器20将从读出电压ar偏移了偏移值后的判定电平ar3设定于半导体存储装置10。进一步,存储控制器20对半导体存储装置10指定擦除对象块内的测定对象的字线wl和串单元su(步骤s21)。

255.接着,存储控制器20对半导体存储装置10命令进行“低位页读取”(步骤s22)。接收“低位页读取”的命令,半导体存储装置10的定序器16例如以所设定的判定电平ar3和读出电压er对测定对象的存储单元执行读出动作,得到纠错前的低位页数据rlp。低位页数据rlp是刚使用判定电平ar3和读出电压er进行了读出之后的数据,是未实施纠错的数据。

256.接着,存储控制器20从半导体存储装置10接收纠错前的低位页数据rlp。存储控制器20通过ecc电路24对纠错前的低位页数据rlp的错误进行纠正,得到纠错后的低位页数据clp(步骤s23)。

257.接着,存储控制器20将状态“c”的读出电压cr设定于半导体存储装置10。进一步,存储控制器20对半导体存储装置10指定擦除对象块blkr内的测定对象的字线wl和串单元su(步骤s24)。

258.接着,存储控制器20对半导体存储装置10命令进行状态“c”的“单电平读取”(步骤s25)。接收状态“c”的“单电平读取”的命令,定序器16例如以所设定的读出电压cr对测定对象的存储单元执行读出动作,取得状态“c”的读出结果rcr,并输出给存储控制器20。

259.存储控制器20进行对在步骤s22中得到的纠错前的低位页数据rlp实施了逻辑非运算而得到的数据rlp2与在步骤s23、s25中得到的两个数据clp、rcr的逻辑与运算,取得用于判断擦除深度的截止位数。存储控制器20将所取得的截止位数存储于存储器22内的缓冲区22a。

260.接着,存储控制器20基于写入动作后的存储单元的擦除状态,判断写入动作后的擦除对象存储单元的擦除深度。即,存储控制器20根据存储于缓冲区22a的截止位数,判断

写入动作后的擦除对象存储单元的擦除深度(步骤s26)。详细而言,存储控制器20在擦除动作后的写入动作后判断存储单元的擦除深度的情况下,执行对于测定对象的存储单元的步骤s22、s23、s25的处理。当步骤s22、s23、s25的处理达到次数x时,存储控制器20判断次数x的截止位数的平均值是否超过基准值y1(步骤s27)。在次数x的截止位数的平均值超过基准值y1的情况下(是),存储控制器20将擦除电压vera的初始电压值par提高预定值(步骤s29)。另一方面,在次数x的截止位数的平均值未超过基准值y1的情况下(否),存储控制器20结束“对擦除电压vera的初始电压值进行判断”的处理。

261.关于前述的步骤s27中的截止位数是否超过基准值y1的判断的具体例,与第1实施方式是同样的。

262.接着,对第2实施方式的擦除动作的第2例中的存储控制器20与半导体存储装置10之间的命令、地址以及数据的输入输出进行说明。

263.图30是表示第2实施方式的擦除动作的第2例中的命令序列的图。对于以下说明的从存储控制器20向半导体存储装置10的命令和地址的输出、以及存储控制器20与半导体存储装置10之间的数据的输入输出,使用i/o信号dq0~dq7来进行。图30所示的命令序列包括命令、地址、数据输入输出周期。命令由六边形表现,地址由圆角四边形(或者长圆形)表现,数据输入输出周期由四边形表现。

264.如图30所示,命令序列具有与“设定擦除电压vera的初始电压值(步骤s31)”对应的阶段p11、与“命令进行擦除动作(步骤s32)”对应的阶段p2、与“命令进行写入动作(步骤s35)”对应的阶段p5、与低位页读取的偏移读取中的“设定判定电平ar3(步骤s21)”对应的阶段p3a、与所述偏移读取中的“命令进行低位页读取(步骤s22)”对应的阶段p4a、以及与“命令进行单电平读取(步骤s25)”对应的阶段p6。此外,阶段p11与前述的图27所示的阶段p11是同样的,阶段p2、p5、p3a、p4a、p6与前述的图20所示的阶段p2、p5、p3a、p4a、p6是同样的。

265.首先,在设定擦除电压vera的初始电压值的阶段p11中,存储控制器20向半导体存储装置10依次输出指定擦除模式的命令“0xh”、地址“00h”以及数据“par”。由此,存储控制器20对半导体存储装置10指定擦除模式,并且,将在对擦除对象块blkr的擦除动作中使用的擦除电压vera的初始电压值par设定于半导体存储装置10的寄存器15d_2。

266.接着,在命令进行擦除动作的阶段p2中,存储控制器20向半导体存储装置10依次输出擦去建立命令“60h”、擦除对象块blkr的地址“add”以及擦去执行命令“d0h”。接收擦去执行命令“d0h”,半导体存储装置10的定序器16向阱布线cpwell施加初始电压值par的擦除电压vera,执行对于擦除对象块blkr的擦除动作。接着,存储控制器20向半导体存储装置10输出状态读取命令“70h”。接收状态读取命令“70h”,半导体存储装置10在此例如向存储控制器20输出表示擦除动作已通过的数据“pass”。

267.接着,在命令进行写入动作的阶段p5中,存储控制器20向半导体存储装置10依次输出写建立命令“80h”、写入对象的地址“add1~add5”、写入数据“di”以及写执行命令“10h”。接收写执行命令“10h”,半导体存储装置10的定序器16对由地址“add1~add5”指定的写入对象的存储单元执行与写入数据“di”相应的写入动作。此外,阶段p5是对于块内的特定地址的写入动作。存储控制器20也可以为了进行对块内的一部分的地址或者全部地址的写入动作而反复实施阶段p5。

268.接着,在设定判定电平ar3的阶段p3a中,存储控制器20向半导体存储装置10依次输出偏移读取命令“x2h”、表示读出电压ar的地址“01h”以及表示从读出电压ar的偏移值的数据“shift”。由此,存储控制器20将在低位页读取的偏移读取中使用的判定电平ar3设定于半导体存储装置10。

269.接着,在命令进行低位页读取的阶段p4a中,存储控制器20向半导体存储装置10依次输出表示低位页的命令“01h”、读取建立命令“00h”、测定对象的地址“add1~add5”以及读取执行命令“30h”。接收读取执行命令“30h”,半导体存储装置10的定序器16对由地址“add1~add5”指定的测定对象的存储单元,执行判定电平ar3下的读出动作和读出电压er下的读出动作。然后,定序器16向存储控制器20输出通过判定电平ar3和读出电压er下的读出动作得到的纠错前的低位页数据“rlp”。存储控制器20通过ecc电路24对所接收到的纠错前的低位页数据“rlp”进行纠错,算出纠错后的低位页数据clp。

270.接着,在命令进行单电平读取的阶段p6中,存储控制器20向半导体存储装置10依次输出单电平读取命令“x1h”、表示状态“c”的读出电压cr的地址“03h”、读取建立命令“00h”、测定对象的地址“add1~add5”以及读取执行命令“30h”。接收读取执行命令“30h”,半导体存储装置10的定序器16对由地址“add1~add5”指定的测定对象的存储单元,执行读出电压cr下的读出动作。然后,半导体存储装置10向存储控制器20输出通过读出电压cr下的读出动作得到的读出结果rcr。

271.然后,如上所述,存储控制器20进行对纠错前的低位页数据rlp实施了逻辑非运算而得到的数据rlp2与两个数据clp、rcr的逻辑与运算,算出用于判断擦除深度的截止位数。

272.在第2例中,通过写入动作后的读出动作,存储控制器20取得擦除对象块blkr内的测定对象的存储单元中的截止位数。存储控制器20基于截止位数,对擦除电压vera的初始电压值par进行更新,或者不进行更新而加以维持。

273.2.2第2实施方式的效果

274.根据第2实施方式,通过在擦除动作后或者写入动作后对第一次擦除循环中的擦除电压vera的初始电压值进行调整或者更新,能够对通过擦除动作实现的对于存储单元的擦除进行优化。换言之,通过对第一次擦除循环中的擦除电压vera的初始电压值进行调整或者更新,能够避免因擦除动作而存储单元转变为擦除不足状态或者过擦除状态。

275.通过避免因擦除动作而存储单元向过擦除状态转变,能够减少因擦除动作而产生于存储单元的损伤。进一步,通过避免因擦除动作而存储单元向擦除不足状态转变,能够减少例如包括状态a的读出的页读取中的读取错误。其他结构以及效果与第1实施方式是同样的。

276.3.第3实施方式

277.以下,对第3实施方式的存储系统1中的擦除动作进行说明。第3实施方式的存储系统1具备的结构与第1实施方式的结构是同样的。在第3实施方式中,主要对与第1实施方式以及第2实施方式不同的点进行说明。

278.3.1第3实施方式的擦除动作

279.在第3实施方式的擦除动作中,基于擦除动作后的存储单元的擦除结果,或者基于擦除动作后的写入动作后的存储单元的擦除结果,对擦除电压vera的初始电压值或者脉冲时间中的至少一个进行调整(或者变更)。在该第3实施方式中进行调整的擦除电压vera的

初始电压值是第一次擦除循环中的擦除电压vera的电压值。

280.3.1.1擦除动作的第1例

281.在第1例中,在擦除动作后,基于擦除对象块内的测定对象的字线wl和串单元su所包括的存储单元的擦除结果,对擦除电压vera的初始电压值和脉冲时间中的至少一个进行更新。在此示出如下例子:在擦除电压vera的初始电压值未超过基准值的情况下,判断是否对擦除电压vera的初始电压值进行更新,在擦除电压vera的初始电压值超过基准值的情况下,判断是否对擦除电压vera的脉冲时间进行更新。

282.图31是表示第3实施方式的存储系统1中的擦除动作的第1例的流程图。图32是表示在存储控制器20与半导体存储装置10之间进行的动作的交互的图。图33是表示在存储控制器20的存储器22内设置的脉冲时间和电压值管理表22b_3的一个例子的图。管理表22b_3对擦除电压vera的脉冲时间和初始电压值进行管理。在管理表22b_3中,按块blkr而关联有在该块blkr的擦除动作中使用的脉冲时间pdr和初始电压值par。图31所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

283.如图31和图32所示,当擦除动作开始时,首先,存储控制器20向半导体存储装置10发送管理表22b_3内的与擦除对象块blkr对应的擦除电压vera的脉冲时间pdr,使之存储于半导体存储装置10的寄存器15d_1(步骤s41)。

284.接着,存储控制器20向半导体存储装置10发送管理表22b_3内的与擦除对象块blkr对应的擦除电压vera的初始电压值par,使之存储于半导体存储装置10的寄存器15d_2(步骤s42)。

285.接着,存储控制器20对半导体存储装置10命令进行擦除动作(步骤s43)。接收擦除动作的命令,半导体存储装置10的定序器16使用存储于寄存器15d_1和15d_2的脉冲时间pdr和初始电压值par,对擦除对象块blkr执行擦除动作。

286.接着,存储控制器20判断在擦除动作中所使用了的擦除电压vera的初始电压值par是否超过基准值y(步骤s44)。在初始电压值par未超过基准值y的情况下(否),存储控制器20转变至“对擦除电压vera的初始电压值进行判断”(步骤s45)。该步骤s45的处理与前述的图23所示的步骤s33的处理是同样的。

287.接着,存储控制器20基于步骤s45的“对擦除电压vera的初始电压值进行判断”的判断结果,对存储器22的管理表22b_3内的与擦除对象块blkr对应的初始电压值par进行更新(步骤s46)。

288.另一方面,在步骤s44的判断中,在擦除电压vera的初始电压值par超过基准值y的情况下(是),存储控制器20转变至“对擦除电压vera的脉冲时间进行判断”(步骤s47)。该步骤s47的处理与前述的图8所示的步骤s3的处理是同样的。

289.接着,存储控制器20基于步骤s47的“对擦除电压vera的脉冲时间进行判断”的判断结果,对存储器22的管理表22b_3内的与擦除对象块blkr对应的脉冲时间pdr进行更新(步骤s48)。通过以上,擦除动作结束。

290.接着,对第3实施方式的擦除动作的第1例中的存储控制器20与半导体存储装置10之间的命令、地址以及数据的输入输出进行说明。

291.图34是表示第3实施方式的擦除动作的第1例中的命令序列的图。对于以下说明的从存储控制器20向半导体存储装置10的命令和地址的输出、以及存储控制器20与半导体存

储装置10之间的数据的输出,使用i/o信号dq0~dq7来进行。图34所示的命令序列包括命令、地址、数据输入输出周期。命令由六边形表现,地址由圆角四边形(或者长圆形)表现,数据输入输出周期由四边形表现。

292.如图34所示,命令序列具有与“设定擦除电压vera的脉冲时间(步骤s41)”对应的阶段p1、与“设定擦除电压vera的初始电压值(步骤s42)”对应的阶段p11、与“命令进行擦除动作(步骤s43)”对应的阶段p2、与“设定判定电平ar2(步骤s11)”对应的阶段p3以及与“命令进行单电平读取(步骤s12)”对应的阶段p4。此外,阶段p1、p11、p2、p3、p4与前述的图15和图27所示的阶段p1、p11、p2、p3、p4是同样的。

293.首先,在设定擦除电压vera的脉冲时间的阶段p1中,存储控制器20向半导体存储装置10依次输出命令“0xh”、地址“00h”以及数据“pdr”。命令“0xh”是指定擦除模式的命令。地址“00h”是设定擦除电压vera的脉冲时间的地址。数据“pdr”是表示与擦除对象块blkr对应的擦除电压vera的脉冲时间的数据。由此,存储控制器20对半导体存储装置10指定擦除模式,并且,将在对擦除对象块blkr的擦除动作中使用的擦除电压vera的脉冲时间pdr设定于半导体存储装置10的寄存器15d_1。

294.接着,在设定擦除电压vera的初始电压值的阶段p11中,存储控制器20向半导体存储装置10依次输出命令“0xh”、地址“01h”以及“par”。命令“0xh”是指定擦除模式的命令。地址“01h”是设定擦除电压vera的初始电压值的地址。数据“par”是表示与擦除对象块blkr对应的擦除电压vera的初始电压值的数据。由此,存储控制器20对半导体存储装置10指定擦除模式,并且,将在对擦除对象块blkr的擦除动作中使用的擦除电压vera的初始电压值par设定于半导体存储装置10的寄存器15d_2。

295.接着,在命令进行擦除动作的阶段p2中,存储控制器20向半导体存储装置10依次输出擦去建立命令“60h”、擦除对象块blkr的地址“add”以及擦去执行命令“d0h”。接收擦去执行命令“d0h”,半导体存储装置10的定序器16向阱布线cpwell施加脉冲时间pdr和初始电压值par的擦除电压vera,执行对于擦除对象块blkr的擦除动作。

296.然后,存储控制器20向半导体存储装置10输出状态读取命令“70h”。接收状态读取命令“70h”,半导体存储装置10在此例如向存储控制器20输出表示擦除动作已通过的数据“pass”。

297.接着,在设定判定电平ar2的阶段p3中,存储控制器20向半导体存储装置10依次输出状态“a”的单状态命令“x1h”、表示状态“a”的读出电压ar的地址“01h”、偏移读取命令“x2h”、地址“01h”以及表示从读出电压ar的偏移值的数据“shift”。由此,存储控制器20将在单电平读取的偏移读取中使用的判定电平ar2设定于半导体存储装置10。

298.接着,在命令进行读取的阶段p4中,存储控制器20向半导体存储装置10依次输出读取建立命令“00h”、地址“add1~add5”以及读取执行命令“30h”。接收读取执行命令“30h”,半导体存储装置10的定序器16对由地址“add1~add5”指定的测定对象的存储单元执行判定电平ar2下的读出动作。然后,定序器16从半导体存储装置10向存储控制器20输出在判定电平ar2下的读出动作中读出的结果ra2r。存储控制器20根据所读出的结果ra2r,对截止位数“do3”进行计数。

299.在第1例中,在擦除动作后,存储控制器20在擦除电压vera的初始电压值未超过基准值的情况下,判断是否对擦除电压vera的初始电压值进行更新,在擦除电压vera的初始

电压值超过基准值的情况下,判断是否对擦除电压vera的脉冲时间进行更新。

300.此外,在第1例中,存储控制器20首先判断擦除电压vera的初始电压值是否超过基准值,在初始电压值超过基准值的情况下,判断是否对擦除电压vera的脉冲时间进行更新,但并不限于此。也可以设为:对初始电压值和脉冲时间进行调换,先判断擦除电压vera的脉冲时间是否超过基准值,在脉冲时间超过基准值的情况下,判断是否对擦除电压vera的初始电压值进行更新。

301.3.1.2擦除动作的第2例

302.在第2例中,在擦除动作后的写入动作后,基于擦除对象块内的测定对象的字线wl和串单元su所包括的存储单元的擦除结果,对擦除电压vera的初始电压值和脉冲时间中的至少一个进行更新。在第2例中,在擦除动作与擦除电压vera的初始电压值是否超过基准值的判断之间追加有写入动作。

303.图35是表示第3实施方式的存储系统1中的擦除动作的第2例的流程图。图35所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

304.与第1例同样地,存储控制器20向半导体存储装置10发送管理表22b_3内的与擦除对象块blkr对应的擦除电压vera的脉冲时间pdr,将其设定于半导体存储装置10的寄存器15d_1(步骤s41)。

305.接着,存储控制器20向半导体存储装置10发送管理表22b_3内的与擦除对象块blkr对应的擦除电压vera的初始电压值par,将其设定于半导体存储装置10的寄存器15d_2(步骤s42)。

306.进一步,存储控制器20对半导体存储装置10命令进行擦除动作(步骤s43)。接收擦除动作的命令,半导体存储装置10的定序器16对擦除对象块blkr执行擦除动作。

307.在对擦除对象块blkr执行了擦除动作之后,存储控制器20对半导体存储装置10命令进行写入动作(步骤s49)。接收写入动作的命令,半导体存储装置10的定序器16对擦除对象块blkr内的写入对象的存储单元执行写入动作。

308.之后的步骤s44、s45、s46以及步骤s44、s47、s48的处理与图31所示的第1例是同样的。即,存储控制器20判断在擦除动作中所使用了的擦除电压vera的初始电压值par是否超过基准值y(步骤s44),在初始电压值par未超过基准值y的情况下(否),判断是否对初始电压值par进行更新(步骤s45)。按照该判断结果,存储控制器20对擦除电压vera的初始电压值par进行更新,或者不进行更新而加以维持(步骤s46)。

309.另一方面,在步骤s44中初始电压值par超过基准值y的情况下(是),存储控制器20判断是否对擦除电压vera的脉冲时间pdr进行更新(步骤s47)。按照该判断结果,存储控制器20对擦除电压vera的脉冲时间pdr进行更新,或者不进行更新而加以维持(步骤s48)。通过以上,擦除动作结束。

310.接着,对第3实施方式的擦除动作的第2例中的存储控制器20与半导体存储装置10之间的命令、地址以及数据的输入输出进行说明。

311.图36是表示第3实施方式的擦除动作的第2例中的命令序列的图。对于以下说明的从存储控制器20向半导体存储装置10的命令和地址的输出、以及存储控制器20与半导体存储装置10之间的数据的输入输出,使用i/o信号dq0~dq7来进行。图36所示的命令序列包括命令、地址、数据输入输出周期。命令由六边形表现,地址由圆角四边形(或者长圆形)表现,

数据输入输出周期由四边形表现。

312.如图36所示,命令序列具有与“设定擦除电压vera的脉冲时间(步骤s41)”对应的阶段p1、与“设定擦除电压vera的初始电压值(步骤s42)”对应的阶段p11、与“命令进行擦除动作(步骤s43)”对应的阶段p2、与“命令进行写入动作(步骤s49)”对应的阶段p5、与低位页读取的偏移读取中的“设定判定电平ar3(步骤s21)”对应的阶段p3a、与所述偏移读取中的“命令进行低位页读取(步骤s22)”对应的阶段p4a以及与“命令进行单电平读取(步骤s25)”对应的阶段p6。此外,阶段p1、p11、p2、p5、p3a、p4a、p6与前述的图15、图20以及图27所示的阶段p1、p11、p2、p5、p3a、p4a、p6是同样的。

313.与第1例同样地,首先,在设定擦除电压vera的脉冲时间的阶段p1中,存储控制器20向半导体存储装置10依次输出命令“0xh”、地址“00h”以及表示脉冲时间的数据“pdr”。由此,存储控制器20将擦除电压vera的脉冲时间pdr设定于半导体存储装置10的寄存器15d_1。

314.接着,在设定擦除电压vera的初始电压值的阶段p11中,存储控制器20向半导体存储装置10依次输出命令“0xh”、地址“01h”以及表示初始电压值的数据“par”。由此,存储控制器20将擦除电压vera的初始电压值par设定于半导体存储装置10的寄存器15d_2。

315.接着,在命令进行擦除动作的阶段p2中,存储控制器20向半导体存储装置10依次输出擦去建立命令“60h”、擦除对象块blkr的地址“add”以及擦去执行命令“d0h”。接收擦去执行命令“d0h”,半导体存储装置10的定序器16向阱布线cpwell施加脉冲时间pdr和初始电压值par的擦除电压vera,执行对于擦除对象块blkr的擦除处理。

316.然后,存储控制器20向半导体存储装置10输出状态读取命令“70h”。接收状态读取命令“70h”,半导体存储装置10在此例如向存储控制器20输出表示擦除动作已通过的数据“pass”。

317.接着,在命令进行写入动作的阶段p5中,存储控制器20向半导体存储装置10依次输出写建立命令“80h”、写入对象的地址“add1~add5”、写入数据“di”以及写执行命令“10h”。接收写执行命令“10h”,半导体存储装置10的定序器16对由地址“add1~add5”指定的写入对象的存储单元执行与写入数据“di”相应的写入动作。此外,阶段p5是对于块内的特定地址的写入动作。存储控制器20也可以为了进行对块内的一部分地址或者全部地址的写入动作而反复实施阶段p5。

318.接着,在设定判定电平ar3的阶段p3a中,存储控制器20向半导体存储装置10依次输出偏移读取命令“x2h”、表示读出电压ar的地址“01h”以及表示从读出电压ar的偏移值的数据“shift”。由此,存储控制器20将在低位页读取的偏移读取中使用的判定电平ar3设定于半导体存储装置10。

319.接着,在命令进行低位页读取的阶段p4a中,存储控制器20向半导体存储装置10依次输出表示低位页的命令“01h”、读取建立命令“00h”、测定对象的地址“add1~add5”以及读取执行命令“30h”。接收读取执行命令“30h”,半导体存储装置10的定序器16对由地址“add1~add5”指定的测定对象的存储单元执行判定电平ar3下的读出动作和状态“e”的读出电压er下的读出动作。定序器16在该读出动作的执行期间使就绪/忙信号r/bn从就绪状态转变为忙状态(r/bn=“l”)。然后,定序器16向存储控制器20输出通过判定电平ar3和读出电压er下的读出动作得到的纠错前的低位页数据rlp。存储控制器20通过ecc电路24对所

接收到的纠错前的低位页数据rlp进行纠错,算出纠错后的低位页数据clp。

320.接着,在命令进行单电平读取的阶段p6中,存储控制器20向半导体存储装置10依次输出单电平读取命令“x1h”、表示状态“c”的读出电压cr的地址“03h”、读取建立命令“00h”、测定对象的地址“add1~add5”以及读取执行命令“30h”。接收读取执行命令“30h”,半导体存储装置10的定序器16对由地址“add1~add5”指定的测定对象的存储单元,执行读出电压cr下的读出动作。定序器16在该读出动作的执行期间使就绪/忙信号r/bn从就绪状态转变为忙状态(r/bn=“l”)。然后,半导体存储装置10向存储控制器20输出通过读出电压cr下的读出动作得到的读出结果rcr。

321.然后,如上所述,存储控制器20进行对纠错前的低位页数据rlp实施了逻辑非运算而得到的数据rlp2与两个数据clp、rcr的逻辑与运算,算出用于判断擦除深度的截止位数。

322.在第2例中,在擦除动作后的写入动作后,存储控制器20在擦除电压vera的初始电压值未超过基准值的情况下,判断是否对擦除电压vera的初始电压值进行更新,在擦除电压vera的初始电压值超过基准值的情况下,判断是否对擦除电压vera的脉冲时间进行更新。

323.此外,在第2例中,存储控制器20也先判断擦除电压vera的初始电压值是否超过基准值,在初始电压值超过基准值的情况下,判断是否对擦除电压vera的脉冲时间进行更新,但并不限于此。也可以设为:将初始电压值和脉冲时间调换,先判断擦除电压vera的脉冲时间是否超过基准值,在脉冲时间超过基准值的情况下,判断是否对擦除电压vera的初始电压值进行更新。

324.3.2第3实施方式的效果

325.根据第3实施方式,通过在擦除动作后或者写入动作后,对第一次擦除循环中的擦除电压vera的初始电压值和脉冲时间中的至少一个进行调整或者更新,能够对通过擦除动作实现的对于存储单元的擦除进行优化。换言之,通过对第一次擦除循环中的擦除电压vera的初始电压值和脉冲时间中的至少一个进行调整或者更新,能够避免因擦除动作而存储单元转变为擦除不足状态或者过擦除状态。

326.通过避免因擦除动作而存储单元向过擦除状态转变,能够减少因擦除动作而产生于存储单元的损伤。进一步,通过避免因擦除动作而存储单元向擦除不足状态转变,能够减少例如包括状态a的读出的页读取中的读取错误。其他结构以及效果与第1实施方式是同样的。

327.4.第4实施方式

328.以下,对第4实施方式的存储系统1中的擦除动作进行说明。第4实施方式的存储系统1具备的结构与第1实施方式的结构是同样的。在第4实施方式中,主要对与第1实施方式不同的点进行说明。

329.4.1第4实施方式的擦除动作

330.在第4实施方式的擦除动作中,对在半导体存储装置10内判断擦除动作后的存储单元的擦除深度并向存储控制器20通知判断结果的第1例和基于以读出动作中的多个判定电平得到的擦除结果来调整擦除电压vera的脉冲时间的第2例进行说明。

331.4.1.1擦除动作的第1例

332.在第1例中,在擦除动作后,在半导体存储装置10内判断擦除对象块内的测定对象

的字线wl和串单元su所包括的存储单元的擦除深度,向存储控制器20通知判断结果。存储控制器20按照所接收到的判断结果,对擦除电压vera的脉冲时间进行更新。

333.以下,对第4实施方式的擦除动作的第1例中的存储控制器20与半导体存储装置10之间的命令、地址以及数据的输入输出进行说明。

334.图37是表示第4实施方式的擦除动作的第1例中的命令序列的图。对于以下说明的从存储控制器20向半导体存储装置10的命令和地址的输出、以及存储控制器20与半导体存储装置10之间的数据的输入输出,使用i/o信号dq0~dq7来进行。此外,在此使用在通常的擦除校验处理中准备的判定电平来作为用于取得截止位数的判定电平。图37所示的命令序列包括命令、地址、数据输入输出周期。命令由六边形表现,地址由圆角四边形(或者长圆形)表现,数据输入输出周期由四边形表现。

335.如图37所示,命令序列具有与“设定擦除电压vera的脉冲时间”对应的阶段p1、与“命令进行擦除动作”对应的阶段p21以及与“输出擦除深度(判断结果)”对应的阶段p22。

336.阶段p21包括的命令“y0h”是对半导体存储装置10命令进行擦除动作~截止位数的计数的动作的命令。命令“y0h”包括与“设定判定电平ar2(步骤s11)”对应的阶段p3、与“命令进行低位页读取(步骤s22)”对应的阶段p4或p4a以及与“命令进行单电平读取(步骤s25)”对应的阶段p6。进一步,在本实施例中包括如下处理:在半导体存储装置10中实施至此为止存储控制器20进行了处理的截止位数的计数。因此,存储控制器20对半导体存储装置10不指定这些阶段p3、p4(或者p4a)以及p6,只是指定阶段p21,就能够取得表示存储单元的擦除深度的截止位数。

337.首先,在设定擦除电压vera的脉冲时间的阶段p1中,存储控制器20向半导体存储装置10依次输出命令“0xh”、地址“00h”以及数据“pdr”。命令“0xh”是指定擦除模式的命令。地址“00h”是设定擦除电压vera的脉冲时间的地址。数据“pdr”是表示与擦除对象块blkr对应的擦除电压vera的脉冲时间的数据。由此,存储控制器20对半导体存储装置10指定擦除模式,并且,将擦除电压vera的脉冲时间pdr设定于半导体存储装置10的寄存器15d_1。

338.接着,在命令进行擦除动作的阶段p21中,存储控制器20向半导体存储装置10依次输出包括了算出擦除动作时的截止位数这一处理的擦除命令“y0h”、擦去建立命令“60h”、擦除对象块blkr的地址“add”以及擦去执行命令“d0h”。接收命令“y0h”,半导体存储装置10的定序器16执行与“设定判定电平ar2(步骤s11)”对应的阶段p3、与“命令进行低位页读取(步骤s22)”对应的阶段p4或p4a、以及与“命令进行单电平读取(步骤s25)”对应的阶段p6。然后,接收擦去执行命令“d0h”,半导体存储装置10的定序器16向阱布线cpwell施加脉冲时间pdr的擦除电压vera,执行对于擦除对象块blkr的擦除处理。

339.进一步,定序器16执行对于擦除对象块blkr的擦除校验处理,取得截止位数。即,定序器16以在擦除校验处理中使用的判定电平对擦除对象块blkr内的存储单元执行读出动作,取得截止位数。定序器16根据所取得的截止位数,判断擦除动作后的存储单元的擦除深度(即擦除不足状态、擦除适当状态或者过擦除状态)。

340.接着,存储控制器20向半导体存储装置10输出状态读取命令“70h”。接收状态读取命令“70h”,半导体存储装置10在此例如向存储控制器20输出表示擦除动作已通过的数据“pass”。

341.接着,如阶段p22所示,存储控制器20向半导体存储装置10输出用于输出表示擦除

深度的数据的状态读取命令“7xh”。接收状态读取命令“7xh”,半导体存储装置10的定序器16向存储控制器20输出表示擦除深度的数据“do5”。

342.然后,存储控制器20将表示擦除深度的数据“do5”与预先设定的阈值进行比较,根据比较结果来对擦除电压vera的脉冲时间pdr进行更新。例如,在表示擦除深度的数据“do5”为过擦除状态的情况下,存储控制器20将擦除电压vera的脉冲时间pdr缩短预定时间。另外,在表示擦除深度的数据“do5”为擦除适当状态的情况下,存储控制器20不更新擦除电压vera的脉冲时间pdr,保持不变地加以维持。在表示擦除深度的数据“do5”为擦除不足状态的情况下,存储控制器20将擦除电压vera的脉冲时间pdr增长预定时间。

343.在第1例中,在擦除动作后,基于在对于擦除对象块blkr内的存储单元的读出动作中取得的截止位数,半导体存储装置10内的定序器16判断存储单元的擦除深度,向存储控制器20通知表示擦除深度的数据。存储控制器20基于表示擦除深度的数据,对擦除电压vera的脉冲时间pdr进行更新,或者不进行更新而加以维持。

344.此外,在第1例中,存储控制器20基于表示擦除深度的数据,判断是否对擦除电压vera的脉冲时间进行更新,对脉冲时间进行了更新,但也可以代替于此,基于表示擦除深度的数据,判断是否对擦除电压vera的初始电压值进行更新,对初始电压值进行更新。

345.4.1.2擦除动作的第2例

346.在第2例中示出如下例子:在擦除动作后,基于在使用了多个判定电平的读出动作中取得的擦除结果,对擦除电压vera的脉冲时间进行更新。

347.图38是表示第4实施方式的存储系统1中的擦除动作的第2例的流程图。表示该擦除动作的第2例的流程图除了“对擦除电压vera的脉冲时间进行判断”(步骤s3b)之外,与图8所示的第1实施方式的擦除动作的第1例的流程图是同样的。以下,对图38所示的步骤s3b的“对擦除电压vera的脉冲时间进行判断”的处理进行说明。

348.图39是表示图38中的步骤s3b的“对擦除电压vera的脉冲时间进行判断”的处理的流程图。图39所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。图40是表示对于在步骤s3b的判断中使用的判定电平ar1~ar4的存储单元的阈值电压分布的图。图41是表示以判定电平ar1~ar4取得的截止位数与擦除状态的关系的图。此外,判定电平ar1~ar4的大小关系为ar4<ar3<ar2<ar1。另外,设为:在处于擦除状态的存储单元的阈值电压分布的下端存在于判定电平ar3与ar2之间的情况下,判断为擦除深度是适当的。

349.如图39所示,首先,存储控制器20将读出电压设定为状态“a”的读出电压ar,进一步,设定从读出电压ar偏移的偏移值f3。在此,将从读出电压ar偏移了偏移值f3后的读出电压定义为判定电平ar3。判定电平ar3是对擦除动作后的存储单元的擦除深度进行判断的电压电平。存储控制器20将从读出电压ar偏移了偏移值f3后的判定电平ar3(参照图40)设定于半导体存储装置10。进一步,存储控制器20对半导体存储装置10指定擦除对象块blkr内的测定对象的字线wl和串单元su(步骤s51)。

350.接着,存储控制器20对半导体存储装置10命令进行“单电平读取”(步骤s52)。接收“单电平读取”的命令,半导体存储装置10的定序器16以所设定的判定电平ar3对测定对象的存储单元执行读出动作。在该读出动作中,阈值电压比判定电平ar3高的存储单元不成为导通状态,保持截止状态不变。定序器16从半导体存储装置10向存储控制器20输出判定电平ar3下的读出结果ra3r。存储控制器20根据读出结果ra3r,对不成为导通状态而保持截止

状态不变的存储单元的数量(以下记载为第1截止位数)进行计数。存储控制器20将第1截止位数存储于存储器22内的缓冲区22a。

351.接着,存储控制器20基于判定电平ar3下的读出结果,判断擦除动作后的存储单元的擦除深度。即,基于通过判定电平ar3下的读出动作取得的第1截止位数,对擦除动作后的存储单元的擦除深度进行判断。具体而言,存储控制器20判断第1截止位数是否超过基准值y3(步骤s53)。

352.在步骤s53中,第1截止位数超过基准值y3的情况下(是),存储控制器20将读出电压设定为状态“a”的读出电压ar,进一步,设定从读出电压ar偏移的偏移值f2。在此,将从读出电压ar偏移了偏移值f2后的读出电压定义为判定电平ar2。判定电平ar2是对擦除动作后的存储单元的擦除深度进行判断的电压电平。存储控制器20将从读出电压ar偏移了偏移值f2后的判定电平ar2(参照图40)设定于半导体存储装置10。进一步,存储控制器20对半导体存储装置10指定擦除对象块blkr内的测定对象的字线wl和串单元su(步骤s54)。

353.接着,存储控制器20对半导体存储装置10命令进行状态“a”的“单电平读取”(步骤s55)。接收状态“a”的“单电平读取”的命令,半导体存储装置10的定序器16以所设定的判定电平ar2对测定对象的存储单元执行读出动作。在该读出动作中,阈值电压比判定电平ar2高的存储单元不成为导通状态,保持截止状态不变。定序器16从半导体存储装置10向存储控制器20输出判定电平ar2下的读出结果ra2r。存储控制器20根据读出结果ra2r,对不成为导通状态而保持截止状态不变的存储单元的数量(以下记载为第2截止位数)进行计数。存储控制器20将第2截止位数存储于存储器22内的缓冲区22a。

354.接着,存储控制器20基于判定电平ar2下的读出结果,判断存储单元的擦除深度。即,基于通过判定电平ar2下的读出动作取得的第2截止位数,判断存储单元的擦除深度。具体而言,存储控制器20判断第2截止位数是否超过基准值y2(步骤s56)。

355.在步骤s56中,第2截止位数未超过基准值y2的情况下(否),存储控制器20判断为存储单元的擦除深度处于擦除适当状态,结束脉冲时间的判断处理。

356.另一方面,在步骤s56中,第2截止位数超过基准值y2的情况下(是),存储控制器20将读出电压设定为状态“a”的读出电压ar,进一步,设定从读出电压ar偏移的偏移值f1。在此,将从读出电压ar偏移了偏移值f1后的读出电压定义为判定电平ar1。判定电平ar1是对擦除动作后的存储单元的擦除深度进行判断的电压电平。存储控制器20将从读出电压ar偏移了偏移值f1后的判定电平ar1(参照图40)设定于半导体存储装置10。进一步,存储控制器20对半导体存储装置10指定擦除对象块blkr内的测定对象的字线wl和串单元su(步骤s57)。

357.接着,存储控制器20对半导体存储装置10命令进行“单电平读取”(步骤s58)。接收“单电平读取”的命令,半导体存储装置10的定序器16以所设定的判定电平ar1对测定对象的存储单元执行读出动作。在该读出动作中,阈值电压比判定电平ar1高的存储单元不成为导通状态,保持截止状态不变。定序器16从半导体存储装置10向存储控制器20输出判定电平ar1下的读出结果ra1r。存储控制器20根据读出结果ra1r,对不成为导通状态而保持截止状态不变的存储单元的数量(以下记载为第3截止位数)进行计数。存储控制器20将第3截止位数存储于存储器22内的缓冲区22a。

358.接着,存储控制器20基于判定电平ar1下的读出结果,判断存储单元的擦除深度。

即,基于通过判定电平ar1下的读出动作取得的第3截止位数,判断存储单元的擦除深度。具体而言,存储控制器20判断第3截止位数是否超过基准值y1(步骤s59)。

359.在步骤s59中,第3截止位数未超过基准值y1的情况下(否),存储控制器20判断为存储单元的擦除深度处于稍稍擦除不足状态,将擦除电压vera的脉冲时间pdr增长1个步长(step)(步骤s60)。然后,结束脉冲时间的判断处理。

360.另一方面,在步骤s59中,第3截止位数超过基准值y1的情况下(是),存储控制器20判断为存储单元的擦除深度为擦除不足状态,将擦除电压vera的脉冲时间pdr增长2个步长(步骤s61)。然后,结束脉冲时间的判断处理。

361.另外,在步骤s53中,第1截止位数未超过基准值y3的情况下(否),存储控制器20将读出电压设定为状态“a”的读出电压ar,进一步设定从读出电压ar偏移的偏移值f4。在此,将从读出电压ar偏移了偏移值f4后的读出电压定义为判定电平ar4。判定电平ar4是判断擦除动作后的存储单元的擦除深度的电压电平。存储控制器20将从读出电压ar偏移了偏移值f4后的判定电平ar4(参照图40)设定于半导体存储装置10。进一步,存储控制器20对半导体存储装置10指定擦除对象块blkr内的测定对象的字线wl和串单元su(步骤s62)。

362.接着,存储控制器20对半导体存储装置10命令进行状态“a”的“单电平读取”(步骤s63)。接收状态“a”的“单电平读取”的命令,半导体存储装置10的定序器16以所设定的判定电平ar4对测定对象的存储单元执行读出动作。在该读出动作中,阈值电压比判定电平ar4高的存储单元不成为导通状态,保持截止状态不变。定序器16从半导体存储装置10向存储控制器20输出判定电平ar4下的读出结果ra4r。存储控制器20根据读出结果ra4r,对不成为导通状态而保持截止状态不变的存储单元的数量(以下记载为第4截止位数)进行计数。存储控制器20将第4截止位数存储于存储器22内的缓冲区22a。

363.接着,存储控制器20基于判定电平ar4下的读出结果,判断存储单元的擦除深度。即,基于通过判定电平ar4下的读出动作取得的第4截止位数,判断存储单元的擦除深度。具体而言,存储控制器20判断第4截止位数是否超过基准值y4(步骤s64)。

364.在步骤s64中,第4截止位数超过基准值y4的情况下(是),存储控制器20判断为存储单元的擦除深度处于稍稍过擦除状态,将擦除电压vera的脉冲时间pdr缩短1个步长(步骤s65)。然后,结束脉冲时间的判断处理。

365.另一方面,在步骤s64中,第4截止位数未超过基准值y4的情况下(否),存储控制器20判断为存储单元的擦除深度处于过擦除状态,将擦除电压vera的脉冲时间pdr缩短2个步长(步骤s66)。然后,结束脉冲时间的判断处理。

366.在第2例中,存储控制器20在擦除动作后,基于在使用了对于擦除对象块内的测定对象的存储单元的多个判定电平的读出动作中取得的截止位数,判断对于存储单元的擦除为过擦除状态、稍稍过擦除状态、擦除适当状态、稍稍擦除不足状态和擦除不足状态中的哪个状态。存储控制器20基于这些判断结果,以4个阶段的步长对擦除电压vera的脉冲时间pdr进行更新,或者不进行更新而加以维持。

367.此外,在第2例中,存储控制器20基于擦除深度的判断结果,判断是否对擦除电压vera的脉冲时间pdr进行更新,对脉冲时间pdr进行了更新,但也可以代替于此,判断是否对擦除电压vera的初始电压值par进行更新,对初始电压值par进行更新。

368.4.1.3擦除动作的第3例

369.第3例是第2例的其他技术方案。在该第3例中示出在擦除动作后基于在使用了多个判定电平的读出动作中取得的擦除结果来对擦除电压vera的脉冲时间进行更新的其他例。

370.示出擦除动作的第3例的流程图除了“对擦除电压vera的脉冲时间进行判断”(步骤s3b)以外,与图38所示的第2例的流程图是同样的。

371.以下,使用图42对与第2例不同的“对擦除电压vera的脉冲时间进行判断”的处理进行说明。图42是表示擦除动作的第3例的“对擦除电压vera的脉冲时间进行判断”的处理的流程图。图42所示的处理由存储控制器20(或者cpu21)进行命令、并进行控制。

372.如图42所示,首先,存储控制器20将读出电压设定为状态“a”的读出电压ar,进一步,设定从读出电压ar偏移的偏移值f3。在此,将从读出电压ar偏移了偏移值f3后的读出电压定义为判定电平ar3。判定电平ar3是对擦除动作后的存储单元的擦除深度进行判断的电压电平。存储控制器20将从读出电压ar偏移了偏移值f3后的判定电平ar3设定于半导体存储装置10。进一步,存储控制器20对半导体存储装置10指定擦除对象块blkr内的测定对象的字线wl和串单元su(步骤s71)。

373.接着,存储控制器20对半导体存储装置10命令进行状态“a”的“单电平读取”(步骤s72)。接收状态“a”的“单电平读取”的命令,半导体存储装置10的定序器16以所设定的判定电平ar3对测定对象的存储单元执行读出动作。定序器16从半导体存储装置10向存储控制器20输出判定电平ar3下的读出结果ra3r。存储控制器20根据读出结果ra3r,对截止状态的存储单元的数量(第1截止位数)进行计数。

374.接着,存储控制器20将读出电压设定为状态“a”的读出电压ar,进一步,设定从读出电压ar偏移的偏移值f4。在此,将从读出电压ar偏移了偏移值f4后的读出电压定义为判定电平ar4。判定电平ar4是对擦除动作后的存储单元的擦除深度进行判断的电压电平。存储控制器20将从读出电压ar偏移了偏移值f4后的判定电平ar4设定于半导体存储装置10。进一步,存储控制器20对半导体存储装置10指定擦除对象块blkr内的测定对象的字线wl和串单元su(步骤s73)。

375.接着,存储控制器20对半导体存储装置10命令进行状态“a”的“单电平读取”(步骤s74)。接收状态“a”的“单电平读取”的命令,定序器16以所设定的判定电平ar4对测定对象的存储单元执行读出动作。定序器16从半导体存储装置10向存储控制器20输出判定电平ar4下的读出结果ra4r。存储控制器20根据读出结果ra4r,对截止状态的存储单元的数量(第2截止位数)进行计数。

376.接着,存储控制器20将读出电压设定为状态“a”的读出电压ar,进一步,设定从读出电压ar偏移的偏移值f2。在此,将从读出电压ar偏移了偏移值f2后的读出电压定义为判定电平ar2。判定电平ar2是对擦除动作后的存储单元的擦除深度进行判断的电压电平。存储控制器20将从读出电压ar偏移了偏移值f2后的判定电平ar2设定于半导体存储装置10。进一步,存储控制器20对半导体存储装置10指定擦除对象块blkr内的测定对象的字线wl和串单元su(步骤s75)。

377.接着,存储控制器20对半导体存储装置10命令进行状态“a”的“单电平读取”(步骤s76)。接收状态“a”的“单电平读取”的命令,定序器16以所设定的判定电平ar2对测定对象的存储单元执行读出动作。定序器16从半导体存储装置10向存储控制器20输出判定电平

ar2下的读出结果ra2r。存储控制器20根据读出结果ra2r,对截止状态的存储单元的数量(第3截止位数)进行计数。

378.接着,存储控制器20将读出电压设定为状态“a”的读出电压ar,进一步,设定从读出电压ar偏移的偏移值f1。在此,将从读出电压ar偏移了偏移值f1后的读出电压定义为判定电平ar1。判定电平ar1是对擦除动作后的存储单元的擦除深度进行判断的电压电平。存储控制器20将从读出电压ar偏移了偏移值f1后的判定电平ar1设定于半导体存储装置10。进一步,存储控制器20对半导体存储装置10指定擦除对象块blkr内的测定对象的字线wl和串单元su(步骤s77)。

379.接着,存储控制器20对半导体存储装置10命令进行状态“a”的“单电平读取”(步骤s78)。接收状态“a”的“单电平读取”的命令,定序器16以所设定的判定电平ar1对测定对象的存储单元执行读出动作。定序器16从半导体存储装置10向存储控制器20输出判定电平ar1下的读出结果ra1r。存储控制器20根据读出结果ra1r,对截止状态的存储单元的数量(第4截止位数)进行计数。

380.接着,存储控制器20根据在读出电压ar1~ar4下的读出动作中得到的第1截止位数~第4截止位数是否超过基准值,判断存储单元的擦除深度。进一步,存储控制器20基于擦除深度的判断结果,对脉冲时间pdr进行更新(步骤s79)。通过以上,结束脉冲时间的判断处理。

381.在第3例中,与第2例同样地,存储控制器20基于在使用了多个判定电平的读出动作中得到的截止位数,判断对于存储单元的擦除处于过擦除状态、稍稍过擦除状态、擦除适当状态、稍稍擦除不足状态和擦除不足状态中的哪个状态。进一步,存储控制器20基于这些的判断结果,对擦除电压vera的脉冲时间pdr进行更新,或者不进行更新而加以维持。

382.此外,在第3例中,存储控制器20基于擦除深度的判断结果,判断是否对擦除电压vera的脉冲时间pdr进行更新,对脉冲时间pdr进行了更新,但也可以代替于此,判断是否对擦除电压vera的初始电压值par进行更新,对初始电压值par进行更新。

383.4.2第4实施方式的效果

384.根据第4实施方式,通过在擦除动作后对擦除电压vera的脉冲时间进行调整或者更新,能够对通过擦除动作实现的对存储单元的擦除进行优化。换言之,通过对擦除电压vera的脉冲时间进行调整或者更新,能够避免因擦除动作而存储单元转变为擦除不足状态或者过擦除状态。

385.通过避免因擦除动作而存储单元向过擦除状态转变,能够减少因擦除动作而产生于存储单元的损伤。进一步,通过避免因擦除动作而存储单元向擦除不足状态转变,能够减少例如包括状态a的读出的页读取中的读取错误。其他结构以及效果与第1实施方式是同样的。

386.5.其他变形例等

387.进一步,在上述实施方式中,作为半导体存储装置,以nand型闪速存储器为例来进行了说明,但不限于nand型闪速存储器,可以应用于全体的其他半导体存储装置,进一步可以应用于半导体存储装置以外的各种存储装置。另外,只要可以的话,在上述实施方式中说明过的流程图可以对其处理的顺序进行调换。

388.对本发明的几个实施方式进行了说明,但这些实施方式是作为例子提示的,并不

是意在限定发明的范围。这些实施方式能够以其他各种各样的方式来实施,能够在不脱离发明的宗旨的范围内进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围、宗旨内,同样地,包含在权利要求书记载的发明及其等同的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1