对微电子装置测试数据的编码及其相关方法、装置和系统与流程

对微电子装置测试数据的编码及其相关方法、装置和系统

1.优先权声明

2.本技术要求于2020年8月18日提交的题为“对微电子装置的测试数据进行编码以及相关方法、装置和系统(encoding test data of microelectronic devices,and related methods,devices,and systems)”的美国专利申请序列号16/996,120的提交日期的权益。

技术领域

3.本公开的实施例总体上涉及微电子装置。更具体地,各个实施例涉及对微电子装置的测试数据进行编码,并且涉及相关方法、装置和系统。

背景技术:

4.存储器装置通常以内部半导体集成电路的形式设置于计算机或其它电子系统中。有许多不同类型的存储器,包含例如随机存取存储器(ram)、只读存储器(rom)、动态随机存取存储器(dram)、同步动态随机存取存储器(sdram)、电阻式随机存取存储器(rram)、双数据速率存储器(ddr)、低功率双数据速率存储器(lpddr)、相变存储器(pcm)和闪速存储器。

5.存储器装置通常包含能够容纳代表数据位的电荷的许多存储器胞元。这些存储器胞元通常被布置成存储器阵列。可以通过经由相关联的字线驱动器选择性地激活存储器胞元来将数据写入到存储器胞元或从存储器胞元中检索数据。

技术实现要素:

6.本公开的各个实施例可以包含一种装置。所述装置可以包含:存储器阵列,所述存储器阵列包含许多列平面;以及至少一个电路,所述至少一个电路耦接到所述存储器阵列。所述至少一个电路可以被配置成接收针对存储器阵列的所述多个列平面中的每个列平面的列地址的测试结果数据。所述至少一个电路还可以被配置成响应于所述多个列平面的多个位中的仅一个位未通过针对所述列地址的测试而将所述测试结果数据转换为第一结果,其中所述第一结果标识所述一个位和所述多个列平面中的包含所述一个位的列平面。此外,所述至少一个电路可以被配置成响应于仅一个列平面未通过针对所述列地址的所述测试并且所述一个列平面的多于一个位有缺陷而将所述测试结果数据转换为第二结果,其中所述第二结果标识所述一个列平面。

7.根据本公开的另一个实施例,测试存储器装置的方法可以包含测试存储器阵列的多个列平面的列地址。所述方法还可以包含测试存储器阵列的多个列平面的列地址。所述方法可以进一步包含响应于所述多个列平面的仅一个位未通过针对所述列地址的测试而生成第一信号,其中所述第一信号标识所述一个位和所述多个列平面中的包含所述一个位的列平面。此外,所述方法可以包含响应于所述多个列平面中的仅一个列平面未通过针对所述列地址的测试并且所述一个列平面的多于一个位未通过针对所述列地址的测试而生成第二信号,其中所述第二信号标识所述一个列平面。

8.根据本公开的另一个实施例,装置可以包含存储器阵列,所述存储器阵列包含多个列平面。所述装置还可以包含耦接到所述存储器阵列的至少一个电路。所述至少一个电路可以被配置成测试所述存储器阵列的所述多个列平面的列地址,其中所述多个列平面包含第一组列平面和第二组列平面,并且所述第一组列平面和所述第二组列平面共同包含多个位。所述至少一个电路还可以被配置成响应于所述多个位中的每个位针对所述列地址具有非缺陷状态而生成第一信号。进一步地,所述至少一个电路可以被配置成响应于所述多个位中的仅一个位针对所述列地址具有缺陷状态而生成第二信号,其中所述第二信号标识所述一个位的地址。此外,所述至少一个电路可以被配置成响应于所述多个位中的两个或两个以上位针对所述列地址具有缺陷状态而生成第三信号。

9.本公开的另外的实施例包含一种系统。所述系统可以包含至少一个输入装置、至少一个输出装置和至少一个处理器装置,所述至少一个处理器装置可操作地耦接到所述输入装置和所述输出装置。所述系统还可以包含至少一个存储器装置,所述至少一个存储器装置可操作地耦接到所述至少一个处理器装置并且包括电路系统。所述电路系统可以被配置成将数据写入所述至少一个存储器装置的n个列平面中的每个列平面,并且从所述n个列平面中的每个列平面读取数据。所述电路系统还可以被配置成将写入数据与读取数据进行比较以生成n位测试数据。所述电路系统可以被配置成响应于所述n个列平面的多个位中的单个位有缺陷而将所述n位测试数据转换为第一m位结果,其中所述第一m位结果标识所述单个位和所述n个列平面中的包含所述单个位的列平面。进一步地,所述电路系统可以被配置成响应于所述n个列平面中的仅一个列平面有缺陷并且所述一个列平面的两个或两个以上位有缺陷而将所述n位测试数据转换为不同的第二m位结果,其中所述不同的第二m位结果标识所述一个列平面。

附图说明

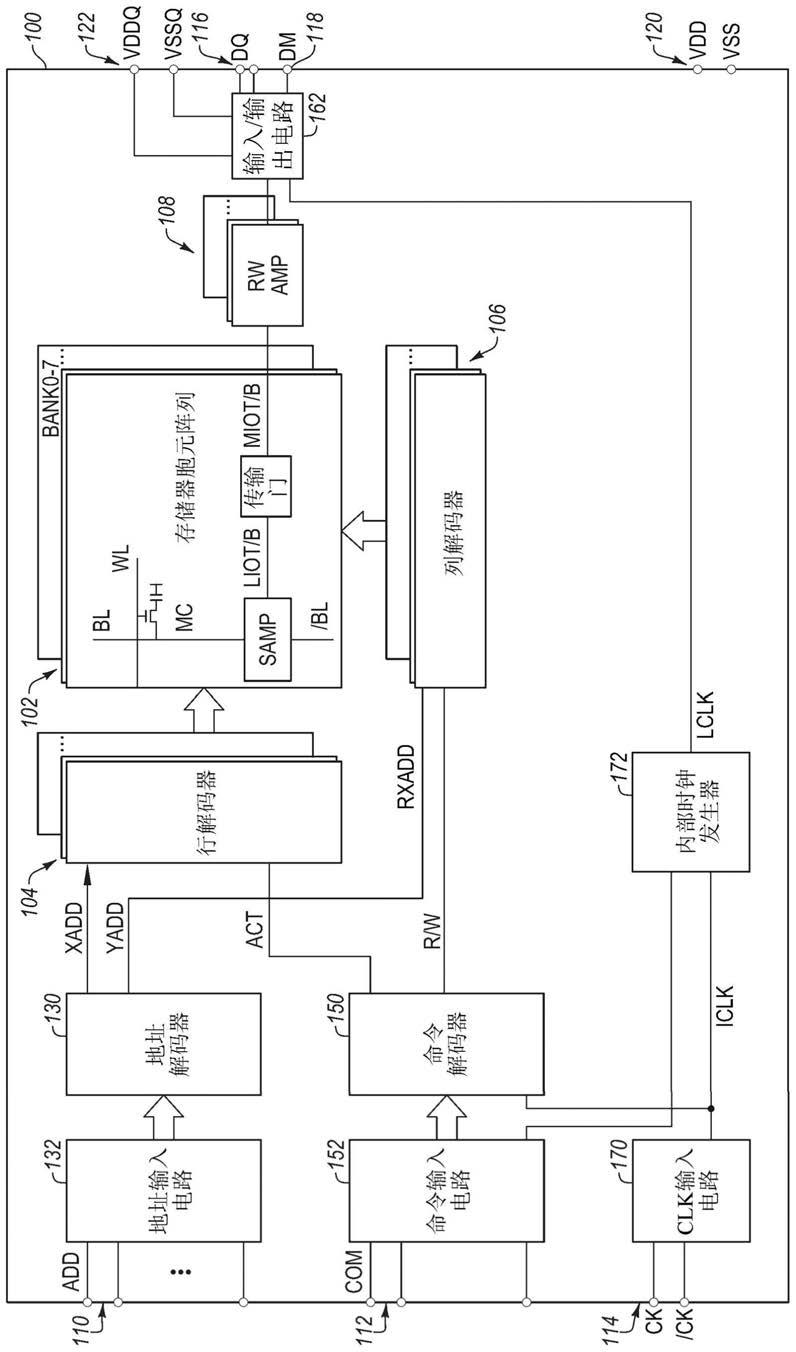

10.图1是根据本公开的至少一个实施例的示例存储器装置的框图。

11.图2描绘了包含存储器阵列的一部分的示例存储器装置。

12.图3描绘了示例存储器阵列的多个元件。

13.图4a描绘了根据本公开的各个实施例的包含耦接到总线的多个元件的示例存储器装置。

14.图4b描绘了根据本公开的各个实施例的包含耦接到编码器的多个元件的示例存储器装置。

15.图5是根据本公开的各个实施例的示例存储器阵列的多个元件的另一个图示。

16.图6是根据本公开的各个实施例的测试存储器装置的示例方法的流程图。

17.图7是根据本公开的各个实施例的测试存储器装置的另一个示例方法的流程图。

18.图8是根据本公开的各个实施例的存储器系统的简化框图。

19.图9是根据本公开的各个实施例的电子系统的简化框图。

具体实施方式

20.半导体存储器装置通常包含存储器胞元阵列。阵列中的存储器胞元借助于输入到存储器装置的行地址信号和列地址信号被选择用于读取和写入。行地址信号和列地址信号

由地址解码电路系统处理,以选择阵列中的行线路和列线路以存取期望的一或多个存储器胞元。

21.当制造半导体装置时,存储器阵列或子阵列中可能出现缺陷的存储器胞元。尽管存在这些缺陷的存储器胞元,但为了补救半导体存储器装置,并且因此提高制造过程中的总产率,通常实施冗余。冗余存储器胞元定位于存储器阵列中,并且存储器阵列可以与多个冗余存储器胞元相关联。当在阵列中检测到缺陷的存储器胞元时,可以(例如,通过熔丝、反熔丝或其它编程技术)对与冗余存储器胞元相关联的冗余解码电路系统进行编程以响应于缺陷的存储器胞元的地址。当选择缺陷的存储器胞元的地址进行存取时,可以存取冗余存储器胞元(例如,从所述冗余存储器胞元读取或写入到所述冗余存储器胞元),而不是存取缺陷的存储器胞元。

22.如在于2020年2月5日提交的题为“微电子装置测试以及相关联的方法、装置和系统(microelectronic device testing,and associated methods,devices,and systems)”的美国专利申请第16/782,949号和于2019年11月15日提交的题为“用于对列平面压缩数据进行编码的设备和方法(apparatuses and methods to encode column plane compression data)”的美国专利申请第16/685,186号中公开的,经编码列平面压缩系统被配置成在读取突发期间对列平面信息进行编码并输出经编码数据。进一步地,应当理解,一些半导体存储器装置可以包含错误检测和/或纠错码(ecc)以纠正错误(例如,单个位错误)。如果使用ecc(即纠正单个位),则可能需要完全可见性(即1x可见性)来标识哪些具体位失效。如将理解的,如果单个位在ecc字上失效(即在整个测试流程中在所述相同字上不存在其它失效),并且单个位可以被标识,则可以容忍所述单个位。换句话说,可能不需要修复所述单个位,而是可以通过ecc来纠正所述单个位。然而,如将理解的,处理完全可见性数据(包含将完全可见性数据从存储器装置传输到测试装置)需要大量资源和时间。

23.如下文更全面地描述的,本文公开的各个实施例涉及微电子装置测试,包含在微电子装置处对测试数据进行编码。根据各个实施例,可以生成经编码完全可见性数据(即经编码1x数据),其可以使测试者能够记录单个位(例如,用于单个位容忍)。更具体地说,各个实施例涉及测试存储器装置、标识缺陷的列平面和/或存储器装置的位(如果有的话)、对测试数据进行编码以及可能标识存储器装置失效(例如,如果对于具体列平面地址有多于一个列平面失效的话)。进一步地,在各个实施例中,可以提供经编码完全可见性数据(例如,用于跟踪碰撞位的1x可见性)以确定哪个具体位失效,使得可以使用错误ecc(即容忍单个位)。与常规装置、系统和方法相比,各个实施例可以减少测试时间和(例如,在存储器装置内或存储器装置的外部)传输到测试电路的数据量。进一步地,各个实施例可以通过利用ecc纠正能力来提高存储装置产率和质量。

24.尽管本文参考存储器装置描述了各个实施例,但本公开并不局限于此,并且实施例可以总体上适用于可以包含或可以不包含半导体装置和/或存储器装置的微电子装置。现在将参考附图来解释本公开的实施例。

25.图1包含根据本公开的各个实施例的示例存储器装置100的框图。在本文中被称为或可以被称为存储器装置的存储器装置100可以包含例如dram(动态随机存取存储器)、sram(静态随机存取存储器)、sdram(同步动态随机存取存储器)、ddr sdram(双倍数据速率dram,如ddr4 sdram等等)或sgram(同步图形随机存取存储器)。可以集成在半导体芯片上

的存储器装置100可以包含存储器胞元阵列102。

26.在图1的实施例中,存储器胞元阵列102被示出为包含八个存储器库bank0-7。可以在其它实施例的存储器胞元阵列102中包含更多或更少的库。每个存储器库包含多条存取线(字线wl)、多条数据线(位线bl)和/bl,以及布置在所述多条字线wl和所述多条位线bl和/bl的交叉点处的多个存储器胞元mc。对字线wl的选择可以由行解码器104执行,并且对位线bl和/bl的选择可以由列解码器106执行。在图1的实施例中,行解码器104可以包含用于每个存储器库bank0-7的相应的行解码器,并且列解码器106可以包含用于每个存储器库bank0-7的相应的列解码器。

27.位线bl和/bl耦接到相应的读出放大器samp。来自位线bl或/bl的读取数据可以通过读出放大器samp放大,并且通过互补的局部数据线(liot/b)、传输门(tg)和互补的主数据线(miot/b)传输到读取/写入放大器108。相反地,从读取/写入放大器108输出的写入数据可以通过互补的主数据线miot/b、传输门tg和互补的局部数据线liot/b传输到读出放大器samp,并且写入耦接到位线bl或/bl的存储器胞元mc中。

28.存储器装置100通常可以被配置成通过如地址端子110、命令端子112、时钟端子114、数据端子116和数据屏蔽端子118等各种端子(例如,从外部控制器)接收各种输入。存储器装置100可以包含另外的端子,如电源端子120和122。

29.在考虑的操作期间,通过命令端子112接收的一或多个命令信号com可以通过命令输入电路152传送到命令解码器150。命令解码器150可以包含被配置成通过对一或多个命令信号com进行解码来生成各种内部命令的电路。内部命令的实例包含有效命令act和读取/写入信号r/w。

30.进一步地,通过地址端子110接收的一或多个地址信号add可以通过地址输入电路132传送到地址解码器130。地址解码器130可以被配置成将行地址xadd供应到行解码器104并且将列地址yadd供应到列解码器106。尽管命令输入电路152和地址输入电路132被展示为单独的电路,但是在一些实施例中,地址信号和命令信号可以通过公共电路接收。

31.有效命令act可以包含响应于命令信号com指示行存取(例如,有效命令)而被激活的脉冲信号。响应于有效信号act,可以激活指定库地址的行解码器104。因此,可以选择并且激活由行地址xadd指定的字线wl。

32.读取/写入信号r/w可以包含响应于命令信号com指示列存取(例如,读取命令或写入命令)而被激活的脉冲信号。响应于读取/写入信号r/w,可以激活列解码器106,并且可以选择由列地址yadd指定的位线bl。

33.响应于有效命令act、读取信号、行地址xadd和列地址yadd,可以从由行地址xadd和列地址yadd指定的存储器胞元mc读取数据。读取数据可以通过读出放大器samp、传输门tg、读取/写入放大器108、输入/输出电路162和数据端子116输出。进一步地,响应于有效命令act、写入信号、行地址xadd和列地址yadd,可以通过数据端子116、输入/输出电路162、读取/写入放大器108、传输门tg和读出放大器samp将写入数据供应到存储器胞元阵列102。可以将写入数据写入由行地址xadd和列地址yadd指定的存储器胞元mc。

34.时钟信号ck和/ck可以通过时钟端子114接收。时钟输入电路170可以基于时钟信号ck和/ck生成内部时钟信号iclk。内部时钟信号iclk可以传送到存储器装置100的各个组件,如命令解码器150和内部时钟发生器172。内部时钟发生器172可以生成可以传送到输

入/输出电路162(例如,以用于控制输入/输出电路162的操作定时)的内部时钟信号lclk。进一步地,数据屏蔽端子118可以接收一或多个数据屏蔽信号dm。当激活数据屏蔽信号dm时,可以禁止重写对应的数据。

35.根据各个实施例,输入/输出电路162可以包含或可以耦接到一或多个编码器,如下文更全面描述的,所述一或多个编码器可以被配置成从存储器胞元阵列102接收测试数据并且响应于此而生成指示一或多个列平面是否有缺陷、缺陷的列平面的地址和/或列平面的哪一位有缺陷(例如,如果仅一个列平面有缺陷并且所述有缺陷的列平面的仅一个位有缺陷的话)的一或多个信号(例如,经编码信号)。

36.如本领域的普通技术人员将理解的,“存储器垫(memory mat)”通常是指具有多个存储器胞元的存储器库的子单元。每个存储器垫被定义为字线wl和位线bl延伸的范围。存储器垫可以包含两个或两个以上子垫。子垫在本文中也可以被称为“列平面”。

37.图2描绘了包含存储器阵列200的一部分的示例装置。存储器阵列200包含存储器胞元的组(例如,在本文中也称为“行”)202,其中每个组202包含多个存储器垫204。如将理解的,每个存储器垫204可以包含多个(例如,两个)列平面。换句话说,每个存储器垫204可以包含多个(例如,两个)子垫。进一步地,每个列平面包含多条列选择(cs)线206,以用于存取位于每个列平面内在列地址处的存储器胞元。仅举例来说,每个列平面可以包含64条cs线。例如,一或多个读出放大器(图2中未描绘)可以定位于行202的相邻存储器垫之间。进一步地,例如,一或多个子字线驱动器(图2中未描绘)可以定位在不同行202的相邻存储器垫之间。

38.此外,每一行202包含可通过冗余列选择(rcs)线存取的多个冗余存储器胞元。例如,如果可通过行202的列平面的列选择线x存取的一或多个存储器胞元失效,则可以将可通过列选择行x存取的所述一或多个存储器胞元替代为可通过冗余列平面208的列选择地址x存取的一或多个存储器胞元。类似地,如果可通过行202的列平面的列选择线y存取的一或多个存储器胞元失效,则可以将可通过列平面的列选择线y存取的所述一或多个存储器胞元替代为可通过冗余列平面208的列选择地址y存取的一或多个存储器胞元。

39.如将理解的,在常规装置中,如果可通过行202的单个列平面的不同cs行存取的存储器胞元失效,则可以通过冗余列平面208的相关联的列选择线来替代单个列平面的不同cs行。进一步地,如果可通过列平面的第一列选择线(例如,cs线a)存取的存储器胞元失效,并且可通过第二(即,不同的)列平面的第二(即,不同的)列选择线(例如,cs线b)可存取的存储器胞元失效,则可以通过冗余列平面208的相关联的列选择线(例如,cs线a)来替代列平面的第一列选择线(例如,cs线a),并且可以通过冗余列平面208的相关联的列选择线(例如,cs线b)来替代第二列平面的第二列选择线(例如,cs线b)。更具体地,如果可通过列平面220a的列选择线61(cs61)存取的一或多个存储器胞元失效,并且可通过第二(即,不同的)列平面220b的列选择线50(cs50)存取的一或多个存储器胞元失效,则可以通过冗余列平面208的列选择线61(rcs61)替代列平面220a的列选择线61(cs61),并且可以通过冗余列平面208的列选择线50(rcs50)替代列平面220b的列选择线50(cs50)。

40.然而,在常规装置中,可能无法替换对应于相同列地址的多于一条列选择线(即,在不同的存储器列平面中)。例如,如果对应于同一列地址的两列失效,则可能无法替代两列。更具体地,如果可通过第一列平面的第一列选择线(例如,cs线a)存取的一或多个存储

器胞元失效,并且可通过第二(即,不同的)列平面的同一列选择线(例如,cs线a)存取的一或多个存储器胞元失效,则仅可以替代列选择线之一。换言之,如果可通过列平面220a的cs61存取的一或多个存储器胞元失效,并且可通过列平面220b的cs61存取的存储器胞元失效,则可能无法替代两条列选择线(即列平面220a中的cs61和列平面220b中的cs61)。

41.图3展示了示例存储器阵列300的多个元件。更具体地,存储器阵列300包含元件304组(例如,“行”)302。在一些实施例中,每个元件304可以包含列平面。在其它实施例中,每个元件304可以包含具有两(2)个列平面(即,两个子垫)的存储器垫。在常规系统和/或装置中,行302中的每个列平面被顺序地(即,一个接一个地)测试以检测失效的列平面(如果有的话)。更具体地,在测试期间,对于每个列地址,(例如,顺序地)生成针对每个列平面的一个位,并且基于所生成的(例如,从列平面输出的)位,可以确定对于具体列地址,列平面是否有缺陷(即列平面是否包含一或多个缺陷的存储器胞元)。如将理解的,在至少一些实例中,为了针对具体列地址测试行中的每个列平面(例如但不限于,17个列平面、35个列平面),从所述行读出n个位数据(例如,针对17个列平面的17*8个位数据或针对35个列平面的35*8个位)。因此,应当理解,用于检测缺陷的列平面的常规系统和方法是耗时的并且是资源密集型的。

42.如美国专利申请第16/782,949号和美国专利申请第16/685,186号中所公开的,(即通过经编码列平面压缩生成的)列平面代码可以包含用于针对多个列平面的多个经编码位(例如,针对17个列平面的5个经编码位或针对35个列平面的6个经编码位)。如下文将更全面地公开,根据各个实施例,经编码数据可以包含在读取突发中的另外多个位(例如,4个位)以指示列平面中的哪个具体位失效(例如,如果仅列平面失效并且列平面中的仅一个位失效)。如将理解的,另外的位可以允许用于全局列压缩的足够可见性以及ecc碰撞可见性。更具体地,例如,另外的位可以包含针对经编码1x数据的四个另外的位,或者另外的位可以包含针对xored 2x数据的三个另外的位(例如,通过盲比较)。尽管另外的位可以增加测试时间和/或测试数据量(即与经编码列平面压缩相比),但是与常规1x测试相比,各个实施例可以缩短测试时间和测试数据量。例如,代替包含针对17个列平面的136个位的读取突发(即1x可见性),根据各个实施例,读取突发可以包含针对17个列平面的9个位。作为另一个实例,代替包含针对35个列平面的280个位的读取突发(即1x可见性),根据各个实施例,读取突发可以包含针对35个列平面的10个位。

43.图4a展示了根据本公开的各个实施例的包含元件404组(例如“行”)402的装置400a。装置400a可以包含存储器装置(如图1的存储器装置100)和/或可以是存储器装置的一部分。例如,行402可以是存储器库(例如,图1所示的八个存储器库bank0-7之一)的一部分。在一些实施例中,每个元件404可以包含列平面。在其它实施例中,每个元件404可以包含具有两个列平面(即,两个子垫)的存储器垫。

44.在测试操作期间,对于具体列地址,可以通过总线403将多个位(例如,8个位)写入行402的每个列平面。因此,在包含35个列平面的实例中,可以将280个位(即35*8)写入行402。进一步地,可以从行402的每个列平面读取多个位(例如,8个位)。因此,在此实例中,可以从行402读取280个位(即35*8)。进一步地,可以将写入行402的每个列平面的位与从每个列平面读取的位进行比较以检测针对具体列地址的缺陷的列平面(如果有的话)。

45.图4b描绘了根据本公开的各个实施例的包含耦接到编码器406的元件404的装置

400b。在一些实施例中,元件404可以是存储器阵列401的一部分,所述部分可以是存储器库(例如,图1所示的八个存储器库bank0-7之一)的一部分。作为非限制性实例,编码器406可以定位于存储器装置(例如,图1的存储器装置100)的外周电路区域内。进一步地,在一些实例中,许多数据放大器(图4中未示出)可以定位于存储器阵列(例如,包含行402)与编码器406之间。例如,编码器406可以是输入/输出电路(如图1的存储器装置100的输入/输出电路162)的一部分或可以耦接到所述输入/输出电路。

46.编码器406耦接到并且被配置成从行402的每个元件404接收数据。更具体地,可以包含一或多个电路的编码器406被配置成从行402接收(例如,基本上同时接收)第一多个位(例如,n个位)、对所述第一多个位进行编码(例如,基本上同时编码)以及输出(例如,基本上同时输出)第二多个位(例如,m个位),其中所述第二多个位小于所述第一多个位(例如,m《n)。

47.如上所述,在考虑的测试操作期间,对于具体列地址,可以将多个位(例如,8个位)写入行402中的每个列平面。更具体地,在一个实例中,可以将各自具有高状态(例如,1)的8个位写入针对行402中的每个列平面的具体列地址。随后,可以针对行402中的每个列平面从具体列地址读取8个位,并且可以将读取的位与写入的位进行比较(即,检测缺陷的列平面并生成m位结果)。

48.作为更具体的实例,编码器406被配置成从行402中的每个列平面接收8个位(例如,280个位(即,35列平面*8个位)或136个位(即,17列平面*8个位))并且输出m个位(例如,m位经编码数据)。例如,如果行402包含17个列平面,则m可能等于9。作为另一个实例,如果行402包含35个列平面,则m可能等于10。

49.又更具体地,在行402的考虑的测试操作期间,对于每个列地址,行402中的每个列平面可以生成8个位,并且因此在包含35个列平面(即,17.5个存储器垫)的一个实例中,在编码器406处生成并且接收(例如,同时接收)280(即,35*8)个位。作为非限制性实例,如果通过列平面生成的每个位具有第一状态(例如,“0”),则列平面“通过”测试(即,列平面不包含任何缺陷的存储器胞元),并且如果列平面生成一或多个具有第二状态(例如,“1”)的位,则列平面“未通过”测试(即,列平面包含一或多个缺陷的存储器胞元)。

50.继续考虑的测试操作,如果对于具体列地址,多于一个列平面生成具有第二状态的位(即,多于一个列平面未通过测试),则编码器406生成指示多于一个列平面已失效的m位输出。更具体地,例如,如果对于具体列地址,多于一个列平面生成具有第二状态的位(即,多于一个列平面未通过测试),则编码器406可以生成指示多于一个列平面未通过测试的m位输出(本文也称为“结果”或“信号”),如“110xxxxxxx”。

51.进一步地,如果由每个列平面生成的每个位具有第一状态(即,每个列平面通过测试),则编码器406生成指示每个列平面通过测试的m位输出。更具体地,例如,如果由行402的每个列平面生成的每个位具有第一状态(即,每个列平面通过测试),则编码器406可以生成指示没有列平面未通过测试的m位输出,如“111xxxxxx”。

52.此外,如果多于一个位失效(即,多位失效(multi-bit failure)),则失效位可能不被容忍,并且可以生成单独的代码以指示多位失效。更具体地,如果对于具体列地址,仅一个列平面未通过测试并且列平面的多于一个位具有第二状态(即,一个列平面的两个或两个以上位有缺陷),则编码器406生成指示以下的m位输出:1)哪个具体列平面未通过测

试;和2)多位失效。更具体地,如果仅一个列平面未通过测试并且列平面的多于一个位未通过测试,则编码器406可以生成m位值,其中m位值的一些位标识失效的列平面,并且至少另一个位指示多位失效。

53.作为更具体的实例,如果列平面0(例如,行402中的第一列平面)是行402中用于生成具有第二状态(即,“1”)的位的唯一列平面,并且列平面0的多于一个位具有第二状态,则编码器406生成“0000001xxx”(即,000000是用于标识列平面0的“0”的二进制值,并且第三位(即,“1”)表示多位失效)。作为另一个实例,如果列平面9(例如,行402中的第十列平面)是行402中用于生成具有第二状态(即,“1”)的位的唯一列平面,并且列平面9的多于一个位具有第二状态,则编码器406生成“0010011xxx”(即,001001是用于标识列平面9的“9”的二进制值,并且第三位(即,“1”)表示多位失效)。作为又另一个实例,如果列平面33(例如,行402中的第34列平面)是行402中用于生成具有第二状态(即,“1”)的位的唯一列平面,并且列平面33的多于一个位具有第二状态,则编码器406生成“1000011xxx”(即,100001是用于标识列平面33的“33”的二进制值,并且第三位(即,“1”)表示多位失效)。进一步地,在此实例中,m位值(例如,介于“0000001xxx”与“1000101xxx”之间)(即,其标识哪个列平面未通过测试)和具体列地址可以用于修复过程中(例如,用于修复失效的列平面中的列选择线)。

54.此外,根据一些实施例,如果多个列平面的多个位中仅单个位未通过测试(例如,行402中的仅单个位未通过测试),则m位值可以指示哪个具体位失效。更具体地,如果对于具体列地址,仅一个列平面未通过测试,并且列平面的仅一个位有缺陷,则编码器406生成指示哪一个具体列平面未通过测试以及一个列平面的哪一个具体位未通过测试的m位输出。更具体地,如果一个列平面未通过测试并且列平面的仅一个位失效,则编码器406可以生成m位值,其中m位值的一些位标识失效的列平面,并且m位值的一些位标识列平面的哪个位失效。

55.在包含35个列平面的更具体的实例中,m位值的6个位(例如,介于“000000”与“100010”之间(即,在0-34之间))可以指示哪个列平面(例如,列平面的地址)未通过测试。在包含17个列平面的另一个实例中,m位值的5个位(例如,介于“000000”与“10000”之间(即,在0-16之间))可以指示哪个列平面(例如,列平面的地址)未通过测试。进一步地,在任一实例中,m位值的另外多个位(例如,4个位)可以指示列平面的哪一位失效。

56.例如,如果列平面0(例如,行402中的第一列平面)是行402中用于生成具有第二状态的位(即,“1”)的唯一列平面,并且位7是列平面0的失效的一个位,则编码器406可以生成“0000000111”(即,000000是用于标识列平面0的“0”的二进制值,并且0111是用于标识位7的“7”的二进制值)。作为另一个实例,如果列平面9(例如,行402中的第十列平面)是行402中用于生成具有第二状态的位(即,“1”)的唯一列平面,并且位6是列平面9的失效的一个位,则编码器406可以生成“0010010110”(即,001001是用于标识列平面9的“9”的二进制值,并且0110是用于标识位6的“6”的二进制值)。作为又另一个实例,如果列平面33(例如,行402中的第34列平面)是行402中用于生成具有第二状态的位(即,“1”)的唯一列平面,并且位1是列平面33的失效的一个位,则编码器406可以生成“1000010001”(即,100001是用于标识列平面33的“33”的二进制值,并且0001是用于标识位1的“1”的二进制值)。进一步地,在此实例中,m位值(即,标识哪个列平面未通过测试并且哪个位未通过测试)和具体列地址可以用于错误容忍(例如,通过ecc)和/或修复过程(例如,用于修复失效的列平面中的列选择

线)。

57.图5是根据本公开的各个实施例的包含元件504组(例如,“行”)502的存储器阵列500的另一个图示。例如,图4的行402可以包含行502。在此实例中,每个元件504包含多个列平面505(例如,其中的一个或两个)。进一步地,行502包含纠错码(ecc)单元506和冗余单元508。每个列平面505、每个ecc单元506和冗余单元508被配置成输出多个位(例如,k位(例如,8个位))。如将理解的,ecc单元506可以用于纠正与行相关联的错误,并且冗余单元508可以包含冗余存储器胞元。作为更具体的实例,ecc单元506可以用于容忍行中的失效位(例如,如果仅一个位失效的话)

58.例如,行502中的每个列平面505可以耦接到输入/输出(i/o)电路系统(例如,图1的i/o电路162),如输入/输出(dq)焊盘(本文也称为“数据焊盘”)。因此,在一些实例中,行502中的每个列平面505可以被配置成针对一个列操作读取或写入2*k个位(例如,2*8个位)。

59.图6是根据本公开的各个实施例的测试存储器装置的示例方法600的流程图。方法600可以根据本公开中描述的至少一个实施例布置。在一些实施例中,方法600可以由如图1的存储器装置100、图4a的装置400a、图4b的装置400b、图5的存储器阵列500、图8的存储器系统800和/或图9的电子系统900等装置或系统或另一个装置或系统执行。尽管被展示为离散的框,但是根据期望的实施方案,各个框可以被划分为另外的框、被组合为更少的框或被消除。

60.方法600可以开始于框602,其中可以测试存储器装置的多个列平面的列地址,并且方法600可以进行到框604。例如,对于多个列地址中的第一列地址,可以(例如,通过图4a的总线403)写入所述多个列平面。进一步地,可以从所述多个列平面读取数据,并且可以(例如,通过图4b的编码器406)将写入数据与读取数据进行比较,以确定所述多个列平面中的每个列平面和/或所述多个列平面的每个位的状态(例如,缺陷或非缺陷)。

61.在框604处,可以响应于所述多个列平面的仅一个位未通过针对列地址的测试而生成第一信号,并且方法600可以进行到框606。第一信号可以标识所述一个位和所述多个列平面中的包含所述一个位的列平面。例如,如果唯一位被确定为有缺陷(例如,基于在框602处执行的测试),则装置(例如,图4b的编码器406)可以生成标识缺陷的所述一个位和包含缺陷位的一个列平面的m位信号。更具体地,例如,如果列平面25是唯一具有缺陷状态的列平面,并且列平面25的第五位是未通过测试的唯一位,则装置可以生成“0110010101”,其中011011是“25”的二进制值,并且0101是“5”的二进制值。

62.在框606处,可以响应于所述多个列平面中的仅一个列平面未通过针对列地址的测试并且所述一个列平面的多于一个位具有缺陷状态而生成第二信号,其中第二信号标识所述一个列平面。例如,如果仅一个列平面被确定为有缺陷,但所述一个列平面的多于一个位有缺陷(例如,基于在框602处执行的测试),则装置(例如,图4b的编码器406)可以生成标识有缺陷和多位失效的所述一个列平面的m位信号。更具体地,例如,如果列平面25是唯一具有缺陷状态的列平面并且列平面25的多于一个位未通过测试,则装置可以生成“0110011xxx”,其中011011是“25”的二进制值,并且第三位“1”指示多位失效。

63.在不脱离本公开的范围的情况下,可以对方法600进行修改、添加或省略。例如,可以以不同的顺序来实施方法600的操作。例如,在框606处的动作可以发生在框604处的动作

之前。进一步地,所概述的操作和动作仅作为实例提供,并且在不背离所公开的实施例的本质的情况下,所述操作和动作中的一些操作和动作可以是任选的、组合成更少的操作和动作或者扩展成另外的操作和动作。例如,一种方法可以包含一或多个动作,其中可以生成针对所述多个列平面中的每个列平面的测试数据,包括一个位(例如,指示有缺陷或非缺陷状态)。进一步地,例如,一种方法可以包含一或多个动作,其中可以响应于所述多个列平面中的每个列平面针对列地址具有非缺陷状态而生成第三信号。此外,例如,一种方法可以包含一或多个动作,其中可以响应于所述多个列平面中的两个或两个以上列平面针对列地址具有缺陷状态而生成第四信号。作为另一个实例,一种方法可以包含一或多个动作,其中可以将第一信号、第二信号、第三信号和/或第四信号传送到测试/修复电路系统(例如,在存储器装置上或存储器装置的外部)。进一步地,例如,一种方法可以包含一或多个动作,其中可以通过存储器装置的ecc来容忍一个有缺陷的位。另外,例如,一种方法可以包含一或多个动作,其中列平面的一或多个列选择线可以被存储器装置的冗余列平面的冗余列线替代。

64.如将理解的,一些存储器装置可以不被配置成执行经过编码的列平面压缩。在这些情况下,为了提供例如17个列平面的完全可见性,需要8个位来标识136个位(即,17*8=136)中的哪一或多个位失效。在这些常规实例中,可以在读取突发中读出两组列平面,并且因此在此实例中,单个读取的读取突发是16个位(2*8)。

65.根据本公开的一些实施例,可以一起(例如,基本上同时)测试多于一组(“组”)的列平面。更具体地,例如,可以(例如,甚至在没有经过编码的列平面压缩的情况下)一起测试34个列平面(例如,两组17个列平面)(即,以提供经过编码的1x数据可见性(例如,针对单个位容忍))。

66.下面的表1展示了用于两组列平面(即两组17个列平面)的示例场景的示例位值。如表1所示,9个位可以用于标识“无失效”场景和单个位失效(即,从位0到位271)。根据各个实施例,可以通过ecc容忍单个位失效。进一步地,继续参考表1,可以使用9个位来标识第一组列平面的多位失效(即“110000001”)和第一组列平面的多位失效(即,“110000010”)。此外,可以使用9个位来标识两组列平面的多位失效(即,“110000011”)。如将理解的,在其中多于一组的列平面一起测试的实施例中,不是需要136个位来实现17个列平面的完全可见性,而是仅需要9个位。

67.失效地址位8位7位6位5位4位3位2位1位0无失效00000000000000000011000000010

…………………………

270100001111271100010000多位失效-第一组17个列平面110000001多位失效-第二组17个列平面110000010多位失效-两组列平面110000011

68.表1

69.例如,再次参考图4a和4b,编码器406可以从多个列平面(例如,其中的两)组接收

多个位。更具体地,作为非限制性实例,编码器406可以从第一组17个列平面和第二组17个列平面接收多个位。进一步地,响应于所述多个位中的每个位通过测试(即,每个位具有非缺陷状态),编码器406可以输出包含指示每个位通过的多个位(例如,000000000;参见表1)的信号。进一步地,响应于所述多个位中的仅一个位失效(即,具有缺陷状态),编码器406可以输出包含指示失效的所述一个位的位地址(本文也称为“地址”)的多个位(例如,100001111;参见表1的地址270)的信号。此外,响应于所述多个位中的多于一个位失效(即,具有缺陷状态),编码器406可以输出包含(例如,在第一组列平面和/或第二组列平面中)指示多位失效的多个位(例如,110000001、110000010或110000011;参见例如表1)的信号。

70.图7是根据本公开的各个实施例的测试存储器装置的示例方法700的流程图。方法700可以根据本公开中描述的至少一个实施例布置。在一些实施例中,方法700可以由如图1的存储器装置100、图4a的装置400a、图4b的装置400b、图5的存储器阵列500、图8的存储器系统800和/或图9的电子系统900等装置或系统或另一个装置或系统执行。尽管被展示为离散的框,但是根据期望的实施方案,各个框可以被划分为另外的框、被组合为更少的框或被消除。

71.方法700可以开始于框702,其中可以测试存储器阵列的多个列平面的列地址,并且方法700可以进行到框704。例如,对于多个列地址中的第一列地址,可以(例如,通过图4a的总线403)写入所述多个列平面。进一步地,可以从所述多个列平面读取数据,并且可以(例如,通过图4b的编码器406)将写入数据与读取数据进行比较,以确定列平面中的每个列平面的状态(例如,缺陷或非缺陷)。

72.在框704处,可以响应于所述多个列平面的多个位中的每个位针对列地址具有非缺陷状态而生成第一信号,并且方法700可以进行到框706。例如,可以响应于第一组列平面(例如,第一组17个列平面)和第二组列平面(例如,第二组17个列平面)中的每个位具有非缺陷状态而生成第一信号(例如000000000;参见例如表1)。

73.在框706处,可以响应于所述多个位中的仅一个位针对列地址具有缺陷状态而生成第二信号,并且方法700可以进行到框708。例如,可以响应于第一组列平面(例如,第一组17个列平面)和第二组列平面(例如,第二组17个列平面)的所述多个位中的仅一个位具有缺陷状态而生成第二信号(例如000000010;参见例如表1)。

74.在框708处,可以响应于所述多个位中的两个或两个以上位针对列地址具有缺陷状态而生成第三信号。例如,可以响应于第一组列平面(例如,第一组17个列平面)和第二组列平面(例如,第二组17个列平面)的所述多个位中的两个或两个以上位具有缺陷状态而生成第三信号(例如110000001、110000010或110000011;参见例如表1)。

75.在不脱离本公开的范围的情况下,可以对方法700进行修改、添加或省略。例如,可以以不同的顺序来实施方法700的操作。进一步地,所概述的操作和动作仅作为实例提供,并且在不背离所公开的实施例的本质的情况下,所述操作和动作中的一些操作和动作可以是任选的、组合成更少的操作和动作或者扩展成另外的操作和动作。

76.如将理解的,使用上面参考图4a、4b、5和/或6公开的实施例中的一或多个实施例,突发长度可从例如136个位减少到9个位(或从280个位减少到10个位)。进一步地,使用上面参考图4a、4b、5和/或7公开的实施例中的一或多个实施例,突发长度可从例如从272个位减少到9个位。因此,经过编码的1x数据(例如,针对ecc碰撞位可见性和单个位容忍)可以在比

生成真实1x数据所需的测试时间小的测试时间内生成。

77.还公开了一种存储器系统。根据各个实施例,存储器系统可以包含存储器装置(例如,图1的存储器装置100),所述存储器装置包含一或多个存储器胞元阵列。图8是根据本文所描述的一或多个实施例实施的存储器系统800的简化框图。可以包含例如半导体装置的存储器系统800包含存储器阵列802和电路系统804,所述电路系统可以包含仅举例来说编码器(例如,图4b的编码器406),如本文所述。可以包含多个存储器库的存储器阵列802可以包含多个存储器胞元。电路系统804可以与存储器阵列802操作性地耦接,可以被配置用于执行本文公开的一或多个实施例。存储器系统800还可以包含耦接到存储器阵列802和/或电路系统804的控制器(图8中未示出)。

78.还公开了一种电子系统。根据各个实施例,电子系统可以包含存储器装置,所述存储器装置包含多个存储器管芯,每个存储器管芯具有存储器胞元阵列。每个存储器胞元可以包含存取晶体管和与存取晶体管可操作地耦接的存储元件。

79.图9是根据本文描述的一或多个实施例实施的电子系统900的简化框图。电子系统900包含至少一个输入装置902,所述至少一个输入装置可以包含例如键盘、鼠标或触摸屏。电子系统900进一步包含至少一个输出装置904,如监视器、触摸屏或扬声器。输入装置902和输出装置904不一定可彼此分离。电子系统900进一步包含存储装置906。输入装置902、输出装置904和存储装置906可以耦接到处理器908。电子系统900进一步包含耦接到处理器908的存储器装置910。存储器装置910可以包含图8的存储器系统800。电子系统900可包含例如计算、处理、工业或消费产品。电子系统900可以包含例如但不限于个人计算机或计算机硬件组件、服务器或其它联网硬件组件、数据库引擎、入侵防御系统、手持装置、平板计算机、电子笔记本、相机、电话、音乐播放器、无线装置、显示器、芯片集、游戏、车辆或其它已知系统。

80.本公开的各个实施例可以包含一种装置。所述装置可以包含:存储器阵列,所述存储器阵列包含许多列平面;以及至少一个电路,所述至少一个电路耦接到所述存储器阵列。所述至少一个电路可以被配置成接收针对存储器阵列的所述多个列平面中的每个列平面的列地址的测试结果数据。所述至少一个电路还可以被配置成响应于所述多个列平面的多个位中的仅一个位未通过针对所述列地址的测试而将所述测试结果数据转换为第一结果,其中所述第一结果标识所述一个位和所述多个列平面中的包含所述一个位的列平面。此外,所述至少一个电路可以被配置成响应于仅一个列平面未通过针对所述列地址的所述测试并且所述一个列平面的多于一个位有缺陷而将所述测试结果数据转换为第二结果,其中所述第二结果标识所述一个列平面。

81.根据本公开的另一个实施例,测试存储器装置的方法可以包含测试存储器阵列的多个列平面的列地址。所述方法还可以包含测试存储器阵列的多个列平面的列地址。所述方法可以进一步包含响应于所述多个列平面的仅一个位未通过针对所述列地址的测试而生成第一信号,其中所述第一信号标识所述一个位和所述多个列平面中的包含所述一个位的列平面。此外,所述方法可以包含响应于所述多个列平面中的仅一个列平面未通过针对所述列地址的测试并且所述一个列平面的多于一个位未通过针对所述列地址的测试而生成第二信号,其中所述第二信号标识所述一个列平面。

82.根据本公开的另一个实施例,装置可以包含存储器阵列,所述存储器阵列包含多

个列平面。所述装置还可以包含耦接到所述存储器阵列的至少一个电路。所述至少一个电路可以被配置成测试所述存储器阵列的所述多个列平面的列地址,其中所述多个列平面包含第一组列平面和第二组列平面,并且所述第一组列平面和所述第二组列平面共同包含多个位。所述至少一个电路还可以被配置成响应于所述多个位中的每个位针对所述列地址具有非缺陷状态而生成第一信号。进一步地,所述至少一个电路可以被配置成响应于所述多个位中的仅一个位针对所述列地址具有缺陷状态而生成第二信号,其中所述第二信号标识所述一个位的地址。此外,所述至少一个电路可以被配置成响应于所述多个位中的两个或两个以上位针对所述列地址具有缺陷状态而生成第三信号。

83.本公开的另外的实施例包含一种系统。所述系统可以包含至少一个输入装置、至少一个输出装置和至少一个处理器装置,所述至少一个处理器装置可操作地耦接到所述输入装置和所述输出装置。所述系统还可以包含至少一个存储器装置,所述至少一个存储器装置可操作地耦接到所述至少一个处理器装置并且包括电路系统。所述电路系统可以被配置成将数据写入所述至少一个存储器装置的n个列平面中的每个列平面,并且从所述n个列平面中的每个列平面读取数据。所述电路系统还可以被配置成将写入数据与读取数据进行比较以生成n位测试数据。所述电路系统可以被配置成响应于所述n个列平面的多个位中的单个位有缺陷而将所述n位测试数据转换为第一m位结果,其中所述第一m位结果标识所述单个位和所述n个列平面中的包含所述单个位的列平面。进一步地,所述电路系统可以被配置成响应于所述n个列平面中的仅一个列平面有缺陷并且所述一个列平面的两个或两个以上位有缺陷而将所述n位测试数据转换为不同的第二m位结果,其中所述不同的第二m位结果标识所述一个列平面。

84.根据惯例,附图中展示的各种特征可以不按比例绘制。本公开中呈现的图示并不旨在是任何特定设备(例如,装置、系统等)或方法的实际视图,而仅仅是用于描述本公开的各个实施例的理想化表示。因此,为清楚起见,可以任意扩大或减小各种特征的尺寸。另外,为清楚起见,可以简化附图中的一些附图。因此,附图可能未描绘给定设备(例如,装置)的组件中的所有组件或特定方法的所有操作。

85.如本文所使用的,术语“装置”或“存储器装置”可以包含具有存储器的装置,但不限于仅具有存储器的装置。例如,装置或存储器装置可以包含存储器、处理器和/或其它组件或功能。例如,装置或存储器装置可以包含片上系统(soc)。

86.如本文所使用的,除非另有说明,否则术语“半导体”应广义地解释为包含可以采用或可以不采用半导体功能以进行操作的微电子装置和mems装置(例如,磁存储器、光学装置等)。

87.本文中并且尤其是所附权利要求(例如,所附权利要求的主体)中使用的术语总体上旨在作为“开放性”术语(例如,术语“包含(including)”应当被解释为“包含但不限于”,术语“具有”应当被解释为“至少具有”,术语“包含(includes)”应当被解释为“包含但不限于”等)。

88.另外,如果意图是特定数量的所引入的权利要求陈述,那么将在所述权利要求中明确陈述此类意图,并且在不存在此类陈述的情况下,不呈现此类意图。例如,为了帮助理解,以下所附权利要求可以含有使用引入性短语“至少一个”和“一或多个”来引入权利要求陈述。然而,此类短语的使用不应当解释为暗示由不定冠词“一个”或“一种”引入的权利要

求陈述将含有此类引入的权利要求陈述的任意特定权利要求限制为仅含有一个此类陈述的实施例,即使当相同的权利要求包含引入性短语“一或多个”或“至少一个”以及不定冠词如“一个”或“一种”时亦是如此(例如,“一个”和/或“一种”应当被解释为意指“至少一个”或“一或多个”);对于用于引入权利要求陈述的定冠词的使用也是如此。如本文所使用的,“和/或”包含相关联的所列项中的一或多个项的任何和所有组合。

89.另外,即使明确陈述了特定数量的引入的权利要求陈述,也应当理解,此类陈述应当被解释为至少意指所陈述的数量(例如,在无其它修饰语的情况下仅陈述“两个陈述”意指至少两个陈述或两个或两个以上陈述)。此外,在其中使用类似于“a、b和c等中的至少一个”或“a、b和c等中的一或多个”的惯例的情况下,通常此类构造旨在包含单独的a、单独的b、单独的c、a和b一起、a和c一起、b和c一起、或a、b和c一起等。例如,术语“和/或”的使用旨在以此方式进行解释。

90.进一步地,无论是在说明书、权利要求还是附图中,呈现两个或两个以上替代性术语的任何分隔性词语或短语都应当被理解为考虑到了包含术语之一、术语中的任一术语或两个术语的可能性。例如,短语“a或b”应当被理解为包含“a”或“b”或“a和b”的可能性。

91.另外,术语“第一”、“第二”、“第三”等的使用在本文中不一定用于暗示元件的具体顺序或数量。通常,术语“第一”、“第二”、“第三”等用于以通用标识符的形式区分不同的元件。在没有表明术语“第一”、“第二”、“第三”等暗示具体顺序的情况下,这些术语不应当被理解为暗示具体顺序。此外,在没有表明术语“第一”、“第二”、“第三”等暗示特定数量的元件的情况下,这些术语不应当被理解为暗示元件的具体数量。

92.以上描述并且在附图中展示的本公开的实施例不限制本公开的范围,所述范围由所附权利要求和其合法等效物的范围所涵盖。任何等效实施例都在本公开的范围内。实际上,除了本文示出和描述的那些之外,根据描述,本公开的各种修改(如所描述的元件的替代性有用组合)对于本领域的技术人员而言将变得显而易见。此类修改和实施例也落入所附权利要求和等效物的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1