储存系统的制作方法

储存系统

1.本技术享受以日本特许申请2021-47259号(申请日:2021年3月22日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

2.本发明的实施方式涉及储存(storage)系统。

背景技术:

3.已知具备电路基板、安装于电路基板的连接器、安装于连接器的存储模块的储存系统。

技术实现要素:

4.本发明的一个实施方式要解决的课题在于提供能够谋求小型化的储存系统。

5.一个实施方式的储存系统具备电路基板、连接器、第1存储系统以及第2存储系统。所述连接器安装于所述电路基板,包括具有在第1方向上排列多个端子的第1端子组的第1插槽和在与所述第1方向交叉的第2方向上离开所述第1插槽且具有在所述第1方向上排列多个端子的第2端子组的第2插槽。所述第1端子组的所述第1方向上的端子排列的顺序与所述第2端子组的所述第1方向上的端子排列的顺序相反。所述第1存储系统被插入到所述第1插槽而与所述第1端子组连接,包括第1基板和安装于所述第1基板的第1半导体存储部件。所述第2存储系统被插入到所述第2插槽而与所述第2端子组连接,包括第2基板和安装于所述第2基板的第2半导体存储部件。

附图说明

6.图1是表示实施方式的储存系统的整体结构的立体图。

7.图2是表示实施方式的储存系统的功能结构的一部分的框图。

8.图3是表示实施方式的ssd模块的图。

9.图4是表示实施方式的储存系统的剖视图。

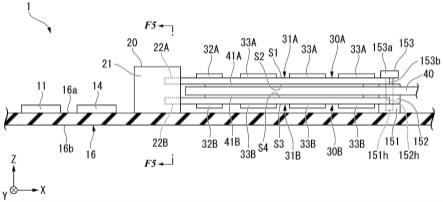

10.图5是图4中所示的连接器的沿着f5-f5线的剖视图。

11.图6是表示实施方式的4个端子部的端子排列的图。

12.图7是表示实施方式的连接器和电路基板的剖视图。

13.图8是表示实施方式的连接器和电路基板的俯视图。

14.图9是用于对实施方式的线路反转(lane reverse)功能进行说明的图。

15.图10是表示实施方式的第1变形例的连接器和电路基板的剖视图。

16.图11是表示实施方式的第2变形例的储存系统的剖视图。

17.标号说明

18.1、1a、1b储存系统;16电路基板;20、20a连接器;21连接器壳体;22a第1插槽;22b第2插槽;30a第1ssd模块(第1存储系统);31a第1基板;32a第1存储控制器;33a第1半导体存储

部件;30b第2ssd模块(第2存储系统);31b第2基板;32b第2存储控制器;33b第2半导体存储部件;91第1导电部;92第2导电部;93第3导电部;94第4导电部;s1第1面;s2第2面;s3第3面;s4第4面;tg1第1端子组;tg2第2端子组;tg3第3端子组;tg4第4端子组。

具体实施方式

19.以下,参照附图对实施方式的储存系统进行说明。在以下的说明中,对具有相同或者类似的功能的结构赋予同一标号。并且,有时省略那些结构的重复说明。“平行”、“正交”、或者“相同”分别也可以包括“大致平行”、“大致正交”或者“大致相同的”情况。“连接”不限定于机械方式的连接,也可以包括电连接。即,“连接”不限定于与对象物直接地连接的情况,也可以包括在其间夹有其他要素而与对象物连接的情况。

20.(实施方式)

21.<1.储存系统的整体结构>

22.图1是表示实施方式的储存系统1的整体结构的立体图。储存系统1例如是如笔记本型个人计算机那样的信息处理装置(或者电子设备)。但是,储存系统1不限定于上述例子,安置型的个人计算机、服务器装置、移动型的信息终端设备、车载装置等各种信息处理装置也适当地符合。

23.储存系统1例如具有主体单元2和能够相对于主体单元2可开闭的显示单元3。主体单元2具有键盘等输入装置2a。显示单元3具有能够显示图像、影像的显示装置3a。

24.在本实施方式中,主体单元2具有报知装置13。报知装置13在后述的ssd(solid state drive,固态硬盘驱动器)模块30正在工作的情况下,向外部(例如用户)报知ssd模块30正在工作这一状况。报知装置13例如包括能够从主体单元2的外部视觉识别的led(light emitting diode,发光二极管)13a和对led13a的发光进行控制的控制电路。报知装置13例如通过使led13a闪烁来报知ssd模块30正在工作这一状况。

25.图2是表示储存系统1的功能结构的一部分的框图。储存系统1例如具有主机控制器11、主机存储器12、报知装置13、主桥(host bridge)14、电源电路15、连接器20以及多个ssd模块30。多个ssd模块30包括第1ssd模块30a和第2ssd模块30b。在本实施方式中,构成了包括主机控制器11、主机存储器12、报知装置13、主桥14以及电源电路15的主机装置10的一个例子。连接器20也可以作为主机装置10的一部分来设置。

26.主机控制器11通过如搭载于储存系统1的cpu(central processing unit,中央处理单元)那样的硬件处理器执行程序(软件)来实现。但是,主机控制器11的功能的全部或者一部分既可以通过asic(application specific integrated circuit,专用集成电路)、pld(programmable logic device,可编程逻辑器件)或者fpga(field programmable gate array,现场可编程门阵列)等硬件(电路部;包括电路系统(circuitry))来实现,也可以通过软件和硬件的协作来实现。

27.主机控制器11对储存系统1的整体进行控制。例如,主机控制器11执行对于ssd模块30的数据的写入、读出或者擦除。在本实施方式中,主机控制器11经由主桥14以及连接器20而与ssd模块30进行数据的收发。

28.主机存储器12由设置于储存系统1的dram(dynamic random access memory,动态随机访问存储器)等构成。主机存储器12例如是暂时性地保存主机控制器11与ssd模块30之

间传送的数据的数据缓存。主机存储器12经由主桥14而与主机控制器11连接。但是,主机存储器12也可以与主机控制器11直接连接。

29.主桥14设置在主机控制器11以及主机存储器12与连接器20之间。主桥14包括主机接口电路(主机i/f)14f。主机i/f14f经由设置于后述的电路基板16的布线以及连接器20而与ssd模块30连接。主机i/f14f在主机控制器11与ssd模块30之间收发数据、命令以及地址。主机i/f14f例如符合pcie(pci express)(注册商标)、nvme(nvm express)(注册商标)、sata(serial advanced technology attachment)或者sas(serial attached scsi)等通信接口标准。主桥14是“桥电路”的一个例子。

30.电源电路15设置于后述的电路基板16,与连接器20连接。电源电路15经由连接器20向ssd模块30供给电力。

31.连接器20设置在主桥14以及电源电路15与ssd模块30之间。连接器20以能够拆装的方式安装ssd模块30,将主桥14与ssd模块30连接,并且,将电源电路15与ssd模块30连接。关于连接器20的详细,将在后面进行描述。

32.第1ssd模块30a和第2ssd模块30b分别是以非易失方式存储从主机装置10接受的数据的存储装置。第1ssd模块30a是“第1存储系统”的一个例子。第2ssd模块30b是“第2存储系统”的一个例子。在本实施方式中,在不对第1ssd模块30a和第2ssd模块30b进行区别的情况下,称为“ssd模块30”。

33.<2.ssd模块的结构>

34.接着,对ssd模块30的结构进行说明。

35.图3是表示ssd模块30(例如第1ssd模块30a)的图。图3中的(a)是从表面观察ssd模块30(例如第1ssd模块30a)而得到的图。图3中的(b)是从背面观察ssd模块30(例如第1ssd模块30a)而得到的图。即,图3中的(b)是将图3中的(a)中所示的ssd模块30翻过来表示的图。第1ssd模块30a具有第1基板31a、第1存储控制器32a以及一个以上(例如多个)第1半导体存储部件33a。

36.第1基板31a是具有如玻璃环氧树脂那样的绝缘体和设置于绝缘体的表层以及内层的布线图案的电路基板或者印制布线基板。第1基板31a具有第1面s1和位于与第1面s1相反侧的第2面s2。在本实施方式中,第1存储控制器32a和多个第1半导体存储部件33a安装于第1面s1。另一方面,在第2面s2不安装存储控制器和半导体存储部件。

37.第1基板31a具有安装于连接器20的第1端部30e1和位于与第1端部30e1相反侧的第2端部30e2。第1端部30e1具有包括多个端子35的端子部34。多个端子35设置于第1基板31a的表面(即第1面s1和第2面s2),在第1基板31a的表面露出。多个端子35包括设置于第1基板31a的第1面s1的多个端子35a和设置于第1基板31a的第2面s2的多个端子35b。多个端子35各自具有细长的平板形状。端子部34符合与主机i/f14f相同的通信接口标准。端子部34例如符合m.2标准。在第2端部30e2设置有位置由后述的固定部件153(参照图4)进行固定的凹部36。

38.第1存储控制器32a设置在第1基板31a的第1端部30e1与多个第1半导体存储部件33a之间。第1存储控制器32a具有主机连接用的接口电路(主机连接i/f)32f。主机连接i/f32f经由第1基板31a的端子部34以及连接器20而与主桥14的主机i/f14f(参照图2)连接。主机连接i/f32f符合与主桥14的主机i/f14f相同的通信接口标准。

39.第1存储控制器32a通过设置于第1基板31a的布线而与多个第1半导体存储部件33a连接。第1存储控制器32a对多个第1半导体存储部件33a进行控制。例如,第1存储控制器32a基于从主机装置10接受的命令,执行对于多个第1半导体存储部件33a的数据的写入、读出以及擦除。

40.第1半导体存储部件33a是以非易失的方式存储数据的非易失性的半导体存储部件,例如是nand型闪速存储器。但是,第1半导体存储部件33a不限定于上述例子,也可以是mram(magnetoresistive random access memory,磁阻随机访问存储器)、其他类型的存储装置。

41.第1ssd模块30a也可以在上述的结构的基础上还具有安装于第1基板31a的易失性存储器37a(参照图11)。易失性存储器37a由dram等构成。易失性存储器37a包括暂时地保存在主机装置10与第1半导体存储部件33a之间传送的数据的数据缓存。

42.同样地,第2ssd模块30b具有第2基板31b、第2存储控制器32b、以及一个以上(例如多个)第2半导体存储部件33b。在本实施方式中,第2ssd模块30b是与第1ssd模块30a相同类型的存储模块。因此,对于关于第2ssd模块30b的说明,在关于第1ssd模块30a的上述说明中,将“第1ssd模块30a”替换表达为“第2ssd模块30b”,将“第1基板31a”替换表达为“第2基板31b”,将“第1面s1”替换表达为“第3面s3”,将“第2面s2”替换表达为“第4面s4”,将“第1存储控制器32a”替换表达为“第2存储控制器32b”,将“第1半导体存储部件33a”替换表达为“第2半导体存储部件33b”,将“易失性存储器37a”替换表达为“易失性存储器37b”即可。

43.在本实施方式中,第1ssd模块30a和第2ssd模块30b是包括部件配置在内完全相同类型的存储模块。但是,“相同类型的存储模块”不限定于完全相同类型的存储模块,是符合了相同标准的存储模块即可。例如,第1ssd模块30a和第2ssd模块30b的所搭载的半导体存储部件的数量、容量也可以不同。

44.<3.与连接器关联的结构>

45.<3.1连接器周边的整体结构>

46.图4是表示储存系统1的剖视图。在此,对x方向、y方向以及z方向进行定义。x方向和y方向是沿着后述的电路基板16的第1面16a的方向。x方向是从连接器20朝向ssd模块30的方向。y方向是与x方向交叉的方向(例如正交的方向),是ssd模块30的宽度方向。z方向是从电路基板16朝向连接器20的方向,是电路基板16的厚度方向。y方向是“第1方向”的一个例子。z方向是“第2方向”的一个例子。以下,有时以图4的姿势为基准来称为“上”或者“下”。但是,这些表现并不规定重力方向。

47.如图4所示,储存系统1在上述的主机控制器11、主桥14、连接器20、第1ssd模块30a以及第2ssd模块30b的基础上还具备电路基板16、散热用部件40、第1热传导部件41a以及第2热传导部件41b。

48.<3.2电路基板的结构>

49.电路基板16例如是储存系统1的母板。电路基板16具有如玻璃环氧树脂那样的绝缘体和设置在绝缘体的内层以及外层的布线图案。布线图案包括在主桥14与连接器20之间延伸的多条布线,并且包括在电源电路15与连接器20之间延伸的多条布线。电路基板16具有第1面16a和位于与第1面16a相反侧的第2面16b。在电路基板16的第1面16a例如安装有主机控制器11、主桥14以及连接器20。第1面16a是“安装面”的一个例子。

50.<3.3连接器的结构>

51.接着,对连接器20进行说明。连接器20是多级插入的连接器。连接器20例如具有连接器壳体21、第1插槽22a以及第2插槽22b。连接器壳体21由绝缘性的树脂部件等形成。连接器壳体21形成连接器20的外廓,并且,对使用图5在后面进行描述的4个端子组tg1、tg2、tg3、tg4所包括的多个端子51、52、53、54进行支承。连接器壳体21是沿着y方向的长方体状。

52.第1插槽22a和第2插槽22b是设置于连接器壳体21的插入口。第1插槽22a和第2插槽22b分别在x方向上开口,并且,在y方向上延伸。第1插槽22a和第2插槽22b分别是例如符合m.2标准的插槽。第1插槽22a和第2插槽22b设置于在z方向上不同的高度,在z方向上相互分离。在本实施方式中,第2插槽22b在z方向上位于第1插槽22a与电路基板16之间。在第1插槽22a以能够拆装的方式插入第1ssd模块30a。在第2插槽22b以能够拆装的方式插入第2ssd模块30b。

53.图5是图4中所示的连接器20的沿着f5-f5线的剖视图。

54.第1插槽22a具有第1端子组tg1和第3端子组tg3。第1端子组tg1位于插入到第1插槽22a的第1ssd模块30a的第1基板31a的下侧(第2面s2侧)。换言之,第1端子组tg1在z方向上位于第3端子组tg3与第2插槽22b之间。第1端子组tg1具有在y方向上排列的多个端子51。多个端子51从下方(第2面s2侧)与第1ssd模块30a的第1基板31a的端子部34接触,与端子部34所包括的多个端子35b连接。

55.第3端子组tg3位于插入到第1插槽22a的第1ssd模块30a的第1基板31a的上侧(第1面s1侧)。换言之,第1ssd模块30a的第1基板31a插入在第1端子组tg1与第3端子组tg3之间。第3端子组tg3具有在y方向上排列的多个端子53。多个端子53从上方(第1面s1侧)与第1ssd模块30a的第1基板31a的端子部34接触,与端子部34所包括的多个端子35a连接。

56.另一方面,第2插槽22b具有第2端子组tg2和第4端子组tg4。第2端子组tg2位于插入到第2插槽22b的第2ssd模块30b的第2基板31b的下侧(第4面s4侧)。换言之,第2端子组tg2在z方向上位于第4端子组tg4与第1插槽22a之间。第2端子组tg2具有在y方向上排列的多个端子52。多个端子52从下方(第4面s4侧)与第2ssd模块30b的第2基板31b的端子部34接触,与端子部34所包括的多个端子35b连接。关于该内容,将在后面详细地进行描述。

57.第4端子组tg4位于插入到第2插槽22b的第2ssd模块30b的第2基板31b的上侧(第3面s3侧)。换言之,第2ssd模块30b的第2基板31b被插入到第2端子组tg2与第4端子组tg4之间。第4端子组tg4具有在y方向上排列的多个端子54。多个端子54从上方(第3面s3侧)与第2ssd模块30b的第2基板31b的端子部34接触,与端子部34所包括的多个端子35a连接。关于该内容,将在后面详细地进行描述。

58.在本实施方式中,第2插槽22b具有以相对于第1插槽22a而上下相反的方式反转(旋转)的端子排列(或者信号排列)。“端子排列”意味着对多个端子分配的多个功能(电源、接地、各种信号)的排列(即排列顺序)。并且,对第1端子组tg1和第2端子组tg2分配有相同的信号。进一步,对第3端子组tg3和第4端子组tg4分配有相同的信号。

59.详细而言,第1端子组tg1的y方向上的端子排列的顺序与第2端子组tg2的y方向上的端子排列的顺序相反。在图5所示的例子中,对第1端子组tg1的多个端子51进行分配,以使得从图5中的右侧起,端子编号(引脚编号)为p2、p4、p6、

……

、pm(m为任意的偶数)。另一方面,对第2端子组tg2的多个端子52进行分配,以使得从图5中的左侧起,端子编号(引脚编

号)为p2、p4、p6、

……

、pm。并且,在第1端子组tg1和第2端子组tg2中,对相同的端子编号(相同的引脚编号)的端子分配相同功能(例如相同信号)。

60.同样地,第3端子组tg3的y方向上的端子排列的顺序与第4端子组tg4的y方向上的端子排列的顺序相反。例如,在图5所示的例子中,对第3端子组tg3的多个端子53进行分配,以使得从图5中的右侧起,端子编号(引脚编号)为p1、p3、p5、

……

、pn(n为任意的奇数)。另一方面,对第4端子组tg4的多个端子54进行分配,以使得从图5中的左侧起,端子编号(引脚编号)为p1、p3、p5、

……

、pn。并且,在第3端子组tg3和第4端子组tg4中,对相同端子编号(相同引脚编号)的端子分配相同功能(例如相同信号)。

61.图6是表示4个端子组tg1、tg2、tg3、tg4的端子排列的图。在此,第1端子组tg1在y方向上具有第1端部e1和位于与第1端部e1相反侧的第2端部e2。“端部”例如意味着在第1端子组tg1中从y方向上的一端起一个(或者两个)端子51所存在的区域。该定义关于第2端子组tg2、第3端子组tg3、第4端子组tg4也是同样的。

62.[第1端子组]

[0063]

第1端子组tg1的多个端子51例如包括电源端子61a、复位信号端子62a、总线信号端子63a、64a、plp(power loss protection,掉电保护)信号端子65a、66a以及状态信号端子67a。电源端子61a、复位信号端子62a、总线信号端子63a、64a、plp信号端子65a、66a以及状态信号端子67a分别是“第1端子”的一个例子。

[0064]

电源端子61a是向第1ssd模块30a供给电源的端子。电源端子61a分别设置于第1端子组tg1的第1端部e1和第2端部e2。在本实施方式中,从第1端子组tg1的第1端部e1的一端起,2个端子51为电源端子61a。进一步,从第1端子组tg1的第2端部e2的一端起,3个端子51为电源端子61a。

[0065]

复位信号端子62a是输出使第1ssd模块30a进行复位的复位信号的端子。复位信号例如是在主机控制器11第一次识别到第1ssd模块30a的情况下从主机控制器11发送的预复位信号。在本实施方式中,对于第1ssd模块30a的复位信号与对于第2ssd模块30b的复位信号相同。复位信号端子62a在y方向上位于第1端子组tg1的第2端部e2与第1端子组tg1的中央部c之间。并且,复位信号端子62a在y方向上位于距第1端子组tg1的中央部c比距第1端子组tg1的第2端部e2近的位置。

[0066]

总线信号端子63a、64a包括总线数据端子63a和总线时钟端子64a。总线数据端子63a是流动伴随有能够确定第1ssd模块30a和第2ssd模块30b中的一方的地址信息的信号的端子。在此所说的“地址信息”既可以是表示信号的发送目的地的地址信息,也可以是表示信号的发送源的地址信息。例如,在总线数据端子63a流动伴随有将第1ssd模块30a或者第2ssd模块30b作为目标的发送目的地的地址信息的确定命令。确定命令是与对于ssd模块30的数据的写入、读出或者擦除的要求不同的命令,例如是要求ssd模块30的温度信息的命令。另外,在总线数据端子63a流动伴随有发送源的ssd模块30的地址信息的数据信号(例如表示ssd模块30的温度信息的信号)来作为对于上述确定命令的响应。总线时钟端子64a是流动被使用于在总线数据端子63a中流动的数据信号的读取的时钟信号的端子。总线信号端子63a、64a例如是被作为pcie标准中的sm总线(system management bus,系统管理总线)来使用的端子。总线信号端子63a、64a在y方向上位于第1端子组tg1的第2端部e2与第1端子组tg1的中央部c之间。并且,总线信号端子63a、64a在y方向上位于距第1端子组tg1的中央

部c比距第1端子组tg1的第2端部e2近的位置。

[0067]

plp信号端子65a、66a包括第1plp信号端子65a和第2plp信号端子66a。

[0068]

第1plp信号端子65a是在对于第1ssd模块30a的电源供给被切断的情况下从主机控制器11向第1ssd模块30a输出预定信号(以下称为“第1plp信号”)的端子。例如,主机控制器11在对于第1ssd模块30a的电源供给被切断的情况下,作为第1plp信号,使之前维持为第1电压(例如高(high)电平的电压)的电压变化为电压电平与第1电压不同的第2电压(例如低(low)电平的电压)。第1ssd模块30a在检测到第1plp信号的情况下,例如进行将暂时性地保存于易失性存储器37a的数据写入到第1半导体存储部件33a的数据退避处理。

[0069]

第2plp信号端子66a是在第1ssd模块30a的数据退避处理已正常地结束的情况下从第1ssd模块30a向主机控制器11输入预定信号(以下记载为“第2plp信号”)的端子。例如,第1ssd模块30a在开始数据退避处理的情况下,使之前维持为第1电压(例如高电平的电压)的电压变化为电压电平与第1电压不同的第2电压(例如低电平的电压)。并且,第1ssd模块30a在数据退避处理已正常地结束的情况下,作为第2plp信号,使之前维持为第2电压的电压恢复为第1电压。由此,主机控制器11对数据退避处理已正常地结束这一情况进行检测。主机控制器11在检测到数据退避处理已正常地结束的情况下,切断向第1ssd模块30a的电源供给。

[0070]

第1plp信号端子65a和第2plp信号端子66a在y方向上位于第1端子组tg1的第1端部e1与第1端子组tg1的中央部c之间。第1plp信号端子65a在y方向上位于距第1端子组tg1的第1端部e1比距第1端子组tg1的中央部c近的位置。第2plp信号端子66a在y方向上位于距第1端子组tg1的中央部c比距第1端子组tg1的第1端部e1近的位置。

[0071]

状态信号端子67a是在第1ssd模块30a正在工作(例如数据的写入、读出或者擦除的工作中)的情况下被从第1ssd模块30a输入表示第1ssd模块30a正在工作这一状况的状态信号的端子。例如,状态信号在第1ssd模块30a正在工作的情况下由第1ssd模块30a维持为第1电压(例如高电平的电压)。另一方面,状态信号在第1ssd模块30a的工作为停止中的情况下由第1ssd模块30a维持为电压电平与第1电压不同的第2电压(例如低电平的电压)。主机控制器11在状态信号端子67a的电压电平被维持为第1电压的情况下,通过使主体单元2的报知装置13的led13a闪烁,向外部报知ssd模块30正在工作这一状况。

[0072]

[第2端子组]

[0073]

第2端子组tg2与第1端子组tg1同样地例如包括电源端子61b、复位信号端子62b、总线信号端子63b、64b、plp信号端子65b、66b以及状态信号端子67b。电源端子61b、复位信号端子62b、总线信号端子63b、64b、plp信号端子65b、66b以及状态信号端子67b分别是“第2端子”的一个例子。

[0074]

电源端子61b是向第2ssd模块30b供给电源的端子。电源端子61b分别设置于第2端子组tg2的第1端部e1和第2端部e2。在本实施方式中,从第2端子组tg2的第1端部e1的一端起,3个端子52是电源端子61b。进一步,从第2端子组tg2的第2端部e2的一端起,2个端子52为电源端子61b。

[0075]

复位信号端子62b是输出使第2ssd模块30b进行复位的复位信号的端子。复位信号例如是在主机控制器11第一次识别到第2ssd模块30b的情况下从主机控制器11发送的预复位信号。复位信号端子62b在y方向上位于第2端子组tg2的第1端部e1与第2端子组tg2的中

央部c之间。并且,复位信号端子62b在y方向上位于距第2端子组tg2的中央部c比距第2端子组tg2的第1端部e1近的位置。

[0076]

总线信号端子63b、64b包括总线数据端子63b和总线时钟端子64b。总线数据端子63b是流动伴随有能够确定第1ssd模块30a和第2ssd模块30b中的一方的地址信息的信号的端子。例如,在总线数据端子63b流动伴随有将第1ssd模块30a或者第2ssd模块30b作为目标的发送目的地的地址信息的确定命令。另外,作为对于上述确定命令的响应,在总线数据端子63b流动伴随有发送源的ssd模块30的地址信息的数据信号。总线时钟端子64b是流动被使用于在总线数据端子63b中流动的数据信号的读取的时钟信号的端子。总线信号端子63b、64b例如是被作为pcie标准中的sm总线来使用的端子。总线信号端子63b、64b在y方向上位于第2端子组tg2的第1端部e1与第2端子组tg2的中央部c之间。并且,总线信号端子63b、64b在y方向上位于距第2端子组tg2的中央部c比距第2端子组tg2的第1端部e1近的位置。

[0077]

plp信号端子65b、66b包括第1plp信号端子65b和第2plp信号端子66b。

[0078]

第1plp信号端子65b是在对于第2ssd模块30b的电源供给被切断的情况下从主机控制器11向第2ssd模块30b输出第1plp信号的端子。对于第2ssd模块30b的第1plp信号和对于第1ssd模块30a的第1plp信号是相同的信号。第2ssd模块30b在检测到第1plp信号的情况下,例如进行将暂时性地保存于易失性存储器37b的数据写入到第2半导体存储部件33b的数据退避处理。在本实施方式中,主机控制器11在对于第1ssd模块30a和第2ssd模块30b的电源供给被切断的情况下,使得从第1端子组tg1的第1plp信号端子65a和第2端子组tg2的第1plp信号端子65b这两方输出第1plp信号。

[0079]

第2plp信号端子66b是在第2ssd模块30b的数据退避处理已正常地结束的情况下从第2ssd模块30b向主机控制器11输入第2plp信号的端子。从第2ssd模块30b输出至主机控制器11的第2plp信号和从第1ssd模块30a输出至主机控制器11的第1plp信号是相同的信号。主机控制器11在检测到第2ssd模块30b的数据退避处理已正常地结束这一状况的情况下,切断向第2ssd模块30b的电源供给。在本实施方式中,主机控制器11在第1端子组tg1的第2plp信号端子66a和第2端子组tg2的第2plp信号端子66b的电压状态从第2电压恢复为第1电压的情况下,视为第1ssd模块30a和第2ssd模块30b的数据退避处理已正常地结束,切断对于第1ssd模块30a和第2ssd模块30b的电源供给。

[0080]

第1plp信号端子65b和第2plp信号端子66b在y方向上位于第2端子组tg2的第2端部e2与第2端子组tg2的中央部c之间。第1plp信号端子65b在y方向上位于距第2端子组tg2的第2端部e2比距第2端子组tg2的中央部c近的位置。第2plp信号端子66b在y方向上位于距第2端子组tg2的中央部c比距第2端子组tg2的第2端部e2近的位置。

[0081]

状态信号端子67b是在第2ssd模块30b正在工作(例如数据的写入、读出或者擦除的工作中)的情况下被从第2ssd模块30b输入表示第2ssd模块30b正在工作这一状况的状态信号的端子。例如,状态信号在第2ssd模块30b正在工作的情况下,由第2ssd模块30b维持为第1电压(例如高电平的电压),在第2ssd模块30b的工作停止中的情况下,由第2ssd模块30b维持为电压电平与第1电压不同的第2电压(例如低电平的电压)。主机控制器11在状态信号端子67b的电压电平被维持为第1电压的情况下,通过使主体单元2的报知装置13的led13a闪烁,向外部报知ssd模块30正在工作这一状况。

[0082]

[第3端子组]

[0083]

第3端子组tg3包括接地端子71a、第1发送端子81a~第4发送端子84a以及第1接收端子85a~第4接收端子88a。“接地端子71a”是“第1端子”的其他一个例子。第1发送端子81a~第4发送端子84a和第1接收端子85a~第4接收端子88a分别是“第3端子”的一个例子。

[0084]

接地端子71a是与第1ssd模块30a的第1基板31a的接地连接的端子。接地端子71a分别设置于第3端子组tg3的第1端部e1和第2端部e2。在本实施方式中,从第3端子组tg3的第1端部e1的一端起,2个端子53为接地端子71a。进一步,从第3端子组tg3的第2端部e2的一端起,3个端子53为接地端子71a。

[0085]

第1发送端子81a~第4发送端子84a和第1接收端子85a~第4接收端子88a是被使用于在主机装置10与第1ssd模块30a之间收发数据的端子。例如,第1发送端子81a~第4发送端子84a是要被写入到第1ssd模块30a的写数据从主机装置10流向第1ssd模块30a的端子。另一方面,第1接收端子85a~第4接收端子88a是从第1ssd模块30a读出的读数据从第1ssd模块30a流向主机装置10的端子。第1发送端子81a~第4发送端子84a和第1接收端子85a~第4接收端子88a例如是与pcle标准的线路(lane)对应的端子。

[0086]

[第4端子组]

[0087]

第4端子组tg4与第3端子组tg3同样地包括接地端子71b、第1发送端子81b~第4发送端子84b以及第1接收端子85b~第4接收端子88b。“接地端子71b”是“第2端子”的其他一个例子。第1发送端子81b~第4发送端子84b和第1接收端子85b~第4接收端子88b分别是“第4端子”的一个例子。

[0088]

接地端子71b是与第2ssd模块30b的第2基板31b的接地连接的端子。接地端子71b分别设置于第4端子组tg4的第1端部e1和第2端部e2。在本实施方式中,从第4端子组tg4的第1端部e1的一端起,3个端子54是接地端子71b。进一步,从第4端子组tg4的第2端部e2的一端起,2个端子54是接地端子71b。

[0089]

第1发送端子81b~第4发送端子84b和第1接收端子85b~第4接收端子88b是被使用于在主机装置10与第2ssd模块30b之间收发数据的端子。例如,第1发送端子81b~第4发送端子84b是要被写入到第2ssd模块30b的写数据从主机装置10流向第2ssd模块30b的端子。另一方面,第1接收端子85b~第4接收端子88b是从第2ssd模块30b读出的读数据从第2ssd模块30b流向主机装置10的端子。第1发送端子81b~第4发送端子84b和第1接收端子85b~第4接收端子88b例如是与pcle标准的线路对应的端子。

[0090]

图7是表示电路基板16和连接器20的剖视图。连接器20具有将第1端子组tg1、第2端子组tg2、第3端子组tg3、第4端子组tg4所包括的多个端子51、52、53、54分别连接于电路基板16的多个导电部90。导电部90例如与所对应的各端子51、52、53、54形成为一体。导电部90在连接器壳体21的内部从端子51、52、53、54朝向电路基板16延伸。

[0091]

在本实施方式中,多个导电部90包括与第1端子组tg1所包括的第1特定端子51s连接的第1导电部91和与第2端子组tg2所包括的第2特定端子52s连接的第2导电部92。并且,在z方向上观察的情况下,第1导电部91和第2导电部92在连接器20的设置区域ma内电连接。设置区域ma意味着在z方向上观察的情况下与连接器20重叠的区域。“在z方向上观察的情况下在连接器20的设置区域ma内电连接”不限定于在连接器壳体21的内部连接了的情况,也可以包括在设置区域ma所包括的电路基板16的表层或者内层连接的情况(参照后述的第

1变形例)。

[0092]

在本实施方式中,第1导电部91和第2导电部92由设置在连接器壳体21的内部的结合部cn1结合,与电路基板16连接。并且,第1导电部91和第2导电部92经由设置于电路基板16的对于第1特定端子51s和第2特定端子52s的共用的布线100而连接于主桥14或者电源电路15。

[0093]

在本实施方式中,作为具有上述连接关系的第1特定端子51s和第2特定端子52s的组的例子,具有第1端子组tg1的电源端子61a和第2端子组tg2的电源端子61b的组。在该情况下,与第1端子组tg1的电源端子61a连接的第1导电部91和与第2端子组tg2的电源端子61b连接的第2导电部92在连接器壳体21的内部结合而与电路基板16连接,经由共用的布线101(参照图8)而连接于电源电路15。

[0094]

进一步,在本实施方式中,作为第1特定端子51s和第2特定端子52s的组的其他例子,具有第1端子组tg1的复位信号端子62a和第2端子组tg2的复位信号端子62b的组。在该情况下,与第1端子组tg1的复位信号端子62a连接的第1导电部91和与第2端子组tg2的复位信号端子62b连接的第2导电部92在连接器壳体21的内部结合而与电路基板16连接,经由共用的布线102(参照图8)而连接于主桥14。

[0095]

进一步,作为第1特定端子51s和第2特定端子52s的组的其他例子,具有第1端子组tg1的总线数据端子63a和第2端子组tg2的总线数据端子63b的组、第1端子组tg1的总线时钟端子64a和第2端子组tg2的总线时钟端子64b的组、第1端子组tg1的第1plp信号端子65a和第2端子组tg2的第1plp信号端子65b的组、第1端子组tg1的第2plp信号端子66a和第2端子组tg2的第2plp信号端子66b的组以及第1端子组tg1的状态信号端子67a和第2端子组tg2的状态信号端子67b的组。

[0096]

在本实施方式中,设置在连接器20的内部的多个导电部90包括与第3端子组tg3所包括的第3特定端子53s连接的第3导电部93、和与第4端子组tg4所包括的第4特定端子54s连接的第4导电部94。在本实施方式中,第3导电部93和第4导电部94相互绝缘,分别与电路基板16连接。并且,第3导电部93和第4导电部94经由设置于电路基板16的对于第3特定端子53s和第4特定端子54s的个别的布线110、120,相互独立地与主桥14连接。

[0097]

在本实施方式中,作为具有上述连接关系的第3特定端子53s和第4特定端子54s的组的例子,具有第3端子组tg3的第1发送端子81a和第2端子组tg2的第1发送端子81b的组。在该情况下,在本实施方式中,与第3端子组tg3的第1发送端子81a连接的第3导电部93和与第4端子组tg4的第1发送端子81b连接的第4导电部94分别与电路基板16连接。并且,第3导电部93和第4导电部94分别经由个别的布线111、121(参照图8)而相互独立地连接于主桥14。关于第3端子组tg3的第2发送端子82a~第4发送端子84a以及第1接收端子85a~第4接收端子88a和第4端子组tg4的第2发送端子82b~第4发送端子84b以及第1接收端子85b~第4接收端子88b,也是同样的。

[0098]

在本实施方式中,设置在连接器20的内部的多个导电部90包括与第3端子组tg3所包括的第5特定端子(例如接地端子71a)连接的第5导电部95和与第4端子组tg4所包括的第6特定端子(例如接地端子71b)连接的第6导电部96。并且,在z方向上观察的情况下,第5导电部95和第6导电部96在连接器20的设置区域ma内电连接。在本实施方式中,第5导电部95和第6导电部96由设置在连接器壳体21的内部的结合部cn2结合,经由设置于电路基板16的

共用的布线108(参照图8)而连接于电路基板16的接地。

[0099]

图8是表示电路基板16和连接器20的俯视图。在本实施方式中,第1端子组tg1的第1端部e1的电源端子61a和第2端子组tg2的第2端部e2的电源端子61b在连接器壳体21的内部相连接,与设置于电路基板16的共用的布线101a连接。进一步,第1端子组tg1的第2端部e2的电源端子61a和第2端子组tg2的第1端部e1的电源端子61b在连接器壳体21的内部相连接,与设置于电路基板16的共用的布线101b连接。布线101a、101b与电源电路15连接。

[0100]

此外,第1端子组tg1的第1端部e1的电源端子61a和第2端子组tg2的第1端部e1的电源端子61b也可以在连接器壳体21的内部相连接,与设置于电路基板16的共用的布线101a连接。进一步,第1端子组tg1的第2端部e2的电源端子61a和第2端子组tg2的第2端部e2的电源端子61b也可以在连接器壳体21的内部相连接,与设置于电路基板16的共用的布线101b连接。布线101a、101b与电源电路15连接。在该情况下,在物理上位于相互靠近的位置的端子彼此相连接,因此,能够简化连接器壳体21内的布线的布局。

[0101]

同样地,第1端子组tg1的复位信号端子62a和第2端子组tg2的复位信号端子62b在连接器壳体21的内部相连接,与设置于电路基板16的共用的布线102连接。第1端子组tg1的总线数据端子63a和第2端子组tg2的总线数据端子63b在连接器壳体21的内部相连接,与设置于电路基板16的共用的布线103连接。第1端子组tg1的总线时钟端子64a和第2端子组tg2的总线时钟端子64b在连接器壳体21的内部相连接,与设置于电路基板16的共用的布线104连接。第1端子组tg1的第1plp信号端子65a和第2端子组tg2的第1plp信号端子65b在连接器壳体21的内部相连接,与设置于电路基板16的共用的布线105连接。第1端子组tg1的第2plp信号端子66a和第2端子组tg2的第2plp信号端子66b在连接器壳体21的内部相连接,与设置于电路基板16的共用的布线106连接。第1端子组tg1的状态信号端子67a和第2端子组tg2的状态信号端子67b在连接器壳体21的内部相连接,与设置于电路基板16的共用的布线107连接。布线102~107与主桥14连接。

[0102]

另一方面,第3端子组tg3的发送端子81a~84a、第3端子组tg3的接收端子85a~88a、第4端子组tg4的发送端子81b~84b以及第4端子组tg4的接收端子85b~88b在连接器20的内部以相互绝缘的状态被引出到电路基板16,分别与设置于电路基板16的布线(线路)111~114、115~118、121~124、125~128一对一地连接。布线111~118、121~128与主桥14连接。

[0103]

图9是用于对主机装置10的线路反转功能进行说明的图。以下说明的线路反转功能例如由主桥14或者由主桥14与主机控制器11的协作来实现。

[0104]

主桥14具有与布线(线路)111~118、121~128对应的端子131~138、141~148。第1ssd模块30a用的端子131~134,作为主桥14中的物理位置,按第1发送端子131、第2发送端子132、第3发送端子133、第4发送端子134的顺序排列。同样地,第1ssd模块30a用的端子135~138,作为主桥14中的物理位置,按第1接收端子135、第2接收端子136、第3接收端子137、第4接收端子138的顺序排列。在此,第1ssd模块30a用的电路基板16的布线(线路)111~118,作为电路基板16中的物理位置,按与主桥14的端子131~138相同的顺序排列。因此,主桥14的端子131~138和电路基板16的布线111~118能够直接一对一地连接。

[0105]

另一方面,主桥14的第2ssd模块30b用的端子141~144,作为主桥14中的物理位置,以与第1ssd模块30a用的端子131~134相同的方向按第1发送端子141、第2发送端子

142、第3发送端子143、第4发送端子144的顺序排列。同样地,第2ssd模块30b用的端子145~148,作为主桥14中的物理位置,按第1接收端子145、第2接收端子146、第3接收端子147、第4接收端子148的顺序排列。然而,在本实施方式中,第2ssd模块30b如后述的那样上下反转地安装于连接器20。因此,第2ssd模块30b用的电路基板16的布线(线路)121~128按与主桥14的端子141~148相反的顺序排列。因此,主桥14的端子141~148和电路基板16的布线121~128无法直接一对一地连接。为了使主桥14的端子141~148与电路基板16的布线121~128在物理上匹配,需要在电路基板16内使布线121~128相互交叉地调换顺序。

[0106]

在本实施方式中,主机装置10通过线路反转功能,在软件上将主桥14的端子141~148的端子排列按相反顺序排列。由此,主机装置10使原本是从第1发送端子141、第2发送端子142、第3发送端子143、第4发送端子144发送的信号分别从第4发送端子144、第3发送端子143、第2发送端子142、第1发送端子141进行发送。进一步,主机装置10将由第4接收端子148、第3接收端子147、第2接收端子146、第1接收端子145接收的信号分别作为原本由第1接收端子145、第2接收端子146、第3接收端子147、第4接收端子148接受的信号来处理。因此,在本实施方式中,不需要在电路基板16内使布线121~128相互交叉地调换顺序,布线121~128能通过比较简单的布线布局来设置。

[0107]

在此,返回图4,对其余的结构进行说明。

[0108]

在本实施方式中,第1ssd模块30a和第2ssd模块30b在安装于连接器20的状态下与电路基板16的第1面16a平行地配置。第1ssd模块30a以使第1基板31a的第1面s1朝向上方、使第2面s2朝向下方的姿势插入到第1插槽22a。并且,第1基板31a的第2面s2的多个端子35b与第1插槽22a的第1端子组tg1连接,第1基板31a的第1面s1的多个端子35a与第3端子组tg3连接。另一方面,第2ssd模块30b以相对于第1ssd模块30a反转了的姿势(使上下相反地旋转后的姿势)安装于连接器20。即,第2ssd模块30b以使第2基板31b的第3面s3朝向下方、使第4面s4朝向上方的姿势插入到第2插槽22b。并且,第2基板31b的第4面s4的多个端子35b与第2插槽22b的第2端子组tg2连接,第2基板31b的第3面s3的多个端子35a与第4端子组tg4连接。换言之,第1ssd模块30a和第2ssd模块30b分别使没有搭载存储控制器32和半导体存储部件33的第2面s2和第4面s4相面对来安装于连接器20。

[0109]

接着,对2个ssd模块30的固定构造进行说明。

[0110]

如图4所示,在电路基板16的第1面16a设置有固定用的凸台(boss)151。凸台151设置在与ssd模块30的第2端部30e2对应的位置。在凸台151设置有供后述的固定部件153结合的结合孔151h。第2ssd模块30b载置在凸台151上。凸台151例如是金属制。

[0111]

在第1ssd模块30a与第2ssd模块30b之间设置有垫片(spacer)152。垫片152介于第1ssd模块30a与第2ssd模块30b之间,使第1ssd模块30a与第2ssd模块30b之间保持距离。垫片152具有供固定部件153插通的贯通孔152h。垫片152例如是金属制。

[0112]

固定部件153具有头部153a和轴部153b。头部153a从与垫片152相反侧面向第1ssd模块30a。轴部153b穿过第1ssd模块30a的第2端部30e2的凹部36、垫片152的贯通孔152h、第2ssd模块30b的第2端部30e2的凹部36而与凸台151的结合孔151h结合。由此,两个ssd模块30的位置被固定。固定部件153例如是金属制。

[0113]

接着,对两个ssd模块30的散热机构进行说明。

[0114]

散热用部件40在z方向上位于第1ssd模块30a与第2ssd模块30b之间。散热用部件

40使第1ssd模块30a与第2ssd模块30b之间的间隙中例如沿着x方向延伸。散热用部件40既可以是具有多个翅片的散热器(heat sink),也可以是与散热器连接的散热管,还可以是被从冷却水供给装置供给冷却水的水冷式的散热装置。

[0115]

第1热传导部件41a设置在第1ssd模块30a的第1基板31a与散热用部件40之间,与第1ssd模块30a的第1基板31a和散热用部件40接触。第1热传导部件41a例如由散热材料(thermal interface material:tim)形成。tim例如是润滑脂或者弹性体片材(elastomer sheet)。

[0116]

同样地,第2热传导部件41b设置在第2ssd模块30b的第2基板31b与散热用部件40之间,与第2ssd模块30b的第2基板31b和散热用部件40接触。第2热传导部件41b例如由散热材料(tim)形成。

[0117]

<2.作用>

[0118]

在本实施方式中,如图8所示,经由设置于电路基板16的共用的布线101,向连接器20的多个电源端子61a、61b供给电力。另外,经由设置于电路基板16的共用的布线108,连接器20的多个接地端子71a、71b与电路基板16的接地连接。

[0119]

另外,经由设置于电路基板16的共用的布线102,对两个ssd模块30发送共用的复位信号。另外,经由设置于电路基板16的共用的布线103、104,形成对于两个ssd模块30的通信用的总线。另外,经由设置于电路基板16的共用的布线105、106,收发用于指示两个ssd模块30的数据退避处理的开始或者对数据退避处理的完成进行识别的信号。另外,经由设置于电路基板16的共用的布线107,接收用于识别两个ssd模块30是否正在工作的信号。

[0120]

两个ssd模块30发出的热的一部分通过第1基板31a或者第2基板31b所包括的布线图案传播至第1基板31a的第2端部30e2或者第2基板31b的第2端部30e2,经由固定部件153传播至电路基板16。进一步,两个ssd模块30发出的热的其他一部分通过散热用部件40传播至两个ssd模块30的外部。由此,两个ssd模块30的散热得到促进。

[0121]

<4.优点>

[0122]

在此,对多个ssd模块被平放的情况(一个一个地安装于不同的连接器的情况)进行考虑。在该情况下,需要与多个ssd模块相应的设置面积。另外,在对于多个ssd模块分别设置散热机构的情况下,设置面积会与多个散热机构相应地增加。

[0123]

于是,考虑使用具有多个插槽的多级插入的连接器来重叠地配置多个ssd模块30。但是,当多个插槽的端子排列相同时,多个ssd模块30中的部件配置有可能会偏倚,在散热或者其他观点上,性能有可能会降低。例如,在将多个ssd模块以相同的上下朝向重叠地配置的情况下,搭载于第1ssd模块的第1存储控制器(高发热部件)朝向与第2ssd模块相反侧。但是,搭载于第2ssd模块的第2存储控制器(高发热部件)位于第1ssd模块的基板与第2ssd模块的基板之间的空间,有时会导致散热机构的大型化、有时散热性能会降低。

[0124]

另一方面,在本实施方式中,储存系统1具有电路基板16、连接器20、第1ssd模块30a以及第2ssd模块30b。连接器20具有在z方向上分离的第1插槽22a和第2插槽22b。根据这样的结构,首先,多个ssd模块30重叠地配置,因此,能够减小设置面积。由此,能够谋求储存系统1的小型化。

[0125]

进一步,在本实施方式中,第1插槽22a的第1端子组tg1的端子排列和第2插槽22b的第2端子组tg2的端子排列在y方向上相反。根据这样的结构,容易将搭载于第1ssd模块

30a和第2ssd模块30b的部件以上下和/或左右对称的方式配置。由此,例如多个ssd模块30中的温度平衡提高。由此,能够谋求对于多个ssd模块30的散热机构的小型化。由此,能够谋求储存系统1的进一步小型化。

[0126]

在本实施方式中,连接器20具有连接器壳体21、与第1端子组tg1的多个端子51所包括的第1特定端子51s连接的第1导电部91以及与第2端子组tg2的多个端子52所包括的第2特定端子52s连接的第2导电部92。在电路基板16的厚度方向上观察的情况下,第1导电部91和第2导电部92在连接器20的设置区域ma内相互连接。根据这样的结构,能够谋求连接器20与电路基板16的连接构造的简化、设置于电路基板16的布线的一部分的共用化。由此,能够谋求储存系统1的进一步小型化。

[0127]

在本实施方式中,第1插槽22a具有第1端子组tg1和第3端子组tg3。第1端子组tg1位于第3端子组tg3与第2插槽22b之间。第2插槽22b具有第2端子组tg2和第4端子组tg4。第2端子组tg2位于第4端子组tg4和第1插槽22a之间。并且,这些4个端子组tg1、tg2、tg3、tg4中相邻的两个端子组tg1、tg2所包括的两个特定端子51s、52s的导电部91、92在连接器20的设置区域ma内相互连接。根据这样的结构,能够由比较简单的结构谋求连接器20与电路基板16的连接构造的简化、设置于电路基板16的布线的一部分的共用化。由此,能够谋求储存系统1的进一步小型化。

[0128]

<5.变形例>

[0129]

接着,对几个变形例进行说明。在各变形例中,以下说明的以外的结构与上述的实施方式相同。

[0130]

<5.1第1变形例>

[0131]

图10是表示第1变形例的储存系统1a的连接器20a和电路基板16的剖视图。在第1变形例中,多个导电部90包括与第1端子组tg1所包括的第1特定端子51s连接的第1导电部91和与第2端子组tg2所包括的第2特定端子52s连接的第2导电部92。并且,在电路基板16的厚度方向上观察到的连接器壳体21的设置区域ma中,第1导电部91和第2导电部92由设置在电路基板16的表层或者内层的结合部cn1结合,与共用的布线100连接。通过这样的结构,也能够与上述的实施方式同样地谋求储存系统1的小型化。将第5导电部95与第6导电部96结合的结合部cn2也可以与结合部cn1同样地设置于电路基板16的表层或者内层。

[0132]

<5.2第2变形例>

[0133]

图11是表示第2变形例的储存系统1b的剖视图。在第2变形例中,在第1ssd模块30a的第1基板31a的第2面s2安装有第1存储控制器32a。在第1基板31a的第1面s1安装有易失性存储器37a和多个第1半导体存储部件33a。

[0134]

另一方面,在第2ssd模块30b的第2基板31b的第4面s4安装有第2存储控制器32b。在第2基板31b的第3面s3安装有易失性存储器37b和多个第2半导体存储部件33b。

[0135]

并且,第1ssd模块30a和第2ssd模块30b使第2面s2与第4面s4相面对来安装于连接器20。散热用部件40经由第1热传导部件41a而连接于第1存储控制器32a。进一步,散热用部件40经由第2热传导部件41b而连接于第2存储控制器32b。

[0136]

通过这样的结构,也能够与上述的实施方式同样地谋求储存系统1的小型化。

[0137]

以上,对实施方式以及变形例进行了说明,但实施方式以及变形例不限定于上述的例子。这些实施方式以及变形例也可以相互组合来实现。例如,连接器20的第1插槽22a和

第2插槽22b也可以在z方向(电路基板16的厚度方向)上较长地开口。在该情况下,第1ssd模块30a和第2ssd模块30b以与电路基板16垂直的姿势安装于连接器20。另外,连接器20的第1插槽22a和第2插槽22b也可以朝向z方向开口。

[0138]

根据以上说明的至少一个实施方式,储存系统具有电路基板、连接器、第1存储模块以及第2存储模块。连接器具有第1插槽和第2插槽。第1插槽的第1端子组的端子排列与第2插槽的第2端子组的端子排列相反。根据这样的结构,能够谋求储存系统的小型化。

[0139]

以上对本发明的几个实施方式进行了说明,但这些实施方式是作为例子提示的,并不是意在限定发明的范围。这些实施方式能够以其他各种各样的方式来实施,能够在不脱离发明的宗旨的范围内进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围、宗旨内,同样地包含在权利要求书所记载的发明及其等同的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1