反熔丝存储版图及其电路、反熔丝存储器及其设计方法与流程

本公开实施例涉及半导体电路设计领域,特别涉及一种反熔丝存储版图及其电路、反熔丝存储器及其设计方法。

背景技术:

1、反熔丝存储器(anti-fuse)可以通过反熔丝存储单元阵列实现,反熔丝存储单元的栅氧介质在施加高压后会发生击穿,击穿后通路的阻抗减小;通过检测击穿后的通路电阻状态可以读出反熔丝存储单元所存储的信息。

2、然而,在对某一存储单元区施加高电压进行编程时,高电压会对相邻的存储单元区造成干扰或损伤。而且,反熔丝存储器在数据编程阶段,对传输导线进行放电的放电晶体管需要进行快速放电,因此,放电晶体管通常被设计成栅介质层较厚的晶体管,不利于缩小反熔丝存储版图的布局面积以及不利于缩小反熔丝存储器的尺寸。

技术实现思路

1、本公开实施例提供一种反熔丝存储版图及其电路、反熔丝存储器及其设计方法,至少有利于缩小反熔丝存储版图的布局面积。

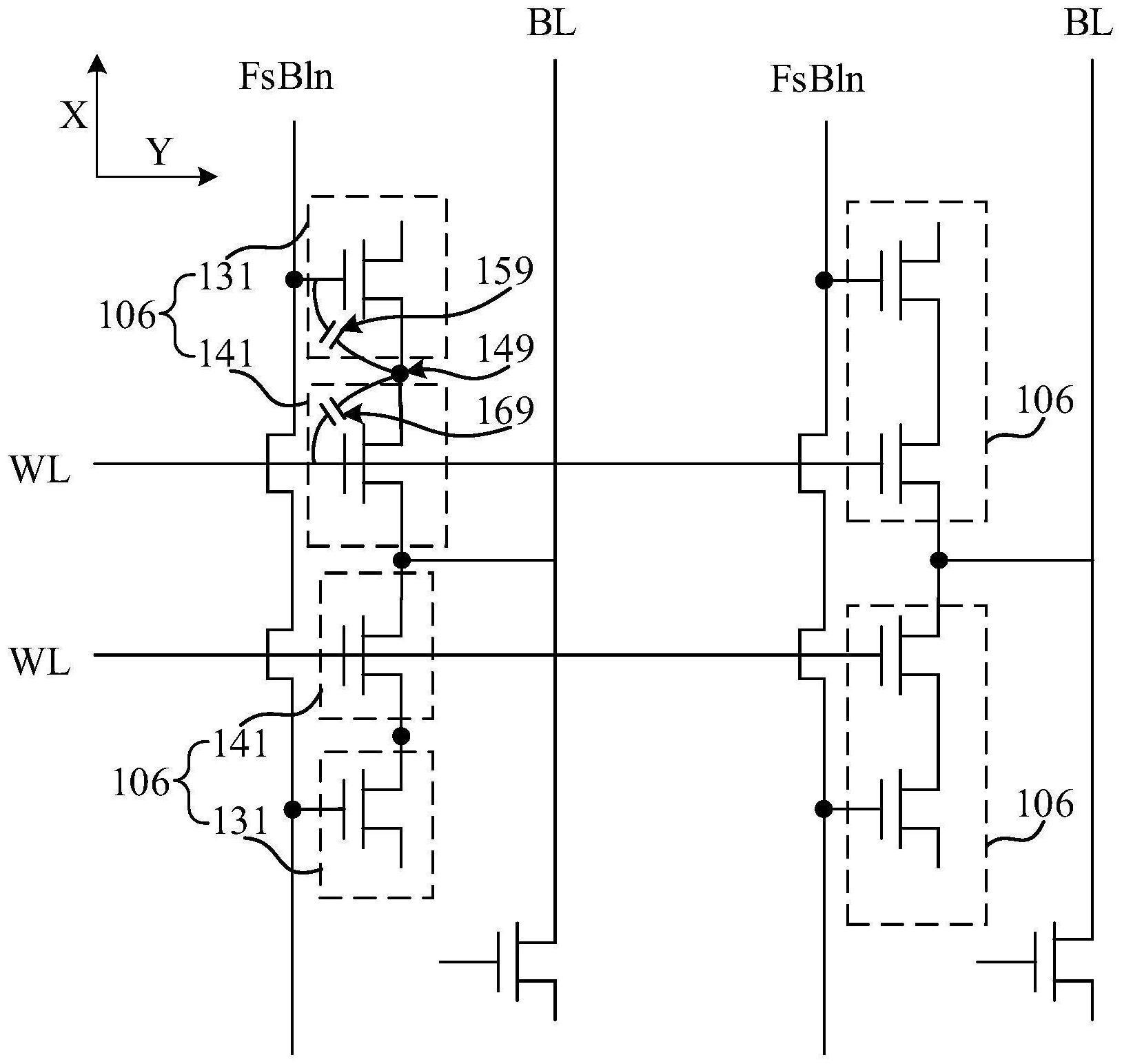

2、根据本公开一些实施例,本公开实施例一方面提供一种反熔丝存储版图,包括:有源区,所述有源区沿第一方向延伸且沿第二方向分立排布,每一所述有源区包括沿所述第一方向排布的至少两个存储单元区,每一所述存储单元区包括沿所述第一方向排布的反熔丝区以及控制区,在沿所述第一方向上,相邻所述存储单元的所述控制区相邻接,所述反熔丝区用于定义反熔丝晶体管,所述控制区用于定义控制晶体管;字线区,所述字线区沿第二方向延伸且与所述控制区相交,所述字线区用于定义与控制晶体管的栅极电连接的字线;电连接区,所述电连接区沿所述第二方向延伸且与所述反熔丝区相交,所述电连接区用于定义与反熔丝晶体管的栅极电连接的电连接层;编程控制区,所述编程控制区沿第三方向延伸且位于相应的所述有源区的一侧,且所述编程控制区与沿所述第一方向排列的所述电连接区相交,所述编程控制区用于定义编程控制层,所述编程控制层与沿所述第一方向排列的所述电连接层电连接。

3、在一些实施例中,所述编程控制区与所述电连接区处于同一层,且所述编程控制区与所述电连接区相邻接。

4、在一些实施例中,所述编程控制区与所述电连接区处于不同层,且所述编程控制区与所述电连接区具有正对区。

5、在一些实施例中,所述反熔丝存储版图还包括:通孔区,所述通孔区位于所述编程控制区与所述电连接区的正对区,用于定义导电柱,所述导电柱电连接所述电连接层与所述编程控制层。

6、在一些实施例中,所述第一方向与所述第三方向相同。

7、在一些实施例中,所述第一方向与所述第二方向相垂直。

8、在一些实施例中,所述有源区用于定义n型有源层。

9、在一些实施例中,所述反熔丝存储版图还包括:位线区,所述位线区沿所述第一方向延伸,以定义与沿所述第一方向排列的控制晶体管电连接的位线。

10、根据本公开一些实施例,本公开实施例另一方面还提供一种反熔丝存储器,包括:沿第一方向以及第二方向排布的至少两个存储单元,每一所述存储单元包括沿所述第一方向排布的反熔丝晶体管以及控制晶体管,所述反熔丝晶体管的栅极结构包括层叠设置的第一栅介质层以及第一栅极层,所述控制晶体管的栅极结构包括层叠设置的第二栅介质层以及第二栅极层;字线层,所述字线层沿所述第二方向延伸,且与沿所述第二方向排布的所述控制晶体管的所述第二栅极层电连接;电连接层,所述电连接层沿所述第二方向延伸,且与所述反熔丝晶体管的所述第一栅极层电连接;编程控制层,所述编程控制层沿第三方向延伸,且通过所述电连接层与沿所述第一方向排列的所述第一栅极层电连接。

11、在一些实施例中,所述电连接层与所述编程控制层处于同层。

12、在一些实施例中,所述电连接层与所述编程控制层处于不同层;所述反熔丝存储器还包括:导电柱,所述导电柱位于所述电连接层与所述编程控制层之间,且电连接所述电连接层以及所述编程控制层。

13、在一些实施例中,所述第一栅介质层的厚度小于或等于30埃;所述第二栅介质层的厚度小于或等于30埃。

14、在一些实施例中,所述反熔丝存储器还包括:位线层,所述位线层沿所述第一方向延伸,且所述位线层与沿所述第一方向排列的所述控制晶体管电连接。

15、根据本公开一些实施例,本公开实施例又一方面还提供一种反熔丝存储器的设计方法,用于设计上述任一项所述的反熔丝存储器,包括:定义在沿所述第一方向上相邻的两个所述存储单元中进行编程的所述存储单元为第一存储单元,未进行编程的所述存储单元为第二存储单元,所述第二存储单元中的所述控制晶体管与所述反熔丝晶体管相连接的节点定义为连接节点,且所述第一栅极层与所述连接节点之间具有第一寄生电容,所述第二栅极层与所述连接节点之间具有第二寄生电容,定义在进行编程期间,所述第二存储单元中的所述第一栅极层与所述连接节点之间具有压差阈值,所述压差阈值为所述反熔丝晶体管被击穿对应的所述第一栅极层与所述连接节点之间的压差,所述第一存储单元对应的所述编程控制层的电压为编程电压;基于所述编程电压以及所述压差阈值,获取所述第一寄生电容与所述第二寄生电容之间的关系;基于所述第一寄生电容与所述第二寄生电容之间的关系,设计所述第二存储单元中的所述反熔丝晶体管的沟道尺寸和/或所述第一栅介质层的厚度,设计所述第二存储单元中的所述控制晶体管的沟道尺寸和/或所述第二栅介质层的厚度。

16、在一些实施例中,所述第一寄生电容、所述第二寄生电容、所述编程电压以及所述压差阈值满足如下关系:u=r1*u0/(r1+r2),其中,u为小于等于所述压差阈值的任意值,u0为所述编程电压,r1为所述第一寄生电容对应的第一容抗,r2为所述第二寄生电容对应的第二容抗。

17、根据本公开一些实施例,本公开实施例再一方面还提供一种反熔丝存储电路,包括:多个存储单元,每一所述存储单元包括相连接的反熔丝晶体管以及控制晶体管,所述反熔丝晶体管与所述控制晶体管的连接节点定义为参考节点;位线,所述位线连接沿第一方向上排列的所述反熔丝晶体管,且每一所述反熔丝晶体管通过所述控制晶体管电连接所述位线;字线,所述字线连接沿第二方向上排列的所述控制晶体管的栅极,用于根据行选通信号导通被选中的所述控制晶体管,以使所述位线与所述反熔丝晶体管电连接;编程控制线,所述编程控制线连接沿所述第一方向排列的所述反熔丝晶体管的栅极,所述反熔丝晶体管用于根据所述编程控制线提供的编程信号进行编程;其中,所述反熔丝晶体管的栅极与所述参考节点之间具有第一寄生电容,所述控制晶体管的栅极与所述参考节点之间具有第二寄生电容,在选中一所述存储单元的所述反熔丝晶体管进行编程期间,相邻的所述反熔丝晶体管的所述参考节点被耦合至预设电压,且所述预设电压与所述编程信号的电压的差值小于或等于压差阈值,所述压差阈值为所述反熔丝晶体管被击穿对应的栅极与漏极之间的压差。

18、本公开实施例提供的技术方案具有以下优点:

19、上述反熔丝存储版图中,字线区沿第二方向延伸,编程控制区沿第三方向延伸,则字线区的排布方向与编程控制区的排布方向交错,使得共用有源区的相邻存储单元区中的反熔丝晶体管与同一编程控制区电连接的同时,共用有源区的相邻存储单元区中的控制晶体管与不同的字线区电连接。如此,在利用编程控制区对相邻存储单元区中某一存储单元区中的反熔丝晶体管进行编程时,可以利用与该存储单元区电连接的字线区将该存储单元区中的控制晶体管导通,而与该存储单元区共用有源区的另一存储单元区中的控制晶体管与另一字线区电连接,则与该存储单元区共用有源区的另一存储单元区中的控制晶体管不会导通,进而不会对与该存储单元区共用有源区的另一存储单元区中的反熔丝晶体管进行编程,避免对某一存储单元区进行编程时,对与之相邻的存储单元区造成干扰或损伤。此外,为保护与需要进行编程的存储单元区相邻的存储单元区,本公开实施例提供的反熔丝存储版图无需设置预充电区,一方面,有利于缩小反熔丝存储版图的布局面积,从而有利于降低依据反熔丝存储版图制备的反熔丝存储器的成本以及缩小反熔丝存储器的尺寸;另一方面,对某一存储单元区进行编程时,无需进行预充电操作,有利于简化操作时序。

- 还没有人留言评论。精彩留言会获得点赞!