EEPROM及其读写电路的制作方法

eeprom及其读写电路

技术领域

1.本发明涉及电子技术领域,尤其涉及一种eeprom(electrically erasable programmable read-only memory,电可擦除可编程只读存储器)及其读写电路。

背景技术:

2.随着集成电路技术的不断发展,eeprom获得了广泛的应用。现有技术中eeprom的读写通路是分开调控的,存储阵列一页的每一个字节都需要对应一组锁存器,所以eeprom的存储容量越大,对应的器件数量就越多,对于存储阵列较大的芯片来说,制造成本较高、使用功耗也较大,不利于eeprom低功耗,低成本的发展需求。

技术实现要素:

3.本发明要解决的技术问题是为了克服现有技术中eeprom的锁存器存在高成本、高功耗的缺陷,提供一种eeprom及其读写电路。

4.本发明是通过下述技术方案来解决上述技术问题:

5.一方面,本发明提供一种eeprom的读写电路,所述读写电路包括:

6.存储电路和若干组锁存器,每组所述锁存器包括电压切换电路和锁存电路,每组所述锁存器对应传输一个字节的数据;

7.所述电压切换电路包括第一切换电路和第二切换电路;

8.所述锁存电路包括第一锁存电路和第二锁存电路;

9.其中,所述第一锁存电路、所述第一切换电路和所述存储电路依次电连接,所述第二锁存电路、所述第二切换电路和所述存储电路依次电连接;

10.所述第一切换电路包括第一nmos管(n-metal-oxide-semiconductor,一种晶体管),所述第二切换电路包括第二nmos管;

11.其中,所述第一nmos管的栅极与所述第一锁存电路的数据传输端电连接,所述第一nmos管的源极与所述存储电路的第一电压端电连接;

12.第二nmos管的栅极与所述第二锁存电路的字节选择端电连接,所述第二nmos管的源极与所述存储电路的第二电压端电连接。

13.优选地,所述第一nmos管的漏极与第三电压端电连接,所述第三电压端加载高电平时,所述第一nmos管为打开状态。

14.优选地,所述第二nmos的漏极与第四电压端电连接,所述第四电压端用于输入偏置电压。

15.优选地,所述存储电路包括第一选择管、第二选择管和数据存储管,所述第一选择管的输入端与所述第一nmos管的源极电连接;

16.所述第二选择管的输出端与所述第二nmos管的源极电连接;

17.所述第一选择管的输出端与所述数据存储管的输入端电连接,所述数据存储管的输出端与所述第二选择管的输入端电连接。

18.优选地,所述第一选择管包括第三nmos管,所述第二选择管包括第四nmos管,所述数据存储管包括第五nmos管;

19.所述第三nmos管的漏极与所述第一nmos管的源极电连接;

20.所述第四nmos管的源极与所述第二nmos管的源极电连接;

21.所述第三nmos管的源极与所述第五nmos管的漏极电连接,所述第五nmos管的栅极与所述第四nmos管的漏极电连接,所述第五nmos管的源极与第五电压端电连接,所述第五电压端包括悬空和接地两种状态。

22.优选地,所述存储电路包括选择端,所述选择端输入高电平时,所述第一选择管和所述第二选择管处于打开状态。

23.优选地,当进行擦除操作时,通过所述字节选择端将目标字节数据输入至所述锁存器,所述第四电压端输入高电平,所述第三电压端输入低电平,所述选择端输入高电平,所述第五电压端接地;

24.所述第二nmos管、所述第二选择管和所述数据存储管处于打开状态,所述第一nmos管处于关闭状态;

25.所述数据存储管根据接收所述第二nmos管输出的擦除电信号,进行数据擦除操作。

26.优选地,当进行写入操作时,所述数据传输端接收目标数据字节至所述锁存器,所述第三电压端输入高电平,所述第四电压端输入低电平,所述选择端输入高电平,所述第五电压端悬空;

27.所述第一nmos管、所述第一选择管、所述数据存储管处于打开状态,所述第二nmos管处于关闭状态;

28.所述数据存储管接收所述第一nmos管输出的写入电信号,进行数据写入操作。

29.优选地,当进行读操作时,所述字节选择端输入高电压,所述数据传输端输入高电压,所述第三电压端为数据输出端,所述第四电压端输入偏置电压,所述选择端输入高电平,所述第五电压端接地;

30.所述第一nmos管、所述第二nmos管、所述第一选择管和所述数据存储管均处于打开状态;

31.当所述第四电压端为高电平时,所述数据存储管接收所述第二选择管输出的第一电信号,进行存储数据操作;

32.当所述第四电压端为低电平时,所述数据存储管接收所述第一选择管输出的第二电信号,以根据第二电信号将所述存储数据发送至所述第三电压端,进行输出数据的读操作。

33.另一方面,本发明提供一种eeprom,所述eeprom包括上述的eeprom的读写电路。

34.本发明的积极进步效果在于:

35.本发明对eeprom的读写电路进行优化设计,采用电压切换电路读写通路共用的方式,使得eeprom的锁存器中的电压切换电路的器件减半,实现读写电路的读取、写入以及擦除功能的同时,有效减少模拟器件的数量,降低了芯片的成本,简化电路结构,减小了占用空间,满足了eeprom低功耗、低成本的产品需求。

附图说明

36.图1为本发明实施例1的eeprom的读写电路的模块示意图。

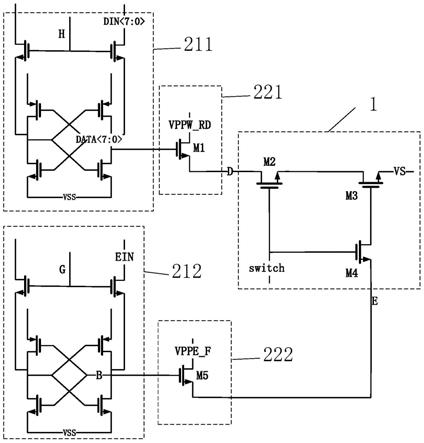

37.图2为本发明实施例1的eeprom的读写电路的电路结构示意图。

具体实施方式

38.下面通过实施例的方式进一步说明本发明,但并不因此将本发明限制在所述的实施例范围之中。

39.实施例1

40.本实施例提供一种eeprom的读写电路,参见图1,读写电路包括:

41.存储电路1和若干组锁存器2,因为在进行读写操作时存储电路1的每个端口所需电压都不相同,因此需要电压切换电路22;对于串行输入的数据而言,eeprom还需要锁存电路21来存储串行输入的数据,然后将锁存电路21中的数据并行存储于阵列中,所以每组锁存器2包括电压切换电路22和锁存电路21,每组锁存器2对应传输一个字节的数据阵列一页有多少个字节,就需要多少组锁存器2。一组锁存器2包括一组电压切换电路22和一组锁存电路21。

42.一组电压切换电路22包括第一切换电路221和第二切换电路222;

43.一组锁存电路21包括第一锁存电路211和第二锁存电路212;

44.其中,第一锁存电路211、第一切换电路221和存储电路1依次电连接,第二锁存电路212、第二切换电路222和存储电路1依次电连接;

45.对于一组锁存器2的电路连接情况,参见图2,第一切换电路221包括第一nmos管m1,第二切换电路222包括第二nmos管m5;

46.其中,第一nmos管m1的栅极与第一锁存电路211的数据传输端data《7:0》电连接,第一nmos管m1的源极与存储电路1的第一电压端d电连接;

47.第二nmos管m5的栅极与第二锁存电路212的字节选择端b电连接,第二nmos管m5的源极与存储电路1的第二电压端e电连接。

48.本实施例的读写电路中只要有一对nmos管(即第一nmos管m1和第二nmos管m5)就可以实现eeprom的读写擦功能,减少了一半的器件,降低了芯片的成本。

49.对于多组锁存器2的电路连接情况,一组锁存器2与另一组锁存器2并联与存储电路1电连接;每组锁存器相互独立,实现原理均与上述一组锁存器的实现原理类似,在此就不再赘述。

50.在一个实施方式中,参见图2,第一nmos管m1的漏极与第三电压端vppw_rd电连接,第三电压端vppw_rd加载高电平时,第一nmos管m1为打开状态。

51.在一个实施方式中,参见图2,第二nmos的漏极与第四电压端vppe_f电连接,第四电压端vppe_f用于输入偏置电压。

52.在一个实施方式中,存储电路1包括第一选择管m2、第二选择管m4和数据存储管m3,第一选择管m2的输入端与第一nmos管m1的源极电连接;

53.第二选择管m4的输出端与第二nmos管m5的源极电连接;

54.第一选择管m2的输出端与数据存储管m3的输入端电连接,数据存储管m3的输出端与第二选择管m4的输入端电连接。

55.本实施例的电压切换电路22简化了与存储电路1的电连接方式,减小了占用空间,降低了芯片的制造成本。

56.在一个实施方式中,参见图2,其中第一选择管m2包括第三nmos管m2,第二选择管m4包括第四nmos管m4,数据存储管m3包括第五nmos管m3。

57.参见图2,第三nmos管m2的漏极与第一nmos管m1的源极电连接;

58.第四nmos管m4的源极与第二nmos管m5的源极电连接;

59.第三nmos管m2的源极与第五nmos管m3的漏极电连接,第五nmos管m3的栅极与第四nmos管m4的漏极电连接,第五nmos管m3的源极与第五电压端vs电连接,第五电压端vs包括悬空和接地两种状态。

60.第一选择管m2、第二选择管m4和数据存储管m3均选择nmos管,优化读写电路的设计,简化电路结构,减少芯片的占用空间。

61.在一个实施方式中,参见图2,存储电路1包括选择端switch,选择端switch输入高电平时,第一选择管m2和第二选择管m4处于打开状态。选择端switch输入高电平,为了保持第一选择管m2和第二选择管m4处于工作状态,接收电压切换电路22的电信号。

62.下面具体说明本实施例eeprom的读写电路的读、写、擦功能的实现原理:

63.1.当进行擦除操作(erase)时,参见下表1:

64.表1

[0065] switchdevserasehv0hv0

[0066]

(1)第二锁存电路212的g端(即第二锁存电路的电压端)接电源电压,第二锁存电路212的ein=1使得擦除操作写入锁存电路;

[0067]

(2)第四电压端vppe_f接高压,第三电压端vppw_rd为低电平;

[0068]

(3)图2中的存储电路1中的选择端switch默认加载高压以打开存储单元的选择管(即第一选择管m2和第二选择管m4);

[0069]

(4)第四电压端vppe_f的高压通过第二nmos管m5传输到数据存储管m3的栅端进行擦除操作。

[0070]

具体地,eeprom的读写电路处于擦除状态时,第四电压端vppe_f输入高电平hv,第三电压端vppw_rd输入低电平lv,选择端switch输入高电平hv,默认加载高压以打开存储电路的选择管(m2和m4),第五电压端vs接地。参见图2,g端输入电源电压,ein端为1,使得擦除操作写入锁存电路21;将选择的字节数据传输给字节选择端b,字节选择端b将目标字节数据输入至第二切换电路222。这时,第二nmos管m5、第二选择管m4和数据存储管m3处于打开状态,第一nmos管m1处于关闭状态;数据存储管m3根据接收第二nmos管m5输出的擦除电信号,进行数据擦除操作。

[0071]

本实施例通过减少一半器件的第二切换电路222,仍然可以实现eeprom擦除操作。

[0072]

2.当进行写入操作(write)时,参见下表2:

[0073]

表2

[0074] switchdevswritehvhv0float

[0075]

(1)第一锁存电路211的h端(即第一锁存电路的电压端)接电源电压,第一锁存电

路211的din《7:0》写入锁存电路;

[0076]

(2)第三电压端vppw_rd接高压,第四电压端vppe_f为低电平;

[0077]

(3)图2中的存储电路1中的选择端switch默认加载高压以打开存储单元的选择管(即第一选择管m2和第二选择管m4);

[0078]

(4)第三电压端vppw_rd的高压通过打开的第一端中管m2传输到数据存储管m3的漏端,进行写入操作。

[0079]

具体地,eeprom的读写电路处于写入状态时,第三电压端vppw_rd输入高电平hv,第四电压端vppe_f输入低电平lv,选择端switch输入高电平hv,默认加载高压以打开存储电路的选择管(m2和m4),第五电压端vs悬空float。参见图2,h端输入电源电压,din《7:0》端输入目标数据字节至数据传输端data《7:0》,数据传输端data《7:0》接收目标数据字节至第一切换电路221。这时第一nmos管m1、第一选择管m2、数据存储管m3处于打开状态,第二nmos管m5处于关闭状态;数据存储管m3接收第一nmos管m1输出的写入电信号,进行数据写入操作。

[0080]

本实施例通过减少一半器件的第一切换电路221,仍然可以实现eeprom写入操作。

[0081]

3.当进行读取操作(read)时,参见下表3:

[0082]

表3

[0083] switchdevsreadlvoutputvb0

[0084]

(1)第二锁存电路212的g端(即第二锁存电路的电压端)接电源电压,第一锁存电路211的din《7:0》和第二锁存电路212的ein端都为高,保证第一nmos管m1和第二nmos管m5为打开状态;

[0085]

(2)第四电压端vppe_f接读操作需要的偏置电压vb,第三电压端vppw_rd为数据输出端;

[0086]

(3)图2中的存储电路1的选择端switch默认加载高压以打开存储单元的选择管(即第一选择管m2和第二选择管m4);

[0087]

(4)第四电压端vppe_f的偏置电压vb通过第二选择管m4传输到数据存储管m3的栅端,进行读取存储数据的操作,通过第一选择管m2传输到第三电压端vppw_rd输出数据。

[0088]

具体地,eeprom的读写电路处于读取状态时,第三电压端vppw_rd为数据输出端,第四电压端vppe_f输入偏置电压vb,选择端switch输入高电平hv,默认加载高压以打开存储电路的选择管(m2和m4),第五电压端vs接地。参见图2,字节选择端b输入高电压,数据传输端data《7:0》输入高电压。第一nmos管m1、第二nmos管m5、第一选择管m2和数据存储管m3均处于打开状态;第四电压端vppe_f为偏置电压端,当第四电压端vppe_f输入高电平hv时,数据存储管m3接收第二选择管m4输出的第一电信号,进行读取存储数据的操作;当第四电压端vppe_f输入低电平lv时,数据存储管m3接收第一选择管m2输出的第二电信号,以根据第二电信号将存储数据发送至第三电压端vppw_rd,进行输出数据的读操作。

[0089]

本实施例通过减少一半器件的电压切换电路22,仍然可以实现eeprom写入操作。

[0090]

本实施例将eeprom的读写电路进行优化设计,将其中的电压切换电路的器件减半,采用读写通路共用的方式,因为一组锁存器对应存储一个字节的数据,所以阵列一页有多少个字节,就需要多少组锁存器,一页的字节数越多,所减少的总器件数越多,对于存储

阵列较大的芯片来说,本实施例的结构对于芯片模拟器件数量的减少尤为明显,降低了芯片的成本,简化电路结构,减小了占用空间,满足了对eeprom低功耗、低成本的产品需求。

[0091]

实施例2

[0092]

本实施例提供一种eeprom,该eeprom包括上述的eeprom的读写电路。

[0093]

本实施例提供的eeprom,与传统的eeprom相比,每一组锁存器的电压切换电路的器件减半,因为一组锁存器对应存储一个字节的数据,所以阵列一页有多少个字节,就需要多少组锁存器,一页的字节数越多,所减少的总器件数越多,对于存储阵列较大的eeprom来说,本实施例的eeprom与传统的eeprom相比,实现读写电路的读取、写入以及擦除功能的同时,有效减少模拟器件的数量,降低了芯片的成本,简化电路结构,减小了占用空间,满足了对eeprom低功耗、低成本的产品需求。

[0094]

虽然以上描述了本发明的具体实施方式,但是本领域的技术人员应当理解,这仅是举例说明,本发明的保护范围是由所附权利要求书限定的。本领域的技术人员在不背离本发明的原理和实质的前提下,可以对这些实施方式做出多种变更或修改,但这些变更和修改均落入本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1