包括双通道前置放大器电路的数据存储设备的制作方法

包括双通道前置放大器电路的数据存储设备

1.相关申请的交叉引用

2.本技术要求于2020年4月29日提交的美国专利申请序列号16/861,565的优先权,该文献据此全文以引用方式并入本文。

背景技术:

3.数据存储设备诸如磁盘驱动器包括磁盘和连接到致动器臂的远侧端部的磁头,该致动器臂通过音圈电机(vcm)绕枢轴旋转,以将磁头径向地定位在磁盘之上。磁盘包括多个径向间隔的同心轨道,用于记录用户数据扇区和嵌入的伺服扇区。嵌入的伺服扇区包括磁头定位信息(例如,磁道地址),所述磁头定位信息由磁头读取并由伺服控制器处理,以在致动器臂从磁道到磁道寻道时控制致动器臂的速度。

4.磁盘驱动器通常包括多个磁盘,每个磁盘具有由相应的磁头访问的顶表面和底表面。即,vcm通常围绕枢轴旋转多个致动器臂,以便基于记录在每个磁盘表面的伺服数据将多个磁头同时定位在相应的磁盘表面上方。图1示出了现有技术的磁盘格式2,其包括由围绕每个伺服磁道的圆周记录的伺服扇区6

0-6n限定的多个伺服磁道4。每个伺服扇区6i包括用于存储周期性图案的前导码8(其允许读取信号的适当的增益调节和时序同步)以及用于存储用于符号同步到伺服数据字段12的特殊图案的同步标记10。伺服数据字段12存储用于在寻道操作期间将磁头定位在目标数据磁道之上的粗略磁头定位信息,诸如伺服磁道地址。每个伺服扇区6i还包括伺服脉冲组14(例如,n伺服脉冲和q伺服脉冲),该伺服脉冲组相对于彼此以及相对于伺服磁道中心线以预定相位被记录。基于相位的伺服脉冲14提供用于在写入/读取操作期间访问数据磁道的同时进行中心线跟踪的精细磁头位置信息。位置误差信号(pes)是通过读取伺服脉冲14来产生的,其中pes表示磁头相对于目标伺服磁道的中心线的测量位置。伺服控制器处理pes以产生施加到磁头致动器(例如,音圈电机)的控制信号,以便沿减小pes的方向在磁盘之上径向地致动磁头。

附图说明

5.图1示出了现有技术的磁盘格式,其包括由伺服扇区限定的多个伺服磁道。

6.图2a示出了根据一个实施方案的数据存储设备,该数据存储设备包括具有在相应磁盘表面上方致动的至少两个磁头的壳体。

7.图2b示出了根据一个实施方案的数据存储设备的操作方法,其中在制造规程期间将制造印刷电路板(pcb)耦接到壳体,并且然后将产品pcb耦接到壳体。

8.图3示出了根据一个实施方案的具有安装到壳体的底表面的pcb的数据存储设备。

9.图4a示出了一个实施方案,其中数据存储设备的壳体包括第一前置放大器电路和第二前置放大器电路,其中制造pcb将通道信号同时施加到每个前置放大器电路。

10.图4b示出了一个实施方案,其中产品pcb将通道信号施加到第一或第二前置放大器电路中的一者。

11.图5示出了一个实施方案,其中壳体包括耦接到多个磁盘的顶部磁头的第一单通

道前置放大器电路和耦接到多个磁盘表面的底部磁头的第二单通道前置放大器电路。

12.图6示出了一个实施方案,其中壳体包括耦接到第一组磁盘表面的顶部/底部磁头的第一双通道前置放大器电路和耦接到第二组磁盘表面的顶部/底部磁头的第二双通道前置放大器电路。

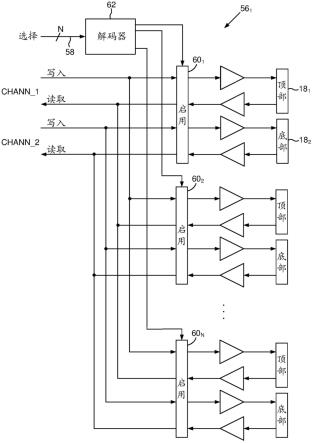

13.图7示出了根据一个实施方案的包括用于将通道信号施加到选定磁盘的顶部/底部磁头的选择电路的双通道前置放大器电路。

具体实施方式

14.图2a示出了根据一个实施方案的呈磁盘驱动器形式的数据存储设备,该数据存储设备包括壳体16,该壳体包括在第一磁盘表面201上方致动的第一磁头181和在第二磁盘表面202上方致动的第二磁头182(未示出)。图2b是根据一个实施方案的流程图,其中将制造印刷电路板(pcb)22耦接到壳体(框24),其中制造pcb 22包括被配置为执行同时访问操作的至少一个双通道。在将制造pcb耦接到壳体时,数据存储设备作为双通道设备操作(框26)。将制造pcb 22与壳体解耦并且将产品pcb 28耦接到壳体(框30),其中产品pcb包括被配置为执行单个访问操作的单个通道。在将产品pcb耦接到壳体时,数据存储设备作为单通道设备操作(框32)。

15.在图2a的实施方案中,每个磁盘表面包括限定多个伺服磁道的多个伺服扇区34

0-34n,其中相对于伺服磁道以相同或不同的径向密度来限定数据磁道36。控制电路处理从磁头发出的读取信号以解调伺服扇区并生成表示磁头的实际位置和相对于目标磁道的目标位置之间的误差的位置误差信号(pes)。控制电路中的伺服控制系统使用合适的补偿滤波器对pes滤波以生成施加到vcm 38的控制信号,该vcm使致动器臂40围绕枢轴旋转以便沿减小pes的方向在磁盘之上径向地致动磁头。在一个实施方案中,还可使用辅助致动器(诸如压电(pzt)致动器)来伺服每个磁头,该辅助致动器被配置为相对于致动器臂40致动悬架,并且/或者被配置为相对于悬架致动磁头。伺服扇区34

0-34n可以包括任何合适的磁头位置信息,诸如用于粗略定位的磁道地址和用于精细定位的伺服脉冲。伺服脉冲可包括任何合适的图案,诸如基于振幅的伺服图案或基于相位的伺服图案(图1)。

16.图3示出了呈磁盘驱动器形式的数据存储设备,其中诸如图2a所示的一个或多个磁盘、磁头堆叠组件和vcm被安装到基部铸件42中,该基部铸件然后用顶覆盖件(未示出)密封以形成壳体16。在该实施方案中,图2a所示的制造pcb 22使用任何合适的耦接特征(例如,夹)来耦接到基部铸件42的底部,其中制造pcb 22包括用于连接到接口电缆(例如,串联ata或scsi)的合适接口连接器。在磁盘驱动器上执行制造规程之后,制造pcb 22可与基部铸件42解耦(例如,未夹紧)并且产品pcb 28可耦接到基础铸件42,之后将数据存储设备运输到客户。

17.在一个实施方案中,图2a所示的壳体16可以是被配置为插入包括制造pcb 22的制造站中的可插拔模块。在执行制造规程之后,可将模块运输到客户,其中模块可插入到产品设备中,诸如将模块插入存储阵列的舱中,其中舱可包括产品pcb 28。

18.可由制造pcb 22执行任何合适的制造规程,其中在一个实施方案中,数据存储设备在制造规程期间作为双通道设备操作,这意味着磁头中的至少两者同时访问相应磁盘表面(例如,同时写入、同时读取或同时写入/读取)。例如,制造pcb 22可执行伺服写入规程,

其中伺服扇区(诸如图2a所示)可组写入到至少两个磁盘表面以便加快伺服写入和/或改善跨磁盘表面的伺服扇区的相干性。在另一个实施方案中,制造pcb 22可执行磁盘表面的缺陷扫描以便绘制出缺陷数据扇区,诸如通过向/从磁盘表面写入/读取测试图案以及基于读取信号检测缺陷。在又一个实施方案中,制造pcb22可执行制造规程以便测量一个或多个部件(例如,磁头部件,诸如写入线圈、写入辅助元件、读取元件、飞行高度致动器、辅助致动器等)的功能,或者测量磁头部件的几何形状,诸如测量写入元件的宽度,或者测量写入/读取元件和/或多个读取元件之间的径向和/或向下磁道偏移。无论执行的制造规程如何,在一个实施方案中,使用至少一个双通道来执行同时访问操作的制造pcb 22可有助于促进和/或加快制造规程。在执行制造规程之后,产品pcb 28可耦接到壳体16并且数据存储设备可作为单通道设备操作。以此方式,与制造pcb 22相比,产品pcb 28可包括更少的部件,由此减小最终产品的成本以及减小数据存储设备的制造时间。

19.图4a示出了根据一个实施方案的制造pcb 22,该制造pcb通过任何合适接口(诸如接口电缆、插入式连接器或无线协议(例如,wi-fi))耦接到壳体16。在该实施方案中,壳体16包括第一单通道前置放大器电路441,该第一单通道前置放大器电路耦接到第一组磁头,诸如在磁盘461的顶表面上方致动的磁头181以及在磁盘461的底表面上方致动的磁头182。壳体16还包括第二单通道前置放大器电路442,该第二单通道前置放大器电路耦接到第二组磁头,诸如在磁盘462的顶表面上方致动的磁头183以及在磁盘462的底表面上方致动的磁头184。在该实施方案中,制造pcb 22包括耦接到第一前置放大器电路441的第一制造控制电路481和耦接到第二前置放大器442的第二制造控制电路482。制造控制电路481和482中的每一者可包括任何合适的电路,诸如读取通道电路、伺服控制电路、被配置为执行存储在计算机可读介质上的指令的微处理器等。当执行访问操作(写入/读取操作)时,第一制造控制电路481通过接口501与第一前置放大器电路441交接,以便从第一组磁头中选择目标磁头以及在写入操作期间传输写入信号并在读取操作期间接收读取信号。类似地,第二制造控制电路482通过接口502与第二前置放大器电路442交接,以便从第二组磁头中选择目标磁头以及在写入操作期间传输写入信号并在读取操作期间接收读取信号。在一个实施方案中,由第一制造控制电路481执行的第一访问操作至少部分地与由第二控制电路482执行的第二访问操作重叠以便执行如上所述的任何合适的制造规程,由此使数据存储设备作为双通道设备操作。

20.图4b示出了根据一个实施方案的产品pcb 28,该产品pcb通过任何合适接口(诸如接口电缆、插入式连接器或无线协议(例如,wi-fi))耦接到壳体16。在该实施方案中,产品pcb 28包括产品控制电路52,该产品控制电路通过接口54耦接到第一前置放大器电路441和第二前置放大器442。在一个实施方案中,产品控制电路52可包括任何合适的电路,诸如读取通道电路、伺服控制电路、被配置为执行存储在计算机可读介质上的指令的微处理器等。当执行访问操作(写入或读取)时,产品控制电路52从第一组磁头或第二组磁头中选择目标磁头,以及在写入操作期间传输写入信号并在读取操作期间接收读取信号。以此方式,产品控制电路52使数据存储设备作为单通道设备操作,以便通过与制造pcb 22相比减小控制电路的成本来减小产品设备的成本。

21.在一个实施方案中,当执行同时操作时,制造pcb 22可执行对磁盘的顶表面和底表面的同时访问操作。例如,在一个实施方案中,制造pcb 22可将伺服扇区组写入到顶表面

和底表面以便改善伺服扇区的相干性。以此方式,当同时对顶表面和底表面执行访问操作时,伺服扇区的相干性使得能够在顶表面和底表面上方同时跟踪磁头。例如,伺服扇区的相干性可使得辅助致动器的冲程能够跟踪顶部数据磁道和底部数据磁道之间的偏差。此外,在磁盘经受热膨胀或相对于被配置为旋转磁盘的主轴马达的主轴的磁盘滑移的情况下,可基本上维持跨顶表面和底表面的伺服扇区的相干性。

22.图5示出了一个实施方案,其中壳体16包括第一单通道前置放大器441,该第一单通道前置放大器耦接到磁盘的顶部磁头以及通过接口501耦接到第一制造控制电路481。壳体16还包括第二单通道前置放大器442,该第二单通道前置放大器耦接到磁盘的底部磁头以及通过接口502耦接到第二制造控制电路482。制造pcb 22通过选择由第一单通道前置放大器电路441服务的顶部磁头以及选择由第二单通道前置放大器电路442服务的对应底部磁头来执行同时访问操作。

23.在图5的实施方案中,在单通道前置放大器电路441和442与顶部磁头和底部磁头之间的布线接口线中存在增加的复杂性(例如,使用柔性电缆)。如图5所示的布线复杂性的这种增加是由于第一单通道前置放大器电路441和第二单通道前置放大器电路442之间的接口线的交织。在图6所示的一个实施方案中,通过使用双通道前置放大器电路561和562来避免图5的布线复杂性,其中每个双通道前置放大器电路通过接口501和502耦接到制造控制电路481和482。第一双通道前置放大器电路561耦接到第一组磁盘(例如,磁盘461)的顶部磁头和底部磁头,并且第二双通道前置放大器电路562耦接到第二组磁盘(例如,磁盘462)的顶部磁头和底部磁头。当执行同时访问操作时,制造pcb 22选择第一双通道前置放大器电路或第二双通道前置放大器电路中的一者以便同时访问目标磁盘的顶表面和底表面。也就是说,在该实施方案中,每个双通道前置放大器电路能够对目标磁盘的顶表面和底表面执行同时访问操作,包括促进通过接口501和502的写入/读取数据的向/从制造pcb 22的同时转移。当壳体16耦接到产品pcb 28时,产品控制电路52耦接到第一双通道前置放大器电路561和第二双通道前置放大器电路562,类似于图4b所示的实施方案。

24.图7示出了双通道前置放大器电路561的示例,其中与制造pcb 22的接口包括用于选择目标磁盘的顶部磁头和底部磁头的选择控制58,以及第一通道的写入/读取接口和第二通道的写入/读取接口。每个通道的写入/读取接口应用于启用电路601至60n,其中每个启用电路(例如,启用电路601)耦接到相应磁盘的顶部磁头和底部磁头(例如,顶部磁头181和底部磁头182)。当执行同时访问操作时,选择控制58由解码器62解码以便激活目标磁盘的启用电路,由此使得能够使用对应的顶部磁头和底部磁头来进行同时访问操作。

25.在一个实施方案中,制造pcb 22可包括能够对多个磁盘的顶表面/底表面执行同时访问命令的控制电路。也就是说,在一个实施方案中,代替接口501和502为线或的(如图6的实施方案所示),在另一个实施方案中,接口501和502可在制造pcb 22的多个控制电路之间多路复用以便实现第一组(对应于第一双通道前置放大器电路561)中的磁盘的顶表面/底表面和第二组(对应于第二双通道前置放大器电路562)中的磁盘的顶表面/底表面的同时访问。

26.在上述实施方案中,制造pcb 22或产品pcb 28与壳体16之间的接口可以任何合适的方式实现。在一个实施方案中,接口可包括并行接口或串行接口,或在另一个实施方案中,并行接口和串行接口的组合。例如,在一个实施方案中,可使用专用接口线来实现写入/

读取线,而某些命令(例如,磁头选择命令)可通过串行接口传输到前置放大器电路。在又一个实施方案中,接口可包括无线接口,诸如合适的wi-fi接口。

27.在一个实施方案中,制造pcb 22或产品pcb 28与壳体16之间的接口可包括控制信号,该控制信号用于控制被配置为在磁盘表面上方径向地致动磁头的主致动器(例如,vcm 38)和一个或多个辅助致动器(例如,pzt)。在一个实施方案中,由产品pcb 28生成的针对辅助致动器的控制信号可被有效地线或(诸如图4b所示),使得磁头中的一者可以精细移动来致动,同时使数据存储设备作为单通道设备操作。

28.在一个实施方案中,在将产品pcb 28耦接到壳体16之后,产品控制电路52可在将数据存储设备运输到客户之前执行附加制造规程。例如,在一个实施方案中,产品控制电路52可执行制造规程,该制造规程验证产品pcb 28的功能以及测试和/或补偿制造pcb 22与产品pcb 28之间的变化。在其他实施方案中,产品pcb 28可执行任何合适的精加工制造规程,诸如执行附加的测试/校准规程,和/或将操作系统和/或校准数据写入磁盘中的一者或多者。

29.在上述实施方案中,数据存储设备的存储介质是磁盘,诸如磁性盘。其他实施方案可采用其他类型的存储介质,诸如磁带。也就是说,图2a所示的壳体16可包括被配置为在任何合适的存储介质上致动写入元件和读取元件的任何合适致动机械部件,以及任选地包括一个或多个单通道和/或双通道前置放大器电路。

30.可以采用任何合适的控制电路来实现上述实施方案中的流程图,例如任何合适的集成电路或电路。例如,控制电路可以在读取通道集成电路内实现,或者在与读取通道分开的部件中实现,诸如数据存储控制器,或者上述某些操作可以由读取通道执行,而其他操作可以由数据存储控制器执行。在一个实施方案中,读取通道和数据存储控制器实现为单独的集成电路,并且在替代实施方案中,它们被制造成单个集成电路或片上系统(soc)。此外,控制电路可以包括合适功率的大规模集成电路(plsi),合适功率的大规模集成电路被实现为单独的集成电路,集成到读取通道或数据存储控制器电路中,或集成到soc中。

31.在一个实施方案中,控制电路包括执行指令的微处理器,该指令可操作以使微处理器执行本文所述的流程图。指令可存储在任何计算机可读介质中。在一个实施方案中,它们可被存储在微处理器外部的或者与soc中的微处理器集成的非易失性半导体存储器上。在另一个实施方案中,指令存储在磁盘上并当磁盘驱动器通电时被读取到易失性半导体存储器中。在另一个实施方案中,控制电路包括合适的逻辑电路,诸如状态机电路。在一些实施方案中,流程图块中的至少一些可以使用模拟电路(例如,模拟比较器、定时器等)来实现,并且在其他实施方案中,块中的一些可以使用数字电路或模拟/数字电路的组合来实现。

32.在各种实施方案中,磁盘驱动器可以包括磁盘驱动器、包括非易失性半导体存储器的混合磁盘驱动器、磁带驱动器等。此外,一些实施方案可以包括诸如计算设备、数据服务器设备、媒体内容存储设备等的电子设备,该电子设备包括如上所述的存储介质和/或控制电路。

33.上述各种特征和过程可以彼此独立地使用,或者可以以各种方式组合。所有可能的组合和子组合均旨在落入本公开的范围内。另外,在一些具体实施中可以省略某些方法、事件或过程块。本文描述的方法和过程也不限于任何特定序列,并且与其相关的块或状态

可以以适当的其他序列执行。例如,所描述的任务或事件可以以不同于具体公开的顺序执行,或者多个可以在单个块或状态中组合。示例性任务或事件可以串行、并行或以某种其他方式执行。可以向所公开的示例性实施方案添加任务或事件或从其中删除任务或事件。本文描述的示例性系统和部件可以与所描述的不同地配置。例如,与所公开的示例性实施方案相比,可以添加、移除或重新布置元件。

34.虽然已经描述了某些示例实施方案,但是这些实施方案仅作为示例呈现,并且不旨在限制本文所公开的发明的范围。因此,上述描述中的任何内容均不旨在暗示任何特定特征、特性、步骤、模块或块是必要的或必不可少的。实际上,本文描述的新颖方法和系统可以各种其他形式体现。此外,在不脱离本文公开的实施方案的实质的情况下,可以对本文描述的方法和系统的形式进行各种省略、替换和改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1