半导体装置的制作方法

半导体装置

1.相关申请的交叉引用

2.本技术要求在2021年4月20日向韩国知识产权局提交的申请号为10-2021-0051054的韩国申请的优先权,该专利申请通过引用被整体合并于此。

技术领域

3.各个实施例总体上涉及半导体电路,并且更具体地涉及包括感测放大器的半导体装置。

背景技术:

4.半导体装置(例如半导体存储装置)的存储单元结构通常可以被划分为折叠式位线结构和开放式位线结构。

5.在折叠式位线结构中,通过其驱动数据的位线(在下文,被称为驱动位线)以及在放大操作中用作参考的位线(在下文,被称为参考位线)相关于感测放大器电路(即,位线感测放大器)而被布置在半导体装置的核心区域中所布置的同一存储单元矩阵区(memory cell mat)中。在开放式位线结构中,驱动位线和参考位线相关于位线感测放大器而被布置在不同的存储单元矩阵区中。因为在驱动位线中生成的噪声和在参考位线中生成的噪声彼此不同,所以开放式位线结构易受这种噪声侵害。在折叠式位线结构的情况下,单位存储单元结构被设计为8f2,而在开放式位线结构的情况下,单位存储单元结构被设计为与8f2相比具有较高集成度的6f2。因此,当考虑相同的数据存储容量时,与具有折叠式位线结构的半导体存储装置相比,具有开放式位线结构的半导体存储装置具有更高的集成度。

6.参考图1,具有开放式位线结构的常规半导体装置10包括置于存储单元矩阵区11至13之间的感测放大器电路21和22。

7.在具有开放式位线结构的半导体装置10中,执行感测和放大的驱动位线bli和blj被布置在第二存储单元矩阵区12中,用作驱动位线bli的参考的参考位线blbi被布置在第一存储单元矩阵区11中,并且用作驱动位线blj的参考的参考位线blbj被布置在第三存储单元矩阵区13中。感测放大器(sa)电路21通过基于参考位线blbi的电压电平来感测和放大驱动位线bli的电平而读取存储在对应的存储单元mc中的数据。感测放大器电路22通过基于参考位线blbj的电压电平来感测和放大驱动位线blj的电平而读取存储在对应的存储单元mc中的数据。在具有开放式位线结构的半导体装置10中,相邻位线之间的噪声可能增加,这可能使半导体装置10的操作性能劣化。

技术实现要素:

8.在实施例中,一种半导体装置可以包括:多个位线;多个感测放大器,其分别耦接到多个位线并且被配置为感测和放大对应的信号;以及,感测放大器驱动信号提供电路,其被配置为通过经由不同的信号线的节点向相邻的感测放大器提供不同的驱动信号来驱动多个感测放大器当中的相邻的感测放大器。

9.在实施例中,一种半导体装置可以包括:多个位线;多个感测放大器,其耦接到多个位线,被划分为多个感测放大器组,并且每个感测放大器被配置为感测和放大耦接到感测放大器的两个位线之间的电压差;以及,感测放大器驱动信号提供电路,其被配置为分别向多个感测放大器组提供多个驱动信号组。

10.在实施例中,一种半导体装置可以包括:第一单元矩阵区,其包括多个驱动位线;第二单元矩阵区,其包括多个参考位线;多个感测放大器,其耦接到多个驱动位线中的一些以及多个参考位线中的一些,并且每个感测放大器被配置为感测和放大耦接到感测放大器的两个位线之间的电压差;以及,感测放大器驱动信号提供电路,其被配置为通过经由不同的信号线的节点向相邻的感测放大器提供不同的驱动信号来驱动多个感测放大器当中的相邻的感测放大器。

11.在实施例中,一种半导体装置可以包括:第一单元矩阵区,其包括多个驱动位线;第二单元矩阵区,其包括多个参考位线;多个感测放大器,其耦接到多个驱动位线中的一些以及多个参考位线中的一些,被划分为多个感测放大器组,并且每个感测放大器被配置为感测和放大耦接到感测放大器的两个位线之间的电压差;以及,感测放大器驱动信号提供电路,其被配置为分别向多个感测放大器组提供多个驱动信号组。

附图说明

12.图1是图示出根据常规技术的具有开放式位线结构的半导体装置的图。

13.图2是图示出根据实施例的半导体装置的配置的图。

14.图3是图示出根据实施例的半导体装置的配置的图。

15.图4是图示出根据实施例的半导体装置的配置的图。

16.图5是图示出根据实施例的半导体装置的配置的图。

17.图6是图示出根据实施例的半导体装置的配置的图。

18.图7是图示出根据实施例的半导体装置的配置的图。

具体实施方式

19.在下文中,以下将通过实施例的各种示例参考附图来描述半导体装置。

20.各个实施例涉及能够降低相邻位线之间的噪声的半导体装置。

21.相邻的感测放大器可以基于多个位线当中的耦接到所述相邻的感测放大器的位线的顺序来确定。

22.感测放大器驱动信号提供电路可以包括驱动器,驱动器被配置为向不同的信号线输出不同的驱动信号,不同的驱动信号是通过对响应于感测放大器控制信号所生成的信号进行分支而生成的。

23.感测放大器驱动信号提供电路可以包括多个驱动器,多个驱动器被配置为向不同的信号线输出通过响应于感测放大器控制信号而使用第一电源所生成的不同的驱动信号。

24.感测放大器驱动信号提供电路可以包括多个驱动器,多个驱动器被配置为向不同的信号线输出通过响应于感测放大器控制信号而使用多个电源所生成的不同的驱动信号。

25.多个感测放大器组可以包括第一感测放大器组和第二感测放大器组。第一感测放大器组可以耦接到多个位线当中的偶序号的位线,而第二感测放大器组可以耦接到多个位

线当中的奇序号的位线。

26.图2是图示出根据实施例的半导体装置100的配置的图。

27.参考图2,根据实施例的半导体装置100可以包括命令解码器200、感测放大器控制电路300、感测放大器驱动信号提供电路400、存储单元阵列110和感测放大器电路500。

28.命令解码器200可以响应于命令cmd来生成激活信号act和预充电信号pcg。除激活信号act和和预充电信号pcg之外,命令解码器200可以生成未示出的读信号、刷新信号等等。感测放大器控制电路300可以响应于激活信号act和和预充电信号pcg来生成多个感测放大器控制信号。感测放大器驱动信号提供电路400可以响应于从感测放大器控制电路300输出的多个感测放大器控制信号来生成至少一个驱动信号组。存储单元阵列110可以具有开放式位线结构。存储单元阵列110可以被划分为多个单元矩阵区。存储单元阵列110可以包括易失性存储器和非易失性存储器中的至少一个。易失性存储器的示例可以包括sram(静态ram)、dram(动态ram)和sdram(同步dram)。非易失性存储器的示例可以包括rom(只读存储器)、prom(可编程rom)、eeprom(电可擦除且可编程序rom)、eprom(电可编程rom)、闪速存储器、pram(相变ram)、mram(磁性ram)、rram(电阻式ram)和fram(铁电ram)。感测放大器电路500可以包括多个感测放大器。感测放大器电路500可以通过被施加从感测放大器驱动信号提供电路400输出的至少一个驱动信号组而被激活。激活的感测放大器可以感测和放大驱动位线bl和参考位线blb之间的电压差。在实施例中,激活的感测放大器可以感测和放大从驱动位线bl和参考位线blb接收的对应的信号。例如,在实施例中,激活的感测放大器可以感测和放大驱动位线bl的对应的信号与参考位线blb的对应的信号之间的电压差。

29.感测放大器电路500的多个感测放大器当中的相邻的感测放大器可以被配置为通过不同的信号线的节点被提供驱动信号。可以基于耦接到相邻的感测放大器的位线的顺序来确定相邻的感测放大器。在多个感测放大器当中,第一感测放大器可以被配置为通过第一信号线的节点被提供驱动信号,并且与第一感测放大器相邻的第二感测放大器可以被配置为通过第二信号线的节点被提供驱动信号。而且,与第二感测放大器相邻的第三感测放大器可以被配置为通过第一信号线的节点被提供驱动信号或通过第三信号线的节点被提供驱动信号。

30.感测放大器电路500的多个感测放大器可以被划分为多个组,并且每个组可以根据通过单独信号线组所提供的单独驱动信号组被驱动。例如,当感测放大器电路500的多个感测放大器被划分为第一组和第二组时,可以根据第一驱动信号组来驱动第一组,并且可以根据第二驱动信号组来驱动第二组。第一组可以是耦接到偶序号的位线的感测放大器,而第二组可以是耦接到奇序号的位线的感测放大器。

31.图3是图示出根据实施例的半导体装置101的配置的图。图3图示出图2的半导体装置100的一些部件(例如,感测放大器驱动信号提供电路400、存储单元阵列110和感测放大器电路500)的配置示例。

32.参考图3,根据实施例的半导体装置101可以包括单元矩阵区(cell mat)111、感测放大器驱动信号提供电路401和感测放大器电路600。半导体装置101还可以包括字线驱动器swd,用于根据行地址解码结果来驱动单元矩阵区111的字线wl。

33.因为单元矩阵区111是图2的存储单元阵列110的一部分,所以单元矩阵区111可以以与存储单元阵列110相同的方式被配置为具有开放式位线结构。单元矩阵区111可以包括

多个存储单元mc以及耦接到多个存储单元mc的多个位线bl0至bl7和多个字线wl。因为单元矩阵区111具有开放式位线结构,所以相对于感测放大器电路600的上部单元矩阵区111的多个位线bl0至bl7当中的一些驱动位线bl0、bl2、bl4和bl6以及相对于感测放大器电路600的下部单元矩阵区(未图示)的多个位线blb0至blb7当中的一些参考位线blb0、blb2、blb4和blb6可以耦接到感测放大器电路600。多个位线bl0至bl7当中的其余驱动位线bl1、bl3、bl5和bl7可以耦接到相对于上部单元矩阵区111的上部感测放大器电路(未图示)。

34.感测放大器驱动信号提供电路401可以响应于从感测放大器控制电路300输出的感测放大器控制信号sap和san来生成驱动信号组rto和sb,并且可以向信号线组416和417施加所生成的驱动信号组rto和sb。感测放大器驱动信号提供电路401可以响应于位线均衡信号bleq而将驱动信号组rto和sb预充电到位线预充电电压vblp的电平。

35.感测放大器驱动信号提供电路401可以包括第一驱动器410、第二驱动器411和预充电电路412。

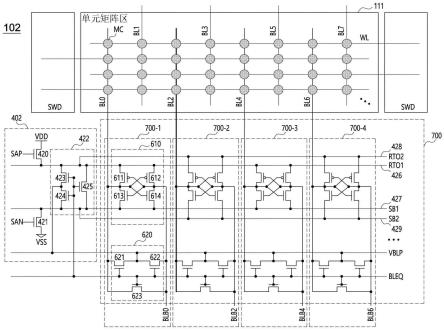

36.第一驱动器410可以通过响应于第一感测放大器控制信号sap使用电源电压vdd来生成驱动信号组rto和sb中的第一驱动信号rto,并且可以向第一信号线416施加第一驱动信号rto。当第一感测放大器控制信号sap具有高电平时,第一驱动器410可以将电源电压vdd生成作为第一驱动信号rto。第一驱动器410可以由晶体管来配置。该晶体管可以具有被施加电源电压vdd的源极端子、被输入第一感测放大器控制信号sap的栅极端子以及耦接到第一信号线416的漏极端子。

37.第二驱动器411可以通过响应于第二感测放大器控制信号san使用接地电压vss来生成驱动信号组rto和sb中的第二驱动信号sb,并且可以向第二信号线417施加第二驱动信号sb。当第二感测放大器控制信号san具有高电平时,第二驱动器411可以将接地电压vss生成作为第二驱动信号sb。第二驱动器411可以由晶体管来配置。该晶体管可以具有被施加接地电压vss的源极端子、被输入第二感测放大器控制信号san的栅极端子以及耦接到第二信号线417的漏极端子。

38.预充电电路412可以响应于位线均衡信号bleq而将驱动信号组rto和sb预充电到位线预充电电压vblp的电平。预充电电路412可以包括第一至第三晶体管413至415。第一晶体管413可以具有通过第一信号线416接收第一驱动信号rto的漏极端子以及被施加位线预充电电压vblp的源极端子。第二晶体管414可以具有通过第二信号线417接收第二驱动信号sb的漏极端子以及被施加位线预充电电压vblp的源极端子。第三晶体管415可以具有通过第一信号线416接收第一驱动信号rto的漏极端子以及通过第二信号线417接收第二驱动信号sb的源极端子。位线均衡信号bleq可以被共同输入到第一至第三晶体管413至415的栅极端子。

39.感测放大器电路600可以包括多个感测放大器600-1至600-4。多个感测放大器600-1至600-4当中的相邻的感测放大器可以被配置为通过不同的信号线的节点来接收驱动信号。多个感测放大器600-1至600-4可以通过第一信号线416共同接收第一驱动信号rto、可以通过第二信号线417共同接收第二驱动信号sb,并且可以响应于第一驱动信号rto和第二驱动信号sb来感测和放大驱动位线bl0、bl2、bl4和bl6与参考位线blb0、blb2、blb4和blb6之间的电压电平差。多个感测放大器600-1至600-4可以响应于位线均衡信号bleq而将驱动位线bl0、bl2、bl4和bl6以及参考位线blb0、blb2、blb4和blb6预充电到位线预充电

电压vblp的电平。多个感测放大器600-1至600-4可以以彼此相同的方式来配置。

40.第一感测放大器600-1可以响应于第一驱动信号rto和第二驱动信号sb来感测和放大驱动位线bl0和参考位线blb0之间的电压电平差。第一感测放大器600-1可以包括感测单元610和预充电电路620。感测单元610可以包括具有交叉耦接结构的第一至第四晶体管611至614。第一晶体管611可以具有通过第一信号线416接收第一驱动信号rto的源极端子以及耦接到驱动位线bl0的漏极端子。第二晶体管612可以具有通过第一信号线416接收第一驱动信号rto的源极端子以及耦接到参考位线blb0的漏极端子。第三晶体管613可以具有通过第二信号线417接收第二驱动信号sb的源极端子以及耦接到驱动位线bl0的漏极端子。所述第四晶体管614可以具有通过第二信号线417接收第二驱动信号sb的源极端子以及耦接到参考位线blb0的漏极端子。第一晶体管611的栅极端子和第三晶体管613的栅极端子可以耦接到参考位线blb0。第二晶体管612的栅极端子和第四晶体管614的栅极端子可以耦接到驱动位线blb0。预充电电路620可以包括第一至第三晶体管621至623。第一晶体管621可以具有耦接到驱动位线bl0的漏极端子以及被施加位线预充电电压vblp的源极端子。第二晶体管622可以具有耦接到参考位线blb0的漏极端子以及被施加位线预充电电压vblp的源极端子。第三晶体管623可以具有耦接到驱动位线bl0的漏极端子以及耦接到参考位线blb0的源极端子。位线均衡信号bleq可以被共同输入到第一至第三晶体管621至623的栅极端子。

41.第二感测放大器600-2可以响应于第一驱动信号rto和第二驱动信号sb来感测和放大驱动位线bl2和参考位线blb2之间的电压电平差。第三感测放大器600-3可以响应于第一驱动信号rto和第二驱动信号sb来感测和放大驱动位线bl4和参考位线blb4之间的电压电平差。第四感测放大器600-4可以响应于第一驱动信号rto和第二驱动信号sb来感测和放大驱动位线bl6和参考位线blb6之间的电压电平差。

42.如上所述的根据图3的存储单元、位线、字线和感测放大器的数量仅仅是根据实施例的示例并不被限制,并且可以根据存储容量和设计方法而改变。

43.图4是图示出根据实施例的半导体装置102的配置的图。

44.参考图4,根据实施例的半导体装置102可以包括单元矩阵区111、感测放大器驱动信号提供电路402和感测放大器电路700。半导体装置102还可以包括字线驱动器swd,用于根据行地址解码结果来驱动单元矩阵区111的字线wl。

45.单元矩阵区111可以以与图3中相同的方式来配置。因为单元矩阵区111具有开放式位线结构,所以相对于感测放大器电路700的上部单元矩阵区111的多个位线bl0至bl7当中的一些驱动位线bl0、bl2、bl4和bl6以及相对于感测放大器电路700的下部单元矩阵区(未图示)的多个位线blb0至blb7当中的一些参考位线blb0、blb2、blb4和blb6可以耦接到感测放大器电路700。多个位线bl0至bl7当中的其余驱动位线bl1、bl3、bl5和bl7可以耦接到相对于上部单元矩阵区111的上部感测放大器电路(未图示)。在下文中,包括一些驱动位线bl0、bl2、bl4和bl6当中的偶序号的驱动位线bl0和bl4的第一组将被称为偶数驱动位线,而包括一些驱动位线bl0、bl2、bl4和bl6当中的奇序号的驱动位线bl2和bl6的第二组将被称为奇数驱动位线。而且,包括一些参考位线blb0、blb2、blb4和blb6当中的偶序号的参考位线blb0和blb4的第一组将被称为偶数参考位线,而包括一些参考位线blb0、blb2、blb4和blb6当中的奇序号的参考位线blb2和blb6的第二组将被称为奇数参考位线。例如,第一位

线,即,第一驱动位线bl0,可以是偶数驱动位线,而第二位线,即,第二驱动位线bl2可以是奇数驱动位线。

46.感测放大器驱动信号提供电路402可以响应于从感测放大器控制电路300输出的感测放大器控制信号sap和san来生成第一驱动信号组rto1和sb1以及第二驱动信号组rto2和sb2、可以向第一信号线组426和427施加第一驱动信号组rto1和sb1、并且可以向第二信号线组428和429施加第二驱动信号组rto2和sb2。在下文中,第一驱动信号组rto1和sb1中的驱动信号rto1可以被称为第一驱动信号rto1,而第一驱动信号组rto1和sb1中的驱动信号sb1可以被称为第二驱动信号sb1。第二驱动信号组rto2和sb2中的驱动信号rto2可以被称为第三驱动信号rto2,而第二驱动信号组rto2和sb2中的驱动信号sb2可以被称为第四驱动信号sb2。第一信号线组426和427中的信号线426可以被称为第一信号线426,而第一信号线组426和427中的信号线427可以被称为第二信号线427。第二信号线组428和429中的信号线428可以被称为第三信号线428,而第二信号线组428和429中的信号线429可以被称为第四信号线429。

47.感测放大器驱动信号提供电路402可以响应于位线均衡信号bleq而将第一驱动信号组rto1和sb1以及第二驱动信号组rto2和sb2预充电到位线预充电电压vblp的电平。

48.感测放大器驱动信号提供电路402可以包括第一驱动器420、第二驱动器421和预充电电路422。

49.第一驱动器420可以响应于第一感测放大器控制信号sap来生成第一驱动信号rto1和第三驱动信号rto2、可以向第一信号线426施加第一驱动信号rto1、并且可以向从第一信号线426分支而来的第三信号线428施加第三驱动信号rto2。第一驱动器420可以由晶体管来配置。该晶体管可以具有被施加电源电压vdd的源极端子、被输入第一感测放大器控制信号sap的栅极端子以及耦接到第一信号线426的漏极端子。当第一感测放大器控制信号sap具有高电平时,第一驱动器420可以将电源电压vdd生成作为第一驱动信号rto1和第三驱动信号rto2。

50.第二驱动器421可以响应于第二感测放大器控制信号san来生成第二驱动信号sb1和第四驱动信号sb2、可以向第二信号线427施加第二驱动信号sb1、并且可以向从第二信号线427分支而来的第四信号线429施加第四驱动信号sb2。第二驱动器421可以由晶体管来配置。该晶体管可以具有被施加接地电压vss的源极端子、被输入第二感测放大器控制信号san的栅极端子以及耦接到第二信号线427的漏极端子。当第二感测放大器控制信号san具有高电平时,第二驱动器421可以将接地电压vss生成作为第二驱动信号sb1和第四驱动信号sb2。

51.预充电电路422可以响应于位线均衡信号bleq而将第一驱动信号组rto1和sb1以及第二驱动信号组rto2和sb2预充电到位线预充电电压vblp的电平。预充电电路422可以包括第一至第三晶体管423至425。第一晶体管423可以具有:通过第一信号线426和第三信号线428接收第一驱动信号rto1和第三驱动信号rto2的漏极端子,以及被施加位线预充电电压vblp的源极端子。第二晶体管424可以具有:通过第二信号线427和第四信号线429接收第二驱动信号sb1和第四驱动信号sb2的漏极端子,以及被施加位线预充电电压vblp的源极端子。第三晶体管425可以具有:通过第一信号线426和第三信号线428接收第一驱动信号rto1和第三驱动信号rto2的漏极端子,以及通过第二信号线427和第四信号线429接收第二驱动

信号sb1和第四驱动信号sb2的源极端子。位线均衡信号bleq可以被共同输入到第一至第三晶体管423至425的栅极端子。

52.感测放大器电路700可以包括多个感测放大器700-1至700-4。多个感测放大器700-1至700-4的电路配置可以与图3中的相同。多个感测放大器700-1至700-4当中的相邻的感测放大器可以被配置为通过不同的信号线的节点来接收驱动信号。可以基于耦接到相邻的感测放大器的位线的顺序来确定相邻的感测放大器。在多个感测放大器700-1至700-4当中,耦接到偶数驱动位线bl0和bl4以及偶数参考位线blb0和blb4的感测放大器700-1和700-3可以响应于第一驱动信号组rto1和sb1来被驱动。在多个感测放大器700-1至700-4当中,耦接到奇数驱动位线bl2和bl6以及奇数参考位线blb2和blb6的感测放大器700-2和700-4可以响应于第二驱动信号组rto2和sb2来被驱动。多个感测放大器700-1至700-4可以响应于位线均衡信号bleq而将驱动位线bl0、bl2、bl4和bl6以及参考位线blb0、blb2、blb4和blb6预充电到位线预充电电压vblp的电平。

53.第一感测放大器700-1可以响应于第一驱动信号rto1和第二驱动信号sb1来感测和放大第一偶数驱动位线bl0和第一偶数参考位线blb0之间的电压电平差。第二感测放大器700-2可以响应于第三驱动信号rto2和第四驱动信号sb2来感测和放大第一奇数驱动位线bl2和第一奇数参考位线blb2之间的电压电平差。第三感测放大器700-3可以响应于第一驱动信号rto1和第二驱动信号sb1来感测和放大第二偶数驱动位线bl4和第二偶数参考位线blb4之间的电压电平差。第四感测放大器700-4可以响应于第三驱动信号rto2和第四驱动信号sb2来感测和放大第二奇数驱动位线bl6和第二奇数参考位线blb6之间的电压电平差。

54.如上所述的根据图4的存储单元、位线、字线和感测放大器的数量仅仅是根据实施例的示例并不被限制,并且可以根据存储容量和设计方法而改变。在以上描述的实施例中,基于包括偶序号的位线的第一组和包括奇序号的位线的第二组来对多个感测放大器进行划分,并且分别通过经由单独的信号线所提供的第一驱动信号组rto1和sb1以及第二驱动信号组rto2和sb2来激活划分的感测放大器组,这使得可以降低相邻位线之间的噪声。

55.图5是图示出根据实施例的半导体装置103的配置的图。

56.参考图5,根据实施例的半导体装置103可以包括单元矩阵区111、感测放大器驱动信号提供电路403和感测放大器电路800。半导体装置103还可以包括字线驱动器swd,用于根据行地址解码结果来驱动单元矩阵区111的字线wl。

57.单元矩阵区111可以以与图4中相同的方式来配置。

58.感测放大器驱动信号提供电路403可以响应于从感测放大器控制电路300输出的感测放大器控制信号sap和san而通过使用单独的驱动器来生成第一驱动信号组rto1和sb1以及第二驱动信号组rto2和sb2的相应的信号,可以向第一信号线组436和437施加第一驱动信号组rto1和sb1,并且可以向第二信号线组438和439施加第二驱动信号组rto2和sb2。第一信号线组436和437中的信号线436可以被称为第一信号线436,而第一信号线组436和437中的信号线437可以被称为第二信号线437。第二信号线组438和439中的信号线438可以被称为第三信号线438,而第二信号线组438和439中的信号线439可以被称为第四信号线439。感测放大器驱动信号提供电路403可以响应于位线均衡信号bleq而将第一驱动信号组rto1和sb1以及第二驱动信号组rto2和sb2预充电到位线预充电电压vblp的电平。

59.感测放大器驱动信号提供电路403可以包括第一驱动器430、第二驱动器431、第三驱动器432、第四驱动器433、第一预充电电路434和第二预充电电路435。

60.第一驱动器430可以响应于第一感测放大器控制信号sap来生成第一驱动信号rto1,并且可以向第一信号线436施加第一驱动信号rto1。第一驱动器430可以由晶体管来配置。该晶体管可以具有被施加电源电压vdd的源极端子、被输入第一感测放大器控制信号sap的栅极端子以及耦接到第一信号线436的漏极端子。当第一感测放大器控制信号sap具有高电平时,第一驱动器430可以输出电源电压vdd作为第一驱动信号rto1。第二驱动器431可以响应于第二感测放大器控制信号san来生成第二驱动信号sb1,并且可以向第二信号线437施加第二驱动信号sb1。

61.第二驱动器431可以由晶体管来配置。该晶体管可以具有被施加接地电压vss的源极端子、被输入第二感测放大器控制信号san的栅极端子以及耦接到第二信号线437的漏极端子。当高第二感测放大器控制信号san具有高电平时,第二驱动器431可以输出接地电压vss作为第二驱动信号sb1。

62.第三驱动器432可以响应于第一感测放大器控制信号sap来生成第三驱动信号rto2,并且可以向第三信号线438施加第三驱动信号rto2。第三驱动器432可以由晶体管来配置。该晶体管可以具有被施加电源电压vdd的源极端子、被输入第一感测放大器控制信号sap的栅极端子以及耦接到第三信号线438的漏极端子。当第一感测放大器控制信号sap具有高电平时,第三驱动器432可以输出电源电压vdd作为第三驱动信号rto2。

63.第四驱动器433可以响应于第二感测放大器控制信号san来生成第四驱动信号sb2,并且可以向第四信号线439施加第四驱动信号sb2。第四驱动器433可以由晶体管来配置。该晶体管可以具有被施加接地电压vss的源极端子、被输入第二感测放大器控制信号san的栅极端子以及耦接到第四信号线439的漏极端子。当第二感测放大器控制信号san具有高电平时,第四驱动器433可以输出接地电压vss作为第四驱动信号sb2。

64.第一预充电电路434可以响应于位线均衡信号bleq而将第一驱动信号组rto1和sb1预充电到位线预充电电压vblp的电平。第一预充电电路434可以以与图4中的预充电电路412相同的方式来配置。

65.第二预充电电路435可以响应于位线均衡信号bleq而将第二驱动信号组rto2和sb2预充电到位线预充电电压vblp的电平。第二预充电电路435可以以与图4中相同的方式来配置。

66.感测放大器电路800可以包括多个感测放大器800-1至800-4。多个感测放大器800-1至800-4的电路配置可以与图4中的相同。多个感测放大器800-1至800-4当中的相邻的感测放大器可以被配置为通过不同的信号线的节点来接收驱动信号。可以基于耦接到相邻的感测放大器的位线的顺序来确定相邻的感测放大器。在多个感测放大器800-1至800-4当中,耦接到偶数驱动位线bl0和bl4以及偶数参考位线blb0和blb4的感测放大器800-1和800-3可以响应于第一驱动信号组rto1和sb1来被驱动。在多个感测放大器800-1至800-4当中,耦接到奇数驱动位线bl2和bl6以及奇数参考位线blb2和blb6的感测放大器800-2和800-4可以响应于第二驱动信号组rto2和sb2来被驱动。多个感测放大器800-1至800-4可以响应于位线均衡信号bleq而将驱动位线bl0、bl2、bl4和bl6以及参考位线blb0、blb2、blb4和blb6预充电到位线预充电电压vblp的电平。

67.第一感测放大器800-1可以响应于第一驱动信号rto1和第二驱动信号sb1来感测和放大第一偶数驱动位线bl0和第一偶数参考位线blb0之间的电压电平差。第二感测放大器800-2可以响应于第三驱动信号rto2和第四驱动信号sb2来感测和放大第一奇数驱动位线bl2和第一奇数参考位线blb2之间的电压电平差。第三感测放大器800-3可以响应于第一驱动信号rto1和第二驱动信号sb1来感测和放大第二偶数驱动位线bl4和第二偶数参考位线blb4之间的电压电平差。第四感测放大器800-4可以响应于第三驱动信号rto2和第四驱动信号sb2来感测和放大第二奇数驱动位线bl6和第二奇数参考位线blb6之间的电压电平差。

68.如上所述的根据图5的存储单元、位线、字线和感测放大器的数量仅仅是根据实施例的示例并不被限制,并且可以根据存储容量和设计方法而改变。在以上描述的实施例中,基于包括偶序号的位线的第一组和包括奇序号的位线的第二组来对多个感测放大器进行划分,并且分别通过使用单独的驱动器所生成的第一驱动信号组rto1和sb1以及第二驱动信号组rto2和sb2来激活划分的感测放大器组,这使得可以降低相邻位线之间的噪声。

69.图6是图示出根据实施例的半导体装置104的配置的图。

70.参考图6,根据实施例的半导体装置104可以包括单元矩阵区111、感测放大器驱动信号提供电路404和感测放大器电路900。半导体装置104还可以包括字线驱动器swd,用于根据行地址解码结果来驱动单元矩阵区111的字线wl。

71.单元矩阵区111可以以与图4中相同的方式来配置。

72.感测放大器驱动信号提供电路404可以响应于从感测放大器控制电路300输出的感测放大器控制信号sap和san而通过使用单独的驱动器和单独的电源来生成第一驱动信号组rto1和sb1以及第二驱动信号组rto2和sb2的相应的信号,可以向第一信号线组446和447施加第一驱动信号组rto1和sb1,并且可以向第二信号线组448和449施加第二驱动信号组rto2和sb2。第一信号线组446和447中的信号线446可以被称为第一信号线446,而第一信号线组446和447中的信号线447可以被称为第二信号线447。第二信号线组448和449中的信号线448可以被称为第三信号线448,而第二信号线组448和449中的信号线449可以被称为第四信号线449。感测放大器驱动信号提供电路404可以响应于位线均衡信号bleq而将第一驱动信号组rto1和sb1以及第二驱动信号组rto2和sb2预充电到位线预充电电压vblp的电平。

73.感测放大器驱动信号提供电路404可以包括第一驱动器440、第二驱动器441、第三驱动器442、第四驱动器443、第一预充电电路444和第二预充电电路445。

74.第一驱动器440可以响应于第一感测放大器控制信号sap来生成第一驱动信号rto1,并且可以向第一信号线446施加第一驱动信号rto1。第一驱动器440可以由晶体管来配置。该晶体管可以具有被施加第一电源电压vdd_ev的源极端子、被输入第一感测放大器控制信号sap的栅极端子以及耦接到第一信号线446的漏极端子。当第一感测放大器控制信号sap具有高电平时,第一驱动器440可以输出第一电源电压vdd_ev作为第一驱动信号rto1。

75.第二驱动器441可以响应于第二感测放大器控制信号san来生成第二驱动信号sb1,并且可以向第二信号线447施加第二驱动信号sb1。第二驱动器441可以由晶体管来配置。该晶体管可以具有被施加第一接地电压vss_ev的源极端子、被输入第二感测放大器控

制信号san的栅极端子以及耦接到第二信号线447的漏极端子。当第二感测放大器控制信号san具有高电平时,第二驱动器441可以输出第一接地电压vss_ev作为第二驱动信号sb1。

76.第三驱动器442可以响应于第一感测放大器控制信号sap来生成第三驱动信号rto2,并且可以向第三信号线448施加第三驱动信号rto2。第三驱动器442可以由晶体管来配置。该晶体管可以具有被施加第二电源电压vdd_od的源极端子、被输入第一感测放大器控制信号sap的栅极端子以及耦接到第三信号线448的漏极端子。当第一感测放大器控制信号sap具有高电平时,第三驱动器442可以输出第二电源电压vdd_od作为第三驱动信号rto2。

77.第四驱动器443可以响应于第二感测放大器控制信号san来生成第四驱动信号sb2,并且可以向第四信号线449施加第四驱动信号sb2。第四驱动器443可以由晶体管来配置。该晶体管可以具有被施加第二接地电压vss_od的源极端子、被输入第二感测放大器控制信号san的栅极端子以及耦接到第四信号线449的漏极端子。当第二感测放大器控制信号san具有高电平时,第四驱动器443可以输出第二接地电压vss_od作为第四驱动信号sb2。

78.第一预充电电路444可以响应于位线均衡信号bleq而将第一驱动信号组rto1和sb1预充电到位线预充电电压vblp的电平。第一预充电电路444可以以与在图3中预充电电路412相同的方式来配置。

79.第二预充电电路445可以响应于位线均衡信号bleq而将第二驱动信号组rto2和sb2预充电到位线预充电电压vblp的电平。第二预充电电路445可以以与图4中相同的方式来配置。

80.感测放大器电路900可以包括多个感测放大器900-1至900-4。多个感测放大器900-1至900-4的电路配置可以与图4中的相同。多个感测放大器900-1至900-4当中的相邻的感测放大器可以被配置为通过不同的信号线的节点来接收驱动信号。可以基于耦接到相邻的感测放大器的位线的顺序来确定相邻的感测放大器。在多个感测放大器900-1至900-4当中,耦接到偶数驱动位线bl0和bl4以及偶数参考位线blb0和blb4的感测放大器900-1和900-3可以响应于第一驱动信号组rto1和sb1来被驱动。在多个感测放大器900-1至900-4当中,耦接到奇数驱动位线bl2和bl6以及奇数参考位线blb2和blb6的感测放大器900-2和900-4可以响应于第二驱动信号组rto2和sb2来被驱动。多个感测放大器900-1至900-4可以响应于位线均衡信号bleq而将驱动位线bl0、bl2、bl4和bl6以及参考位线blb0、blb2、blb4和blb6预充电到位线预充电电压vblp的电平。

81.如上所述的根据图6的存储单元、位线、字线和感测放大器的数量仅仅是根据实施例的示例并不被限制,并且可以根据存储容量和设计方法而改变。在以上描述的实施例中,基于包括偶序号的位线的第一组和包括奇序号的位线的第二组来对多个感测放大器进行划分,并且分别通过使用单独的驱动器和单独的电源所生成的第一驱动信号组rto1和sb1以及第二驱动信号组rto2和sb2来驱动划分的感测放大器组,这使得可以降低相邻位线之间的噪声。

82.图7是图示出根据实施例的半导体装置105的配置的图。

83.参考图7,根据实施例的半导体装置105可以包括第一单元矩阵区112、第二单元矩阵区113、感测放大器驱动信号提供电路405和感测放大器电路1000。

84.因为第一单元矩阵区112是图2的存储单元阵列110的一部分,所以第一单元矩阵

区112可以以与存储单元阵列110相同的方式被配置为具有开放式位线结构。第一单元矩阵区112可以包括多个驱动位线bl0至bl15。尽管未图示,第一单元矩阵区112可以进一步包括多个存储单元mc以及耦接到多个存储单元mc的多个字线wl。因为第一单元矩阵区112具有开放式位线结构,所以多个驱动位线bl0至bl15当中的一些驱动位线bl0、bl2、bl4、bl6、bl8、bl10、bl12和bl14可以耦接到感测放大器电路1000。

85.第二单元矩阵区113也可以被配置为具有开放式位线结构。第二单元矩阵区113可以包括多个参考位线blb0至blb15。尽管未图示,第二单元矩阵区113可以进一步包括多个存储单元mc以及耦接到多个存储单元mc的多个字线wl。因为第二单元矩阵区113具有开放式位线结构,所以多个参考位线blb0至blb15当中的一些参考位线blb0、blb2、blb4、blb6、blb8、blb10、blb12和blb14可以耦接到感测放大器电路1000。

86.感测放大器驱动信号提供电路405可以响应于从感测放大器控制电路300输出的感测放大器控制信号sap和san来生成第一驱动信号组rto1和sb1、第二驱动信号组rto2和sb2、第三驱动信号组rto3和sb3,以及第四驱动信号组rto4和sb4。感测放大器驱动信号提供电路405可以向第一信号线组451和452施加第一驱动信号组rto1和sb1、可以向第二信号线组453和454施加第二驱动信号组rto2和sb2、可以向第三信号线组455和456施加第三驱动信号组rto3和sb3,并且可以向第四信号线组457和458施加第四驱动信号组rto4和sb4。第一驱动信号组rto1和sb1中的驱动信号rto1可以被称为第一驱动信号rto1,而第一驱动信号组rto1和sb1中的驱动信号sb1可以被称为第二驱动信号sb1。第二驱动信号组rto2和sb2中的驱动信号rto2可以被称为第三驱动信号rto2,而第二驱动信号组rto2和sb2中的驱动信号sb2可以被称为第四驱动信号sb2。第三驱动信号组rto3和sb3中的驱动信号rto3可以被称为第五驱动信号rto3,而第三驱动信号组rto3和sb3中的驱动信号sb3可以被称为第六驱动信号sb3。第四驱动信号组rto4和sb4中的驱动信号rto4可以被称为第七驱动信号rto4,而第四驱动信号组rto4和sb4中的驱动信号sb4可以被称为第八驱动信号sb4。第一信号线组451和452中的信号线451可以被称为第一信号线451,而第一信号线组451和452中的信号线452可以被称为第二信号线452。第二信号线组453和454中的信号线453可以被称为第三信号线453,而第二信号线组453和454中的信号线454可以被称为第四信号线454。第三信号线组455和456中的信号线455可以被称为第五信号线455,而第三信号线组455和456中的信号线456可以被称为第六信号线456。第四信号线组457和458中的信号线457可以被称为第七信号线457,而第四信号线组457和458中的信号线458可以被称为第八信号线458。感测放大器驱动信号提供电路405可以响应于位线均衡信号bleq而将第一驱动信号组rto1和sb1、第二驱动信号组rto2和sb2、第三驱动信号组rto3和sb3以及第四驱动信号组rto4和sb4预充电到位线预充电电压vblp的电平。

87.感测放大器驱动信号提供电路405可以以与图4的感测放大器驱动信号提供电路402、图5的感测放大器驱动信号提供电路403或图6的感测放大器驱动信号提供电路404相同的形式来配置。

88.当感测放大器驱动信号提供电路405以与图4的感测放大器驱动信号提供电路402相同的形式来配置时,感测放大器驱动信号提供电路405可以通过对通过使用一个驱动器根据第一感测放大器控制信号sap驱动电源电压所生成的信号进行分支来生成第一驱动信号rto1、第三驱动信号rto2、第五驱动信号rto3和第七驱动信号rto4。另外,感测放大器驱

3可以响应于第五驱动信号rto3和第六驱动信号sb3来感测和放大驱动位线bl4和参考位线blb4之间的电压电平差。

96.第四感测放大器1000-4可以通过第七信号线457的节点被提供第七驱动信号rto4,并且可以通过第八信号线458的节点被提供第八驱动信号sb4。第四感测放大器1000-4可以响应于第七驱动信号rto4和第八驱动信号sb4来感测和放大驱动位线bl6和参考位线blb6之间的电压电平差。

97.第五感测放大器1000-5可以响应于通过第一信号线451的节点和第二信号线452的节点所提供的第一驱动信号rto1和第二驱动信号sb1来感测和放大驱动位线bl8和参考位线blb8之间的电压电平差。

98.第六感测放大器1000-6可以响应于通过第三信号线453的节点和第四信号线454的节点所提供的第三驱动信号rto2和第四驱动信号sb2来感测和放大驱动位线bl10和参考位线blb10之间的电压电平差。

99.第七感测放大器1000-7可以响应于通过第五信号线455的节点和第六信号线456的节点所提供的第五驱动信号rto3和第六驱动信号sb3来感测和放大驱动位线bl12和参考位线blb12之间的电压电平差。

100.第八感测放大器1000-8可以响应于通过第七信号线457的节点和第八信号线458的节点所提供的第七驱动信号rto4和第八驱动信号sb4来感测和放大驱动位线bl14和参考位线blb14之间的电压电平差。

101.如上所述,在实施例中,相邻的感测放大器,即,第一至第八感测放大器1000-1至1000-8,可以分别通过不同的信号线的节点被提供不同的驱动信号。具体地,预置单元组(例如四个感测放大器全部)可以分别通过不同的信号线的节点被提供驱动信号。

102.如上所述的根据图7的存储单元、位线、字线和感测放大器的数量仅仅是根据实施例的示例并不被限制,并且可以根据存储容量和设计方法而改变。在以上描述的实施例中,多个感测放大器被划分为多个组(例如4个组),并且根据分别通过相应的信号线所提供的第一驱动信号组rto1和sb1、第二驱动信号组rto2和sb2、第三驱动信号组rto3和sb3以及第四驱动信号组rto4和sb4来激活划分的感测放大器组,这使得可以降低相邻位线之间的噪声。

103.尽管已经在上面描述了各个实施例,但本领域的技术人员将理解,所描述的实施例仅仅是示例。因此,不应当基于所描述的实施例来限制在本文描述的半导体装置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1