一种基于极性加固技术的SRAM存储电路的制作方法

一种基于极性加固技术的sram存储电路

技术领域

1.本发明涉及集成电路设计技术领域,尤其涉及一种基于极性加固技术的sram存储电路。

背景技术:

2.随着科技进步,静态随机存储器(static random access memory,sram)已被广泛应用于各种航天电子领域,由于集成度越来越高,sram受到单粒子效应(single event effects,set)的影响导致单粒子翻转(single event upset,seu)的概率越来越高,单粒子翻转是一种主要的可靠性故障机制,可通过临时改变存储值导致电子系统故障,当带电粒子击中集成电路的敏感节点时,沿其路径的感应电荷可以通过漂移过程有效地收集和积累,一旦累积电荷产生的瞬态电压脉冲高于电路的开关阈值,该敏感节点中的存储值将会改变。

3.当今抗seu已经成为科研工作者不可忽略的一个问题,而现有技术缺乏相应的解决方案。

技术实现要素:

4.本发明的目的是提供一种基于极性加固技术的sram存储电路,利用该结构的存储电路可以提高存储单元写速度、降低单元功耗,并提高单元抗单粒子翻转seu的能力。

5.本发明的目的是通过以下技术方案实现的:

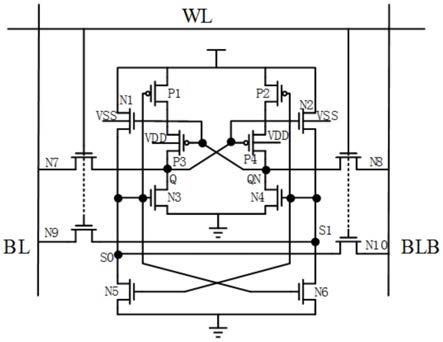

6.一种基于极性加固技术的sram存储电路,所述电路包括四个pmos晶体管和十个nmos晶体管,四个pmos晶体管依次记为p1~p4,十个nmos晶体管依次记为n1~n10,其中:

7.pmos晶体管p3的栅极与pmos晶体管p4的漏极相连接,同时pmos晶体管p4的栅极与pmos晶体管p3的漏极相连接,即p3、p4形成mos管的交叉耦合结构;

8.nmos晶体管n5和n6交叉耦合,主存储节点q和qn分别连接nmos晶体管的n2、n1的栅极;

9.pmos晶体管p3、p4的漏极连接到主存储节点q、qn,故pmos晶体管p1、p3、p2、p4起到主存储节点q、qn上拉晶体管的作用;nmos晶体管n3、n4的漏极与主存储节点q、qn相连接,故nmos晶体管n3、n4起到主存储节点q、qn下拉晶体管的作用;

10.nmos晶体管n1、n2的源极与冗余存储节点s0、s1相连接,故nmos晶体管n1、n2起到冗余存储节点s0、s1上拉晶体管的作用;nmos晶体管n5、n6的漏极与冗余存储节点s0、s1相连接,故nmos晶体管n5、n6起到冗余存储节点s0、s1下拉晶体管的作用;

11.主存储节点q和qn通过nmos晶体管n7与n8分别与位线bl和blb相连,冗余存储节点s0与s1通过nmos晶体管n9与n10分别与位线bl和blb相连,其中:

12.nmos晶体管n7、n8、n9、n10由字线wl控制;

13.位线bl与nmos晶体管n7与n9的源极电连接,位线blb与nmos晶体管n8与n10的源极电连接;

14.字线wl与nmos晶体管n7、n8、n9、n10的栅极电连接;

15.nmos晶体管n7的漏极与nmos晶体管n3的漏极电连接,nmos晶体管n8的漏极与nmos晶体管n4的漏极电连接;nmos晶体管n9的漏极与nmos晶体管n6的漏极电连接,nmos晶体管n10的漏极与nmos晶体管n5的漏极电连接;

16.电源vdd与pmos晶体管p1、p2的源极,以及nmos晶体管n1、n2的漏极电连接;

17.nmos晶体管n3、n4、n5、n6的源极均接地。

18.由上述本发明提供的技术方案可以看出,上述sram存储电路能够提高单元抗seu的能力,并可以在牺牲较小单元面积的情况下大幅度提高单元的写速度,降低单元的功耗。

附图说明

19.为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域的普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他附图。

20.图1为本发明实施例提供的基于极性加固技术的sram存储电路结构示意图;

21.图2为本发明实施例所提供的sram存储单元电路的时序波形图;

22.图3为本发明实施例所提供的sram存储电路在不同时刻不同节点受到双指数电流源脉冲注入的瞬态波形仿真图;

23.图4为现有技术sram单元电路和本发明实施例所提供的sram存储电路在相同时刻主存储节点受到双指数电流源脉冲注入后恢复其初试状态2000次蒙特卡洛仿真中失败次数对比图。

具体实施方式

24.下面结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例,这并不构成对本发明的限制。基于本发明的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明的保护范围。

25.如图1所示为本发明实施例提供的基于极性加固技术的sram存储电路结构示意图,所述电路包括四个pmos晶体管和十个nmos晶体管,四个pmos晶体管依次记为p1~p4,十个nmos晶体管依次记为n1~n10,其中:

26.pmos晶体管p3的栅极与pmos晶体管p4的漏极相连接,同时pmos晶体管p4的栅极与pmos晶体管p3的漏极相连接,即p3、p4形成mos管的交叉耦合结构;

27.nmos晶体管n5和n6交叉耦合,主存储节点q和qn分别连接nmos晶体管的n2、n1的栅极;

28.pmos晶体管p3、p4的漏极连接到主存储节点q、qn,故pmos晶体管p1、p3、p2、p4起到主存储节点q、qn上拉晶体管的作用;nmos晶体管n3、n4的漏极与主存储节点q、qn相连接,故nmos晶体管n3、n4起到主存储节点q、qn下拉晶体管的作用;

29.nmos晶体管n1、n2的源极与冗余存储节点s0、s1相连接,故nmos晶体管n1、n2起到冗余存储节点s0、s1上拉晶体管的作用;nmos晶体管n5、n6的漏极与冗余存储节点s0、s1相

连接,故nmos晶体管n5、n6起到冗余存储节点s0、s1下拉晶体管的作用;

30.主存储节点q和qn通过nmos晶体管n7与n8分别与位线bl和blb相连,冗余存储节点s0与s1通过nmos晶体管n9与n10分别与位线bl和blb相连,其中:

31.nmos晶体管n7、n8、n9、n10由字线wl控制;

32.位线bl与nmos晶体管n7与n9的源极电连接,位线blb与nmos晶体管n8与n10的源极电连接;

33.字线wl与nmos晶体管n7、n8、n9、n10的栅极电连接;

34.nmos晶体管n7的漏极与nmos晶体管n3的漏极电连接,nmos晶体管n8的漏极与nmos晶体管n4的漏极电连接;nmos晶体管n9的漏极与nmos晶体管n6的漏极电连接,nmos晶体管n10的漏极与nmos晶体管n5的漏极电连接;

35.电源vdd与pmos晶体管p1、p2的源极,以及nmos晶体管n1、n2的漏极电连接;

36.nmos晶体管n3、n4、n5、n6的源极均接地。

37.具体实现中,各晶体管的具体连接关系为:

38.pmos晶体管p1的漏极与pmos晶体管p3的源极电连接,并且pmos晶体管p1的栅极与nmos晶体管n1的源极、nmos晶体管n3的栅极、nmos晶体管n5的漏极、nmos晶体管n6的栅极电连接;

39.pmos晶体管p2的漏极与pmos晶体管p4的源极电连接,并且pmos晶体管p2的栅极与nmos晶体管n2的源极、nmos晶体管n4的栅极、nmos晶体管n5的栅极、nmos晶体管n6的漏极电连接;

40.pmos晶体管p3的漏极与nmos晶体管n3的漏极、pmos晶体管p4的栅极、nmos晶体管n2的栅极电连接,并且pmos晶体管p3的栅极与nmos晶体管n1的栅极、nmos晶体管n4的漏极电连接;

41.pmos晶体管p4的漏极与nmos晶体管n4的漏极、pmos晶体管p3的栅极、nmos晶体管n1的栅极电连接,并且pmos晶体管p4的栅极与nmos晶体管n2的栅极、nmos晶体管n3的漏极电连接;

42.nmos晶体管n1的源极与pmos晶体管p1的栅极、nmos晶体管n3的栅极、nmos晶体管n5的漏极、nmos晶体管n6的栅极电连接,并且nmos晶体管n1的栅极与pmos晶体管p3的栅极、nmos晶体管n4的漏极电连接;

43.nmos晶体管n2的源极与pmos晶体管p2的栅极、nmos晶体管n4的栅极、nmos晶体管n5的栅极、nmos晶体管n6的漏极电连接,并且nmos晶体管n2的栅极与pmos晶体管p3的栅极、nmos晶体管n4的漏极电连接;

44.nmos晶体管n3的漏极与pmos晶体管p4的栅极、nmos晶体管n2的栅极电连接,并且nmos晶体管n3的栅极与pmos晶体管p1的栅极、nmos晶体管n1的源极、nmos晶体管n5的漏极、nmos晶体管n6的栅极电连接;

45.nmos晶体管n4的漏极与pmos晶体管p3的栅极、nmos晶体管n1的栅极电连接,并且nmos晶体管n4的栅极与pmos晶体管p2的栅极、nmos晶体管n2的源极、nmos晶体管n5的栅极、nmos晶体管n6的漏极电连接;

46.nmos晶体管n5的漏极与nmos晶体管n1的源极、pmos晶体管p1的栅极、nmos晶体管n3的栅极、nmos晶体管n6的栅极电连接,并且nmos晶体管n5的栅极与pmos晶体管p2的栅极、

nmos晶体管n2的源极、nmos晶体管n4的栅极、nmos晶体管n6的漏极电连接;

47.nmos晶体管n6的漏极与nmos晶体管n2的源极、pmos晶体管p2的栅极、nmos晶体管n4的栅极、nmos晶体管n5的栅极电连接,并且nmos晶体管n6的栅极与pmos晶体管p1的栅极、nmos晶体管n1的源极、nmos晶体管n4的栅极、nmos晶体管n5的漏极电连接。

48.基于所述电路:

49.在保持阶段,位线bl和blb都预充到高电平,字线wl为低电平,电路内部保持初始状态,电路不工作;

50.在读取数据阶段,位线bl和blb都预充到高电平,字线wl为高电平,传输晶体管n7、n8、n9与n10打开;如果电路存储的数据为

‘0’

,则“q=s1=0、qn=s0=1”,那么位线bl通过放电路径1,即nmos晶体管n7与n3,和放电路径2,即nmos晶体管n9与n6向地放电,使得位线bl产生电压差,然后通过灵敏放大器读出数据;如果电路存储的数据为

‘1’

,则“q=s1=1、qn=s0=0”,那么位线blb通过放电路径3,即nmos晶体管n8与n4,和放电路径4,即nmos晶体管n10与n5向地放电,使得位线blb产生电压差,然后通过灵敏放大器读出数据;

51.在写入数据阶段,字线wl为高电平,如果位线bl为高电平,位线blb为低电平,那么通过传输晶体管n7和n9分别向存储节点q与s1写“1”;如果位线bl为低电平,位线blb为高电平,那么通过传输晶体管n8和n10分别向存储节点qn与s0写

‘1’

。

52.在数据写入过程中,因为通过传输晶体管n7与n9、n8与n10向存储节点q/s1、qn/s0写入数据,使得存储节点更容易被写入数据,这样写入的速度会大大提高,同时由于写入速度的提高从而使电路的功耗降低。

53.另外,所有晶体管的栅长均为65nm,其中:

54.pmos晶体管p1、p2、p3、p4的栅宽为300nm;

55.nmos晶体管n1、n2的栅宽为75nm;

56.nmos晶体管n5、n6的栅宽为300nm;

57.nmos晶体管n3、n4、n7、n8、n9、n10的栅宽为150nm。

58.如图2所示为本发明实施例所提供的sram存储单元电路的时序波形图,具体仿真条件为:corner:tt;temperature:25℃;vdd:1.2v。由图2可知:在整个20ns的时间内先后完成了写“1”、写“0”、写“1”、读“1”的功能,因此,rcpd-14t单元可以完成sram单元所需要的读写功能。

59.下表1为现有技术sram单元电路和本发明实施例所提供的sram存储单元电路的读写时间和功耗仿真对比表,具体仿真条件为:corner:tt;temperature:25℃;vdd:1.2v。

60.表1

61.单元读延迟(ps)写延迟(ps)dice58.831.12quatro11429.32s4p8n80.622.41rhpd-12t61.614.9qucce-10t95.831.74rcpd-14t6420

62.由表1可知:在仿真条件相同的情况下,rcpd-14t单元的读速度远超于quatro、

s4p8n、qucce-10t等单元;rcpd-14t单元的写速度远超于dice、quatro、s4p8n、qucce-10t等单元。rcpd-14t单元的读写速度可以与rhpd-12t相媲美。

63.如图3所示为本发明实施例所提供的sram存储电路在不同时刻不同节点受到双指数电流源脉冲注入的瞬态波形仿真图,具体仿真条件为:vdd:1.2v。由图3可知:当q和qn同时受到双指数电流源脉冲注入,q和qn可以完全恢复,当q、qn、s1分别受到双指数电流源脉冲注入,相关存储节点可以完全恢复,这就说明,rcpd-14t单元具有单节点和双节点受到双指数电流源脉冲注入,单元存储节点不会受其影响。

64.如图4所示为现有技术sram单元电路和本发明实施例所提供的sram存储电路在相同时刻主存储节点受到双指数电流源脉冲注入后恢复其初试状态2000次蒙特卡洛仿真中失败次数对比图,具体仿真条件为:corner:mc;temperature:25℃;vdd:1.2v。由图4可知:在相同仿真环境中,对所有单元q和qn主存储节点进行双指数电流源脉冲注入,在2000次的蒙特卡洛仿真中,dice、quatro、s4p8n、qucce-10t单元主存储节点值均受到破坏,而rhpd-12t和rcpd-12t单元主存储节点2000次均得到恢复。

65.值得注意的是,本发明实施例中未作详细描述的内容属于本领域专业技术人员公知的现有技术。

66.综上所述,本发明实施例提供的sram存储电路能够提高单元电路的抗seu的能力,可以在牺牲较小单元面积的情况下大幅度提高单元的写速度,并且降低了单元的功耗。

67.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明披露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求书的保护范围为准。本文背景技术部分公开的信息仅仅旨在加深对本发明的总体背景技术的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域技术人员所公知的现有技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1