存储装置和包括其的半导体系统的制作方法

存储装置和包括其的半导体系统

1.相关申请的交叉引用

2.本技术要求在2021年4月19日在韩国知识产权局提交的申请号为10-2021-0050403的韩国专利申请的优先权,其全部内容通过引用合并于此。

技术领域

3.各个实施例总体上涉及集成电路技术,更具体地涉及存储装置和使用其的半导体系统。

背景技术:

4.每一个电子装置可以包括许多电子部件。在电子装置中,计算机系统可以包括通过半导体配置的许多电子部件。在配置计算机系统的半导体装置中,诸如处理器或存储控制器的主机可以执行与存储装置的数据通信。存储装置可以通过包括多个存储单元来存储数据,该多个存储单元的每个都可以通过字线和位线来指定。存储装置可以在其中包括纠错码(ecc)电路以确保数据的可靠性。当数据被存储在存储装置中时,ecc电路可以生成奇偶校验数据,并且当数据被读取时,ecc电路可以通过使用奇偶校验数据来校正数据中的错误。为了测试存储装置的ecc电路是否正常执行纠错操作,主机可以执行ecc测试操作。可以通过有意地将错误插入要存储到存储装置的数据中并且检查ecc电路是否适当地校正错误来执行ecc测试操作。

技术实现要素:

5.在实施例中,一种存储装置可以包括:地址解码电路,其基于从存储控制器发送的地址来输出测试冗余地址;以及冗余地址检查电路,其确定所述测试冗余地址是否在代替故障地址以便通过使用所述测试冗余地址来执行ecc测试操作。

6.在实施例中,一种存储装置可以包括:多个冗余区域;以及冗余地址检查电路,其通过将测试冗余地址与对应于所述冗余区域的多个冗余地址中的参考地址相比较来确定所述测试冗余地址是否可用于ecc测试操作。

7.在实施例中,一种半导体系统可以包括:具有ecc电路的存储装置,所述存储装置执行用于所述ecc电路的ecc测试操作;以及存储控制器,其向存储装置发送地址以用于所述ecc测试操作,其中,所述存储装置确定与所述地址相对应的测试冗余地址,并且在确定测试冗余地址不可用于所述ecc测试操作时向所述存储控制器输出警告信号。

附图说明

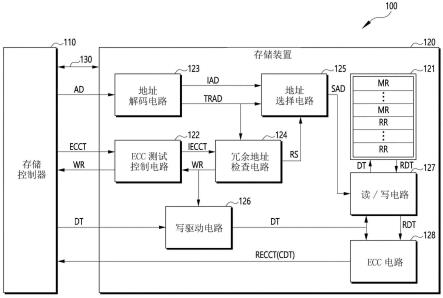

8.图1是示出根据本公开的实施例的半导体系统的结构的图。

9.图2a是示出根据本公开的实施例的使用冗余区域的方法的图。

10.图2b和图2c是示出根据本公开的实施例的冗余地址检查电路的结构的图。

11.图3a是示出根据本公开的实施例的使用冗余区域的方法的图。

12.图3b是示出根据本公开的实施例的冗余地址检查电路的结构的图。

13.图4是示出根据本公开的实施例的用于存储装置执行ecc测试操作的方法的流程图。

14.图5是示出根据本公开的实施例的用于存储控制器控制存储装置的ecc测试操作的方法的流程图。

具体实施方式

15.在下文中,以下将参考附图通过实施例的各种示例来描述存储装置和包括其的半导体系统。

16.各个实施例涉及提供一种存储装置以及包括其的半导体系统,该存储装置高效地执行ecc测试操作,而不影响存储装置的存储容量。

17.根据本公开的实施例的存储装置和包括其的半导体系统可以高效地执行ecc测试操作,而不影响存储装置的存储容量。

18.图1是示出根据本公开的实施例的半导体系统100的结构的图。

19.参考图1,半导体系统100可以包括存储控制器110和存储装置120。存储控制器110可以提供存储装置120进行操作所必需的各个控制信号。存储控制器110可以被内置在各种类型的主机设备中。主机设备的示例可以包括中央处理单元(cpu)、图形处理单元(gpu)、多媒体处理器(mmp)、数字信号处理器以及应用处理器(ap)。在实施例中,存储控制器110与存储装置120一起可以被堆叠在一个衬底上,并且可以被封装成单个封装体。存储装置120的示例可以包括dram(动态随机存取存储器)、sram(静态随机存取存储器)、闪速存储器、feram(铁电随机存取存储器)、pcram(相变随机存取存储器)、mram(磁随机存取存储器)和reram(电阻随机存取存储器)。

20.存储控制器110可以通过一个或多个总线130耦接到存储装置120。总线130可以是用于传送信号的信号传输路径、链路或者信道。存储控制器110可以通过总线130向存储装置120传送诸如命令、地址和数据的信号,并且可以通过总线130从存储装置120接收包括数据的各种信号。

21.存储控制器110可以控制存储装置120,使得存储装置120执行纠错码(ecc)测试操作。ecc测试操作可以用于测试存储装置120中的ecc电路128是否正常地执行纠错操作。为了指示存储装置120执行ecc测试操作,存储控制器110可以向存储装置120发送ecc测试信号ecct。ecc测试信号ecct可以是用于将存储装置120中的模式寄存器(未示出)设置为预定值的信号,以使得存储装置120执行ecc测试操作。ecc测试信号ecct可以是指示存储装置120执行ecc测试操作的预定命令。

22.存储控制器110可以向存储装置120发送地址ad以用于ecc测试操作。地址ad可以对应于存储装置120中的任何一个主区域mr。地址ad可以是行地址。当从存储装置120接收到指示地址ad不可用于ecc测试操作的警告信号wr时,存储控制器110可以向存储装置120发送与不可用的地址ad不同的地址ad。当从存储装置120接收到ecc测试操作的结果recct而非警告信号wr时,存储控制器110可以单独地存储地址ad,并且可以在稍后再次执行ecc测试操作时向存储装置120发送所存储的地址ad。也就是说,当确定地址ad可用于ecc测试操作时,存储控制器110可以单独地存储地址ad以供重新使用。

23.存储控制器110可以进一步向存储装置120发送数据dt以用于存储装置120的ecc测试操作。存储控制器110可以从存储装置120接收包括在ecc测试操作的结果recct中的纠错数据cdt。通过将纠错数据cdt与数据dt相比较,存储控制器110可以确定ecc电路128是否正常地执行纠错操作。例如,当纠错的数据cdt与数据dt相同时,存储控制器110可以确定ecc电路128正常地执行纠错操作,而当纠错的数据cdt不同于数据dt时,存储控制器110可以确定ecc电路128没有正常地执行纠错操作。

24.存储装置120可以基于存储控制器110进行操作。存储装置120可以包括存储单元阵列121、ecc测试控制电路122、地址解码电路123、冗余地址检查电路124、地址选择电路125、写驱动电路126、读/写电路127以及ecc电路128。

25.多个字线和多个位线可以被布置在存储单元阵列121中,并且多个存储单元可以耦接到多个字线和多个位线彼此相交的点。存储单元阵列121可以包括主区域mr和冗余区域rr。冗余区域rr可以用于代替主区域mr中的故障区域。主区域mr可以分别对应于不同的主地址,而冗余区域rr可以分别对应于不同的冗余地址。主地址和冗余地址例如可以是行地址。

26.响应于ecc测试信号ecct,ecc测试控制电路122可以控制存储装置120的内部单元的一般操作,使得存储装置120的内部单元执行ecc测试操作。ecc测试控制电路122可以响应于ecc测试信号ecct而输出(或使能)内部ecc测试信号iecct。ecc测试控制电路122可以将从冗余地址检查电路124发送的警告信号wr发送到存储控制器110。

27.地址解码电路123可以接收地址ad,并且可以输出内部地址iad和对应于地址ad的测试冗余地址trad。

28.内部地址iad可以对应于主区域mr和冗余区域rr中的任何一个。内部地址iad可以是主区域mr的主地址和冗余区域rr的冗余地址中的任何一个。当确定作为地址ad发送的主地址是故障地址时,地址解码电路123可以输出代替地址ad的冗余地址作为内部地址iad。当确定作为地址ad发送的主地址不是故障地址时,地址解码电路123可以输出地址ad作为内部地址iad。

29.测试冗余地址trad可以对应于任何一个冗余区域rr。测试冗余地址trad可以是冗余区域rr的任何一个冗余地址。地址解码电路123可以根据预定规则来确定和输出对应于地址ad的测试冗余地址trad。例如,地址解码电路123可以输出与地址ad相同值的测试冗余地址trad,但是本公开的实施例不限于此。

30.无论是否在执行ecc测试操作,地址解码电路123都可以输出内部地址iad和测试冗余地址trad。根据实施例,地址解码电路123可以在没有执行ecc测试操作时仅输出内部地址iad,并且可以在执行ecc测试操作时输出内部地址iad和测试冗余地址trad。例如,地址解码电路123可以接收内部ecc测试信号iecct,可以在内部ecc测试信号iecct被禁止时仅输出内部地址iad,并且可以在内部ecc测试信号iecct被使能时输出内部地址iad和测试冗余地址trad。

31.冗余地址检查电路124可以响应于内部ecc测试信号iecct而在ecc测试操作中操作。冗余地址检查电路124可以在内部ecc测试信号iecct被禁止时不进行操作,并且可以在内部ecc测试信号iecct被使能时进行操作。冗余地址检查电路124可以在ecc测试操作中接收测试冗余地址trad,可以确定测试冗余地址trad是否可用于ecc测试操作,并且可以根据

确定结果来输出(或使能)冗余选择信号rs和警告信号wr。当没有执行ecc测试操作时,冗余地址检查电路124可以不输出(或禁止)冗余选择信号rs和警告信号wr。

32.具体而言,通过确定测试冗余地址trad是否在代替故障地址,冗余地址检查电路124可以确定测试冗余地址trad是否可用于ecc测试操作。当测试冗余地址trad未在代替故障地址时,冗余地址检查电路124可以确定测试冗余地址trad可用于ecc测试操作。当确定测试冗余地址trad可用于ecc测试操作时,冗余地址检查电路124可以输出(或使能)冗余选择信号rs,并且可以不输出(或禁止)警告信号wr。当测试冗余地址trad在代替故障地址时,冗余地址检查电路124可以确定测试冗余地址trad不可用于ecc测试操作。当确定测试冗余地址trad不可用于ecc测试操作时,冗余地址检查电路124可以不输出(或禁止)冗余选择信号rs,并且可以输出(或使能)警告信号wr。

33.为了确定测试冗余地址trad是否在代替故障地址,冗余地址检查电路124可以将测试冗余地址trad与冗余区域rr的冗余地址中的参考地址相比较。参考地址可以是最近用于代替故障地址的冗余地址。为了确定测试冗余地址trad是否在代替故障地址,冗余地址检查电路124可以进一步将测试冗余地址trad与冗余区域rr的冗余地址中的最后冗余地址相比较。

34.地址选择电路125可以接收内部地址iad和测试冗余地址trad,并且可以响应于冗余选择信号rs来输出内部地址iad和测试冗余地址trad中的任何一个作为输出地址sad。例如,地址选择电路125可以接收内部地址iad和测试冗余地址trad,并且可以在冗余选择信号rs被禁止时输出内部地址iad。另一方面,地址选择电路125可以接收内部地址iad和测试冗余地址trad,并且可以在冗余选择信号rs被使能时输出测试冗余地址trad。

35.写驱动电路126可以接收数据dt,并且可以基于警告信号wr通过驱动数据dt来将数据dt发送到ecc电路128和读/写电路127。在警告信号wr被禁止时写驱动电路126可以向ecc电路128和读/写电路127发送数据dt。在警告信号wr被使能时写驱动电路126可以不向ecc电路128和读/写电路127发送数据dt。根据实施例,写驱动电路126可以不直接地从冗余地址检查电路124接收警告信号wr,并且可以通过ecc测试控制电路122来接收警告信号wr。

36.读/写电路127可以对主区域mr和冗余区域rr中的与输出地址sad相对应的区域进行存取。读/写电路127可以将从写驱动电路126发送的数据dt存储在与输出地址sad相对应的区域中,并且可以从与输出地址sad相对应的区域中读取该读取数据rdt。当地址选择电路125输出内部地址iad时,读/写电路127可以对主区域mr和冗余区域rr中的与内部地址iad相对应的区域进行存取。当地址选择电路125输出测试冗余地址trad时,读/写电路127可以对冗余区域rr中的与测试冗余地址trad相对应的冗余区域rr进行存取。

37.ecc电路128可以接收由写驱动电路126所发送的数据dt,并且可以生成与数据dt相对应的错误检测数据(例如,奇偶校验数据)。ecc电路128可以接收由读/写电路127输出的读取数据rdt,可以基于错误检测数据来校正读取数据rdt中的错误,并且可以输出纠错的数据cdt。可以将纠错的数据cdt作为ecc测试操作的结果recct来向存储控制器110输出。

38.在ecc测试操作中,可以以各种方式将错误引入数据dt中。例如,错误可以被覆写到存储单元中所存储的数据dt。例如,可以在将数据dt存储在存储单元中之前将错误引入读/写电路127中。同时,可以在将错误引入数据dt之前生成奇偶校验数据,并且即使当将错误引入数据dt时也可以不更新奇偶校验数据。因此,可以通过奇偶校验数据来校正读取数

据rdt中所包括的错误。

39.存储装置120可以以下面的方式对存储单元阵列121进行存取。当没有执行ecc测试操作时,地址选择电路125可以响应于禁止的冗余选择信号rs来输出内部地址iad,并且读/写电路127可以对主区域mr和冗余区域rr中的与内部地址iad相对应的区域进行存取。当执行ecc测试操作时,如果冗余地址检查电路124确定测试冗余地址trad可用于ecc测试操作,则地址选择电路125可以响应于使能的冗余选择信号rs而输出测试冗余地址trad,并且读/写电路127可以对冗余区域rr中的与测试冗余地址trad相对应的冗余区域rr进行存取。当执行ecc测试操作时,如果冗余地址检查电路124确定测试冗余地址trad不可用于ecc测试操作,则地址选择电路125可以响应于禁止的冗余选择信号rs而输出内部地址iad。然而,由于写驱动电路126响应于使能的警告信号wr而不进行操作,所以读/写电路127可以不将数据dt存储在与内部地址iad相对应的区域中。

40.根据实施例,当存储装置120包括多个存储体并且每一个存储体包括冗余区域rr和ecc电路128时,可以根据以上描述的方法对每一个存储体执行ecc测试操作。

41.因此,根据本公开,当执行ecc测试操作时,可以使用没有代替故障区域的冗余区域rr,因此主区域mr的容量可以不受影响。此外,根据本公开,即使当主区域mr充满数据时,也可以使用冗余区域rr来进行ecc测试操作。此外,根据本公开,通过有效地确定测试冗余地址trad是否在代替故障地址,可以防止存储在冗余区域rr中的数据由于ecc测试操作而被损坏。

42.图2a是示出根据本公开的实施例的使用冗余区域rr0至rrn的方法的图。图2b和图2c是示出根据本公开的实施例的冗余地址检查电路124的结构的图。

43.参考图2a,冗余区域rr0至rrn可以以地址顺序分别对应于从第一冗余地址0至最后冗余地址(lrad)n的冗余地址rad。可以通过对应的冗余地址rad对冗余区域rr0至rrn中的每一个进行存取。当输入任何一个冗余地址rad时,读/写电路127可以对冗余区域rr0至rrn中的对应的冗余区域进行存取。

44.可以提供冗余区域rr0至rrn以代替(或修复)主区域mr中的故障区域。不仅在存储装置120的制造步骤期间可能存在故障区域,而且在存储装置120的使用期间也可能存在故障区域。当存在故障区域(或故障地址)时,冗余区域rr0至rrn中的第一冗余区域rr0(或第一冗余地址0)可以首先用于代替故障区域(或故障地址)。因此,当从0至i的冗余地址rad在代替故障地址时,冗余地址i可以是最近用于代替故障地址的冗余地址(在下文,被称为参考冗余地址rrad)。

45.因此,由于从0至i的冗余地址rad在代替故障地址,所以冗余地址检查电路124可以确定从0至i的冗余地址rad不可用于ecc测试操作。然而,由于从i+1至n的冗余地址rad没有在代替故障地址,所以冗余地址检查电路124可以确定从i+1至n的冗余地址rad可用于ecc测试操作。

46.参考图2b,冗余地址检查电路124_a可以是图1的冗余地址检查电路124的实施例。冗余地址检查电路124_a可以确定测试冗余地址trad是否是从i+1至n的冗余地址rad中的一个。换句话说,冗余地址检查电路124_a可以基于紧邻参考冗余地址rrad的冗余地址i+1至最后冗余地址lrad n来确定测试冗余地址trad是否是冗余地址rad中的一个。根据确定结果,冗余地址检查电路124_a可以输出(或使能)冗余选择信号rs或者输出(或使能)警告

信号wr。

47.冗余地址检查电路124_a可以包括第一比较电路a1、第二比较电路a2、与门a3以及或门a4。

48.第一比较电路a1和第二比较电路a2可以响应于内部ecc测试信号iecct来进行操作。当内部ecc测试信号iecct被禁止时,第一比较电路a1可以不输出(或可以禁止)第一通过信号p1和第一故障信号f1。当内部ecc测试信号iecct被禁止时,第二比较电路a2可以不输出(或可以禁止)第二通过信号p2和第二故障信号f2。

49.当内部ecc测试信号iecct被使能时,第一比较电路a1可以将测试冗余地址trad与参考冗余地址rrad相比较,并且可以基于比较结果来输出第一通过信号p1和第一故障信号f1。当测试冗余地址trad在地址顺序中晚于参考冗余地址rrad时,第一比较电路a1可以使能第一通过信号p1并且禁止第一故障信号f1。当测试冗余地址trad在地址顺序中早于或等于参考冗余地址rrad时,第一比较电路a1可以使能第一故障信号f1并且禁止第一通过信号p1。

50.当内部ecc测试信号iecct被使能时,第二比较电路a2可以将测试冗余地址trad与最后冗余地址lrad相比较,并且可以基于比较结果来输出第二通过信号p2和第二故障信号f2。当测试冗余地址trad在地址顺序中早于或等于最后冗余地址lrad时,第二比较电路a2可以使能第二通过信号p2并且禁止第二故障信号f2。当测试冗余地址trad在地址顺序中晚于最后冗余地址lrad时,第二比较电路a2可以使能第二故障信号f2并且禁止第二通过信号p2。

51.与门a3可以接收所述第一通过信号p1和第二通过信号p2,并且可以输出冗余选择信号rs。当第一通过信号p1和第二通过信号p2两者都被使能时,与门a3可以使能冗余选择信号rs。

52.或门a4可以接收第一故障信号f1和第二故障信号f2,并且可以输出警告信号wr。当第一故障信号f1或第二故障信号f2被使能时,或门a4可以使能警告信号wr。

53.冗余地址检查电路124_a可以通过第二比较电路a2来将测试冗余地址trad与最后冗余地址lrad相比较,以为地址解码电路123没有输出测试冗余地址trad作为0至n冗余地址rad之一的情况作准备。根据实施例,地址解码电路123可以遵循将测试冗余地址trad必要地输出为0至n冗余地址rad中的一个冗余地址rad的规则。在这种情况下,可以如图2c中所示那样来配置冗余地址检查电路124_b。

54.参考图2c,冗余地址检查电路124_b可以是图1的冗余地址检查电路124的实施例。冗余地址检查电路124_b可以包括比较电路b1。比较电路b1可以响应于内部ecc测试信号iecct来进行操作。当内部ecc测试信号iecct被禁止时,比较电路b1可以不输出(或可以禁止)冗余选择信号rs和警告信号wr。当内部ecc测试信号iecct被使能时,比较电路b1可以将测试冗余地址trad与参考冗余地址rrad相比较,并且可以基于比较结果来输出(或使能)冗余选择信号rs或警告信号wr。当测试冗余地址trad在地址顺序中晚于参考冗余地址rrad时,比较电路b1可以使能冗余选择信号rs并且禁止警告信号wr。当测试冗余地址trad在地址顺序中早于或等于参考冗余地址rrad时,比较电路b1可以使能警告信号wr并且禁止冗余选择信号rs。

55.图3a是示出根据本公开的实施例的使用冗余区域rr0至rrn的方法的图。图3b是示

出根据本公开的实施例的冗余地址检查电路124的结构的图。

56.参考图3a,与图2a的所示相反,当存在故障区域(或故障地址)时,冗余区域rr0至rrn中的最后冗余区域rrn(或最后冗余地址n)可以首先用于代替故障区域(或故障地址)。因此,当从n至j的冗余地址rad在代替故障地址时,冗余地址j可以是最近用于代替故障地址的参考冗余地址rrad。

57.因此,由于从n至j的冗余地址rad在代替故障地址,所以冗余地址检查电路124可以确定从n至j的冗余地址rad不可用于ecc测试操作。然而,由于从j-1至0的冗余地址rad没有在代替故障地址,所以冗余地址检查电路124可以确定从j-1至0的冗余地址rad可用于ecc测试操作。

58.参考图3b,冗余地址检查电路124_c可以是图1的冗余地址检查电路124的实施例。冗余地址检查电路124_c可以包括比较电路c1。比较电路c1可以响应于内部ecc测试信号iecct来进行操作。当内部ecc测试信号iecct被禁止时,比较电路c1可以不输出(或可以禁止)冗余选择信号rs和警告信号wr。当内部ecc测试信号iecct被使能时,比较电路c1可以将测试冗余地址trad与参考冗余地址rrad相比较,并且可以根据比较结果来输出(或使能)冗余选择信号rs或警告信号wr。当测试冗余地址trad在地址顺序中早于参考冗余地址rrad时,比较电路c1可以使能冗余选择信号rs并且禁止警告信号wr。当测试冗余地址trad在地址顺序中晚于或等于参考冗余地址rrad时,比较电路c1可以使能警告信号wr并且禁止冗余选择信号rs。

59.图4是示出根据本公开的实施例的用于存储装置120执行ecc测试操作的方法的流程图。

60.参考图4,在步骤s110,地址解码电路123可以输出与从存储控制器110发送的地址ad相对应的测试冗余地址trad。

61.在步骤s120,冗余地址检查电路124可以确定测试冗余地址trad是否在代替故障地址。当测试冗余地址trad未在代替故障地址时,处理可以继续到步骤s130。当测试冗余地址trad在代替故障地址时,处理可以继续到步骤s140。

62.在步骤s130,存储装置120可以基于测试冗余地址trad来执行ecc测试操作。通过将用于ecc测试操作的数据dt存储在与测试冗余地址trad相对应的冗余区域中并且对从对应的冗余区域中读取的读取数据rdt执行纠错操作,存储装置120可以执行ecc测试操作。与测试冗余地址trad相对应的冗余区域可以存储引入错误的数据。

63.在步骤s140,存储装置120可以向存储控制器110输出警告信号wr,并且可以不执行ecc测试操作。

64.图5是示出根据本公开的实施例的用于存储控制器110控制存储装置120的ecc测试操作的方法的流程图。

65.参考图5,在步骤s210,为了进行ecc测试操作,存储控制器110可以向存储装置120发送地址ad。存储装置120可以根据图4中所示出的处理来执行ecc测试操作。

66.在步骤s220,存储控制器110可以确定是否从存储装置120接收到警告信号wr。当接收到警告信号wr时,处理可以继续到步骤s230。当没有接收到警告信号wr时,处理可以继续到步骤s240。

67.在步骤s230,存储控制器110可以确定将要发送到存储装置120的另一个地址ad。

然后,处理可以继续到步骤s210。也就是说,存储控制器110可以向存储装置120发送另一个地址ad用于ecc测试操作。

68.在步骤s240,存储控制器110可以确定是否从存储装置120接收到ecc测试操作的结果recct。当没有接收到ecc测试操作的结果recct时,可以重复步骤s240。当接收到ecc测试操作的结果recct时,处理可以继续到步骤s250。

69.在步骤s250,基于ecc测试操作的结果recct,存储控制器110可以确定ecc电路128是否正常地操作。

70.在s260,存储控制器110可以单独地存储地址ad以便当稍后再次执行ecc测试操作时向存储装置120发送地址ad。

71.尽管已经在上面描述了各个实施例,但本领域的技术人员将理解,所描述的实施例仅是示例。因此,在本文描述的存储装置和包括该存储装置的半导体系统不应当基于所描述的实施例被限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1