一种存储器及其编程方法、存储器系统与流程

1.本发明涉及存储器技术领域,尤其涉及一种存储器及其编程方法、存储器系统。

背景技术:

2.非易失性存储器已经广泛应用于各个领域的电子器件中。闪存是可以被电擦除并重新编程的使用最为广泛的非易失性存储器之一,闪存可以包括nor和nand两种架构的存储器,其中,对闪存中的每一个存储单元的阈值电压改变为需要的电平以实现各种操作,如读取、编程和擦除。在对闪存操作时,可以按照块级别执行擦除操作,可以按照页级别执行编程操作,可以按照存储单元级别执行读取操作。目前,平面结构的nand闪存已经应用广泛,为了进一步的提高闪存的存储容量,降低每比特的存储成本,提出了三维(3d)nand存储器,其结构包括衬底;位于衬底上设置堆叠结构;贯穿堆叠结构的若干通道孔;位于通道孔中的存储结构,所述存储结构包括位于所述通道孔侧壁表面上的电荷存储层和位于电荷存储层侧壁表面上的沟道层,每一个沟道孔中的存储结构与每一个控制栅相交的位置对应一个存储单元。在该种结构下的3d nand,对某一通道孔的某一层存储单元执行编程时,存在对其他通道孔的其他层的存储单元带来热载流子注入(hci,hot carrier injection)类型的编程干扰。

技术实现要素:

3.有鉴于此,本发明的主要目的在于提供一种存储器及其编程方法、存储器系统,通过对受编程干扰影响严重的未选中字线上施加一个小于其相邻字线上的通过电压,以降低二者之间的电压差,进而减小三维非易失性存储器执行编程时耦接到未选定的字线的存储单元的hci类型干扰。

4.为达到上述目的,本发明的技术方案是这样实现的:

5.第一方面,本发明实施例提供一种存储器的编程方法,所述存储器包括:多个存储单元串;每一个存储单元串一端与位线连接,另一端与源极线连接;每一个存储单元串包含串联的多个存储单元;其中,所述多个存储单元分别与多个字线耦接;所述编程方法包括:

6.根据编程顺序对选定存储单元串进行编程;

7.在对所述选定存储单元串中与所述多个字线中选定的非边缘字线耦接的存储单元进行编程时,对所述多个字线中的边缘字线施加第一通过电压;对与所述边缘字线相邻的非边缘字线施加第二通过电压;其中,所述边缘字线为所述多个字线中与所述源极线相邻的至少一个字线,或者所述多个字线中与所述位线相邻的至少一个字线;所述非边缘字线为所述多个字线中除所述边缘字线之外的字线;所述选定的非边缘字线与所述边缘字线不相邻;所述第一通过电压小于所述第二通过电压。

8.第二方面,本发明实施例还提供一种存储器,包括存储器阵列,所述存储器阵列包括多个存储单元串;每一个存储单元串一端与位线连接,另一端与源极线连接;每一个存储单元串包含串联的多个存储单元;其中,所述多个存储单元分别与多个字线耦接;

9.以及耦接在所述存储器阵列且用于控制所述存储器阵列的控制电路;

10.其中,所述控制电路被配置为:

11.根据编程顺序对选定存储单元串进行编程;

12.在对所述选定存储单元串中与所述多个字线中选定的非边缘字线耦接的存储单元进行编程时,对所述多个字线中的边缘字线施加第一通过电压;对与所述边缘字线相邻的非边缘字线施加第二通过电压;其中,所述边缘字线为所述多个字线中与所述源极线相邻的至少一个字线,或者所述多个字线中与所述位线相邻的至少一个字线;所述非边缘字线为所述多个字线中除所述边缘字线之外的字线;所述选定的非边缘字线与所述边缘字线不相邻;所述第一通过电压小于所述第二通过电压。

13.第三方面,本发明实施例还提供一种存储器系统,包括前述的存储器;以及耦接到所述存储器的存储器控制器,所述存储器控制器被配置为控制所述存储器。

14.本发明实施例提供一种存储器及编程方法、存储器系统。其中,所述存储器包括:多个存储单元串;每一个存储单元串包含串联的多个存储单元;其中,所述多个存储单元分别与多个字线耦接;所述编程方法包括:根据编程顺序对选定存储单元串进行编程;在对所述选定存储单元串中与所述多个字线中选定的非边缘字线耦接的存储单元进行编程时,对所述多个字线中的边缘字线施加第一通过电压;对与所述边缘字线相邻的非边缘字线施加第二通过电压;其中,所述边缘字线为所述多个字线中与所述源极线相邻的至少一个字线,或者所述多个字线中与所述位线相邻的至少一个字线;所述非边缘字线为所述多个字线中除所述边缘字线之外的字线;所述选定的非边缘字线与所述边缘字线不相邻;所述第一通过电压小于所述第二通过电压。本发明实施例提供的存储器及其编程方法、存储器系统,通过在边缘字线(比如,wl0和wl1)上施加一个小于相邻非边缘字线(比如,字线wl2)上施加的通过电压,以此,将相邻的边缘字线与相邻的非边缘字线(比如,字线wl1和字线wl2)之间的电位差降低,以此减少不相邻的非边缘字线(比如,字线wl3)编程期间边缘字线(比如,字线wl1)上的hci类型干扰。

附图说明

15.在不一定按比例绘制的附图中,相同的标号可以描述不同视图中的类似组件。具有不同字母后缀的相同数字可表示类似组件的不同实例。附图以实例而非限制的方式一般性地说明了本文档中讨论的各种实施例。

16.图1为本发明实施例提供的一个nand串的结构示意图;

17.图2为本发明实施例的一个nand串的等效电路图;

18.图3为本发明实施例提供的存储单元的阵列结构示意图;

19.图4为本发明实施例提供的单块三维存储器阵列的结构示意图;

20.图5(a)至图5(e)为本发明实施例提供的三维nand的相关结构示意图;

21.图6为本发明实施例提供的具有用于对存储单元阵列进行并行读取和编程的读/写电路的存储器的结构示意图;

22.图7为本发明实施例提供的外围电路与存储器阵列之间的结构示意图;

23.图8为本发明实施例提供的阈值电压与存储单元数量的曲线图;

24.图9为本发明实施例提供的编程的流程图;

25.图10本发明实施例提供的ispp方式的编程脉冲的结构示意图;

26.图11为本发明实施例提供的揭示技术问题的示意图;

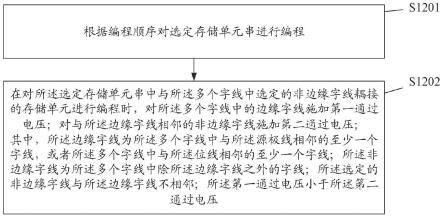

27.图12为本发明实施例提供的对存储器进行编程的方法流程示意图;

28.图13为本发明实施例提供的对存储器进行编程时施加编程电压与通过电压的一种可选实施方式的示意图;

29.图14为本发明实施例提供的对存储器进行编程的方法流程示意图;

30.图15为本发明实施例提供的存储器系统的结构示意图;

31.图16(a)为根据本发明提供的一些方面的具有存储器系统的示例性存储器卡的示意图;

32.图16(b)为根据本发明的一些方面的具有存储器系统的示例性固态驱动器(ssd)的示意图。

具体实施方式

33.以下参照附图更详细地描述本发明的各个实施例。可以通过不同地配置或布置本发明中的元件和特征以形成可作为任何所公开的实施例的变形的其它实施例。因此,本发明不限于在本文中阐述的实施例。相反,提供所描述的实施例以使得本发明是彻底和完整的,并且将本发明的范围充分传达给本发明所属技术领域的技术人员。应当注意的是,对“实施例”、“另一实施例”等的引用不一定表示仅一个实施例,并且对任何这样的短语的不同引用不一定针对相同的实施例。应当理解的是,尽管在本文中可以使用术语“第一”、“第二”、“第三”等来标识各种元件,但是这些元件不受这些术语的限制。这些术语用于将一个元件与另一个具有相同或者相似名称的元件区分开。因此,在不脱离本发明的精神和范围的情况下,在一个实施例中的第一元件在另一实施例中也可以称为第二或三元件。

34.附图不一定按照比例绘制,并且在某些情况下,可以放大比例以清楚地示出实施例的特征。当元件称为连接或联接至另一个元件时,应该理解的是,前者可以直接连接或联接后者,或者可以经由二者之间的一个或多个中间元件电连接或电联接至后者。此外,还应当理解的是,当元件被称为在两元件“之间”时,该元件可以是两个元件之间唯一元件,或者也可以存在一个或多个中间元件。

35.在本文中所使用术语仅出于描述特定实施例的目的,并且不旨在限制本发明。如本文中所使用的单数形式旨在包括复数形式,除非上下文另外明确指出。除非另外说明或者从上下文可以清楚地理解为单数形式,否者在本发明和所附权利要求书中使用的冠词“一”和/或“一个”统称应该解释为表示“一个或多个”。应当进一步理解的是,本发明中使用的术语“包括”、“包括有”、“包含”和“包含有”指定存在所述元件并且不排除存在或附加一个或更多其它元件。本发明所使用的术语“和/或”包括一个或者多个相关联的所列项目的任意和所有组合。除非另外定义,否则本发明使用的包括技术和科学技术的所有术语具有与本发明所属领域的普通技术人员鉴于本发明而通常理解的相同含义。应当进一步理解的是,除非本发明明确定义,否则诸如在常用词典中定义的属于应解释为具有与其在本发明和相关技术的环境中的含义一致的含义,而不应以理想化或过于形式化的方式解释。

36.在以下描述中,阐述了许多具体细节以提供对本发明的透彻理解,可以在没有某些或者所有这些具体细节的情况下实践本发明。在其它情况下,没有详细描述公知的处理

结构和/或处理,以免不必要地模糊本发明。还应当理解的是,在某些情况下,除非另外特别之处,否则对相关领域的技术人员显而易见的是,关于一个实施例描述的特征或元件可以被单独使用或者与另一实施例的其它特征或元件组合使用。在下文中,参考附图详细描述本发明的各个实施例。以下描述集中在细节上以促进对本发明的实施例的理解。可能省略了众所周知的技术细节,以免模糊本发明的特征和方面。

37.下面结合附图及具体实施例对本发明作进一步详细的说明。

38.图1为本发明实施例提供的一个nand串的结构示意图;图2为图1所示nand串的等效电路图。在nand结构的闪存系统中,多个晶体管串联布置并且被夹在两个选择栅极(源极栅极和漏极栅极)之间,串联的晶体管和两个选择栅极被称之为nand串。如图1和图2所示的nand串包括顶部选择栅极sgd(在漏极侧)、底部选择栅极sgs(在源极侧),以及夹在二者之间的顶部虚设晶体管sgdt、四个晶体管101-104和底部预设晶体管sgst。其中,顶部选择栅极sgd通过位线接触部将nand串连接到位线;通过向顶部选择栅极线sgdl施加合适的电压而对顶部选择栅极sgd进行控制。底部选择栅极sgs将nand串连接到源极线;通过向底部选择栅极线sgsl施加合适的电压而对底部选择栅极sgs进行控制。顶部虚设晶体管sgdt、四个晶体管101-104和底部预设晶体管sgst中的每个晶体管包含有控制栅极和浮置栅极,比如,顶部虚设晶体管sgdt包括控制栅极cgdt和浮置栅极fgdt;晶体管101包含控制栅极101cg1和浮置栅极101fg1;晶体管102包含控制栅极102cg1和浮置栅极102fg1;晶体管103包含控制栅极103cg1和浮置栅极103fg1;晶体管104包含控制栅极105(b)g1和浮置栅极105(e)g1;底部虚设晶体管sgst包括控制栅极cgst和浮置栅极fgst。控制栅极cgst与底部虚设字线bdwl连接;控制栅极101cg1-控制栅极105(b)g1分别字线wl0-wl3连接;控制栅极cgdt与顶部虚设字线tswl连接。

39.需要说明的是,图1和图2仅是实例性的示出nand串中用于读写操作的四个存储单元(晶体管101-104)及用于读写测试的两个虚设存储单元(顶部虚设晶体管sgdt和底部预设晶体管sgst)。在实际应用中,nand串可以包含8个、16个、32个、64个、128个存储单元等等,也就是说,nand串中的存储单元或者虚设存储单元的个数不限制本发明的范围。此外,使用nand结构的闪存系统的典型结构包含多个nand串。每个nand串通过由底部选择栅极线sgsl控制的底部选择栅极sgs连接到源极线,通过由顶部选择栅极线sgdl控制的顶部选择栅极sgd连接到相应的位线。每个位线和经由位线接触部连接到该位线的相应的nand串(单个或多个)形成存储单元的阵列中的列。位线被多个nand串共享。典型的,位线在垂直于字线的方向上在nand串顶部延伸,连接到一个或过个感测放大器。应该理解的是,本发明仅是利用图1和图2中的结构实例性的说明nand串结构,在实际应用中,捕获电荷层并不一定是浮置栅极,还可能是捕获氮化层、非导电电介质材料等等。

40.在实际应用过程中,存储器中的存储器阵列是经由图1和图2所示的nand串经过合理布局后形成的包含具有多个存储块的存储器阵列,其实例性的结构如图3所示。存储器阵列300被分成block

1-block

t

具有多个存储块的存储器阵列,其中t为正整数,并且一般为较大的数。每个存储块包含一组nand串,该一组nand串被经由位线bl

0-bl

m-1

和一组公共字线wl

0-wl

n-1

访问,其中,m、n均是大于1整数。nand串的一个端子经由顶部选择栅极sgd(由顶部选择栅极线sgdl控制)连接至对应的位线,另一端经由底部选择栅极sgs(由底部选择栅极线sgsl控制)连接至源极线。在一些实施例中,存储块是常规的擦除单元。在一些实施例中,

存储块可以逻辑上划分成多个页面(page),page是常规的编程和读取单位。在另一些实施例中,也可以使用擦除、编程的其他单位。在实例中,图3示出的存储器阵列中的存储单元物理结构不限制本发明的范围。

41.对于某一存储块的结构,如图4所示,其示出本发明实施例提供的单存储块的三维存储器阵列的结构示意图。参考图4,存储块400包含堆叠在衬底(未示出)之上且平行于衬底表面的多个层,图4示出了四个层上的四个字线(wl),不妨将其记为wl0至wl3。存储块400还布置有多个与字线垂直的通孔。一个字线与一个通孔的交叉点形成一个存储单元,因此也可以将一个通孔称之为存储单元串。本领域技术人员应该理解的是,存储块400的字线的数量和存储单元串的数量不限于特定的值,比如,存储块400可以包括64字线,64个字线与一个存储单元串交叉形成沿着存储单元串的64个存储单元。再比如,存储块400包括存储单元串的数量可以是以十万、百万甚至更大的数量级计算,一个字线上包括其与例如几百万个存储单元串交叉而形成的几百万个存储单元。存储块400中的存储单元可以是单级存储单元或者多级存储单元,其中,单级存储单元可以是能够存储1个比特(bit)的单级单元(slc);多级存储单元可以是能够存储2个bit的多级单元(mlc),能够存储3个bit的三级单元(tlc),能够存储4个bit的四级单元(qlc),能够存储5个bit的五级单元(plc)。如图4所示,存储块400还包括位线(bl)、位线选择器(bls,也可以称之为顶部选择栅极线sgdl)、源极线(sl)、源极选择线(sls,也可称之为底部选择栅极线sgsl),这些电路线和字线(wl)一起可以实现对存储块400中任何存储单元的寻址。

42.图5(a)至图5(e)描绘了对应于图4的三维(3d)nand结构的一部分的结构示意图、剖面图等。图5(a)为本发明实施例提供的描绘图4中三维(3d)nand结构的一部分的结构示意图。需要说明的是,图5(a)中的多个圆圈表示竖直列,每一个竖直列包括多个选择晶体管(也称之为选择栅极或选取栅极)和多个存储单元。在一个实施方案中,每个竖直列实现一个nand串,例如,图5(a)描绘了竖直列501、502、503和504,其中,竖直列501实现nand串501a。竖直列502实现nand串502a。竖直列503实现nand串503a。竖直列503实现nand串503a。应该理解的是,图5(a)仅展示了存储块400顶视的一部分,因此存储块400应该具有比图5(a)展示的更多的竖直列。图5(a)还描绘了一组位线505。图5(a)仅示出了二十四个位线,因为仅示出了该存储块400的一部分。应该理解的是,应该具有多于二十四个位线连接到该存储块400的竖直列。表示竖直列的每个圆圈都有一个“x”以指示其与一个位线连接,例如,位线5051连接到竖直列501、502、503和504。图5(a)中描绘的存储块还包括一组局部互连506、507、508、509和510,该组局部互连将各个层连接到在竖直列下方的源极线。局部互连506、507、508、509和510还用于将存储块400的每个层分为四个区域,例如,图5(a)中描绘的顶层被分为区域511、512、513和514,这些区域被称为指状部。在实现存储单元的存储块的层中,这四个区域被称为字线指状部,它们被局部互连分开。在一个实施方案中,在存储块的公共级上的字线指状部连接在一起以形成单一字线。在另一个实施方案中,在同一级上的字线指状部不连接在一起。在一个示例性实施方式中,位线仅连接到区域511、512、513和514中的每个中的一个竖直列。在该实施方式中,每个存储块具有十六行活动列,并且每个位线连接到每个存储块中的四个行。在一个实施方案中,连接到公共位线的所有四个行都连接到同一字线(经由连接在一起的在同一级上的不同字线指状部);因此,存储器系统使用源极选择线和漏极选择线来选择四个行中要进行存储器操作(编程、验证、读取和/或擦除)的一

个(或另一个子集)。

43.需要说明的是,尽管图5(a)示出了在一个存储块中每个区域具有四行竖直列,四个区域就有十六行竖直列,但是这些确切数字是示例性实施方式。其它实施方案可以包括每一块更多或更少的区域、每一区域更多行或更少行的竖直列、以及每一块更多行或更少行的竖直列。此外,图5(a)还示出了竖直列是交错的。在其它实施方案中,可以使用不同交错模式。在一些实施方案中,竖直列不交错。

44.图5(b)示出了沿图5(a)的线aa的剖视图。该剖视图切穿竖直列502和与竖直列502相邻的515以及区域512(具体参见图5(a))。图5(b)示出存储块400包括:四个漏极侧选择层sgd0、sgd1、sgd2和sgd3;四个源极侧选择层sgs0、sgs1、sgs2和sgs3;六个虚设字线层tswl0、tswl1、bdwl0、bdwl1、wldl、wldu;以及128个数据字线层wll0至wll127,这些数据字线层用于连接到数据存储单元。其它实施方案可实现多于或少于四个漏极侧选择层、多于或少于四个源极侧选择层、多于或少于六个虚设字线层,以及多于或少于128个字线层。竖直列502和515被描绘为突出穿过漏极侧选择层、源极侧选择层、虚设字线层以及字线层。在一个实施方案中,每个竖直列都包括竖直nand串。例如,竖直列502包括nand串502a。在竖直列和下面列出的层之下的是衬底101、衬底上设置有绝缘膜以及源极线sl。竖直列502的nand串在堆叠的底部处具有源极端并且在堆叠的顶部处具有漏极端。与图5(e)一致,图5(b)示出了经由连接器516连接到位线5051的竖直列502。还描绘了局部互连507和508。

45.为了便于引用,漏极侧选择层sgd0、sgd1、sgd2和sgd3;源极侧选择层sgs0、sgs1、sgs2和sgs3;虚设字线层tswl0、tswl1、bdwl0、bdwl1、wldl、wldu;以及字线层wll0至wll127被统称为导电层。在一个实施方案中,导电层可以是由tin和钨的组合制成。在其它实施方案中,也可以使用其它材料形成导电层,诸如掺杂的多晶硅、金属(诸如钨或金属硅化物)。在一些实施方案中,不同导电层可以由不同材料形成。在导电层之间的是介电层dl0至dl145。例如,介电层dl104在字线层wl94上方并且在字线层wl95下方。在一个实施方案中,介电层可以由sio2制成。在其它实施方案中,可以使用其它介电材料形成介电层。

46.其中,非易失性存储单元沿竖直列形成,该竖直列延伸穿过堆叠中的交替的导电层和介电层。在一个实施方案中,存储单元布置在nand串中。字线层wl0至wl127连接到存储单元(也可以称之为字线层wl0至wl127耦接到存储单元,这些数据器单元也可以称之为数据存储单元)。虚设字线层tswl0、tswl1、bdwl0、bdwl1、wldl、wldu连接到虚设存储单元。虚设存储单元不存储主机数据并且没有资格存储主机数据(从主机提供的数据,诸如来自主机用户的数据),而数据存储单元有资格存储主机数据。在一些实施方案中,数据存储单元和虚设存储单元可具有相同结构。虚设字线连接到虚设存储单元。漏极侧选择层sgd0、sgd1、sgd2和sgd3用于将nand串与位线电连接和断开。源极侧选择层sgs0、sgs1、sgs2和sgs3用于将nand串与源极线sl电连接和断开。

47.图5(b)还示出了接合区域。在一个实施方案中,蚀刻与介电层混合的128个字线层是昂贵和/或具有挑战性的。为了减轻这种负担,一个实施方案包括铺设与介电层交替的64个字线层的第一堆叠,铺设接合区域,以及铺设与介电层交替的64个字线层的第二堆叠。接合区域定位在第一堆叠与第二堆叠之间。接合区域用于将第一堆叠连接到第二堆叠。在图5(b)中,第一堆叠可以被标记为字线的下集;第二堆叠可以被标记为字线的上集。在一个实施方案中,接合区域可以由与字线层相同的材料制成。在一个示例性具体实施组中,多条字

线(控制线)可以包括交替的字线层和介电层的第一堆叠、交替的字线层和介电层的第二堆叠,以及第一堆叠与第二堆叠之间的接合区域,如图5(b)所示。

48.图5(c)描绘了图5(b)中部分的存储块的导电层的逻辑表示,比如,具有具有sgd0、sgd1、sgd2、sgd3、sgs0、sgs1、sgs2、sgs3、tswl0、tswl1、bdwl0、bdwl1以及wl0至wl127字线的逻辑表示。根据上面关于图5(a)的描述,在一个实施方案中,局部互连506、507、508、509和510将导电层分成四个区域/指状部(或存储子块),例如,字线层wl126被划分成区域517、518、519和520。对于具有wl0至wl95个字线层,区域被称为字线指状部,因此,字线层wl94被局部互连506、507、508、509和510划分成字线指状部517、518、519和520。在实际使用过程中,区域517是一个字线层上的一个字线指状部。在一个实施方案中,在同一级上的四个字线指状部连接在一起。在另一个实施方案中,每个字线指状部作为单独的字线操作。漏极侧选择栅极层sgd0(顶层)也被划分成区域511、512、513和514,也可以称为指状部或选择线指状部。在一个实施方案中,在同一级上的四个选择线指状部连接在一起。在另一个实施方案中,每个选择线指状部作为单独的字线操作。

49.图5(d)描绘了包括竖直列502(存储器孔)的一部分的图5(b)的区域521的剖视图。在一个实施方案中,竖直列是圆形的;然而,在其它实施方案中,可使用其它形状。在一个实施方案中,竖直列502可以包括由诸如sio2的电介质制成的内芯层522。也可以使用其它材料。包围内芯层522的是多晶硅沟道523。也可以使用除了多晶硅之外的材料。应该注意的是,沟道523连接到位线和源极线。包围沟道523的是隧穿电介质524。在一个实施方案中,隧穿电介质524具有ono结构。包围隧穿电介质524的是电荷捕集层525,诸如氮化硅。也可以使用其它存储器材料和结构。本文所述的技术不限于任何特定材料或结构。

50.图5(d)描绘了介电层dl139、dl138、dl137、dl136和dl135,以及字线wl127、wl126、wl125、wl124和wl123。字线层中的每个字线层包括由氧化铝层526包围的字线区域527,氧化铝层由阻挡氧化物层528包围。字线层与竖直列的物理相互作用形成存储单元。因此,在一个实施方案中,存储单元包括沟道523、隧穿电介质524、电荷捕集层525、阻挡氧化物层528、氧化铝层526以及字线区域527。例如,字线层wl127和竖直列502的一部分构成存储单元mc1。字线层wl126和竖直列502的一部分构成存储单元mc2。字线层wl125和竖直列502的一部分构成存储单元mc3。字线层wl124和竖直列502的一部分构成存储单元mc4。字线层wl123和竖直列502的一部分构成存储单元mc5。在其它架构中,存储单元可具有不同结构;然而,存储单元仍将是数据存储单元。

51.当对存储单元进行编程时,电子存储在与存储单元相关联的电荷捕集层525的一部分中。响应于字线区域527上的适当电压,这些电子通过隧穿电介质524从沟道523被吸引到电荷捕集层525中。存储单元的阈值电压(v

th

)与所存储的电荷量成比例地增大。在一个实施方案中,通过电子的福勒-诺得海姆(fowler-nordheim)隧穿到电荷捕集层中来实现编程。在擦除操作期间,电子返回到沟道或空穴被注入到电荷捕集层中以与电子重组。在一个实施方案中,使用经由诸如栅极感应的漏极泄漏(gidl)的物理机制的空穴注入到电荷捕集层中来实现擦除。

52.图5(e)是图4至图5(d)中描绘的存储器的一部分的示意图。图5(e)示出了跨整个块延伸的物理字线wl0至wl127。图5(e)的结构对应于图5(a)至图5(d)的存储块400的一部分,包括位线505。在该存储块内,每个位线连接到四个nand串。漏极侧选择线sgd0、sgd1、

sgd2和sgd3用于确定四个nand串中的哪一个连接到相关联的一个或多个位线。源极侧选择线sgs0、sgs1、sgs2和sgs3用于确定四个nand串中的哪一个连接到公共源极线。还可以考虑将该块划分成四个存储子块b0、b1、b2和b3。存储子块b0对应于由sgd0和sgs0控制的竖直nand串,存储子块b1对应于由sgd1和sgs1控制的竖直nand串,存储子块b2对应于由sgd2和sgs2控制的竖直nand串,并且存储子块b3对应于由sgd3和sgs3控制的竖直nand串。

53.需要说明的是,图4至图5(e)的示例性存储器系统是包括具有电荷捕集材料的竖直nand串的三维存储器结构,但是其它(2d和3d)存储器结构也可与本文所述的技术一起使用。

54.基于图3所示的存储器阵列,图6示出本发明实施例提供的基于图3所示的存储器阵列形成的用于并行地对存储器阵列的页面(或其他单位)进行读取和/或编程的读写电路的存储器系统60的结构示意图。

55.存储器系统60包括存储器601以及存储器控制器602,其中,存储器601包括存储器阵列300(二维或三维)和外围电路,所述外围电路包括:控制电路6011、读/写电路6012a和6012b、行解码器6013a和6013b以及列解码器6014a和6014b。在一些实施例中,在存储器阵列300的相对侧上以对称的方式实现各种外围电路对存储器阵列300的访问,以使在每侧上的访问先和电路的密度减少一半。读/写电路6012a和6012b包括多个感测块sb,用于对存储器阵列300的页面并行地进行读取或者编程。存储器阵列300可通过字线经由行解码器6013a和6013b以及位线经由列解码器6014a和6014b寻址。在一些实施例中,存储器阵列300、控制电路6011、读/写电路6012a和6012b、行解码器6013a和6013b以及列解码器6014a和6014b可以被制造在芯片上,其中图6中间的虚线框也可以代表芯片。外部信号和数据经由信号线603在主机和存储器控制器602之间传送,并且通过信号线604在存储器控制器602和芯片之间传送。

56.控制电路6011被配置为与读/写电路6012a和6012b协作以对存储器阵列300执行存储操作。控制电路6011包括状态机、片上地址解码器和功率控制模块,其中,状态机被配置为提供存储操作的芯片级控制;片上地址解码器被配置为在主机或存储器系统的控制器使用的地址到行解码器6013a和6013b以及列解码器6014a和6014b使用的硬件地址之间提供地址接口。功率控制模块被配置为在每次存储操作器件控制提供给字线和位线的功率和电压。

57.上面讨论的存储器系统中的存储器阵列可以被擦除、编程和读取。在成功编程过程(具有验证)结束时,在适当时,被编程的存储单元的阈值电压应当在用于经编程的存储单元的阈值电压的一个或者多个分布内或者在经擦除的存储单元的阈值电压的分布内。

58.尽管上面详细介绍了外围电路与存储器阵列300之间的关系,在另一些实施例中,外围电路和存储器阵列还可以以下面图7的结构示出。图7示出了根据本发明的一些方面的包括存储器阵列和外围电路的示例性存储器的块图。

59.图7示出了一些示例性外围电路,外围电路包括页缓冲器704、列解码器706、行解码器708、电压发生器710、控制逻辑单元712、寄存器714、输入/输出(input/output,i/o)电路716。应当理解,在一些示例中,还可以包括图7中未示出的附加外围电路。

60.页缓冲器704可以经由位线连接到存储单元阵列300,并且被配置为根据来自控制逻辑单元712的控制信号从存储器阵列300读取数据以及向存储器阵列300编程(写入)数

据。在一个示例中,页缓冲器704可以存储要被编程到存储器阵列300的一个存储页中的一页编程数据(写入数据)。在另一示例中,页缓冲器704可以感测来自位线的信号,以验证数据已经被正确地编程到耦接到选定字线718的目标存储单元中。在又一示例中,在读取操作中,页缓冲器704还可以感测来自位线的表示存储在存储单元中的数据位的低功率信号,并且将小电压摆幅放大到可识别的逻辑电平。列解码器706可以被配置为由控制逻辑单元712控制,以及通过施加从电压发生器710生成的位线电压来选择一个或多个nand存储器串。

61.行解码器708可以经由字线连接到存储器阵列300,并且可以基于行地址来选择字线。行解码器708可以被配置为由控制逻辑单元712根据控制信号来控制,以及选择/取消选择存储器阵列300的存储块并且选择/取消选择存储块的选定行。行解码器708还可以被配置为将从电压发生器710生成的字线电压提供给字线。在一些实施方式中,行解码器708还可以将从电压发生器710生成的ssg电压和dsg电压提供给驱动ssg线315和dsg线313。

62.电压发生器710可以被配置为由控制逻辑单元712控制,并且生成提供给存储器阵列300的各种电压,例如字线电压(例如,读取电压、编程电压、通过电压、验证电压等)、ssg电压(选择/取消选择电压)、dsg电压(选择/取消选择电压)、位线电压和源极线电压等。

63.控制逻辑单元712可以耦接到上文描述的每个外围电路,并且被配置为控制各个外围电路的操作。寄存器714可以耦接到控制逻辑单元712,并且包括状态寄存器、命令寄存器和地址寄存器,以用于存储用于控制每个外围电路的操作的状态信息、命令操作码和命令地址。控制逻辑单元712可以由微处理器、微控制器(又名微控制器单元(mcu))、数字信号处理器(dsp)、专用集成电路(asic)、现场可编程门阵列(fpga)、可编程逻辑设备(pld)、状态机、门控逻辑单元、分立硬件电路或者它们的组合,以及被配置为执行以下详细描述的各种功能或的其他合适的硬件、固件和/或软件来实现。

64.输入/输出电路716可以耦接到控制逻辑单元712,并且充当控制缓冲器以缓冲从存储器存储器控制器602接收的控制命令并且并将其中继到控制逻辑单元712,以及缓冲从控制逻辑单元712接收的状态信息并且将其中继到存储器控制器。输入/输出电路716还可以耦接到列解码器706,并且充当数据输入/输出接口和数据缓冲器,以缓冲数据并且将其中继到存储器阵列300或从存储器阵列300中继或缓冲数据。

65.需要说明的是,图6和图7从不同角度对外围电路与存储器阵列进行了描述,其中,图6中的控制电路与图7中的控制逻辑单元仅是在不同角度描述下的不同名称而已,二者作用相同。可以理解为相同的结构。

66.图8是阈值电压与存储单元数量的曲线图,并且示出了当每个存储单元存储四位数据时存储器阵列的示例性阈值电压分布。然而,其它实施方案可以使用每一存储单元其它数据容量,比如前述的存储1bit数据的slc、存储2bit数据的mlc、存储3bit数据的tlc、存储5(b)it数据的plc等。存储多于一位数据的存储单元被称为多级单元mlc。图8示出了16个阈值电压分布,其对应16个阈值电压分布:e(也称之为l0)、l1、l2、l3、l4、l5、l6、l7、l8、l9、l10、l11、l12、l13、l14、l15,阈值电压依次升高。同样的,阈值电压分布e对应于擦除数据状态;阈值电压分布l1、l2、l3、l4、l5、l6、l7、l8、l9、l10、l11、l12、l13、l14、l15对应于编程数据状态,对于数据状态n,该数据状态n具有比数据状态n-1更高的阈值电压和比数据状态n+1更低的阈值电压。在一些实施例中,qlc类型的存储单元存储四位数据,具体的,被擦除的存储单元可以存储数据1111,被编程到l1、l2、l3、l4、l5、l6、l7、l8、l9、l10、l11、l12、l13、

l14、l15数据状态的存储单元可以依次存储数据1110、1101、1100、1011、1010、1201、1000、0111、0110、0101、0100、0011、0010、0001、0000。对于数据状态n,该数据状态n具有比数据状态n-1更高的阈值电压和比数据状态n+1更低的阈值电压。第一阈值电压分布对应于数据状态l0表示被擦除的存储单元。其它15个阈值电压分布对应于数据状态l1至l15表示被编程的存储单元,并且因此也称为编程数据状态。在一些实施方案中,数据状态l1-l15可重叠,其中存储器控制器602依赖错误校正来识别正在存储的正确数据。图7还示出了15个读取参考电压vr1、vr2、vr3、vr4、vr5、vr6、vr7、vr8、vr9、vr10、vr11、vr12、vr13、vr14、vr15,用于从存储单元读取数据,具体读取过程可以为:测试,如执行感测操,给定存储单元的阈值电压是高于还是低于15个读取参考电压,存储器系统可以确定存储单元所处于的数据状态。

67.图8还示出了15个验证参考电压vv1、vv2、vv3、vv4、vv5、vv6、vv7、vv8、vv9、vv10、vv11、vv12、vv13、vv14和vv15,这些验证参考电压也可称之为验证目标电压。当将存储单元编程为数据状态l1时,存储器系统将测试这些存储单元是否具有大于或等于vv1的阈值电压。当将存储单元编程为数据状态l2时,存储器系统将测试存储单元是否具有大于或等于vv2的阈值电压。当将存储单元编程为数据状态l3时,存储器系统将确定存储单元是否具有大于或等于vv3的阈值电压。当将存储单元编程为数据状态l4时,系统将测试这些存储单元是否具有大于或等于vv4的阈值电压。当将存储单元编程为数据状态l5时,存储器系统将测试这些存储单元是否具有大于或等于vv5的阈值电压。当将存储单元编程为数据状态l6时,存储器系统将测试这些存储单元是否具有大于或等于vv6的阈值电压。当将存储单元编程为数据状态l7时,存储器系统将测试这些存储单元是否具有大于或等于vv7的阈值电压,其余的数据状态依次验证是否具有大于或等于vv8、vv9、vv10、vv11、vv12、vv13、vv14和vv15,来确定其是否被编程为l8、l9、l10、l11、l12、l13、l14、l15。在被称为全序列编程的一个实施方案中,存储单元可从擦除的数据状态l0直接编程到编程数据状态l1-s15中的任一种。例如,可首先擦除要被编程的存储单元的群体,使得该群体中的所有存储单元处于擦除数据状态l0。然后,使用编程过程来将存储单元直接编程到数据状态l1、l2、l3、l4、l5、l6、l7、l8、l9、l10、l11、l12、l13、l14、l15之一中。例如,虽然一些存储单元正在从数据状态l0编程到数据状态l1,但其它存储单元正在从数据状态l0编程到数据状态l2和/或从数据状态l0编程到数据状态l3,以此类推。图8的箭头表示全序列编程。除全序列编程之外,本文所述的技术还可与其它类型的编程一起使用,包括但不限于多级编程/多相编程。

68.图8的每个阈值电压分布(数据状态)对应于存储在存储单元中的一组数据位的预定值。编程到存储单元中的数据与存储单元的阈值电压电平之间的具体关系取决于存储单元采用的数据编码方案。在一个实施方案中,使用格雷码分配将数据值分配到阈值电压范围,使得如果存储器的阈值电压错误地移位到其相邻物理状态,那么将仅影响一个位。

69.一般来讲,在验证操作和读取操作期间,将选定的字线连接到电压,该电压为参考信号,该电压的电平针对每个读取操作(如,参见图8的读取参考电压)或验证操作(如,参见图8的验证参考电压)指定,以便确定相关存储单元的阈值电压是否已达到这个电平。在施加字线该电压之后,测量存储单元的传导电流以确定该存储单元是否响应于施加到字线的该电压而接通(是否有传导电流,并测量传导电流的大小)。如果传导电流被测量为大于特定值,那么假设存储单元被接通并且施加到字线的电压大于存储单元的阈值电压。如果传导电流未测量为大于特定值,那么假设存储单元未接通并且施加到字线的电压不大于存储

单元的阈值电压。在读取或验证过程期间,未选定的存储单元在其控制栅极处被提供有一个或多个通过电压,也可以称之为旁路电压,使得这些存储单元将作为通过栅极操作,不管这些存储单元是被编程还是被擦除都传导电流。

70.有许多方法来测量读取或验证操作期间存储单元的传导电流。在一个示例中,以存储单元对感测放大器中的专用电容器放电或充电的速率来测量该存储单元的传导电流。在另一个示例中,选定的存储单元的传导电流允许(或不允许)包括存储单元的nand串对对应位线放电,在某时间段之后测量位线上的电压,以查看其是否已经放电。应该注意的是,本文所述的技术可以与本领域中已知的用于验证/读取的不同方法一起使用。也可以使用本领域中已知的其它读取和验证技术。

71.图9是描述由存储器601执行的用于编程的过程的一个实施方案的流程图。在一个示例性实施方案中,图9的过程在状态机的指引下使用上面讨论的控制电路在存储器601上执行。执行图9的过程以实现图8的全序列编程或包括多级编程的其它编程方案。当实施多级编程时,图9的过程用于实施多级编程过程的任何/每个阶段。

72.通常,在编程操作期间将编程信号vpgm(也称之为编程电压、编程脉冲)作为一系列编程电压脉冲施加到控制栅极(经由选定的字线施加),如图10所示。在编程脉冲之间的是一组验证脉冲以执行验证。在一些实施例中,vpgm的幅值随每个连续脉冲而增大预定的步长大小,例如,所述预定的步长大小的范围可以在0.2v至0.5v中选择。在图9的步骤901中,将编程电压(vpgm)初始化为起始幅值,如,起始幅值约12v至16v中的任一电平,或另一个合适的电平,并且将由状态机维持的编程计数器pc初始化为1。在步骤902中,将vpgm的编程脉冲施加到选定的字线(选定的字线为被选择用于编程的字线)。在一个实施方案中,被同时编程的一组存储单元全部都连接到同一字线(该字线为选定的字线)。未选定的字线接收一个或多个升压电压(或者称之为通过电压),如,约7伏至11,以执行本领域中已知的升压方案。在一个实施方案中,如果存储单元应进行编程,则对应位线接地。另一方面,如果存储单元应保持在其当前阈值电压,则对应位线连接到vdd,例如,1v至3.5v,以抑制编程。在步骤902中,将编程电压脉冲同时地施加到连接到选定的字线的所有存储单元,使得同时地对连接到选定的字线的所有存储单元进行编程。也就是说,它们在同一时间上或在重叠时间期间(两者都被视为是同时的)进行编程。以此方式,除非已经将它们锁定以阻止进行编程,否则连接到选定的字线的所有存储单元将同时地具有其阈值电压变化。

73.在步骤903中,使用一组适当验证参考电压以执行一个或多个验证操作来验证适当存储单元。在一个实施方案中,通过测试被选择用于编程的存储单元的阈值电压是否已达到适当验证参考电压来执行验证过程。

74.在步骤904中,确定是否所有存储单元都已达到其目标阈值电压(通过)。若是如此,那么编程过程完成并是成功的,因为所有选择的存储单元都被编程并验证了其目标状态。在步骤905中,报告“通过”(或成功)状态。如果在步骤904中确定不是所有存储单元都已达到其目标阈值电压(失败),那么编程过程将继续到步骤906。

75.在步骤906中,该系统对尚未达到其相应的目标阈值电压分布的存储单元的数量进行计数。即,该系统对目前为止验证过程已失败的存储单元的数量进行计数。该计数可以由状态机、存储器控制器602或其它逻辑部件来完成。在一个具体实施中,感测块中的每个感测块将存储其相应存储单元的状态(通过/失败)。在一个实施方案中,存在一个总计数,

其反映了最后一个验证步骤已失败的当前正在编程的存储单元的总数。在另一个实施方案中,为每个数据状态保留单独计数。

76.在步骤907中,确定来自步骤906的计数是否小于或等于预定的极限。在一个实施方案中,预定的极限是在存储单元的页面的读取过程期间可通过纠错码(ecc)校正的位的数量。如果失败单元的数量小于或等于预定的极限,则编程过程可以停止并且在步骤905中报告“通过”状态。在这种情况下,足够的存储单元被正确地编程,使得可以在读取过程期间使用ecc来校正校正尚未完全地编程的剩余几个存储单元。在一些实施方案中,步骤906将针对每个扇区、每个目标数据状态或其它单元计数失败单元的数量,并且在步骤907中将这些计数单独地或共同地与一个或多个阈值进行比较。

77.在一个实施方案中,预定的极限可以小于在读取过程期间可由ecc校正的位的总数以考虑到未来错误。当对页面的少于所有的存储单元进行编程、或比较仅一个数据状态(或少于所有的状态)的计数时,预定的极限就可以是在存储单元的页面的读取过程期间ecc可校正的位的数量的一部分(按比例或不按比例)。在一些实施方案中,该极限不是预定的。相反,它基于已经为页面计数的错误数量、所执行的编程擦除周期数量或其它标准来改变。

78.如果失败的存储单元的数量不小于预定的极限,则编程过程在步骤908处继续并对照编程极限值(pl)检查编程计数器pc。编程极限值,比如包括6、20和30等等;然而,可以使用其它值。如果编程计数器pc不小于编程极限值pl,则认为编程过程已失败并且在步骤910中报告“失败”状态。如果编程计数器pc小于编程极限值pl,则过程在步骤909处继续,在此期间,编程计数器pc递增1,并且编程电压vpgm被步进到下一幅值。例如,下一脉冲将具有比前一脉冲大一个步长大小的幅值,例如,0.1伏至0.4伏的步长大小。在步骤909之后,过程循环回到步骤902,并且另一个编程脉冲被施加到选定的字线,使得执行图9的编程过程的另一个迭代(步骤902至909)。

79.由于在编程或读取时可能发生错误,并且在存储数据时可能发生错误(例如,由于电子漂移、数据保留问题或其它现象),因此纠错与数据编程一起使用。存储器系统通常使用纠错码(ecc)来保护数据免于损坏。许多ecc编码方案是本领域熟知的。这些常规的纠错码在包括闪存(和其它非易失性)存储器的大容量存储器中尤其有用,因为此类编码方案可提供对制造产率和设备可靠性的实质影响,使得具有几个不可编程或有缺陷的单元的设备成为可用的。当然,在产率节省和提供附加存储单元以存储代码位(即,编码“速率”)的成本之间存在权衡。因此,一些ecc代码比其它ecc代码更适合闪存存储器设备。一般来讲,闪存存储器设备的ecc代码往往具有比数据通信应用中使用的代码(其可具有低至1/2的编码速率)更高的编码速率(即,更低的代码位/数据位比率)。通常与闪存存储器存储装置结合使用的熟知的ecc代码的示例包括里德-所罗门码、其它bch码、汉明码等。有时,与闪存存储器存储装置结合使用的纠错码是“系统的”,因为最终码字的数据部分与被编码的实际数据没有变化,其中代码或奇偶校验位附加到数据位以形成完整的码字。

80.给定纠错码的特定参数包括代码的类型、从中导出码字的实际数据的块的大小以及编码之后码字的总长度。例如,如果使用至少60个ecc或奇偶校验位,则应用于512字节(4096位)数据扇区的典型bch码可校正最多四个错误位。里德-所罗门码是bch码的子集,并且也通常用于纠错。例如,典型的里德-所罗门码可使用约72个ecc位在512字节数据扇区中

校正最多四个错误。在闪存存储器的情况下,纠错编码提供了制造产率以及闪存存储器随时间推移的可靠性的显著改进。

81.在一些实施方案中,存储器控制器602接收要存储在非易失性存储器中的主机数据(也称为用户数据或来自存储器系统外部的实体的数据),也称为信息位。信息位由矩阵i=[1 0]表示(需注意,两个位仅用于示例目的,并且许多实施方案具有长于两个位的码字)。纠错编码过程(诸如上文或下文提到的任何过程)由存储器控制器602的ecc引擎实施,其中奇偶校验位被添加到信息位以提供由矩阵或码字v=[1 0 1 0]表示的数据,指示两个奇偶校验位已经附加到数据位。可使用以更复杂方式将输入数据映射到输出数据的其它技术。例如,可使用低密度奇偶校验(ldpc)码,也称为gallager码。在实施过程中,此类ldpc码通常应用于(例如,通过ecc引擎)跨多个存储元件编码的多个页面,但它们不需要跨多个页面应用。可通过将一个或多个存储单元编程到对应于v的一个或多个编程状态来将数据位映射到逻辑页面并且存储在存储器阵列中。

[0082]

在一个实施方案中,编程用于将存储单元的阈值电压升高到编程数据状态l1至l15中的一者。擦除用于将存储单元的阈值电压降低到擦除数据状态l0。

[0083]

擦除一些存储器设备中的存储单元的一种技术是将p阱(或其它类型的)基板偏置到高电压以对nand沟道充电。将擦除使能电压施加到存储单元的控制栅极,同时使nand沟道处于高电压,以擦除非易失性存储元件(存储单元)。擦除存储单元的另一种方法是生成栅极感应的漏极泄漏(gidl)电流以对nand串沟道充电。将擦除使能电压施加到存储单元的控制栅极,同时保持串沟道电势以擦除存储单元。

[0084]

在一个实施方案中,通过在选择晶体管处漏极到栅极之间的电压差引起带间遂穿(band to band tunneling)效应,生成电子-空穴对,以产生栅诱导漏极泄漏(gidl,gate induced drain leakage)电流。在一个实施方案中,gidl电流可导致一种类型的载流子(例如,空穴)主要移动到nand沟道中,从而升高沟道的电势。通过电场在位线的方向上或在源极线的方向上从沟道中提取另一类型的载流子,例如电子。在擦除期间,空穴可从沟道隧穿到存储单元的电荷存储区,并且与其中的电子重组,以降低存储单元的阈值电压。

[0085]

其中,gidl电流可在nand串的任一端生成,比如,连接到位线的选择晶体管(例如,漏极侧选择晶体管)的两个端子之间电压差可以生成第一gidl电流;再比如,连接到源极线的选择晶体管(例如,源极侧选择晶体管)的两个端子之间电压差可以生成第二gidl电流。基于nand串的仅一端处的gidl电流进行擦除称为单侧gidl擦除。基于nand串的两端的gidl电流进行擦除称为两侧gidl擦除。需要说明的是,对选定的字线进行编程时,施加在选定的字线的电压(施加编程电压vpgm)与施加在未选定的字线、顶部虚设字线、底部虚设字线的电压(施加通过电压vpass)是不同,一般情况下,vpgm不小于vpass。

[0086]

在这种情况下,经研究发现,在3d存储器中,由于相邻字线可能施加不同的电压或处于不同的编程状态,而由此造成的相邻字线的电位差会产生了由低电位字线向高电位字线注入的热载流子,使得耦接到高电位字线的存储单元的阈值电压升高,这种现象称之为热载流子注入效应。

[0087]

前述的这种热载流子注入的现象,比如在某一具有128个字线层的3d nand(字线编号从下自上依次为字线wl0、wl1、wl2、

……

、wl

n-1

,n为不小于1的整数)中,对耦接到字线wl3至wl127的存储单元编程期间,在字线wl2和字线wl1之间尤为明显。在这种热载流子注

入效应的影响下,耦接到字线wl1的存储单元在擦除态对应的阈值电压将朝着正方向漂移(一般擦除态对应的阈值电压为负值),从而耦接到字线wl1的存储单元对应的第一个可读分布将会受到影响。

[0088]

需要说明的是,所说的第一个可读分布可以是指耦接到字线wl1的存储单元处于擦除态对应的阈值电压分布与处于第一个编程数据状态对应的阈值电压分布之间能够用来读取处于擦除态的存储单元上数据的电压区间,这个电压区间也可以称之为e0,如图8中所示的,在qlc类型的存储单元中,数据状态l0对应的阈值电压分布的下尾翼与电压vr1之间的电压区间即为第一个可读分布e0。本领域技术人员应该知道的是,对于qlc类型的存储单元,每两个相邻数据状态之间存在两个可读分布,前一个可读分布用于读取处于前一个数据状态的存储单元上的数据,后一个可读分布用于读取处于后一个数据状态的存储单元上的数据,比如,数据状态l0和数据状态l1之间的可读分布包含e0和e1,其中,e0也即前述的第一个可读分布;e1为电压vr1与数据状态l1对应的阈值电压分布上尾翼之间的电压区间。在一些实施例中,对于qlc类型的存储单元,总共的可读分布可以包含:e0、e1、

……

、e29总共30个可读分布,可记做:esum=e0+e1+

……

+e29。

[0089]

举例来说,如图11所示,其示出具有128层字线的存储器,不同字线编程后对字线wl1与字线wl5的影响的示意图。其中,上边的那个after fine pgm wln+1表示与字线wl1或字线wl5相邻的字线的精细编程,所谓精细编程为多遍编程中的最后一遍编程;after pgm wl63表示对耦接在wl63的存储单元进行编程;after pgm wl127表示对耦接在wl127的存储单元进行编程。从图11所示可知,耦接在字线wl1上的存储单元的阈值电压在对字线wl63和字线wl1编程时向右偏移比较严重,与字线wl5上的存储单元相比,字线wl上的e0问题比较严重。

[0090]

上述情况,特别是在耦接到字线wl1的存储单元及wl1以上字线的存储单元采用qlc时,在对耦接到wl3至wl127的存储单元编程期间,由于耦接到wl1并处于最低数据状态(l0)的存储单元与耦接到wl2并处于最高数据状态(l15)的存储单元之间存在电位差而产生从字线wl2向字线wl1注入的热载流子。在热载流子注入效应的影响下,耦接到字线wl1并处于最低数据状态(l0)的存储单元的阈值电压朝着正方向漂移,从而使得耦接到字线wl1并且在非选择串的存储单元对应的第一个可读分布e0丢失的比较严重。

[0091]

为了解决上述技术问题,如图12所示,本发明实施例提供一种存储器的编程方法,具体的,所述编程方法可以包括:

[0092]

步骤1201:根据编程顺序对选定存储单元串进行编程;

[0093]

步骤1202:在对所述选定存储单元串中与所述多个字线中选定的非边缘字线耦接的存储单元进行编程时,对所述多个字线中的边缘字线施加第一通过电压;对与所述边缘字线相邻的非边缘字线施加第二通过电压;其中,所述边缘字线为所述多个字线中与所述源极线相邻的至少一个字线,或者所述多个字线中与所述位线相邻的至少一个字线;所述非边缘字线为所述多个字线中除所述边缘字线之外的字线;所述选定的非边缘字线与所述边缘字线不相邻;所述第一通过电压小于所述第二通过电压。

[0094]

这里,所述存储器包括:多个存储单元串;每一个存储单元串一端与位线连接,另一端与源极线连接;每一个存储单元串包含串联的多个存储单元;其中,所述多个存储单元分别与多个字线耦接。其中,每一个存储单元具有一条位线。多个存储单元串共用源极线。

[0095]

在步骤1201中,在一些实施例中,所述编程顺序包括正序编程和逆序编程,其中;

[0096]

所述正序编程为对所述选定的存储单元串中的存储单元从邻近源极线的存储单元开始向邻近位线的存储单元的顺序依次进行编程;

[0097]

所述逆序编程为对所述选定的存储单元串中的存储单元从邻近所述位线的存储单元开始向邻近所述源极线的存储单元的顺序依次进行编程。

[0098]

可以理解的是,基于前述图1至7所示的存储器的结构示意图。存储单元串的一端连接源极线;另一端连接位线。这里定义,对一存储单元串中的存储单元,从靠近位线一侧的存储单元向靠近源极线一侧的存储单元依次进行编程称之为逆序编程。对一存储单元串中的存储单元,从靠近源极线一侧的存储单元向靠近位线一侧的存储单元依次进行编程称之为正序编程。也就是说,本发明实施例中的编程顺序可以是正序编程,也可以是逆序编程。

[0099]

在步骤1202中,对于与选定的非边缘字线耦接的存储单元进行编程时,对边缘字线施加第一通过电压;对与所述边缘字线相邻的非边缘字线施加第二通过电压,这里,所述第一通过电压小于所述第二通过电压,以此,减少编程期间,边缘字线与相邻的非边缘字线之间的电压差,进而降低hcl类型的编程干扰。

[0100]

需要说明的是,在上述描述的技术方案中,边缘字线与非边缘字线的划分不是一成不变的,二者是一个相对的概念,换句话说,对于不同的存储器601而言,定义的边缘字线和非边缘字线是不一样的,具体来说,如何定义边缘字线和非边缘字线依据存储器中字线之间受热载流子注入影响的严重程度(依据e0的丢失情况确定)而定,一种可选的确定方式可以为,受热载流子注入影响比较严重的字线以及以下的字线定义为边缘字线;受热载流子注入影响不严重的字线以及以上的字线定义为非边缘字线,比如说,一些存储器601中定义边缘字线包含wl0和wl1(以图5(b)所示结构的存储器阵列),那么此时,非边缘字线就包含wl2及以上的字线。再比如说,一些存储器601中定义的边缘字线包含wl0、wl1、wl2,那么此时,非边缘字线就包含wl3及以上的字线。

[0101]

举例来说,在边缘字线包含字线wl0和wl1,非边缘字线包含字线wl2及以上,并且,在耦接到字线wl1及以上字线的存储单元为qlc类型的存储单元时,按照本发明实施例提供的编程方法,在对耦接到非边缘字线wl3及以上字线的存储单元执行编程时,可以在字线wl0和wl1上施加第一通过电压;在字线wl2上施加第二通过电压,以此,降低字线wl2与字线wl1之间的电位差,从而减少对耦接到字线wl1未选择串的存储单元的第一个读取分布的影响,具体可参考如图13所示。

[0102]

在一些实施例中,所述边缘字线中的每一个边缘字线上施加的第一通过电压可以不相同,比如,前述的边缘字线wl0和wl1,在字线wl0上施加的第一通过电压与在字线wl1上施加的第一通过电压不相同,但其均小于第二通过电压。也就是说,所述第一通过电压可以是一组小于所述第二通过电压的电压值。在一些实施例中,为了降低边缘字线之间的存在的电位差,可以越靠近衬底的边缘字线施加的第一通过电压越小,比如,前述的边缘字线wl0和wl1,在字线wl0上施加的第一通过电压小于在字线wl1上施加的第一通过电压。

[0103]

应该说明的是,这里描述的场景均是在对耦接到所述多个字线中选定的非边缘字线的第一存储单元执行编程时。

[0104]

在一些实施例中,所述编程方法还包括:

[0105]

对其余非边缘字线施加第三通过电压;所述第三通过电压包含一组大于所述第一通过电压的电压。

[0106]

需要说明的是,这里描述的是除了与边缘字线相邻的非边缘字线(比如,wl2)之外,在对所述选定存储单元串中与所述多个字线中选定的非边缘字线耦接的存储单元进行编程时,其余非边缘字线上可以施加第三通过电压。该第三通过电压是一组大于所述第一通过电压的电压。

[0107]

在一些实施例中,在所述多个字线从所述源极线或所述位线开始编号依次为字线wl0、字线wl1、

……

、wlm、

……

、wln、

……

时,所述编程方法还包括:在所述边缘字线包含字线wl0和字线wl1且所述选定的非边缘字线为字线wln时,对未选定的非边缘字线wl2至字线wlm施加的所述第三通过电压等于所述第二通过电压;对未选定的非边缘字线wln-4到字线wlm施加的所述第三通过电压大于所述第二通过电压;其中,n不小于17;m不大于15。

[0108]

需要说明的是,上述施加通过电压的方式是为了减少在对耦接到非边缘字线字线wl17及以上任一非边缘字线的存储单元进行编程时,其他非边缘字线之间因施加的通过电压而引起的编程干扰。

[0109]

作为一种可选的实施方式,在对字线wln进行编程时,对其他字线施加的通过电压,如下表1所示。

[0110]

其中,vpass7也即前述的第一通过电压的一种形式;vpass6也即前述的第二通过电压的一种形式;vpass1、vpass2、vpass3、vpass4也即前述的第三通过电压的一组形式,需要说明的是,vpass6也是第三通过电压中的一个电压。这里,vpass1大于vpass6;vpass6大于vpass7。其余通过电压的大小更具芯片的型号而具体设计。vpgm是编程电压,根据前述描述,vpgm大于所有的通过电压。

[0111]

表1

[0112]

字线wl施加的电压wln&abovevpass2wln+3vpass2wln+2vpass2wln+1vpass3wlnvpgmwln-1vpass3wln-2vpass4wln-3vpass4wln-4&wl16vpass1wl2-wl15vpass6wl0-wl1vpass7

[0113]

本发明实施例提供的编程方法,通过在边缘字线(比如,wl0和wl1)上施加一个小于相邻非边缘字线(比如,字线wl2)上施加的通过电压,以此,将相邻的边缘字线与相邻的非边缘字线(比如,字线wl1和字线wl2)之间的电位差降低,以此减少不相邻的非边缘字线(比如,字线wl3)编程期间边缘字线(比如,字线wl1)上的hci类型干扰。

[0114]

如图14所示,本发明实施例提供一种存储器,所述存储器601,包括存储器阵列,所

述存储器阵列包括多个存储单元串;每一个存储单元串一端与位线连接,另一端与源极线连接;每一个存储单元串包含串联的多个存储单元;其中,所述多个存储单元分别与多个字线耦接;

[0115]

以及耦接在所述存储器阵列且用于控制所述存储器阵列的控制电路;

[0116]

其中,所述控制电路被配置为:

[0117]

根据编程顺序对选定存储单元串进行编程;

[0118]

在对所述选定存储单元串中与所述多个字线中选定的非边缘字线耦接的存储单元进行编程时,对所述多个字线中的边缘字线施加第一通过电压;对与所述边缘字线相邻的非边缘字线施加第二通过电压;其中,所述边缘字线为所述多个字线中与所述源极线相邻的至少一个字线,或者所述多个字线中与所述位线相邻的至少一个字线;所述非边缘字线为所述多个字线中除所述边缘字线之外的字线;所述选定的非边缘字线与所述边缘字线不相邻;所述第一通过电压小于所述第二通过电压。

[0119]

需要说明的是,前述附图1至7所描述的存储器仅是为了实例性的说明存储器中包含的存储单元串、存储块、存储子块、字线、位线等等之间的部分连接关系以及部分工作原理,并不用于限制本发明,也就是说,本发发明实施例中所描述的存储器601可以是附图1至7描述的结构,也可以是具有类似功能的其他实现的结构。在一些实施例中,所述多个字线可以均包含在第一堆叠;所述第一堆叠还包含与字线交替铺设的介电层,也就是说,第一堆叠可以是字线与介电层交替铺设的,在一些实施例中,所述多个字线所采用的材质可以为前述描述字线材质的任一种;所述介电层所采用的材质可以为前述描述的介电层所采用的材质的任一种。

[0120]

在一些实施例中,基于前述描述,由于蚀刻与介电层混合的多个字线是昂贵的和/或具有挑战性的,为了减轻这种负担,本发明实施例提供的存储器也可以将所述多个字线包含在第一堆叠和第二堆叠,并利用接合区域将所述第一堆叠和所述第二堆叠连接,其中,所述接合区域的材质可以与字线所采用的材质相同。在一些实施例中,在所述第一堆叠中字线的编号小于在所述第二堆叠中字线的编号。

[0121]

在一些实施例中,本发明实施例提供的存储器中的所述选定的非边缘字线可以在所述第一堆叠或在所述第二堆叠。

[0122]

在一些实施例中,其中本发明实施例提供的存储器中的所述存储阵列可以为三维nand存储阵列,也可以为其它3d存储阵列。

[0123]

在一些实施例中,所述控制电路还被配置为:对其余非边缘字线施加第三通过电压;所述第三通过电压包含一组大于所述第一通过电压的电压。

[0124]

在一些实施例中,在所述多个字线从所述源极线或所述位线开始编号依次为字线wl0、字线wl1、

……

、wlm、

……

、wln、

……

时,所述控制电路还被配置为:在所述边缘字线包含字线wl0和字线wl1且所述选定的非边缘字线为字线wln时,对未选定的非边缘字线wl2至字线wlm施加的所述第三通过电压等于所述第二通过电压;对未选定的非边缘字线wln-4到字线wlm施加的所述第三通过电压大于所述第二通过电压;其中,n不小于17;m不大于15。

[0125]

在所述存储器装为3d nand存储器时,为了保证一部分的读写速度,在一些实施例中,耦接到所述字线wl0的存储单元为单级单元slc、多级单元mlc及三级单元tlc存储单元之一;耦接到其余字线的存储单元为四级单元qlc存储单元。在另一些实施例中,为了保证

存储容量,将耦接到所述多个字线中的每一个存储单元设置为多级单元mcl存储单元、tlc存储单元、qlc存储单元、五级单元plc存储单元中的一个。这仅是一部分实例性的设置方式,具体如何设置可以按照客户需求而定。

[0126]

需要说明的是,该存储器与前述的编程方法属于同一发明构思,二者具有相同的技术特征,该存储器中出现的名词在前述的编程方法中均以详细解释,在此同样适用,不再一一赘述。

[0127]

本发明实施例提供的存储器,通过在边缘字线(比如,wl0和wl1)上施加一个小于相邻非边缘字线(比如,字线wl2)上施加的通过电压,以此,将相邻的边缘字线与非边缘字线(比如,字线wl1和字线wl2)之间的电位差降低,以此减少选定的非边缘字线(比如,字线wl3及以上字线任一)编程期间边缘字线(比如,字线wl1)上的hci类型干扰。

[0128]

基于与前述同样的发明构思,如图15所示,本发明实施例还提供一种存储器系统60,包括存储器601,所述存储器包含包括存储器阵列,所述存储器阵列包括多个存储单元串;每一个存储单元串一端与位线连接,另一端与源极线连接;每一个存储单元串包含串联的多个存储单元;其中,所述多个存储单元分别与多个字线耦接;

[0129]

以及耦接在所述存储器阵列且用于控制所述存储器阵列的控制电路;

[0130]

其中,所述控制电路被配置为:

[0131]

根据编程顺序对选定存储单元串进行编程;

[0132]

在对所述选定存储单元串中与所述多个字线中选定的非边缘字线耦接的存储单元进行编程时,对所述多个字线中的边缘字线施加第一通过电压;对与所述边缘字线相邻的非边缘字线施加第二通过电压;其中,所述边缘字线为所述多个字线中与所述源极线相邻的至少一个字线,或者所述多个字线中与所述位线相邻的至少一个字线;所述非边缘字线为所述多个字线中除所述边缘字线之外的字线;所述选定的非边缘字线与所述边缘字线不相邻;所述第一通过电压小于所述第二通过电压。

[0133]

以及,

[0134]

耦接到所述存储器的存储器控制器602,所述控制器被配置为控制所述存储器。

[0135]

需要说明的是,该存储器系统60可以与前述图6中的主机(host)通信。其中,所述主机和/或所述存储器系统60可以包含在各种产品,比如,物联网(iot)器件,如冰箱或者其他设备、传感器、电动机、移动通信器件、汽车、无人驾驶等,用于支持产品的处理、通信或者控制。在一种实施例中,存储器系统60可以为主机器件的离散存储器或存储器组件。在另一些实施例中,存储器系统60还可以为集成电路的一部分,如,芯片上系统(soc,system on chip)的一部分。此时,存储器系统60与主机的一个或多个组件堆叠或以其他方式组装在一起。在另一些实施例中,前述的存储器系统可以实施例并封装在存储卡、驱动器等产品中,比如图16(a)和图16(b)所示,其中,图16(a)示出了根据本发明提供的一些方面的具有存储器系统的示例性存储器卡的示意图;图图16(b)示出了根据本发明的一些方面的具有存储器系统的示例性固态驱动器(ssd)的示意图。在如图16(a)中所示的一个示例中,存储器系统的存储器控制器602和单个存储器601可以集成到存储器卡160中。存储器卡160可以包括pc卡(pcmcia,个人计算机存储器卡国际协会)、cf卡、智能媒体(sm)卡、存储器棒、多媒体卡(mmc、rs-mmc、mmcmicro)、sd卡(sd、minisd、microsd、sdhc)、ufs等。存储器卡160还可以包括将存储器卡160与主机(例如,图6中的主机)耦接的存储器卡连接器1401。在如图图16(b)

中所示的另一示例中,存储器存储器控制器602和多个存储器601可以集成到ssd161中。ssd161还可以包括将ssd161与主机(例如,图6中的主机)耦接的ssd连接器1611。在一些实施方式中,ssd161的存储容量和/或操作速度大于存储器卡160的存储容量和/或操作速度。

[0136]

在一些实施例中,主机可以包括处理器和主机ram,其中,所述主机ram可以包括dram、sdram或任何其它合适的易失性或者非易失性存储器件。所述存储器系统60上可以设置一个或者多个通信接口,与主机中的一个或者多个组件及进行通信。所说的主机中的一个或者多个组件可以为串行高级技术附接(sata)接口、高速外围组件互连(pcie)接口、通用串行总线(usb)接口、通用快闪存储(ufs)接口、emmctm接口等等。主机还可以包括电子元件、存储器卡读取器或存储器系统60外部的一个或多个其它电子元件。

[0137]

在一些实施例中,存储器控制器602可从主机接收指令,与所述存储器601进行通信,如存储器控制器602通过执行写入或者擦除指令将数据传送到所述存储器601中的一个或多个存储单元、平面、子块、块或页中;或者存储器控制器602通过执行读取指令将数据传送给主机。在硬件上,所述存储器控制器602可包括一或多个控制器单元、电路或组件,被配置为控制跨越所述存储器601的访问且提供主机与所述存储器系统60之间的转换层。存储器控制器602还可包括一个或多个输入/输出(i/o)电路、线或接口以将数据传送到所述存储器601,或者从所述存储器601中传输数据。存储器控制器602还可包括存储器管理单元和阵列控制单元。

[0138]

所述存储器管理单元可包括电路硬件或固件,比如与各种存储器管理功能相关联的多个组件或集成电路。以nand存储器为例存储器系统操作或管理功能。本领域技术人员应该知道,其他形式的非易失性存储器可具有类似的存储器操作或管理功能。其中,nand存储器的管理功能可包括磨损均衡,如垃圾收集或回收、错误检测或纠错、块引退或者一个或多个其它存储器管理功能。所述存储器管理单元可将主机的指令处理成所述存储器系统60可识别的命令,比如,将从主机接收到的指令解析或者格式化成与所述存储器601的操作相关的命令等;或者所述存储器管理单元还可生成用于所述阵列控制单元或者所述存储器系统60的一个或多个其他组件的器件命令,如,实现各种存储器管理功能的命令。

[0139]

所述存储器管理单元可被配置为包含一组管理表,该一组管理表用于维护与所述存储器系统60的一个或多个组件关联的各种信息,如,与耦接到所述存储器控制器602的存储器阵列,或者一个或多个存储单元相关的各种信息,比如,所述管理表可包含耦接到存储器控制器602上的存储单元一个或多个块的块年龄、块擦除计数、错误历史或一个或多个错误计数等信息。其中,错误计数可以包括操作错误计数、读位错误计数等。在一些实施例中,在检测到的错误计数高于一定阈值的情况下,位错误则是不可纠正的位错误。在一些实施例中,管理表可维护可校正或不可校正位错误的计数等。管理表还可以包含一个或多个l2p表,其包含一个或多个使用逻辑地址与所述存储器601处对的物理地址相关联的l2p指针。在一些实施例中,管理表可以包含未加密l2p表和/或加密l2p表。未加密l2p表可以包括指示未加密逻辑地址和未加密物理地址的l2p指针;加密l2p表可以包含加密物理地址和未加密逻辑地址的加密l2p指针。在实际应用过程中,所述管理表可以在所述存储器管理单元处示出,也即所述管理表可以存储在存储器控制器602的ram。在另一些实施例中,所述管理表还可以存储在所述存储器601。在使用时,所述存储器管理单元可从存储器控制器602的ram读取缓存的部分或全部管理表;也可以从所述存储器601读取所述管理表。

[0140]

所述阵列控制单元可以包含电路系统或组件,被配置成控制完成以下相关的存储器操作,比如,所述阵列控制单元控制将数据写入到耦接在所述存储器控制器602的存储器系统60中的一个或多个存储单元,从所述一个或多个存储单元读取数据,或擦除所述一个或多个存储单元。所述阵列控制单元可接收到所述主机发送的命令,或所述存储器管理单元内部生成的主机命令,主机命令可以为与耗损均衡、错误检测或校正等关联的命令。

[0141]

所述阵列控制单元还可包括错误校正码(ecc)组件,其可包含用于检测或校正与以下相关错误的ecc引擎或其他电路系统,其中相关错误可以为将数据写入到耦接在所述存储器控制器602的存储器系统60中的一个或多个存储单元或从所述一个或多个存储单元读取数据过程中可能出现的错误。存储器控制器602被配置为有效检测与各种操作或数据存储相关的错误事件,所说错误事件,比如,位错误、操作错误等等,并从所述错误事件中恢复,同时维持在主机与存储器系统60之间传输数据的完整性,或者维持所存储数据的完整性,比如可以使用冗余raid存储等,可以移除,如引退发生故障的存储器资源,如,存储单元、存储器阵列、页、块等,用于防止未来的错误。

[0142]

在一些实施例中,其中,所述多个字线均包含在第一堆叠;所述第一堆叠还包含与字线交替铺设的介电层。

[0143]

在一些实施例中,其中,所述多个字线包含在第一堆叠和第二堆叠,其中,在所述第一堆叠中字线的编号小于在所述第二堆叠中字线的编号。

[0144]

在一些实施例中,其中,所述选定的非边缘字线在所述第一堆叠或在所述第二堆叠。

[0145]

在一些实施例中,其中,其中所述存储阵列为三维nand存储阵列。

[0146]

需要说明的是,该存储器系统包含前述的存储器,因此,二者具有相同的技术特征,该存储器系统中出现的名词在前述的存储器中均以详细解释,在此同样适用,不再一一赘述。

[0147]

以上描述旨在是说明性的,而不是限制性的。例如,上述实例(或其一或多个方面)可以彼此组合使用。可使用其它实施例,诸如所属领域的普通技术人员在阅读以上描述时可使用的。应当理解,它将不用于解释或限制权利要求的范围或含义。此外,在以上详细描述中,可将各种特征组合在一起以简化本发明。这不应当被解释为意味着未经要求保护的公开特征对于任何权利要求是必不可少的。相反,公开主题可在于少于特定公开实施例的所有特征。因此,随附权利要求由此被并入详细说明中,其中每一权利要求独立地作为单独的实施例,并且预期这些实施例可以以各种组合或置换而彼此组合。本发明的范围应当参考随附权利要求以及这些权利要求所赋予的等同物的全部范围来确定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1