基于可变电容的单端灵敏放大电路

1.本发明涉及一种单端灵敏放大电路,尤其是涉及一种基于可变电容的单端灵敏放大电路。

背景技术:

2.灵敏放大电路是静态随机存储器(static random access memory,sram)的一个重要电路,它的功能主要是将位线的数据进行放大输出。对于差分输出的存储阵列,由于差分的灵敏放大电路灵敏度较高,可识别位线对的电压差较小,所以,通常sram的存储阵列(由多个子阵列构成)的一对差分位线对所挂载的存储单元数目会比较多,可达64或128个,保证了sram的存储密度。而对于单端输出的存储阵列,由于无法采用通用的差分灵敏放大电路,使得大多数单端输出的存储阵列采用多级单端动态位线的输出策略,导致单端输出的存储阵列的一条单端位线所挂载的存储单元数目会比较少,一般为8个或16个,严重影响sram的存储密度。因此,研发用于单端输出的存储阵列的单端灵敏放大电路来提高sram的存储密度是一个亟待解决的问题。

3.目前,针对sram提出的灵敏放大电路技术主要以差分灵敏放大电路为主,也有少量的单端灵敏放大电路。例如,作者sharifkhani m等人,在杂志“ieee trans.very large scale integration”上,提出了一种差分结构的混合型灵敏放大电路,它同时混合了电压型和电流型锁存灵敏放大电路,几乎可以达到“0”静态电流。作者nambu h等人,在国际固态电路会议“international solid-state circuit conference(isscc)”上,提出了一种电流镜差分灵敏放大器,它可以将非常小的读电流进行放大输出。作者qazi m等人针对单端8管sram,在国际固态电路杂志“journal solid-state circuit(jssc)”上提出一种单端灵敏放大电路,它可以有效的增加8t-sram的存储密度,局部位线(local bitline,lbl)上一共挂载了256个存储单元,sram容量达到了512kb,并且它的工作电压幅度范围为1.2v~0.57v,最快数据读出时间为400ps,0.57v时读操作速度也有3.4ns。虽然该单端灵敏放大电路有效的增加了8t-sram的存储密度,但是,它采用了特殊的soi工艺,而且耦合电容采用的是厚栅氧层的mos管电容,单个电容的面积达到了4μm2,并不适合通用的cmos工艺。

4.上述第一种灵敏放大电路和第二种灵敏放大电路只支持差分输出,无法实现单端放大输出,不能用于单端输出的存储阵列来提高sram的存储密度,而第三种灵敏放大电路虽然能够实现单端输出,可以有效提高sram的存储密度,但是其需要特殊工艺支持,工艺成本比较高。

技术实现要素:

5.本发明所要解决的技术问题是提供一种能够实现单端输出,可以有效提高sram的存储密度,且不需要特殊工艺支持,采用通用的cmos工艺即可实现,工艺成本比较低的基于可变电容的单端灵敏放大电路。

6.本发明解决上述技术问题所采用的技术方案为:一种基于可变电容的单端灵敏放

大电路,包括开关电路、交叉耦合辅助放大电路和可变电容;所述的开关电路包括第一nmos管和第二nmos管,所述的第一nmos管的栅极为所述的开关电路的控制端,用于接入列选择信号sel,所述的第一nmos管的漏极为所述的开关电路的输入端,用于连接sram的全局位线grbl,所述的第一nmos管的源极和所述的第二nmos管的漏极连接且其连接端为所述的开关电路的输出端,所述的第二nmos管的源极接地,所述的第二nmos管的栅极为所述的开关电路的时钟端,用于接入时钟信号clkn;所述的交叉耦合辅助放大电路包括第一pmos管、第二pmos管、第三pmos管和第三nmos管,所述的第一pmos管的源极、所述的第二pmos管的源极和所述的第三pmos管的源极均接入电源,所述的第一pmos管的栅极、所述的第二pmos管的漏极、所述的第三pmos管的漏极和所述的第三nmos管的漏极连接且其连接端为所述的交叉耦合辅助放大电路的输出端,用于连接后级动态锁存器,所述的第一pmos管的漏极、所述的第二pmos管的栅极、所述的第三pmos管的栅极和所述的第三nmos管的栅极连接,且其连接端为所述的交叉耦合辅助放大电路的输入端,所述的第三nmos管的源极接地;所述的可变电容采用一个本征掺杂层的nmos管实现,将该nmos管称为第四nmos管,所述的第四nmos管的栅级为可变电容的一端,记为电容节点san,所述的第四nmos管的源极和其漏极连接且其连接端为所述的可变电容的另一端,所述的可变电容的另一端用于接入使能信号sa,所述的使能信号sa为脉冲信号;所述的开关电路的输出端和所述的交叉耦合辅助放大电路的输入端均与所述的电容节点san连接。

7.所述的使能信号sa通过第一反相器和第二反相器进入所述的可变电容的另一端,所述的第一反相器的输入端接入所述的使能信号sa,所述的第一反相器的输出端和所述的第二反相器的输入端连接,所述的第二反相器的输出端和所述的可变电容的另一端连接。该结构中,使能信号sa通过第一反相器和第二反相器进入可变电容的另一端,可以使所述的电容节点san的电荷具有高偏斜,使电容节点san的电荷可以快速传递,提高数据读取的速度。

8.与现有技术相比,本发明的优点在于通过开关电路、交叉耦合辅助放大电路和可变电容构建基于可变电容的单端灵敏放大电路,开关电路包括第一nmos管和第二nmos管,第一nmos管的栅极为开关电路的控制端,用于接入列选择信号sel,第一nmos管的漏极为开关电路的输入端,用于连接sram的全局位线grbl,第一nmos管的源极和第二nmos管的漏极连接且其连接端为开关电路的输出端,第二nmos管的源极接地,第二nmos管的栅极为开关电路的时钟端,用于接入时钟信号clkn,交叉耦合辅助放大电路包括第一pmos管、第二pmos管、第三pmos管和第三nmos管,第一pmos管的源极、第二pmos管的源极和第三pmos管的源极均接入电源,第一pmos管的栅极、第二pmos管的漏极、第三pmos管的漏极和第三nmos管的漏极连接且其连接端为交叉耦合辅助放大电路的输出端,用于连接后级动态锁存器,第一pmos管的漏极、第二pmos管的栅极、第三pmos管的栅极和第三nmos管的栅极连接,且其连接端为交叉耦合辅助放大电路的输入端,第三nmos管的源极接地,可变电容采用一个本征掺杂层的nmos管实现,将该nmos管称为第四nmos管,第四nmos管的栅级为可变电容的一端,记为电容节点san,第四nmos管的源极和其漏极连接且其连接端为可变电容的另一端,可变电容的另一端用于接入使能信号sa,使能信号sa为脉冲信号,开关电路的输出端和交叉耦合辅助放大电路的输入端均与电容节点san连接;当单端灵敏放大电路用于具有单端输出的存储阵列的sram时,开关电路的输入端连接该sram的全局位线grbl,该sram中单端输出的

存储阵列的各子阵列分别通过局部位线连接在全局位线grbl上,每个子阵列挂载若干个存储单元,单端灵敏放大电路对sram的数据进行读出操作时,在列选择信号sel控制下选择对应列的存储单元,sram的局部位线的电压差生变化,此时会引起全局位线grbl的微小电压变化,而全局位线grbl的电压变化通过开关电路传递到电容节点san,使电容节点san的电压产生变化,电容节点san的电压变化致使第四nmos管开启,从而导致可变电容的电容发生了变化,使能信号sa利用电容的耦合作用使电容节点san的电压进行第一级放大,此时若电容节点san的电压大于等于交叉耦合辅助放大电路的开关阈值,则交叉耦合辅助放大电路启动,对电容节点san的电压进行第二级放大,将电容节点san的电压放大至高电平,在其输出端输出逻辑“0”到后级动态锁存器进行数据存储,若电容节点san的电压小于交叉耦合辅助放大电路的开关阈值,则交叉耦合辅助放大电路关断,在其输出端输出“1”到后级动态锁存器进行数据存储,从而实现数据单端放大输出,由此本发明能够实现单端输出,可以有效提高sram的存储密度,且不需要特殊工艺支持,采用通用的cmos工艺即可实现,工艺成本比较低。

附图说明

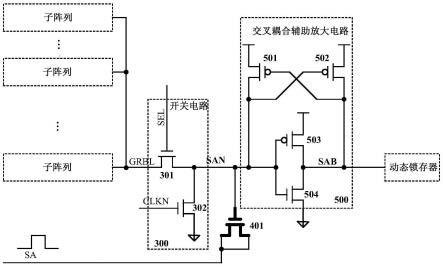

9.图1为本发明的基于可变电容的单端灵敏放大电路实施例一的电路图;

10.图2为本发明的基于可变电容的单端灵敏放大电路实施例二的电路图。

具体实施方式

11.以下结合附图实施例对本发明作进一步详细描述。

12.实施例一:一种基于可变电容的单端灵敏放大电路,包括开关电路300、交叉耦合辅助放大电路500和可变电容;开关电路300包括第一nmos管301和第二nmos管302,第一nmos管301的栅极为开关电路300的控制端,用于接入列选择信号sel,第一nmos管301的漏极为开关电路300的输入端,用于连接sram的全局位线grbl,第一nmos管301的源极和第二nmos管302的漏极连接且其连接端为开关电路300的输出端,第二nmos管302的源极接地,第二nmos管302的栅极为开关电路300的时钟端,用于接入时钟信号clkn;交叉耦合辅助放大电路500包括第一pmos管501、第二pmos管502、第三pmos管503和第三nmos管504,第一pmos管501的源极、第二pmos管502的源极和第三pmos管503的源极均接入电源,第一pmos管501的栅极、第二pmos管502的漏极、第三pmos管503的漏极和第三nmos管504的漏极连接且其连接端为交叉耦合辅助放大电路500的输出端,用于连接后级动态锁存器,第一pmos管501的漏极、第二pmos管502的栅极、第三pmos管503的栅极和第三nmos管504的栅极连接,且其连接端为交叉耦合辅助放大电路500的输入端,第三nmos管504的源极接地;可变电容采用一个本征掺杂层的nmos管实现,将该nmos管称为第四nmos管401,第四nmos管401的栅级为可变电容的一端,记为电容节点san,第四nmos管401的源极和其漏极连接且其连接端为可变电容的另一端,可变电容的另一端用于接入使能信号sa,使能信号sa为脉冲信号;开关电路300的输出端和交叉耦合辅助放大电路500的输入端均与电容节点san连接。

13.当本实施例的单端灵敏放大电路用于具有单端输出的存储阵列的sram时,开关电路300的输入端连接该sram的全局位线grbl,该sram中单端输出的存储阵列的各子阵列分别通过局部位线连接在全局位线grbl上,每个子阵列挂载若干个存储单元,单端灵敏放大

电路对sram的数据进行读出操作时,在列选择信号sel控制下选择对应列的存储单元,sram的局部位线的电压差生变化,此时会引起全局位线grbl的微小电压变化,而全局位线grbl的电压变化通过开关电路300传递到电容节点san,使电容节点san的电压产生变化,电容节点san的电压变化致使第四nmos管401开启,从而导致可变电容的电容发生了变化,使能信号sa利用电容的耦合作用使电容节点san的电压进行第一级放大,此时若电容节点san的电压大于等于交叉耦合辅助放大电路500的开关阈值,则交叉耦合辅助放大电路500启动,对电容节点san的电压进行第二级放大,将电容节点san的电压放大至高电平,在其输出端输出逻辑“0”到后级动态锁存器进行数据存储,若电容节点san的电压小于交叉耦合辅助放大电路500的开关阈值,则交叉耦合辅助放大电路500关断,在其输出端输出“1”到后级动态锁存器进行数据存储,从而实现数据单端放大输出。

14.实施例二:本实施例与实施例一基本相同,区别仅在于:本实施例中,使能信号sa通过第一反相器f1和第二反相器f2进入可变电容的另一端,第一反相器f1的输入端接入使能信号sa,第一反相器f1的输出端和第二反相器f2的输入端连接,第二反相器f2的输出端和可变电容的另一端连接。

15.本实施例中,使能信号sa通过第一反相器f1和第二反相器f2进入可变电容的另一端,可以使电容节点san的电荷具有高偏斜,使电容节点san的电荷可以快速传递,提高数据读取的速度。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1