内嵌交叉结构的亚阈值P-P-N型10管存储单元

n型10管存储单元,包括一对内嵌交叉结构的交叉耦合p-p-n型反相器、两组nmos传输管、四个存储结点、字线wl、写字线wwl和一对位线,将一对内嵌交叉结构的交叉耦合p-p-n型反相器分别称为第一p-p-n型反相器和第二p-p-n型反相器,将两组nmos传输管分别称为第一组nmos传输管和第二组nmos传输管,将四个存储结点分别称为第一存储结点、第二存储结点、第三存储结点和第四存储结点,将一对位线分别称为位线bl和位线blb;所述的第一p-p-n型反相器包括第一pmos管、第二pmos管和第一nmos管,所述的第一pmos管的源极接入电源,所述的第一pmos管的栅极、所述的第一nmos管的栅极连接且其连接端为所述的第一p-p-n型反相器的输出端,所述的第一p-p-n型反相器的输出端和所述的第二存储结点连接,所述的第一pmos管的漏极、所述的第二pmos管的源极均与所述的第一存储结点连接,所述的第二pmos管的漏极和所述的第一nmos管的漏极均与所述的第三存储结点连接,所述的第一nmos管的源极接地,所述的第二pmos管的栅极和所述的第四存储结点连接;所述的第二p-p-n型反相器包括第三pmos管、第四pmos管和第二nmos管,所述的第三pmos管的源极接入电源,所述的第三pmos管的栅极、所述的第二nmos管的栅极连接且其连接端为所述的第二p-p-n型反相器的输入端,所述的第二p-p-n型反相器的输入端和所述的第一存储结点连接,所述的第三pmos管的漏极、所述的第四pmos管的源极均与所述的第二存储结点连接,所述的第四pmos管的漏极和所述的第二nmos管的漏极均与所述的第四存储结点连接,所述的第二nmos管的源极接地,所述的第四pmos管的栅极和所述的第三存储结点连接;所述的第二pmos管和所述的第四pmos管相互交叉耦合,构成内嵌的交叉结构,所述的第一p-p-n型反相器和所述的所述的第二p-p-n型反相器相互交耦合,构成所述的存储单元的存储核心;所述的第一组nmos传输管包括第三nmos管和第四nmos管,所述的第三nmos管的栅极和所述的写字线wwl连接,所述的第三nmos管的源极和所述的位线bl连接,所述的第三nmos管的漏极和所述的第一存储结点连接,所述的第四nmos管的栅极和所述的字线wl连接,所述的第四nmos管的源极和所述的位线bl连接,所述的第四nmos管的漏极和所述的第三存储结点连接,所述的第二组nmos传输管包括第五nmos管和第六nmos管,所述的第五nmos管的栅极和所述的写字线wwl连接,所述的第五nmos管的源极和所述的位线blb连接,所述的第五nmos管的漏极和所述的第二存储结点连接,所述的第六nmos管的栅极和所述的字线wl连接,所述的第六nmos管的源极和所述的位线blb连接,所述的第六nmos管的漏极和所述的第四存储结点连接。

7.与现有技术相比,本发明的优点在于通过一对内嵌交叉结构的交叉耦合p-p-n型反相器、两组nmos传输管、四个存储结点、字线wl、写字线wwl和一对位线构成内嵌交叉结构的亚阈值p-p-n型10管存储单元,将一对内嵌交叉结构的交叉耦合p-p-n型反相器分别称为第一p-p-n型反相器和第二p-p-n型反相器,将两组nmos传输管分别称为第一组nmos传输管和第二组nmos传输管,将四个存储结点分别称为第一存储结点、第二存储结点、第三存储结点和第四存储结点,将一对位线分别称为位线bl和位线blb;第一p-p-n型反相器包括第一pmos管、第二pmos管和第一nmos管,第一pmos管的源极接入电源,第一pmos管的栅极、第一nmos管的栅极连接且其连接端为第一p-p-n型反相器的输出端,第一p-p-n型反相器的输出端和第二存储结点连接,第一pmos管的漏极、第二pmos管的源极均与第一存储结点连接,第二pmos管的漏极和第一nmos管的漏极均与第三存储结点连接,第一nmos管的源极接地,第二pmos管的栅极和第四存储结点连接;第二p-p-n型反相器包括第三pmos管、第四pmos管和

第二nmos管,第三pmos管的源极接入电源,第三pmos管的栅极、第二nmos管的栅极连接且其连接端为第二p-p-n型反相器的输入端,第二p-p-n型反相器的输入端和第一存储结点连接,第三pmos管的漏极、第四pmos管的源极均与第二存储结点连接,第四pmos管的漏极和第二nmos管的漏极均与第四存储结点连接,第二nmos管的源极接地,第四pmos管的栅极和第三存储结点连接;第二pmos管和第四pmos管相互交叉耦合,构成内嵌的交叉结构,第一p-p-n型反相器和第二p-p-n型反相器相互交耦合,构成存储单元的存储核心;第一组nmos传输管包括第三nmos管和第四nmos管,第三nmos管的栅极和写字线wwl连接,第三nmos管的源极和位线bl连接,第三nmos管的漏极和第一存储结点连接,第四nmos管的栅极和字线wl连接,第四nmos管的源极和位线bl连接,第四nmos管的漏极和第三存储结点连接,第二组nmos传输管包括第五nmos管和第六nmos管,第五nmos管的栅极和写字线wwl连接,第五nmos管的源极和位线blb连接,第五nmos管的漏极和第二存储结点连接,第六nmos管的栅极和字线wl连接,第六nmos管的源极和位线blb连接,第六nmos管的漏极和第四存储结点连接,第一存储结点和第三存储结点构成第一对存储结点,第二存储结点和第四存储结点构成第二对存储结点,第一组nmos传输管与第一对存储结点相连,构成存储单元的读电路,第二组nmos传输管与第二对存储结点相连,与第一组nmos传输管一起构成存储单元的写电路,当存储单元处于非工作状态时,数据通过一对内嵌交叉结构的交叉耦合p-p-n型反相器进行保持,当存储单元处于写操作状态时,写字线wwl和字线wl都开启,位线bl和位线blb的数据通过两组nmos传输管分别差分写入四个存储结点之中,当存储单元处于读操作状态时,字线wl开启,写字线wwl关断,数据通过第一组nmos传输管差分传送到位线bl和位线blb上,由于第一对存储结点和第二对存储结点彼此相互隔离,所以读操作期间的噪声无法影响存储单元的存储数据,即消除了读破坏,提高了存储单元的读噪声容限,由此本发明能够在亚阈值电压下工作,具有非常高的读、写噪声容限,不容易受到噪声的干扰,不需要额外配备读、写辅助电路,具有较高读、写稳定性。

附图说明

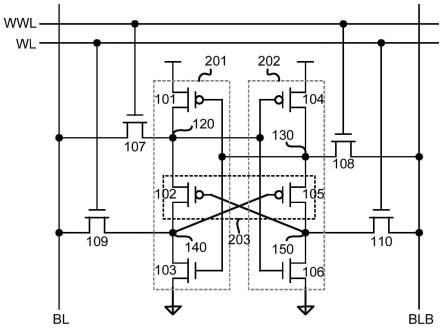

8.图1为本发明的内嵌交叉结构的亚阈值p-p-n型10管存储单元的电路结构示意图。

9.图2为本发明的内嵌交叉结构的亚阈值p-p-n型10管存储单元进行写操作的电路操作示意图;

10.图3为本发明的内嵌交叉结构的亚阈值p-p-n型10管存储单元进行读操作的电路操作示意图。

具体实施方式

11.以下结合附图实施例对本发明作进一步详细描述。

12.实施例:如图1所示,一种内嵌交叉结构的亚阈值p-p-n型10管存储单元,包括一对内嵌交叉结构的交叉耦合p-p-n型反相器、两组nmos传输管、四个存储结点、字线wl、写字线wwl和一对位线,将一对内嵌交叉结构的交叉耦合p-p-n型反相器分别称为第一p-p-n型反相器201和第二p-p-n型反相器202,将两组nmos传输管分别称为第一组nmos传输管和第二组nmos传输管,将四个存储结点分别称为第一存储结点120、第二存储结点130、第三存储结点140和第五存储结点150,将一对位线分别称为位线bl和位线blb;第一p-p-n型反相器201

包括第一pmos管101、第二pmos管102和第一nmos管103,第一pmos管101的源极接入电源,第一pmos管101的栅极、第一nmos管103的栅极连接且其连接端为第一p-p-n型反相器201的输出端,第一p-p-n型反相器201的输出端和第二存储结点130连接,第一pmos管101的漏极、第二pmos管102的源极均与第一存储结点120连接,第二pmos管102的漏极和第一nmos管103的漏极均与第三存储结点140连接,第一nmos管103的源极接地,第二pmos管102的栅极和第五存储结点150连接;第二p-p-n型反相器202包括第三pmos管104、第四pmos管105和第二nmos管106,第三pmos管104的源极接入电源,第三pmos管104的栅极、第二nmos管106的栅极连接且其连接端为第二p-p-n型反相器202的输入端,第二p-p-n型反相器202的输入端和第一存储结点120连接,第三pmos管104的漏极、第四pmos管105的源极均与第二存储结点130连接,第四pmos管105的漏极和第二nmos管106的漏极均与第五存储结点150连接,第二nmos管106的源极接地,第四pmos管105的栅极和第三存储结点140连接;第二pmos管102和第四pmos管105相互交叉耦合,构成内嵌的交叉结构203,第一p-p-n型反相器201和第二p-p-n型反相器202相互交耦合,构成存储单元的存储核心;第一组nmos传输管包括第三nmos管107和第四nmos管109,第三nmos管107的栅极和写字线wwl连接,第三nmos管107的源极和位线bl连接,第三nmos管107的漏极和第一存储结点120连接,第四nmos管109的栅极和字线wl连接,第四nmos管109的源极和位线bl连接,第四nmos管109的漏极和第三存储结点140连接,第二组nmos传输管包括第五nmos管108和第六nmos管110,第五nmos管108的栅极和写字线wwl连接,第五nmos管108的源极和位线blb连接,第五nmos管108的漏极和第二存储结点130连接,第六nmos管110的栅极和字线wl连接,第六nmos管110的源极和位线blb连接,第六nmos管110的漏极和第五存储结点150连接。

13.本发明的内嵌交叉结构的亚阈值p-p-n型10管存储单元进行写操作的电路操作示意图如图2所示,此时,写字线wwl和字线wl都开启(被置为“1”),第三nmos管107、第五nmos管108、第四nmos管109和第六nmos管110都处于打开状态。当执行写“0”操作时,位线bl为“0”,而位线blb为“1”,第一存储结点120和第三存储结点140被下拉至“0”,然后通过第一p-p-n型反相器201和第二p-p-n型反相器202构成的正反馈环将第三存储结点130和第四存储结点150预充至“1”。当执行写“1”操作时,位线bl为“1”,而位线blb为“0”,第二存储结点130和第四存储结点150被下拉至“0”,然后通过第一p-p-n型反相器201和第二p-p-n型反相器202构成的正反馈环将第一存储结点120和第三存储结点140预充至“1”。本发明的存储单元的写“0”与写“1”操作完全是镜像对称的,这种双差分的写操作方式大大提高了存储单元的写噪声容限。

14.本发明的内嵌交叉结构的亚阈值p-p-n型10管存储单元进行读操作的电路操作示意图如图3所示。此时,字线wl开启,而写字线wwl关断,第四nmos管109和第六nmos管110处于打开状态,位线bl和位线blb被预充至“1”,并浮空。当存储单元执行读“0”操作时,位线blb保持原来的“1”电平,而位线bl通过第五nmos管109和第一nmos管103下拉至一个低电平,导致位线bl和位线blb形成电压差。当存储单元执行读“1”操作时,位线bl保持原来的“1”电平,而位线blb通过第六nmos管110和第二nmos管106下拉至一个低电平,在位线bl和位线blb上形成电压差。由于整个读操作过程中,读电流路径是与第一存储结点120和第二存储结点130隔离的,所以电路不会发生读破坏情况。也就是说,该电路消除了读破坏,具有较高的读噪声容限。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1