内容寻址存储器单元结构的版图的制作方法

1.本发明涉及半导体技术领域,特别是涉及一种内容寻址存储器单元结构的版图。

背景技术:

2.cam是一种特殊的存储器。所谓cam,即内容寻址存储器。cam存储器在其每个存储单元都包含了一个内嵌的比较逻辑,写入cam的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所有内部数据的地址。概括地讲,ram(随机存取存储器)是一个根据地址读、写数据的存储单元,而cam和ram恰恰相反,它返回的是与端口数据内容相匹配的地址。cam的应用也比较广泛,比如在路由器中的地址交换表,cpu的cache控制器(tag阵列)等。

3.cam单元是通过在标准的sram(静态随机存取存储器)单元结构中增加执行匹配功能的晶体管而构成的。把同一个字所包含的多个cam单元连接到同一条匹配线上,将匹配线预充电或者上拉为高电平,作为一个分布的伪nmos门,关键字放置在位线上。

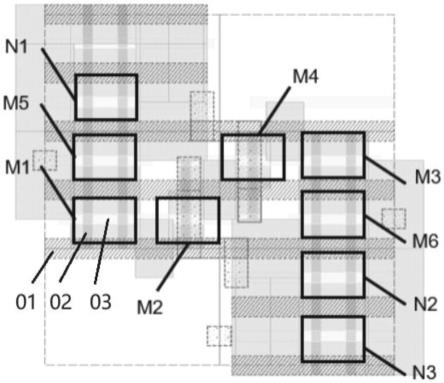

4.现有技术中的一种9晶体管的内容寻址存储器的结构示意图如图1所示,其中第一下拉管图形m1和第二下拉管图形m3为n型下拉管,第一上升管图形m2和第二上升管图形m4为p型上升管,第四传输管图形m5、第五传输管图形m6、第一传输管图形n1、第二传输管图形n2和第三传输管图形n3为n型传输管,通过第一传输管图形n1和第二传输管图形n2,把关键字和单元数据进行异或。如果关键字和单元数据不相同,那么第三传输管图形n3就导通,将匹配线的电平下拉为低电平,但第三传输管图形n3的栅极式一个降低的高逻辑电平,具体工作原理和真值表见图2和图3。

5.现有技术中的内容寻址存储器功耗较高,需要一种新型的版图结构,用以降低其功耗。

技术实现要素:

6.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种内容寻址存储器单元结构的版图,用于解决现有技术中的内容寻址存储器功耗较高,需要一种新型的版图结构,用以降低其功耗的问题。

7.为实现上述目的及其他相关目的,本发明提供一种内容寻址存储器单元结构的版图,包括:

8.传输管图形,所述传输管图形包括第一传输管图形、第四传输管图形、第五传输管图形、第二传输管图形、第三传输管图形;

9.下拉管图形,所述下拉管图形包括第一下拉管图形和第二下拉管图形;

10.上升管图形,所述上升管图形包括第一上升管图形和第二上升管图形;

11.其中,第一传输管图形、第二传输管图形、第三传输管图形为相对于现有技术晶体管内容寻址存储器单元结构新增的三个传输管,通过第一传输管图形和第二传输管图形,把关键字和单元数据进行异或。如果关键字和单元数据不相同,那么第三传输管图形就导

通,将匹配线的电平下拉为低电平。

12.所述传输管图形、所述下拉管图形和所述上升管图形中分别包括:有源区图形和横跨在所述有源区图形上的多晶硅图形;位于所述有源区图形上且分布在所述多晶硅图形一侧的接触孔图形;

13.所述第一传输管图形、第四传输管图形和第一下拉管图形自上而下依次分布,且所述第一传输管图形、第四传输管图形、第一下拉管图形的所述有源区图形连在一起;所述第二下拉管图形、第五传输管图形、第二传输管图形和第三传输管图形自上而下依次分布,且所述第二下拉管图形、第五传输管图形、第二传输管图形、第三传输管图形的所述有源区图形连在一起;所述第一上升管图形和第二上升管图形分别设在所述第一下拉管图形、第一上升管图形的一侧,即第一上升管图形位于第一下拉管图形的右侧,第二上升管图形位于第二下拉管图形的左侧,使得所述传输管图形、所述下拉管图形和所述上升管图形为非对称分布。

14.优选地,所述第四传输管图形、第五传输管图形、第一传输管图形、第二传输管图形、第三传输管图形均为n型传输管图形。

15.优选地,所述第一上升管图形和第二上升管图形均为p型上升管图形。

16.优选地,所述第一下拉管图形和第二下拉管图形均为n型下拉管图形。

17.优选地,所述版图还包括金属层图形,所述金属层图形用于连接所述传输管图形、所述下拉管图形和所述上升管图形。

18.优选地,所述金属层图形包括:用于连接第四传输管图形和第一传输管图形的第一位线图形;用于连接第五传输管图形和第二传输管图形的第二位线图形;用于连接第四传输管图形和第五传输管图形且与第一、二位线图形连接的字线图形;用于连接第三传输管图形且与第一、二位线连接的匹配线图形。

19.优选地,所述第一下拉管图形、第一上升管图形、第二下拉管图形、第二上升管图形、第五传输管图形、第四传输管图形、第一传输管图形、第二传输管图形为对称分布。

20.优选地,所述传输管图形、所述下拉管图形和所述上升管图形中的所述有源区图形为sra结构中的有源区图形。

21.优选地,所述版图结构基于14纳米技术节点的低功耗工艺的内容寻址存储器单元。

22.如上所述,本发明的内容寻址存储器单元结构的版图,具有以下有益效果:

23.本发明设计了一种基于鳍式工艺平台绘制寻址存储单元器件版图结构。像一个普通的静态随机存储器一样,在给定地址和数据时可以读出或者写入,但它同时执行匹配操作,可以用于越来越普及的人工智能应用;通过本发明的版图制作的内容寻址存储器单元结构,可作为为微处理器中支持虚拟存储器的翻译后援缓冲器;本发明的版图运用了非对称版图结构,制造出的内容寻址存储器整体功耗更低。

附图说明

24.图1显示为现有技术中一种9晶体管内容寻址存储器电路图示意图;

25.图2显示为现有技术中一种内容寻址存储器的原理示意图;

26.图3显示为现有技术中一种内容寻址存储器的真值表示意图;

27.图4显示为本发明的内容寻址存储器的版图示意图。

具体实施方式

28.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

29.请参阅图4,本发明提供一种内容寻址存储器单元结构的版图,包括:

30.传输管图形,传输管图形包括第一传输管图形n1、第四传输管图形m5、第五传输管图形m6、第二传输管图形n2、第三传输管图形n3;

31.下拉管图形,下拉管图形包括第一下拉管图形m1和第二下拉管图形m3;

32.上升管图形,上升管图形包括第一上升管图形m2和第二上升管图形m4;

33.其中第一传输管图形n1、第二传输管图形n2、第三传输管图形n3为相对6晶体管内容寻址存储器单元结构增加的三个传输管图形,通过第一传输管图形n1和第二传输管图形n2,把关键字和单元数据进行异或。如果关键字和单元数据不相同,那么第三传输管图形n3就导通,将匹配线的电平下拉为低电平,但第三传输管图形n3的栅极式一个降低的高逻辑电平,具体工作原理和真值表见图2和图3。

34.在一种可选的实施方式中,传输管图形、下拉管图形和上升管图形中的有源区图形02为sram结构中的有源区图形02。

35.在一种可选的实施方式中,第四传输管图形m5、第五传输管图形m6、第一传输管图形n1、第二传输管图形n2、第三传输管图形n3均为n型传输管图形。

36.在一种可选的实施方式中,第一上升管图形m2和第二上升管图形m4均为p型上升管图形。

37.在一种可选的实施方式中,第一下拉管图形m1和第二下拉管图形m3均为n型下拉管图形。

38.传输管图形、下拉管图形和上升管图形中分别包括:有源区图形02和横跨在有源区图形02上的多晶硅图形03;位于有源区图形02上且分布在多晶硅图形03一侧的接触孔图形;

39.第一传输管图形n1、第四传输管图形m5和第一下拉管图形m1依次分布,且第一传输管图形n1、第四传输管图形m5、第一下拉管图形m1的有源区图形02连在一起;第二下拉管图形m3、第五传输管图形m6、第二传输管图形n2和第三传输管图形n3依次分布,且第二下拉管图形m3、第五传输管图形m6、第二传输管图形n2、第三传输管图形n3的有源区图形02连在一起;第一上升管图形m2和第二上升管图形m4分别设在第一下拉管图形m1、第一上升管图形m2的一侧,使得传输管图形、下拉管图形和上升管图形,即第一传输管图形n1、第四传输管图形m5、第五传输管图形m6、第二传输管图形n2、第三传输管图形n3、第一下拉管图形m1、第二下拉管图形m3、第一上升管图形m2和第二上升管图形m4这九个晶体管图形为非对称分布。

40.在一种可选的实施方式中,第一下拉管图形m1、第一上升管图形m2、第二下拉管图形m3、第二上升管图形m4、第四传输管图形m5、第五传输管图形m6、第一传输管图形n1、第二

传输管图形n2为对称分布。

41.在一种可选的实施方式中,传输管图形、下拉管图形和上升管图形的位置分布,可参照现有技术中的6晶体管内容寻址存储器单元结构的版图,绘制出第四传输管图形m5、第一下拉管图形m1和第一上升管图形m2,之后镜像出中心对称的第二上升管图形m4、第二下拉管图形m3和第五传输管图形m6,之后绘制出第一传输管图形n1、第二传输管图形n2和第三传输管图形n3。

42.在一种可选的实施方式中,版图还包括金属层图形01,金属层图形01用于连接传输管图形、下拉管图形和上升管图形。

43.在一种可选的实施方式中,访问sram时,字线(word line)加高电平,使得每个基本单元的两个控制开关用的晶体管开通,把基本单元与位线(bit line)连通,金属层图形01包括:用于连接第四传输管图形m5和第一传输管图形n1的第一位线图形;用于连接第五传输管图形m6和第二传输管图形n2的第二位线图形;用于连接第四传输管图形m5和第五传输管图形m6且与第一、二位线图形连接的字线图形;用于连接第三传输管图形n3且与第一、二位线连接的匹配线图形。

44.在一种可选的实施方式中,所述版图结构基于14纳米技术节点的低功耗工艺的内容寻址存储器单元。

45.也就是说,在本实施例的9晶体管内容寻址存储器中,基于鳍式工艺的静态随机存储器单元基础上,完成内容寻址存储器件的版图实现,绘制了完整的sram器件版图最小阵列。利用现有的6晶体管的sram单元结构基础上,增加三个传输管绘制成9晶体管的内容寻址存储器件单元(如图1)。第一下拉管图形m1、第一上升管图形m2、第二下拉管图形m3、第二上升管图形m4、第四传输管图形m5、第四传输管图形m6、第一传输管图形n1、第二传输管图形n2为对称分布,传输管图形、下拉管图形和上升管图形中第一传输管图形n1、第四传输管图形m5、第五传输管图形m6、第二传输管图形n2、第三传输管图形n3、第一下拉管图形m1、第二下拉管图形m3、第一上升管图形m2和第二上升管图形m4这九个晶体管图形为非对称分布,其版图面积为普通6晶体管sram单元面积两倍左右,但在保持原先读写功能的基础上,增加了匹配操作。利用匹配操作可以找出cam中含有给定关键字的每一个字,然后通过选中的匹配线输出。后期也可以再绘制10晶体管内容寻址存储器件版图。

46.需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

47.综上所述,本发明设计了一种基于鳍式工艺平台绘制寻址存储单元器件版图结构。像一个普通的静态随机存储器一样,在给定地址和数据时可以读出或者写入,但它同时执行匹配操作,可以用于越来越普及的人工智能应用;通过本发明的版图制作的内容寻址存储器单元结构,可作为为微处理器中支持虚拟存储器的翻译后援缓冲器;本发明的版图运用了非对称版图结构,制造出的内容寻址存储器整体功耗更低。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

48.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因

此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1