一种半导体结构及其制造方法、子字线驱动器、存储器与流程

本公开涉及半导体制造领域,尤其涉及一种半导体结构及其制造方法、子字线驱动器、存储器。

背景技术:

1、半导体结构,例如子字线驱动器,通常由数目巨多的重复单元组成,其最小单元包括一个pmos与一个nmos,或者一个pmos与一对nmos。

2、然而,随着半导体结构不断朝着小型化、高集成度的方向发展,pmos失配现象越来越严重,进而降低半导体结构的性能。

技术实现思路

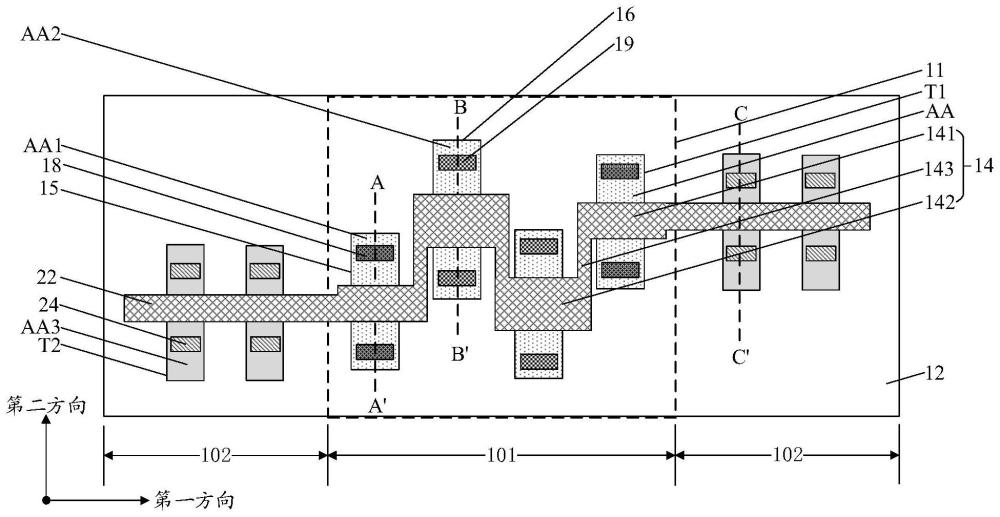

1、本公开实施例提供一种半导体结构,包括:

2、衬底;

3、位于所述衬底上的第一导电类型晶体管区,所述第一导电类型晶体管区包括多个第一导电类型晶体管;

4、将排布在外围的所述第一导电类型晶体管定义为第一晶体管,排布在中间区域的所述第一导电类型晶体管定义为第二晶体管,所述第一晶体管包括第一沟道区,所述第二晶体管包括第二沟道区;其中,所述第一沟道区的长度小于所述第二沟道区的长度。

5、在一些实施例中,所述第一沟道区的长度与所述第二沟道区的长度的比值的范围是0.6至0.9之间。

6、在一些实施例中,所述多个第一导电类型晶体管在所述衬底上沿第一方向排布,所述第一方向平行于所述衬底的上表面,排布在两端的所述第一导电类型晶体管定义为第一晶体管,位于所述第一晶体管之间的所述第一导电类型晶体管定义为第二晶体管;

7、所述第一晶体管与所述第二晶体管均还包括第一极和第二极,所述第一晶体管的第一极、第一沟道区及第二极在第二方向上依次排布;所述第二晶体管的第一极、第二沟道区及第二极在所述第二方向上依次排布,其中,所述第二方向平行于所述衬底的上表面且与所述第一方向垂直。

8、在一些实施例中,所述衬底包括第一有源区和第二有源区,所述第一晶体管形成于所述第一有源区上,所述第二晶体管形成于所述第二有源区上,所述第一有源区在所述第一方向上的尺寸等于所述第二有源区在所述第一方向上的尺寸,所述第一有源区在所述第二方向上的尺寸小于所述第二有源区在所述第二方向上的尺寸。

9、在一些实施例中,所述半导体结构还包括:栅线,所述栅线包括至少一个第一栅极部、至少一个第二栅极部和至少一个连接部,所述第一栅极部覆盖所述第一沟道区,所述第二栅极部覆盖所述第二沟道区,所述连接部用于电连接相邻的栅极部;其中,所述第一栅极部沿所述第二方向的延伸长度小于所述第二栅极部沿所述第二方向的延伸长度。

10、在一些实施例中,沿所述第一方向相邻的两个栅极部的中心在所述第二方向上存在偏移。

11、在一些实施例中,所述半导体结构还包括:多个第一接触插塞,多个所述第一接触插塞位于所述第一栅极部的两侧且分别与所述第一晶体管的第一极、第二极电连接;多个第二接触插塞,多个所述第二接触插塞位于所述第二栅极部的两侧且分别与所述第二晶体管的第一极、第二极电连接;其中,所述第一接触插塞与所述第一栅极部的距离和所述第二接触插塞与所述第二栅极部的距离相等。

12、在一些实施例中,所述半导体结构还包括:第二导电类型晶体管区,包括多个第二导电类型晶体管,设置于所述第一导电类型晶体管区的至少一侧。

13、在一些实施例中,所述第一导电类型晶体管为p型晶体管,所述第二导电类型晶体管为n型晶体管。

14、本公开实施例还提供了一种子字线驱动器,所述子字线驱动器包括如上所述的任一半导体结构。

15、本公开实施例还提供了一种存储器,所述存储器包括如上所述的子字线驱动器。

16、本公开实施例还提供了一种半导体结构的制造方法,包括:

17、提供衬底;

18、在所述衬底上形成第一导电类型晶体管区,所述第一导电类型晶体管区包括多个第一导电类型晶体管,将排布在外围的所述第一导电类型晶体管定义为第一晶体管,排布在中间区域的所述第一导电类型晶体管定义为第二晶体管,所述第一晶体管包括第一沟道区,所述第二晶体管包括第二沟道区;其中,所述第一沟道区的长度小于所述第二沟道区的长度。

19、在一些实施例中,在所述衬底上形成第一导电类型晶体管区,包括:

20、采用离子注入工艺对所述衬底进行掺杂以形成阱区;

21、在所述阱区内形成隔离结构,所述隔离结构将所述阱区间隔为多个沿第一方向排布的有源区,排布在两端的所述有源区定义为第一有源区,位于所述第一有源区之间的所述有源区定义为第二有源区,每一所述有源区的长度方向延第二方向延伸,所述第一有源区在所述第一方向上的尺寸等于所述第二有源区在所述第一方向上的尺寸,所述第一有源区在所述第二方向上的尺寸小于所述第二有源区在所述第二方向上的尺寸,其中,所述第一方向与所述第二方向均与所述衬底的上表面平行,且相互垂直。

22、在一些实施例中,在所述阱区内形成隔离结构之后,还包括:

23、形成栅介质材料层,所述栅介质材料层覆盖所述第一有源区、所述第二有源区及所述隔离结构;

24、形成导电材料层,所述导电材料层覆盖所述栅介质材料层;

25、刻蚀所述导电材料层、所述栅介质材料层以分别形成栅线、栅介质层,所述栅线覆盖所述栅介质层,且所述栅线包括至少一个第一栅极部、至少一个第二栅极部和至少一个连接部,所述第一栅极部覆盖部分所述第一有源区,所述第一有源区被所述第一栅极部覆盖的区域构成所述第一沟道区,所述第二栅极部覆盖部分所述第二有源区,所述第二有源区被所述第二栅极部覆盖的区域构成所述第二沟道区,所述连接部用于电连接相邻的栅极部;其中,所述第一栅极部沿所述第二方向的延伸长度小于所述第二栅极部沿所述第二方向的延伸长度。

26、在一些实施例中,在刻蚀所述导电材料层、所述栅介质材料层以分别形成栅线、栅介质层之后,还包括:

27、对所述第一有源区和所述第二有源区执行离子注入工艺,以在所述第一沟道区的两侧分别形成第一极和第二极,在所述第二沟道区的两侧分别形成第一极和第二极;所述第一有源区的第一极、第一沟道区及第二极在所述第二方向上依次排布,所述第二有源区的第一极、第二沟道区及第二极在所述第二方向上依次排布。

28、在一些实施例中,还包括:

29、形成介质层,所述介质层覆盖所述第一晶体管、所述第二晶体管、所述隔离结构及所述栅线;

30、形成贯穿所述介质层的多个第一接触插塞和多个第二接触插塞,多个所述第一接触插塞的底部分别与所述第一晶体管的第一极、第二极电连接,多个所述第二接触插塞的底部分别与所述第二晶体管的第一极、第二极电连接;其中,所述第一接触插塞与所述第一栅极部的距离和所述第二接触插塞与所述第二栅极部的距离相等。

31、在一些实施例中,还包括:在所述衬底上形成第二导电类型晶体管区,所述第二导电类型晶体管区包括多个第二导电类型晶体管,所述多个第二导电类型晶体管设置于所述第一导电类型晶体管区的至少一侧。

32、本公开实施例提供的半导体结构及其制造方法、子字线驱动器、存储器,其中,所述半导体结构包括:衬底;位于所述衬底上的第一导电类型晶体管区,所述第一导电类型晶体管区包括多个第一导电类型晶体管;将排布在外围的所述第一导电类型晶体管定义为第一晶体管,排布在中间区域的所述第一导电类型晶体管定义为第二晶体管,所述第一晶体管包括第一沟道区,所述第二晶体管包括第二沟道区;其中,所述第一沟道区的长度小于所述第二沟道区的长度。本公开实施例提供的第一导电类型晶体管区包括排布在外围的第一晶体管和排布在中间区域的第二晶体管,第一晶体管的第一沟道区的长度小于第二晶体管的第二沟道区的长度,如此,相比第一沟道区的长度和第二沟道区的长度相同的情况,可以减小排布在外围的第一晶体管的阈值电压,在实际工艺中,可以减小或消除第一晶体管的阈值电压和第二晶体管的阈值电压的差值,从而缓解或避免第一晶体管和第二晶体管失配,进而提高半导体结构的性能。

33、本公开的一个或多个实施例的细节在下面的附图和描述中提出。本公开的其它特征和优点将从说明书附图以及权利要求书变得明显。

- 还没有人留言评论。精彩留言会获得点赞!