运用于反熔丝型一次编程存储单元阵列的编程控制电路的制作方法

本发明是有关于一种存储器的控制电路,且特别是有关于一种运用于反熔丝型一次编程存储单元阵列的编程控制电路。

背景技术:

1、众所周知,非易失性存储器可区分为:多次编程的存储器(multi-timeprogramming memory,简称mtp存储器)、一次编程的存储器(one time programmingmemory,简称otp存储器)或者掩模式只读存储器(mask rom存储器)。基本上,用户可以对mtp存储器进行多次的编程,用以多次修改储存数据。而用户仅可以编程一次otp存储器,一旦otp存储器编程完成之后,其储存数据将无法修改。而mask rom存储器于出厂之后,所有的储存数据已经记录在其中,用户仅能够读取mask rom存储器中的储存数据,而无法进行编程。

2、举例来说,反熔丝型(antifuse-type)otp存储器的存储单元在尚未进行编程动作(program action)前,其为高电阻值的储存状态。反熔丝型otp存储器的存储单元进行编程动作之后,其为低电阻值的储存状态。一旦反熔丝型otp存储单元进行编程动作后,其储存数据将无法修改。

3、请参照图1a与图1b,其所绘示为公知二种反熔丝型otp存储单元。以下将反熔丝型otp存储单元简称为otp存储单元。

4、如图1a所示,otp存储单元100为三端点元件,第一端x连接至位线bl,第二端y连接至字线wl,第三端z连接至反熔丝型控制线(antifuse control line)af。otp存储单元100包括选择晶体管(select transistor)ms与反熔丝型晶体管(antifuse transistor)maf。选择晶体管ms的第一汲/源端(drain/source terminal)连接至位线bl,选择晶体管ms的栅极端连接至字线wl,选择晶体管ms的第二汲/源端连接至反熔丝型晶体管maf的第一汲/源端,反熔丝型晶体管maf的栅极端连接至反熔丝型控制线af,反熔丝型晶体管maf的第二汲/源端为浮接(floating)。由于反熔丝型晶体管maf的第二汲/源端为浮接,所以反熔丝型晶体管maf可视为一电容器(capacitor)。也就是说,otp存储单元100为一晶体管与一电容器存储单元(1t1c cell)。

5、如图1b所示,otp存储单元102为四端点元件,第一端x连接至位线bl,第二端y连接至字线wl,第三端z连接至反熔丝型控制线af,第四端w连接至跟随线(following line)fl。otp存储单元102包括选择晶体管ms、跟随晶体管(following transistor)mfl与反熔丝型晶体管maf。选择晶体管ms的第一汲/源端连接至位线bl,选择晶体管ms的栅极端连接至字线wl,选择晶体管ms的第二汲/源端连接至跟随晶体管mfl的第一汲/源端,跟随晶体管mfl的栅极端连接至跟随线fl,跟随晶体管mfl的第二汲/源端连接至反熔丝型晶体管maf的第一汲/源端,反熔丝型晶体管maf的栅极端连接至反熔丝型控制线af,反熔丝型晶体管maf的第二汲/源端为浮接。因此,otp存储单元102为二晶体管与一电容器存储单元(2t1c cell)。

6、当然,otp存储单元并不限定于上述的二种结构,也可以利用反熔丝型晶体管maf搭配更多晶体管形成otp存储单元。

7、以下以图1a所示的otp存储单元100为例,对otp存储单元100进行编程动作与编程抑制动作。请参照图2a与图2b,其为将otp存储单元进行编程动作与编程抑制动作的偏压示意图。

8、如图2a所示,在编程动作时,反熔丝型控制线af接收编程脉冲(program pulse),位线bl接收接地电压(0v),字线wl接收开启电压von并使得字线wl动作。其中,编程脉冲的脉冲高度(pulse height)为编程电压vpp,编程脉冲的脉冲宽度(pulse width)为t。

9、于编程动作时,otp存储单元100的选择晶体管ms开启(turn on),位线bl的接地电压(0v)传递至反熔丝型晶体管maf的第一汲/源端。当反熔丝型控制线af接收编程脉冲时,反熔丝型晶体管maf的栅极端与第一汲/源端之间承受的电压应力(voltage stress)为编程电压vpp,造成反熔丝型晶体管maf的栅极氧化层(gate oxide layer)破裂(rupture)并产生一编程电流(program current)ip,使得反熔丝型晶体管maf的栅极端与第一汲/源端之间呈现低电阻值。亦即,otp存储单元100被编程为低电阻值的储存状态。

10、如图2b所示,在编程抑制动作时,反熔丝型控制线af接收编程脉冲(programpulse),位线bl接收接地电压(0v),字线wl接收关闭电压voff并使得字线wl不动作。

11、在编程抑制动作时,otp存储单元100的选择晶体管ms关闭(turn off),位线bl的接地电压(0v)无法传递至反熔丝型晶体管maf的第一汲/源端。当反熔丝型控制线af接收编程脉冲时,反熔丝型晶体管maf的栅极端与第一汲/源端之间承受的电压应力很小,反熔丝型晶体管maf的栅极氧化层(gate oxide layer)未破裂(rupture),反熔丝型晶体管maf的栅极端与第一汲/源端之间仍维持在高电阻值。亦即,otp存储单元100维持在高电阻值的状态。

12、另外,在编程抑制动作时,由于反熔丝型控制线af接收编程脉冲且位线bl接收接地电压(0v)。虽然字线wl未动作,编程电压vpp仍会造成选择晶体管ms产生漏电流il,例如栅极诱导漏极漏电流(gate induced drain leakage current),又称为gidl电流。

13、请参照图3,其所绘示为otp存储单元阵列进行编程动作的示意图。以下将otp存储单元阵列简称为存储单元阵列。存储单元阵列由由mxn个otp存储单元组成,m与n为正整数。举例来说,图3的存储单元阵列包括3x3个otp存储单元c11~c33所组成,每一个otp存储单元c11~c33的结构相同于图1a。当然,存储单元阵列也可以由第1b图的otp存储单元或者其他结构的otp存储单元所组成。

14、在存储单元阵列的第一行中,otp存储单元c11~c13的第一端连接至对应的位线bl1~bl3,otp存储单元c11~c13的第二端连接至字线wl1,otp存储单元c11~c13的第三端连接至反熔丝型控制线af。在第二行中,otp存储单元c21~c23的第一端连接至对应的位线bl1~bl3,otp存储单元c21~c23的第二端连接至字线wl2,otp存储单元c21~c23的第三端连接至反熔丝型控制线af。在第三行中,otp存储单元c31~c33的第一端连接至对应的位线bl1~bl3,otp存储单元c31~c33的第二端连接至字线wl3,otp存储单元c31~c33的第三端连接至反熔丝型控制线af。

15、对存储单元阵列中的任一otp存储单元进行编程动作时,反熔丝型控制线af接收编程脉冲,对应的字线动作(activated),其他的字线不动作,对应的位线连接至接地电压(0v),其他位线连接为浮接(floating)。举例来说,对存储单元阵列内的otp存储单元c11进行编程动作时,反熔丝型控制线af接收编程脉冲,字线wl1接收开启电压von并使得字线wl1动作(activated),其他字线wl2、wl3接收关闭电压voff而不动作,位线bl1接收接地电压(0v),其他位线bl2、bl3则浮接(floating)。其中,编程脉冲的脉冲高度(pulse height)为编程电压vpp,编程脉冲的脉冲宽度(pulse width)为t。举例来说,脉冲宽度为10μs,编程电压vpp为6.5v,开启电压von为3v,关闭电压voff为0v。当然,上述的偏压以及脉冲宽度t可随实际情况而适当地修改,例如将位线bl2、bl3连接至接地电压(0v)。

16、如图3所示,由于位线bl2、bl3为浮接,因此不论字线wl1~wl3动作与否,存储单元阵列中第二列(column)的otp存储单元c12、c22、c32以及第三列的otp存储单元c13、c23、c33皆不会改变储存状态。

17、另外,在存储单元阵列的第一列(column)中,反熔丝型控制线af接收编程脉冲,位线bl1接收接地电压(0v),字线wl1接收开启电压von,其他字线wl2、wl3接收关闭电压voff。因此,otp存储单元c11为选定存储单元(selected cell),otp存储单元c21、c31为非选定存储单元(unselected cell)。

18、在otp存储单元c11中,选择晶体管ms1开启(turn on),反熔丝型晶体管maf1的栅极氧化层(gate oxide layer)破裂(rupture)并产生一编程电流(program current,ip),使得otp存储单元c11被编程为低电阻值的储存状态。

19、在otp存储单元c21中,选择晶体管ms2关闭(turn off),反熔丝型晶体管maf2的栅极氧化层(gate oxide layer)未破裂(rupture),otp存储单元c21维持在高电阻值的储存状态。同理,otp存储单元c31也会维持在高电阻值的储存状态。

20、再者,由于反熔丝型控制线af接收编程脉冲且位线bl1接收接地电压(0v)。虽然字线wl2、wl3未动作,otp存储单元c21会产生漏电流(leakage current)il2,且otp存储单元c31会产生漏电流il3。也就是说,反熔丝型控制线af上的总电流iaf为(ip+il1+il2),亦即iaf=ip+il1+il2。

21、由以上的说明可知,对otp存储单元进行编程动作时,会提供编程脉冲。其中,编程脉冲的脉冲高度为编程电压vpp,编程脉冲的脉冲宽度为t。然而,由于半导体的制造工艺变异,无法准确的得知反熔丝型晶体管maf1的栅极氧化层(gate oxide layer)何时会破裂(rupture)。

22、有些时候,于编程脉冲提供至编程控制线af的初期,反熔丝型晶体管maf1的栅极氧化层就会破裂了,此时将造成otp存储单元c11被过度编程(over programmed),使得otp存储单元c11劣化。而有些时候,经过脉冲宽度t的时间之后,反熔丝型晶体管maf1的栅极氧化层仍未破裂,此时需要提高编程脉冲的脉冲高度或者脉冲宽度,并再进行一次编程动作。

技术实现思路

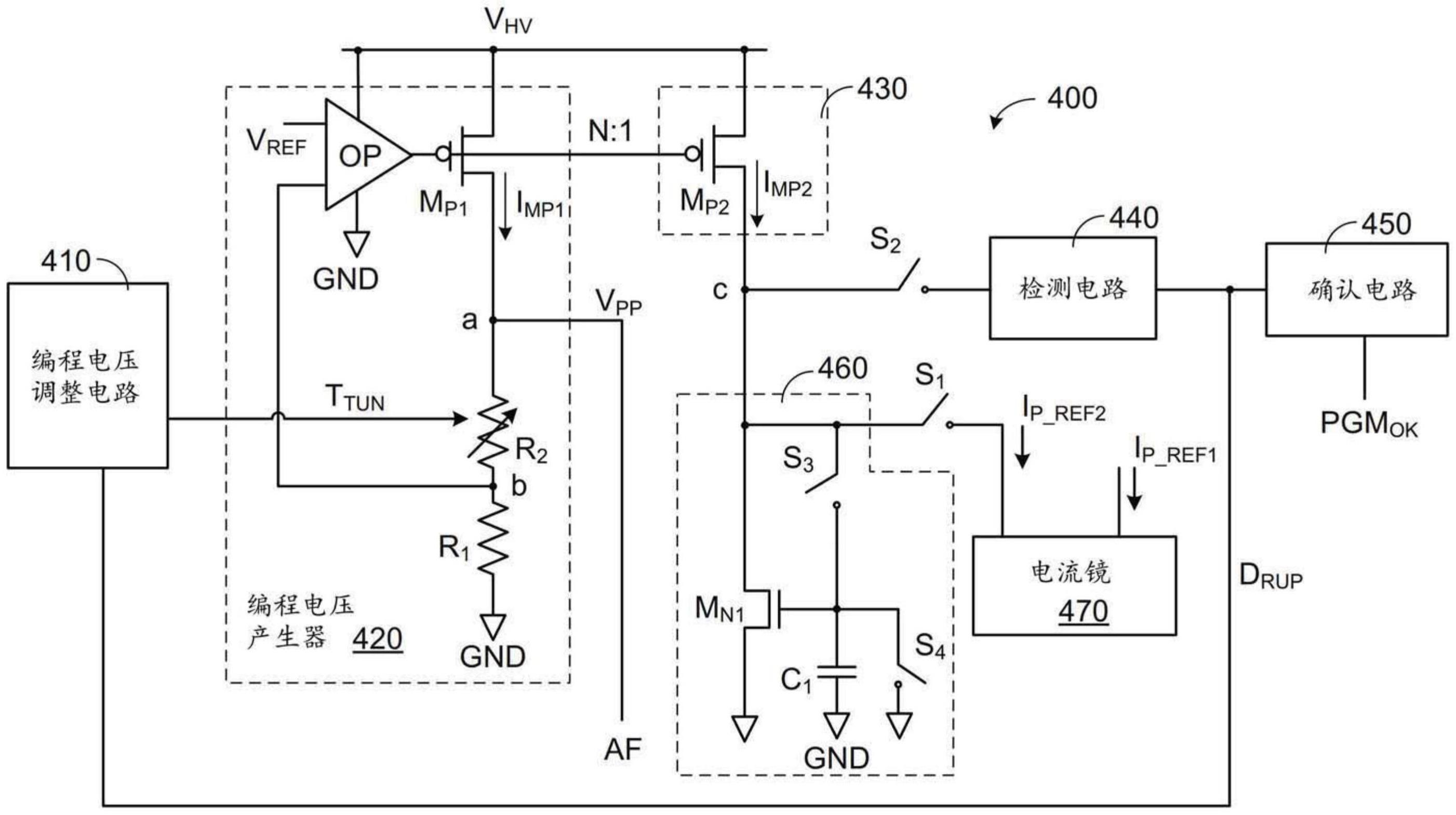

1、本发明有关于一种编程控制电路,耦接(couple to)至反熔丝型一次编程存储单元阵列中反熔丝控制线,该编程控制电路产生编程电压用以编程该反熔丝型一次编程存储单元阵列中的选定存储单元,该编程控制电路包括:编程电压产生器,该编程电压产生器的一输出端耦接至该反熔丝控制线;其中,于编程动作的校正相位,该编程电压产生器产生校正电压至该反熔丝控制线;以及,于该编程动作的至少编程相位,该编程电压产生器产生该编程电压至该反熔丝控制线;编程电压调整电路,连接至该编程电压产生器,其中该编程电压调整电路接收破裂信号,并于该破裂信号的未动作时,选择性地调整该编程电压;比例电流产生器,连接至该编程电压产生器;其中,在该校正相位,该比例电流产生器产生一校正电流至第一节点;于该至少编程相位,该比例电流产生器产生运作电流至该第一节点;电流取样电路,连接至该第一节点;其中,于该校正相位,该电流取样电路将该校正电流转换为一取样电压;在该至少编程相位,该电流取样电路根据该取样电压产生该校正电流由该第一节点流向接地端;第一开关,该第一开关的第一端连接至该第一节点;第二开关,该第二开关的第一端连接至该第一节点;其中,于该校正相位,该第一开关与该第二开关打开;于该至少编程相位,该第一开关与该第二开关闭合;电流镜,该电流镜的电流输入端接收一第一编程参考电流,该电流镜的电流镜射端产生第二编程参考电流,且该电流镜射端连接至该第一开关的第二端;其中,于该至少一编程相位,该第二编程参考电流由该第一节点流向该电流镜的该电流镜射端;以及,一检测电路,连接至该第二开关的第二端;其中,在该至少一编程相位,该检测电路根据判断该选定存储单元产生的一编程电流的大小,当该检测电路确认该编程电流的大小已足够时,该检测电路动作该破裂信号。

2、为了对本发明之上述及其他方面有更佳的了解,下文特举较佳实施例,并配合所附图式,作详细说明如下:

- 还没有人留言评论。精彩留言会获得点赞!