一种10T-SRAM单元及其数据读写方法、电路结构

一种10t-sram单元及其数据读写方法、电路结构

1.本技术是申请号为cn202210638677.2,申请日为2020/06/08,且发明名称为一种基于10t-sram单元的电路结构、芯片及模块的分案申请。

技术领域

2.本发明涉及静态随机存储器技术领域,特别是涉及一种10t-sram单元及其数据读写方法、电路结构。

背景技术:

3.作为突破冯诺依曼架构的有效策略之一,存内计算(computing in memory,缩写为cim)引起了广泛关注,存内计算将存储器与运算模块合二为一,大幅减少了数据的搬移,进而节省了这部分的时间和能耗开销。

4.内容可寻址存储器(binary content addressable memory,缩写为bcam)作为存内计算的特殊应用,它通过数据输入与存储数据逐位比较,实现了在存储器内部完成比较操作,提高了搜索效率的同时降低了功耗。现有的bcam研究主要拘泥于单向数据搜索,有的是数据纵向输入,与阵列存储字逐行比较,结构复杂固化,模块复用性差,功能单一;有的是数据横向输入,与阵列存储字逐列比较,与sram数据按行写入方式相悖,不易写入待比较数据。根据公开号为cn102024819a公开的sram位单元装置与cam位单元装置,其具有较低待机漏电流isb、改善的vcc,min用以降低待机耗电、与改善的存取速度等优点。但是该装置的10t-sram单元中行列逻辑操作无法同时进行。

技术实现要素:

5.基于此,有必要针对单向数据搜索不易写入待比较数据的问题,提供一种10t-sram单元及其数据读写方法、电路结构、模块、芯片。

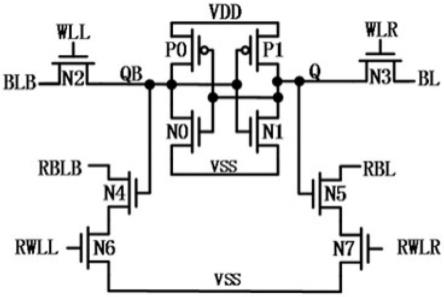

6.10t-sram单元,其包括:nmos晶体管n0~n7,pmos晶体管p0~p1。

7.具体连接方式如下:n0的源极电连接电压源vss。

8.n1的栅极与n0的漏极电连接,n1的源极与n0的源极电连接,n1的漏极与n0的栅极电连接。

9.p0的漏极与n0的漏极电连接,p0的栅极与n0的栅极电连接,p0的源极电连接电压源vdd。

10.p1的漏极与n1的漏极电连接,p1的栅极与p0的漏极电连接,p1的源极与p0的源极电连接。

11.n2的漏极与n0的漏极电连接,n2的栅极电连接字线wll,n2的源极电连接位线blb。

12.n3的漏极与n0的栅极电连接,n3的栅极电连接字线wlr,n3的源极电连接位线bl。

13.n4的栅极与n0的漏极电连接,n4的源极电连接位线rblb。

14.n5的栅极与n1的漏极电连接,n5的源极与位线rbl电连接。

15.n6的漏极与n4的漏极电连接,n6的栅极与字线rwll电连接,n6的源极电连接电压

源vss。

16.n7的漏极与n5的漏极电连接,n7的源极与n6的源极电连接,n7的栅极与字线rwlr电连接。

17.存储节点qb通过n2与字线wll、位线blb相连;存储节点q通过n3与字线wlr、位线bl相连;p0和n0构成一个反相器,p1和n1构成另一个反相器,两个反相器形成交叉耦合结构;n2和n3作为传输管,各自位于交叉耦合结构左右两侧作为左右两个写通路;n4和n6构成左通路,n5和n7构成右通路。

18.进一步的,10t-sram单元数据写入时,通过bl和blb进行写入,字线wll和字线wlr置为高电平。

19.进一步的,10t-sram单元数据读取时,通过rblb或rbl进行读出,字线rwll或字线rwlr置为高电平。

20.本发明还包括一种根据前述的10t-sram单元的数据读写方法,数据读写方法在数据写入时,通过bl和blb进行写入,字线wll和字线wlr置为高电平;所述数据读写方法在数据读取时,通过rblb或rbl进行读出,字线rwll或字线rwlr置为高电平。

21.本发明还提供一种基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路结构,其采用前述10t-sram单元,基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路结构包括4

×

4个10t-sram单元。

22.其中,位于同一行的10t-sram单元,所有单元晶体管n2的栅极电连接字线wll,所有单元晶体管n3的栅极电连接字线wlr,所有单元晶体管n4的源极电连接位线rblb,所有单元晶体管n5的源极电连接位线rbl,每一行共享字线wll、wlr以及位线rbl、rblb。

23.位于同一列的10t-sram单元,所有单元晶体管n2的源极电连接位线blb,所有单元晶体管n3的源极电连接位线bl,所有单元晶体管n6的栅极电连接字线rwll,所有单元晶体管n7的栅极电连接字线rwlr,每一列共享位线bl、blb以及字线rwll、rwlr。

24.该电路结构进行数据按阵列逐行查找时,字线rwll和rwlr分别作为数据输入线,位线rbl和rblb作为匹配线,匹配结果通过位线rbl和rblb末端灵敏放大器再经过与门读出。数据按阵列逐列查找时,字线wll和wlr分别作为数据输入线,位线bl和blb作为匹配线,匹配结果通过位线bl和blb末端灵敏放大器再经过与门读出。

25.进一步的,在10t-sram单元保持数据期间,写字线wll、写字线wlr、读字线rwll及读字线rwlr均保持低电平,此时n2、n3、n6以及n7均关断。

26.进一步的,假设在写操作前10t-sram单元的存储节点q为高电平,qb为低电平,即存储数据为“1”,在写入数据“0”时,写操作字线wll和wlr被拉为高电平选中单元,同时将需要写入的数据“0”加载到写位线bl和blb上。

27.进一步的,假设在读操作前10t-sram单元的存储节点q为高电平,qb为低电平,即存储数据为“1”;在读操作开始时,读位线rbl和rblb预充电至高电平,读字线rwll或rwlr被拉为高电平,nmos晶体管n6或nmos晶体管n7被开启。

28.本发明还包括基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路模块,其采用前述的基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路结构,基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路模块包括:

29.位于同一行的10t-sram单元,所有单元晶体管n2的栅极电连接字线wll,由此引出

第一连接端,所有单元晶体管n3的栅极电连接字线wlr,由此引出第二连接端,所有单元晶体管n4的源极电连接位线rblb,由此引出第三连接端,所有单元晶体管n5的源极电连接位线rbl,由此引出第四连接端;每一行存在一个第一连接端、第二连接端、第三连接端和第四连接端。

30.位于同一列的10t-sram单元,所有单元晶体管n2的源极电连接位线blb,由此引出第五连接端,所有单元晶体管n3的源极电连接位线bl,由此引出第六连接端,所有单元晶体管n6的栅极电连接字线rwll,由此引出第七连接端,所有单元晶体管n7的栅极电连接字线rwlr,由此引出第八连接端;每一列存在一个第五连接端、第六连接端、第七连接端和第八连接端。

31.本发明还包括一种基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路芯片,其采用如前述的基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路结构封装而成。

32.本发明提供的技术方案,具有如下有益效果:

33.10t-sram单元采用双端口布置以及双字线双位线的交叉布局,控制不同字线的开启与关断,能够并行激活多行和多列的阵列,实现在两个方向上的矢量逻辑操作,使由10t-sram单元构建的存储阵列具有良好的对称性,不仅可以同一个周期读取两列数据,还能够同时进行横纵双向存内逻辑运算和bcam数据搜索操作,并且保证了操作时数据独立性,提高了单元的抗干扰能力和计算效率。它的对称性提供了数据按列或按行搜索,很容易适合sram存储模式。这些模式允许在存内计算中进行矩阵转置、逻辑操作和内容寻址存内(cam)数据搜索,而无需进行额外的数据移动。

附图说明

34.图1为本发明10t-sram单元的结构示意图;

35.图2为以图1为基础进行数据按行或按列进行与和或非逻辑运算结构示意图;

36.图3为以图1为基础进行数据按行或按列进行和逻辑运算结构示意图;

37.图4为以图1为基础的进行数据按行或按列进行同或和异或逻辑运算结构示意图;

38.图5为以图1内10t-sram单元为基础的4

×

4个10t-sram单元的结构示意图;

39.图6为以图5为基础进行双向bcam搜索的操作时序图;

40.图7为以图5内4

×

4个10t-sram单元为基础的基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路芯片的结构示意图。

具体实施方式

41.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步地详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

42.如图1所示,本发明提供一种10t-sram单元,其包括nmos晶体管n0~n7和pmos晶体管p0~p1,p0和n0构成一个反相器,p1和n1构成另一个反相器,两个反相器形成交叉耦合结构;n2和n3作为传输管,各自位于交叉耦合结构左右两侧作为左右两个写通路;n4和n6构成左通路,n5和n7构成右通路。

43.具体连接方式为:nmos晶体管n1,n1的栅极与n0的漏极电连接,n1的源极与n0的源极电连接,n1的漏极与n0的栅极电连接。nmos晶体管n2,n2的漏极与n0的漏极、n1的栅极电连接,n2的栅极电连接字线wll,nmos晶体管n2的源极电连接位线blb。nmos晶体管n3,n3的漏极与n0的栅极、n1的漏极电连接,n3的栅极电连接字线wlr,n3的源极电连接位线bl。nmos晶体管n4,n4的栅极与n0的漏极、n1的栅极、n2的漏极电连接,n4的源极电连接位线rblb。nmos晶体管n5,n5的栅极与n1的漏极、n0的栅极、n3的漏极电连接,n5的源极与位线rbl电连接。nmos晶体管n6,n6的漏极与n4的漏极电连接,n6的栅极与字线rwll电连接。nmos晶体管n7,n7的漏极与n5的漏极电连接,n7的源极与n6的源极电连接,n7的栅极与字线rwlr电连接。pmos晶体管p0,p0的漏极与n0的漏极、n2的漏极、n1的栅极、n4的栅极电连接,p0的栅极与n1的漏极、n3的漏极、n0的栅极、n5的栅极电连接。pmos晶体管p1,p1的漏极与n1的漏极、n3的漏极、n0的栅极、n5的栅极以及p0的栅极电连接,p1的栅极与p0的漏极、n0的漏极、n2的漏极、n1的栅极以及n4的栅极电连接,p1的源极与p0的源极电连接。

44.用10t-sram单元数据写入时,通过bl和blb进行写入,字线wll和字线wlr置为高电平;用10t-sram单元数据读取时,通过rblb或rbl进行读出,rwll或rwlr置为高电平。

45.在上述10t-sram单元的基础上,可以组建一种基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路结构,其包括4

×

4个10t-sram单元。

46.针对4

×

4个10t-sram单元,位于同一行的10t-sram单元,所有单元晶体管n2的栅极电连接字线wll,所有单元晶体管n3的栅极电连接字线wlr,所有单元晶体管n4的源极电连接位线rblb,所有单元晶体管n5的源极电连接位线rbl,每一行共享字线wll、wlr以及位线rbl、rblb。位于同一列的10t-sram单元,所有单元晶体管n2的源极电连接位线blb,所有单元晶体管n3的源极电连接位线bl,所有单元晶体管n6的栅极电连接字线rwll,所有单元晶体管n7的栅极电连接字线rwlr,每一列共享位线bl、blb以及字线rwll、rwlr。每一列共享位线bl、blb以及字线rwll、rwlr。bl与blb在每一列末尾处连接两个灵敏放大器sa,在此基础上连接一个与门进行读出。rbl与rblb在每一行末尾处连接两个灵敏放大器sa,在此基础上连接一个与门进行读出。

47.具体操作如下:数据按阵列逐行查找时,字线rwll和rwlr分别作为数据输入线,位线rbl和rblb作为匹配线,匹配结果通过位线rbl和rblb末端灵敏放大器再经过与门读出,记为row search。数据按阵列逐列查找时,字线wll和wlr分别作为数据输入线,位线bl和blb作为匹配线,匹配结果通过位线bl和blb末端灵敏放大器再经过与门读出,记为column search。

48.上述阵列结构在不增加晶体管数量的情况下可以同时实现横纵双向bcam数据搜索操作,既可以很好地适应sram的写入方式,又增加了结构的复用性,并且数据抗干扰能力大大提高,可以适应各种复杂的应用场景。

49.以sram模式为例,在上述4

×

4个10t-sram单元的基础上,进行sram模式,具体操作步骤如下:

50.(1)保持操作

51.在存储单元保持数据期间,写字线wll、写字线wlr、读字线rwll及读字线rwlr均保持低电平。此时nmos晶体管n2、nmos晶体管n3、nmos晶体管n6以及nmos晶体管n7均关断,写位线bl和blb以及读位线rbl和rblb均不会对存储节点q或qb造成影响。pmos晶体管p0、nmos

晶体管n0、pmos晶体管p1和nmos晶体管n1构成的锁存结构将锁存存储节点q和qb的数据。

52.(2)写操作

53.假设在写操作前存储单元存储节点q为高电平,qb为低电平,即存储数据为“1”,在写入数据“0”时,写操作字线wll和wlr被拉为高电平选中单元,同时将需要写入的数据“0”加载到写位线上,即bl为低电平,blb为高电平。bl通过nmos晶体管n3下拉节点q,blb通过nmos晶体管n2上拉节点qb,所存结构反馈环被打破,数据“0”写入存储单元。写入数据“1”与上述过程同理。

54.(3)读操作

55.假设在读操作前存储单元存储节点q为高电平,qb为低电平,即存储数据为“1”。在读操作开始时,读位线rbl和rblb预充电至高电平,读字线rwll或rwlr被拉为高电平,nmos晶体管n6或nmos晶体管n7被开启。若nmos晶体管n6被开启,由于存储节点qb为低电平,因此nmos晶体管n4关断,读位线rblb仍保持高电平,经过灵敏放大器sa放大后,读出结果为“1”。若存储节点qb为高电平,与上述过程同理。

56.实现sram模式的真值表如下表所示,其中a表示第a列,b表示第b列,l表示低电平,h表示高电平,read表示读操作,write表示写操作,hold表示保持状态。

57.sram真值表

[0058][0059]

以存内计算模式为例,在上述4

×

4个10t-sram单元的基础上,进行存内计算模式。

[0060]

下列以存内计算模式的布尔逻辑运算为例,具体实施如下:

[0061]

如图2所示,以1位逻辑与操作为例介绍同一列之间通过bl和blb实现两行或多行逻辑与运算。

[0062]

同一列之间,控制wll和wlr的开启与关断,通过bl和blb实现两行或多行逻辑与运算和或非运算。同一行之间,控制rwll和rwlr的开启与关断,通过rbl和rblb实现两列或多列逻辑与运算或和非运算。第一列的第一行的单元存储数据记为q3,字线记为wll1和wlr1,位线记为blb1和bl1,第一列的第二行的单元存储数据记为q1,字线记为wll0和wlr0,位线blb1配置一个单端灵敏放大器(sa),位线bl1也配置一个单端灵敏放大器,将两个灵敏放大器的输出端与与门相接作为逻辑输出。位线blb1和bl1预充至高电平,字线wll1和字线wll0置为低电平,字线wlr1和wlr0置为高电平,q3与q1中的任一节点存在数据0,位线bl1出现放电;只有节点q3与q1同时为1,位线bl1保持高电平,由于字线wll1和字线wll0都为低电平,所以blb1一直保持高电平,通过sa和与门,即可实现q3与q1的逻辑与运算。

[0063]

如图3所示,以1位逻辑操作为例介绍同一行之间通过rbl和rblb实现两列逻辑运算。

[0064]

同一列之间,控制wll和wlr的开启与关断,通过bl和blb实现两行逻辑或运算。同一行之间,控制rwll和rwlr的开启与关断,通过rbl和rblb实现两列逻辑或运算。第一行的第一列的单元存储数据记为q3,字线记为rwll1和rwlr1,位线记为rblb1和rbl1,第一行的第二列的单元存储数据记为q2,字线记为rwll0和rwlr0。位线rblb1配置一个单端灵敏放大器(sa),位线rbl1也配置一个单端灵敏放大器,将两个灵敏放大器的输出端与与门相接作为逻辑输出。位线rblb1和rbl1预充至高电平,字线rwlr1和字线rwll0置为低电平,字线rwll1和rwlr0置为高电平,只有qb3和q2至少一个为1时,rbl1和rblb1至少有一个放电,通过灵敏放大器和与门输出得到低电平,即可实现逻辑运算。

[0065]

如图4所示,以逻辑异或操作为例介绍同一列之间通过bl和blb实现两行逻辑异或运算。

[0066]

同一列之间,同时开启某两行的wll和wlr,通过bl和blb实现两行逻辑同或和异或运算。同一行之间,同时开启某两列的rwll和rwlr,通过rbl和rblb实现两列逻辑同或和异或运算。第一列的第一行的单元存储数据记为q3,字线记为wll1和wlr1,位线记为blb1和bl1,第一列的第二行的单元存储数据记为q1,字线记为wll0和wlr0,位线blb1配置一个单端灵敏放大器(sa),位线bl1也配置一个单端灵敏放大器,将两个灵敏放大器的输出端与与门相接作为逻辑输出。位线blb1和bl1预充至高电平,字线wll1、字线wll0、字线wlr1和wlr0都置为高电平,由于q3q1有四种状态:00、01、10、11,因此位线放电电压会相应有所不同,利用灵敏放大器的参考电压可以实现逻辑或操作和逻辑操作,再通过一个与门,即可实现q3与q1的逻辑异或运算。

[0067]

下列以存内计算模式的双向bcam为例,具体实施如下:

[0068]

如图5所示,数据查找之前,存储单元存入待查二进制数据,匹配线bl、blb、rbl和rblb预充为高电平,数据输入线wll、wlr、rwll和rwlr根据查找数据置高电平或低电平。若查找数据为1,wlr和rwll置为高电平,wll和rwlr置为低电平;若查找数据为0,wlr和rwll置为低电平,wll和rwlr置为高电平。

[0069]

结合图6,为了更加清晰地展现出本发明所提供的技术方案及所产生的技术效果,以4位二进制数据“0110”进行row search为例,则rwll3、rwlr2、rwlr1和rwll0置为低电平,rwll2、rwlr3、rwlr0和rwll1置为高电平。阵列一共四行,每一行从左到右存储单元分别存入“0110”、“0101”、“1100”、“1110”。下面分析数据比较过程,当搜索数据为“0”时,rwlr为高电平,只有当存储节点为“1”时,相应的rbl才会放电,代表搜索的数据不匹配。因为rwll为低电平,所以rblb保持高电平,则rbl和rblb经过两个灵敏放大器和一个与门,最终输出是否匹配结果。当搜索数据为“1”时,rwll为高电平,只有当存储节点为“0”时,相应的rblb才会放电,代表搜索的数据不匹配。因为rwlr为低电平,所以rbl保持高电平,则rbl和rblb经过两个灵敏放大器和一个与门,最终输出是否匹配结果。若搜索数据与存储数据完全匹配,则最终输出高电平。若搜索数据与存储数据不完全匹配,则最终输出低电平。

[0070]

以4位二进制数据“1001”进行column search为例,则wll3、wlr2、wlr1和wll0置为

低电平,wll2、wlr3、wlr0和wll1置为高电平。当搜索数据为“0”时,wll为高电平,只有当存储节点为“1”时,相应的blb才会放电,代表搜索的数据不匹配。因为wlr为低电平,所以bl保持高电平,则bl和blb经过两个灵敏放大器和一个与门,最终输出是否匹配结果。当搜索数据为“1”时,wlr为高电平,只有当存储节点为“0”时,相应的bl才会放电,代表搜索的数据不匹配。因为wll为低电平,所以blb保持高电平,则bl和blb经过两个灵敏放大器和一个与门,最终输出是否匹配结果。若搜索数据与存储数据完全匹配,则最终输出高电平。若搜索数据与存储数据不完全匹配,则最终输出低电平。

[0071]

实现cim模式的真值表如下表所示,其中a表示第a行(列),b表示第b行(列),l表示低电平,h表示高电平,ha表示第a行的相应字线为高电平,l1表示若搜索数据为1则相应字线应置为低电平。

[0072]

内布尔逻辑运算和双向bcam功能的真值表

[0073][0074]

综上所述,10t-sram单元采用双端口布置以及双字线双位线的交叉布局,使由10t-sram单元构建的存储阵列具有良好的对称性,不仅可以同一个周期读取两列数据,还能够同时进行横纵双向存内逻辑运算和bcam数据搜索操作,并且保证了操作时数据独立性,提高了单元的抗干扰能力和计算效率。

[0075]

如图7所示,在前述4

×

4个10t-sram单元的基础上,进一步的提供了一种基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路芯片,其采用前述的4

×

4个10t-sram单元封装而成,封装成芯片的模式,更易于4

×

4个10t-sram单元电路的推广与应用。

[0076]

基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路芯片的引脚包括:位于第一行的四个10t-sram单元,所有单元晶体管n2的栅极电连接字线wll,由此引出第一引脚;所有单元晶体管n3的栅极电连接字线wlr,由此引出第二引脚;所有单元晶体管n4的源极电连接位线rblb,由此引出第三引脚;所有单元晶体管n5的源极电连接位线rbl,由此引出第四引脚;第一行存在一个所述第一引脚、所述第二引脚、所述第三引脚和所述第四引

脚。位于第二行的四个10t-sram单元,所有单元晶体管n2的栅极电连接字线wll,由此引出第五引脚;所有单元晶体管n3的栅极电连接字线wlr,由此引出第六引脚;所有单元晶体管n4的源极电连接位线rblb,由此引出第七引脚;所有单元晶体管n5的源极电连接位线rbl,由此引出第八引脚;第二行存在一个所述第五引脚、所述第六引脚、所述第七引脚和所述第八引脚。位于第三行的四个10t-sram单元,所有单元晶体管n2的栅极电连接字线wll,由此引出第九引脚;所有单元晶体管n3的栅极电连接字线wlr,由此引出第十引脚;所有单元晶体管n4的源极电连接位线rblb,由此引出第十一引脚;所有单元晶体管n5的源极电连接位线rbl,由此引出第十二引脚;第三行存在一个所述第九引脚、所述第十引脚、所述第十一引脚和所述第十二引脚。位于第四行的四个10t-sram单元,所有单元晶体管n2的栅极电连接字线wll,由此引出第十三引脚;所有单元晶体管n3的栅极电连接字线wlr,由此引出第十四引脚;所有单元晶体管n4的源极电连接位线rblb,由此引出第十五引脚;所有单元晶体管n5的源极电连接位线rbl,由此引出第十六引脚;第四行存在一个所述第十三引脚、所述第十四引脚、所述第十五引脚和所述第十六引脚。

[0077]

位于第一列的10t-sram单元,所有单元晶体管n2的源极电连接位线blb,由此引出第十七引脚,所有单元晶体管n3的源极电连接位线bl,由此引出第十八引脚,所有单元晶体管n6的栅极电连接字线rwll,由此引出第十九引脚,所有单元晶体管n7的栅极电连接字线rwlr,由此引出第二十引脚;第一列存在一个所述十七引脚、所述十八引脚、所述十九引脚和所述二十引脚。位于第二列的10t-sram单元,所有单元晶体管n2的源极电连接位线blb,由此引出第二十一引脚,所有单元晶体管n3的源极电连接位线bl,由此引出第二十二引脚,所有单元晶体管n6的栅极电连接字线rwll,由此引出第二十三引脚,所有单元晶体管n7的栅极电连接字线rwlr,由此引出第二十四引脚;第二列存在一个所述二十一引脚、所述二十二引脚、所述二十三引脚和所述二十四引脚。位于第三列的10t-sram单元,所有单元晶体管n2的源极电连接位线blb,由此引出第二十五引脚,所有单元晶体管n3的源极电连接位线bl,由此引出第二十六引脚,所有单元晶体管n6的栅极电连接字线rwll,由此引出第二十七引脚,所有单元晶体管n7的栅极电连接字线rwlr,由此引出第二十八引脚;第三列存在一个所述二十五引脚、所述二十六引脚、所述二十七引脚和所述二十八引脚。位于第四列的10t-sram单元,所有单元晶体管n2的源极电连接位线blb,由此引出第二十九引脚,所有单元晶体管n3的源极电连接位线bl,由此引出第三十引脚,所有单元晶体管n6的栅极电连接字线rwll,由此引出第三十一引脚,所有单元晶体管n7的栅极电连接字线rwlr,由此引出第三十二引脚;第四列存在一个所述二十九引脚、所述三十引脚、所述三十一引脚和所述三十二引脚。

[0078]

在前述4

×

4个10t-sram单元的基础上,还提供了一种基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路模块,其包括:位于同一行的10t-sram单元,所有单元晶体管n2的栅极电连接字线wll,由此引出第一连接端,所有单元晶体管n3的栅极电连接字线wlr,由此引出第二连接端,所有单元晶体管n4的源极电连接位线rblb,由此引出第三连接端,所有单元晶体管n5的源极电连接位线rbl,由此引出第四连接端;每一行存在一个所述第一连接端、所述第二连接端、所述第三连接端和所述第四连接端。位于同一列的10t-sram单元,所有单元晶体管n2的源极电连接位线blb,由此引出第五连接端,所有单元晶体管n3的源极电连接位线bl,由此引出第六连接端,所有单元晶体管n6的栅极电连接字线rwll,由此引出

第七连接端,所有单元晶体管n7的栅极电连接字线rwlr,由此引出第八连接端;每一列存在一个所述第五连接端、所述第六连接端、第七连接端和第八连接端。

[0079]

将基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路结构设计成电路模块,可方便基于10t-sram单元的存内布尔逻辑运算和双向bcam的电路结构在市场中的推广与应用,方便本领域技术人员快速使用,只需要对着产品说明书,对模块进行线路连接即可。

[0080]

以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0081]

以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1