存储器件失效测试结构及测试方法与流程

1.本发明涉及半导体集成电路制造领域,特别涉及一种存储器件失效测试结构及测试方法。

背景技术:

2.随着快闪存储器的进一步发展,存储单元的尺寸进一步缩小,对工艺的挑战也越来越大。其中,字线的宽度进一步缩小会导致存储单元的电性能对字线上的缺陷更加敏感,但是,常规的测试结构无法筛选出此类不良。

3.在常规测试结构中,只引出单个字线和位线,以用于检测单个存储单元的本征特性(包含阈值电压vt和饱和漏电流idsat等),但是,对于字线的线宽明显变窄的异常,无法在工艺生产过程中提前采用此常规测试结构以及相应的测试方法测试出来,而是需对芯片进行可靠性测试之后,才能发现线宽过窄的字线所在的存储单元保持电子的能力下降,阈值电压发生漂移,从而确定该存储单元中的字线存在缺陷,导致无法提前发现工艺的恶化倾向,无法及时对工艺异常进行改善,进而导致批量产品存在可靠性风险。

4.因此,需要对测试结构及测试方法进行改进,以解决上述问题。

技术实现要素:

5.本发明的目的在于提供一种存储器件失效测试结构及测试方法,能够在工艺过程中提前发现工艺的恶化倾向,及时对工艺异常进行改善,避免导致批量产品存在可靠性风险。

6.为实现上述目的,本发明提供了一种存储器件失效测试结构,包括:

7.存储器件,包含若干存储单元,每个所述存储单元均包含字线和位线;

8.第一焊盘,与所有的所述存储单元中的字线电连接;

9.第二焊盘,与所有的所述存储单元中的位线电连接。

10.可选地,每个所述存储单元均包含源极线,所述存储器件失效测试结构还包括:

11.第三焊盘,与所有的所述存储单元中的源极线电连接。

12.可选地,所述存储器件失效测试结构还包括若干个导电插塞和若干条金属互连线,所述第一焊盘通过所述导电插塞和所述金属互连线与所述字线电连接,所述第二焊盘通过所述导电插塞和所述金属互连线与所述位线电连接。

13.本发明还提供一种存储器件失效测试方法,包括:

14.提供所述的存储器件失效测试结构;

15.将所有的所述存储单元置于

‘0’

状态;

16.于所述第一焊盘施加负电压且于所述第二焊盘施加第一正电压,以同时对所有的所述存储单元进行应力测试;

17.同时对所有的所述存储单元进行读操作,并根据读取的第一漏电流判断所述存储器件中是否存在缺陷。

18.可选地,将所有的所述存储单元置于

‘0’

状态的步骤包括:

19.于所述第一焊盘施加第二正电压且于所述第二焊盘施加第三正电压,以同时对所有的所述存储单元进行写入操作,使得所有的所述存储单元写入全

‘0’

。

20.可选地,将所有的所述存储单元置于

‘0’

状态的步骤还包括:

21.于所述第一焊盘施加第四正电压且于所述第二焊盘施加第五正电压,并同时对所有的所述存储单元进行读操作,以读取获得第二漏电流。

22.可选地,所述第二正电压的范围为大于9v,所述第三正电压的范围为大于或等于3.5v,所述第四正电压的范围为5v~9v,所述第五正电压的范围为0.5v~1v。

23.可选地,于所述第一焊盘施加所述第二正电压且于所述第二焊盘施加所述第三正电压的时间范围为1μs~10μs。

24.可选地,所述负电压的范围为小于或等于-1v,所述第一正电压的范围为大于或等于3.8v。

25.可选地,于所述第一焊盘施加所述负电压且于所述第二焊盘施加所述第一正电压的时间范围为大于或等于1μs。

26.可选地,在应力测试过程中,处于

‘0’

状态的所述存储单元中的字线中的电子被拉出到所述存储单元中的漏极区中。

27.可选地,于所述第一焊盘施加第六正电压且于所述第二焊盘施加第七正电压,以同时对所有的所述存储单元进行读操作。

28.可选地,所述第六正电压的范围为5v~9v,所述第七正电压的范围为0.5v~1v。

29.可选地,若读取的所述第一漏电流与所述第二漏电流之比小于或等于10,则所述存储器件中的栅极结构未存在缺陷;若读取的所述第一漏电流与所述第二漏电流之比大于10,则所述存储器件中的栅极结构存在缺陷;其中,所述栅极结构包含自下向上的隧穿氧化层、浮栅层、栅间介质层和所述字线。

30.可选地,若读取的所述第一漏电流和所述第二漏电流均为na级,则所述存储器件中的栅极结构未存在缺陷;若读取的所述第一漏电流为μa级,所述第二漏电流为na级,则所述存储器件中的栅极结构存在缺陷。

31.与现有技术相比,本发明的技术方案具有以下有益效果:

32.1、本发明的应力迁移测试结构,由于将所有的存储单元中的字线连通后电连接至同一第一焊盘,且将所有的所述存储单元中的位线连通后电连接至同一第二焊盘,使得能够通过所述第一焊盘和所述第二焊盘同时对存储器件中的所有存储单元进行失效测试,进而使得在晶圆制造完成之后即可立即对所述存储器件进行失效测试,而无需等待至对芯片进行可靠性测试之后才能发现缺陷,从而使得能够在工艺过程中提前发现工艺的恶化倾向,监控工艺的稳定性,及时对工艺异常进行改善,避免导致批量产品存在可靠性风险。

33.2、本发明的应力迁移测试方法,通过提供所述存储器件失效测试结构,并在将所有的所述存储单元置于

‘0’

状态之后,于所述第一焊盘施加负电压且于所述第二焊盘施加第一正电压,以同时对所有的所述存储单元进行应力测试,使得能够根据应力测试之后读取的第一漏电流判断所述存储器件中是否存在缺陷,从而使得能够在工艺过程中提前发现工艺的恶化倾向,监控工艺的稳定性,及时对工艺异常进行改善,避免导致批量产品存在可靠性风险。

附图说明

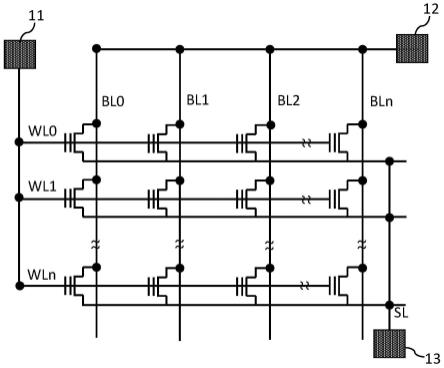

34.图1是本发明一实施例的存储器件失效测试结构的示意图;

35.图2是本发明一实施例的存储单元的结构示意图;

36.图3是本发明一实施例的存储器件失效测试方法的流程图。

37.其中,附图1~图3的附图标记说明如下:

38.11-第一焊盘;12-第二焊盘;13-第三焊盘;21-衬底;221-源极区;222-漏极区;231-隧穿氧化层;232-浮栅层;233-栅间介质层;234-控制栅层;24-侧墙;25-金属硅化物层;26-层间介质层;27-字线导电插塞;28-位线导电插塞。

具体实施方式

39.为使本发明的目的、优点和特征更加清楚,以下对本发明提出的存储器件失效测试结构及测试方法作进一步详细说明。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

40.本发明一实施例提供了一种存储器件失效测试结构,包括:存储器件,包含若干存储单元,每个所述存储单元均包含字线和位线;第一焊盘,与所有的所述存储单元中的字线电连接;第二焊盘,与所有的所述存储单元中的位线电连接。

41.下面参阅图1~图2详细描述本实施例提供的存储器件失效测试结构。其中,图2也是存储单元的纵向剖面示意图。

42.所述存储器件包含若干阵列排布的存储单元,如图2所示,每个所述存储单元包含衬底21以及形成于衬底21上的栅极结构,所述衬底21中形成有阱区(未图示),所述栅极结构形成于所述阱区上,所述栅极结构包括自下向上的隧穿氧化层231、浮栅层232、栅间介质层233和控制栅层234,所述栅极结构的侧壁上形成有侧墙24,所述栅极结构的顶面形成有金属硅化物层25,所述栅极结构两侧的阱区中分别形成有源极区221和漏极区222,所述衬底21上还覆盖有层间介质层26,所述层间介质层26将所述栅极结构、侧墙24、金属硅化物层25、源极区221和漏极区222掩埋在内,金属硅化物层25上的层间介质层26中形成有字线导电插塞27,所述漏极区222上的层间介质层26中形成有位线导电插塞28,所述源极区221上的层间介质层26中形成有源极线导电插塞(未图示)。并且,所述层间介质层26中还可形成有用于分别将所述字线导电插塞27、所述位线导电插塞28和所述源极线导电插塞引出到所述层间介质层26顶面的若干条金属互连线(未示出)。

43.在所述存储单元中,所述控制栅层234称为字线,所述漏极区222称为位线,所述源极区221称为源极线。

44.所述存储器件失效测试结构包含第一焊盘11、第二焊盘12和第三焊盘13,所述第一焊盘11、所述第二焊盘12和所述第三焊盘13可以形成于所述层间介质层26的顶面。

45.所有的所述存储单元中的字线均可以通过所述字线导电插塞27和所述金属互连线电连接至所述第一焊盘11,所有的所述存储单元中的位线均可以通过所述位线导电插塞28和所述金属互连线电连接至所述第二焊盘12,所有的所述存储单元中的源极线均可以通过所述源极线导电插塞和所述金属互连线电连接至所述第三焊盘13。

46.如图1所示,在所述存储器件中的存储单元阵列中,所述第一焊盘11与所有的所述存储单元中的字线wl0、wl1至wln电连接,所述第二焊盘12与所有的所述存储单元中的位线

bl0、bl1、bl2至bln电连接,所述第三焊盘13与所有的所述存储单元中的源极线sl电连接。

47.从上述内容可知,本发明提供的存储器件失效测试结构,由于将所有的所述存储单元中的字线连通后电连接至同一第一焊盘,将所有的所述存储单元中的位线连通后电连接至同一第二焊盘,且将所有的所述存储单元中的源极线连通后电连接至同一第三焊盘,使得能够通过所述第一焊盘、所述第二焊盘和所述第三焊盘同时对所述存储器件中的所有存储单元进行失效测试(即当所述存储单元中的栅极结构存在宽度过窄缺陷时,能够测试到电流明显增高),进而使得在晶圆制造完成之后即可立即对所述存储器件进行失效测试,而无需等待至对芯片进行可靠性测试之后才能发现缺陷,从而使得能够在工艺过程中提前发现工艺的恶化倾向,监控工艺的稳定性,及时对工艺异常进行改善,避免导致批量产品存在可靠性风险。

48.基于同一发明构思,本发明一实施例提供了一种存储器件失效测试方法,参阅图3,从图3中可看出,所述存储器件失效测试方法包括:

49.步骤s1,提供所述的存储器件失效测试结构;

50.步骤s2,将所有的所述存储单元置于

‘0’

状态;

51.步骤s3,于所述第一焊盘施加负电压且于所述第二焊盘施加第一正电压,以同时对所有的所述存储单元进行应力测试;

52.步骤s4,同时对所有的所述存储单元进行读操作,并根据读取的第一漏电流判断所述存储器件中是否存在缺陷。

53.下面参阅图1和图2对本实施例提供的存储器件失效测试方法进行详细说明。

54.按照步骤s1,提供所述的存储器件失效测试结构,所述存储器件失效测试结构参见上述内容,在此不再赘述。

55.按照步骤s2,将所有的所述存储单元置于

‘0’

状态。

56.其中,将所有的所述存储单元置于

‘0’

状态的步骤可以包括:于所述第一焊盘11施加第二正电压且于所述第二焊盘12施加第三正电压,以同时对所有的所述存储单元进行写入操作,使得所有的所述存储单元写入全

‘0’

,进而使得每个所述存储单元的电流变小。

57.优选的,将所有的所述存储单元置于

‘0’

状态的步骤还包括:于所述第一焊盘11施加第四正电压且于所述第二焊盘12施加第五正电压,并同时对所有的所述存储单元进行读操作,以确认所有的所述存储单元均置于

‘0’

状态,进而确认应力测试前读取获得的第二漏电流足够小。

58.优选的,所述第二正电压的范围为大于9v,所述第三正电压的范围为大于或等于3.5v,所述第四正电压的范围为5v~9v(含5v和9v),所述第五正电压的范围为0.5v~1v(含0.5v和1v)。

59.优选的,于所述第一焊盘11施加所述第二正电压且于所述第二焊盘12施加所述第三正电压的时间范围为1μs~10μs(含1μs和10μs)。

60.按照步骤s3,于所述第一焊盘11施加负电压且于所述第二焊盘12施加第一正电压,以同时对所有的所述存储单元进行应力测试。

61.在应力测试的过程中,处于

‘0’

状态的所述存储单元中的字线中的电子会被拉出到漏极区中,由于宽度过窄的栅极结构中的字线中存储的电子比宽度正常的栅极结构中的字线中存储的电子少,那么,电子被从字线中拉出对宽度过窄的字线的影响比对宽度正常

的字线的影响更大,宽度过窄的字线会导致应力测试之后的所述存储器件的阈值电压降低,漏电流增大;并且,由于栅极结构的宽度过窄会导致沟道的宽度也过窄,从而导致所述字线中存储的电子更加容易被拉出到所述漏极区中,从而导致应力测试之后的所述存储器件的阈值电压进一步降低,漏电流进一步增大。

62.那么,在所述存储器件中,若至少一个处于

‘0’

状态的所述存储单元中存在栅极结构宽度过窄缺陷,会导致应力测试之后的所述存储器件的阈值电压明显降低,漏电流明显增大,应力测试之后的漏电流相比应力测试之前的漏电流(即所述第二漏电流)突增;若所有处于

‘0’

状态的所述存储单元中均不存在栅极结构宽度过窄缺陷,则所述存储器件不受应力测试影响或受应力测试影响很小,应力测试之后与应力测试之前的漏电流差异很小。因此,通过所述第一焊盘11和所述第二焊盘12同时对所有的所述存储单元施加电压进行应力测试,能够根据应力测试前后的漏电流的变化来判断所述存储器件中是否存在栅极结构宽度过窄缺陷。

63.优选的,所述负电压的范围为小于或等于-1v,所述第一正电压的范围为大于或等于3.8v。

64.优选的,于所述第一焊盘11施加所述负电压且于所述第二焊盘12施加所述第一正电压的时间范围为大于或等于1μs,可以根据缺陷情况选择合适的时间。

65.按照步骤s4,同时对所有的所述存储单元进行读操作,并根据读取的第一漏电流判断所述存储器件中是否存在缺陷。

66.其中,若应力测试之后读取的所述第一漏电流与应力测试之前读取的所述第二漏电流之比小于或等于10,则所述存储器件中的栅极结构未存在缺陷(即宽度过窄缺陷);若应力测试之后读取的所述第一漏电流与应力测试之前读取的所述第二漏电流之比大于10,则所述存储器件中的栅极结构存在缺陷。

67.例如,若应力测试之后读取的所述第一漏电流和应力测试之前读取的所述第二漏电流均为na级,则所述存储器件中的栅极结构未存在缺陷;若应力测试之后读取的所述第一漏电流为μa级,应力测试之前读取的所述第二漏电流为na级,则所述存储器件中的栅极结构存在缺陷。

68.其中,所述存储器件中存在宽度过窄缺陷的栅极结构的数量至少为一个,并且,可以为图2所示的存储单元中的所述隧穿氧化层231、所述浮栅层232、所述栅间介质层233和所述控制栅层234中的至少一层结构存在宽度过窄缺陷。

69.并且,可以通过于所述第一焊盘11施加第六正电压且于所述第二焊盘12施加第七正电压,以同时对所有的所述存储单元进行读操作。

70.优选的,所述第六正电压的范围为5v~9v(含5v和9v),所述第七正电压的范围为0.5v~1v(含0.5v和1v)。

71.并且,需要说明的是,在上述步骤s2~步骤s4中,所述源极线sl通过所述第三焊盘13接地,且所述阱区接地。

72.并且,上述步骤s2~步骤s4可以在晶圆制造完成之后立即执行,例如在对晶圆进行晶圆级测试的过程中执行,使得无需等待至对芯片进行可靠性测试之后才能发现缺陷,从而使得能够在工艺过程中提前发现工艺的恶化倾向,监控工艺的稳定性,及时对工艺异常进行改善,避免导致批量产品存在可靠性风险。

73.从上述内容可知,本发明提供的存储器件失效测试方法,通过提供所述存储器件失效测试结构,并在将所有的所述存储单元置于

‘0’

状态之后,于所述第一焊盘施加负电压且于所述第二焊盘施加第一正电压,以同时对所有的所述存储单元进行应力测试,使得能够根据应力测试之后读取的第一漏电流判断所述存储器件中是否存在缺陷,从而使得能够在工艺过程中提前发现工艺的恶化倾向,监控工艺的稳定性,及时对工艺异常进行改善,避免导致批量产品存在可靠性风险。

74.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1