半导体存储装置及存储器系统的制作方法

半导体存储装置及存储器系统

1.分案申请的相关信息

2.本案是分案申请。该分案的母案是申请日为2018年1月30日、申请号为201810088572.8、发明名称为“半导体存储装置”的发明专利申请案。

3.[相关申请案]

[0004]

本技术享有以日本专利申请案2017-156530号(申请日:2017年8月14日)为基础申请案的优先权。本技术案通过参照该基础申请案而包含基础申请案的全部内容。

技术领域

[0005]

本发明的实施方式涉及一种半导体存储装置。

背景技术:

[0006]

作为半导体存储装置,已知有nand(not and,与非)型高速缓冲存储器。

技术实现要素:

[0007]

实施方式提供一种能够提高处理能力的半导体存储装置。

[0008]

实施方式的半导体存储装置包含:连结电路,设置在半导体衬底上,且包含连接于第一位线的第一电路及连接于第二位线的第二电路;第一组,包含连接于第一电路的第一读出放大器电路、及经由第一数据总线而连接于第一读出放大器电路的第一数据寄存器;第二组,包含连接于第二电路的第二读出放大器电路、及经由第二数据总线而连接于所述第二读出放大器电路的第二数据寄存器;及存储单元阵列,介隔层间绝缘膜设置在连结电路及第一及第二组的上方,且包含连接于第一位线的第一存储单元及连接于所述第二位线的第二存储单元。沿着与半导体衬底平行的第一方向,依次排列有第一组、连结电路、第二组。

附图说明

[0009]

图1是具备第一实施方式的半导体存储装置的存储器系统的框图。

[0010]

图2是第一实施方式的半导体存储装置的框图。

[0011]

图3是第一实施方式的半导体存储装置所具备的存储单元阵列的电路图。

[0012]

图4是第一实施方式的半导体存储装置所具备的存储单元阵列的立体图。

[0013]

图5是第一实施方式的半导体存储装置所具备的存储单元阵列的剖视图。

[0014]

图6是第一实施方式的半导体存储装置所具备的读出放大器的电路图。

[0015]

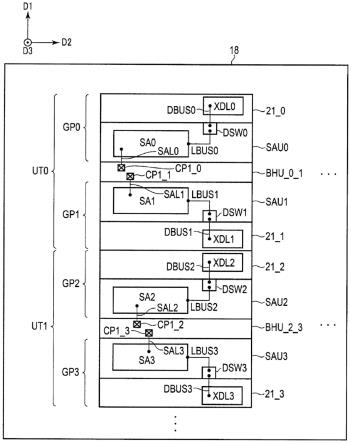

图7是第一实施方式的半导体存储装置所具备的bl连结电路、读出放大器及数据寄存器的俯视图。

[0016]

图8是第一实施方式的半导体存储装置的平面布局图。

[0017]

图9是第一实施方式的半导体存储装置所具备的存储单元阵列、bl连结电路、及读出放大器的剖视图。

[0018]

图10是第二实施方式的半导体存储装置所具备的bl连结电路、读出放大器及数据寄存器的俯视图。

[0019]

图11是第三实施方式的半导体存储装置所具备的bl连结电路、读出放大器及数据寄存器的俯视图。

[0020]

图12是第四实施方式中第一例的半导体存储装置所具备的dbus(data bus,数据总线)开关电路的电路图。

[0021]

图13是第四实施方式中第二例的半导体存储装置所具备的dbus开关电路的电路图。

[0022]

图14是第四实施方式中第三例的半导体存储装置所具备的dbus开关电路的电路图。

[0023]

图15是第四实施方式中第四例的半导体存储装置所具备的dbus开关电路的电路图。

[0024]

图16是第四实施方式中第五例的半导体存储装置所具备的dbus开关电路的电路图。

[0025]

图17是第四实施方式中第六例的半导体存储装置所具备的dbus开关电路的电路图。

[0026]

图18是第四实施方式中第七例的半导体存储装置所具备的dbus开关电路的电路图。

[0027]

图19是第四实施方式中第八例的半导体存储装置所具备的dbus开关电路的电路图。

[0028]

图20是第四实施方式中第九例的半导体存储装置所具备的dbus开关电路的电路图。

[0029]

图21是第一变化例的半导体存储装置所具备的存储单元阵列的剖视图。

具体实施方式

[0030]

以下,参照附图对实施方式进行说明。在该说明时,在所有图中对共通的部分标注共通的参照符号。

[0031]

1.第一实施方式

[0032]

对第一实施方式的半导体存储装置进行说明。以下,作为半导体存储装置,列举在半导体衬底上方三维地积层存储单元晶体管而成的三维积层型nand型高速缓冲存储器为例进行说明。

[0033]

1.1关于构成

[0034]

1.1.1关于存储器系统的整体构成

[0035]

首先,利用图1对具备本实施方式的半导体存储装置的存储器系统的整体构成进行说明。

[0036]

如图1所示,存储器系统1具备nand型高速缓冲存储器100及控制器110。也可通过例如控制器110与nand型高速缓冲存储器100的组合而构成一个半导体存储装置,作为其例,可列举像sdtm(secure digital touch memory,安全数字接触式存储)卡那样的存储卡或ssd(solid state drive,固态驱动器)等。

[0037]

nand型高速缓冲存储器100具备多个存储单元晶体管,将数据非易失地存储。nand型高速缓冲存储器100通过nand总线与控制器110连接,根据来自控制器110的命令进行动作。更具体来说,nand型高速缓冲存储器100与控制器110进行例如8位的信号dq0~dq7(以下,在不限定dq0~dq7的情况下,简单地表述为信号dq或信号dq[7:0])的收发。信号dq0~dq7中包含例如数据、地址、及指令。另外,nand型高速缓冲存储器100从控制器110接收例如芯片使能信号cen、指令锁存使能信号cle、地址锁存使能信号ale、写入使能信号wen、及读出使能信号ren。而且,nand型高速缓冲存储器100对控制器110发送就绪/忙碌信号r/bn。

[0038]

芯片使能信号cen是用来将nand型高速缓冲存储器100使能的信号,且以例如低(“l”)电平断定。指令锁存使能信号cle是表示信号dq为指令的信号,且以例如高(“h”)电平断定。地址锁存使能信号ale是表示信号dq为地址的信号,且以例如“h”电平断定。写入使能信号wen是用来将接收到的信号取入至nand型高速缓冲存储器100内的信号,每当从控制器110接收指令、地址、及数据等时,以例如“l”电平断定。由此,每当触发wen时,便将信号dq取入至nand型高速缓冲存储器100。读出使能信号ren是用于控制器110从nand型高速缓冲存储器100读出数据的信号。读出使能信号ren以例如“l”电平断定。就绪/忙碌信号r/bn是表示nand型高速缓冲存储器100为忙碌状态还是就绪状态(为无法从控制器110接收指令的状态还是能够从控制器110接收指令的状态)的信号,例如当nand型高速缓冲存储器100为忙碌状态时设为“l”电平。

[0039]

控制器110响应来自主机设备2的命令,对nand型高速缓冲存储器100命令数据的读出、写入、删除等。另外,控制器110管理nand型高速缓冲存储器100的存储空间。

[0040]

控制器110包含主机接口电路120、内置存储器(ram(random access memory,随机存取存储器))130、处理器(cpu(central processing unit,中央处理器))140、缓冲存储器150、nand接口电路160、及ecc电路170。

[0041]

主机接口电路120经由控制器总线与主机设备2连接,负责与主机设备2的通信。主机接口电路120将从主机设备2接收到的命令及数据传输至处理器140及缓冲存储器150。另外,主机接口电路120响应处理器140的命令而将缓冲存储器150内的数据向主机设备2传输。

[0042]

nand接口电路160经由nand总线与nand型高速缓冲存储器100连接,负责与nand型高速缓冲存储器100的通信。nand接口电路160将从处理器140接收到的命令传输至nand型高速缓冲存储器100。另外,nand接口电路160在写入时将缓冲存储器150内的写入数据传输至nand型高速缓冲存储器100。进而,nand接口电路160在读出时将从nand型高速缓冲存储器100读出的数据传输至缓冲存储器150。

[0043]

处理器140控制控制器110整体的动作。另外,处理器140响应主机设备2的命令而发出各种指令,并发送至nand型高速缓冲存储器100。例如,处理器140在从主机设备2接收到写入命令时,响应此而向nand型高速缓冲存储器100发送写入命令。读出及删除时也同样。另外,处理器140执行耗损平均等用来管理nand型高速缓冲存储器100的各种处理。进而,处理器140执行各种运算。例如,处理器140执行数据的加密处理或随机化处理等。

[0044]

缓冲存储器150保存从主机设备2接收到的写入数据、及从nand型高速缓冲存储器100接收到的读出数据等。

[0045]

ecc电路170执行数据的错误校正(ecc:error checking and correcting(错误检

查和纠正))处理。

[0046]

内置存储器130是例如dram(dynamic random access memory,动态随机存取存储器)等半导体存储器,用作处理器140的作业区域。而且,内置存储器130保存用来管理nand型高速缓冲存储器100的固件或各种管理表格等。

[0047]

1.1.2关于半导体存储装置的构成

[0048]

接下来,利用图2对半导体存储装置的构成进行说明。此外,图2中,以箭头线表示各区块间的连接的一部分,但区块间的连接并不限定于此。

[0049]

如图2所示,nand型高速缓冲存储器100包含输入输出电路10、逻辑控制电路11、状态寄存器12、地址寄存器13、指令寄存器14、定序器15、就绪/忙碌电路16、电压产生电路17、存储单元阵列18、行解码器19、读出放大器20、数据寄存器21、及列解码器22。

[0050]

输入输出电路10与控制器110进行例如8位的信号dq0~dq7的收发。更具体来说,输入输出电路10具备输入电路与输出电路。输入电路将从控制器110接收到的数据dat(写入数据wd)发送至数据寄存器21,将地址add发送至地址寄存器13,并将指令cmd发送至指令寄存器14。输出电路将从状态寄存器12接收到的状态信息sts、从数据寄存器21接收到的数据dat(读出数据rd)、及从地址寄存器13接收到的地址add发送至控制器110。

[0051]

逻辑控制电路11从控制器110接收例如芯片使能信号cen、指令锁存使能信号cle、地址锁存使能信号ale、写入使能信号wen、及读出使能信号ren。

[0052]

而且,逻辑控制电路11根据接收到的信号,控制输入输出电路10及定序器15。

[0053]

状态寄存器12暂时保存例如数据的写入、读出、及删除动作中的状态信息sts,并向控制器110通知动作是否已正常结束。

[0054]

地址寄存器13暂时保存经由输入输出电路10从控制器110接收到的地址add。而且,地址寄存器13将行地址ra向行解码器19传输,并将列地址ca向列解码器22传输。

[0055]

指令寄存器14暂时保存经由输入输出电路10从控制器110接收到的指令cmd,并传输至定序器15。

[0056]

定序器15控制nand型高速缓冲存储器100整体的动作。更具体来说,定序器15根据指令寄存器14保存的指令cmd,控制例如状态寄存器12、就绪/忙碌电路16、电压产生电路17、行解码器19、读出放大器20、数据寄存器21、及列解码器22等,执行写入动作、读出动作、及删除动作等。

[0057]

就绪/忙碌电路16根据定序器15的动作状况,将就绪/忙碌信号r/bn发送至控制器110。

[0058]

电压产生电路17根据定序器15的控制,产生写入动作、读出动作、及删除动作所需的电压,并将该产生的电压供给至例如存储单元阵列18、行解码器19、及读出放大器20等。行解码器19及读出放大器20将从电压产生电路17供给的电压施加至存储单元阵列18内的存储单元晶体管。

[0059]

存储单元阵列18具备包含与行及列建立对应关系的非易失性的存储单元晶体管(以下,也表述为“存储单元”)的多个区块blk(blk0、blk1、

…

、bl(l-1))(l是2以上的整数)。各区块blk包含多个串单元su(su0、su1、su2、su3、

…

)。而且,各个串单元su包含多个nand串sr。此外,存储单元阵列18内的区块blk数及区块blk内的串单元su数为任意。关于存储单元阵列18的详情,将在下文进行叙述。

[0060]

行解码器19将行地址ra解码。行解码器19基于解码结果,选择区块blk中的任一个,进而选择任一个串单元su。然后,行解码器19对区块blk施加所需的电压。

[0061]

读出放大器20在读出动作时,将从存储单元阵列18读出的数据读出(sense)。而且,读出放大器20将读出数据rd发送至数据寄存器21。另外,读出放大器20在写入动作时,将写入数据wd发送至存储单元阵列18。

[0062]

数据寄存器21具备多个锁存电路。锁存电路保存写入数据wd及读出数据rd。例如,在写入动作中,数据寄存器21暂时保存从输入输出电路10接收到的写入数据wd,并发送至读出放大器20。另外,例如,在读出动作中,数据寄存器21暂时保存从读出放大器20接收到的读出数据rd,并发送至输入输出电路10。

[0063]

列解码器22在例如写入动作、读出动作、及删除动作时,将列地址ca解码,并根据解码结果选择数据寄存器21内的锁存电路。

[0064]

1.1.3关于存储单元阵列的构成

[0065]

接下来,利用图3对存储单元阵列18的构成进行说明。图3是区块blk0的电路图。区块blk1~blk3也具有相同的构成。

[0066]

如图3所示,区块blk0包含4个串单元su。另外,各个串单元su包含n个(n是自然数)nand串sr。

[0067]

nand串sr的各个包含例如8个存储单元晶体管mt(mt0~mt7)、选择晶体管st1、st2、及背栅极晶体管bt。存储单元晶体管mt具备包含控制栅极与电荷蓄积层的积层栅极,将数据非易失地保存。此外,存储单元晶体管mt的个数并不限于8个,也可为16个或32个、64个、128个等,它的数量不受限定。背栅极晶体管bt也与存储单元晶体管mt同样地,具备包含控制栅极与电荷蓄积层的积层栅极。但是,背栅极晶体管bt不是用来保存数据的,而是在数据的写入及删除时作为单纯的电流路径发挥功能。存储单元晶体管mt及背栅极晶体管bt以其电流路径串联连接的方式配置在选择晶体管st1、st2间。此外,背栅极晶体管bt设置在存储单元晶体管mt3与mt4之间。该串联连接的一端侧的存储单元晶体管mt7的电流路径连接于选择晶体管st1的电流路径的一端,另一端侧的存储单元晶体管mt0的电流路径连接于选择晶体管st2的电流路径的一端。

[0068]

串单元su0~su3各自的选择晶体管st1的栅极分别共通连接于选择栅极线sgs0~sgs3,选择晶体管st2的栅极分别共通连接于选择栅极线sgs0~sgs3。与此相对,位于同一区块blk0内的存储单元晶体管mt0~mt7的控制栅极分别共通连接于字线wl0~wl7,背栅极晶体管bt的控制栅极共通连接于背栅极线bg(区块blk0~blk3中,分别为bg0~bg3)。

[0069]

也就是说,字线wl0~wl7及背栅极线bg在同一区块blk0内的多个串单元su0~su3间共通连接,与此相对,选择栅极线sgd、sgs即使在同一区块blk0内,也针对每一串单元su0~su3而独立。

[0070]

另外,在存储单元阵列18内呈矩阵状配置的nand串sr中,位于同一行的nand串sr的选择晶体管st1的电流路径的另一端共通连接于任一条位线bl(bl0~bl(n-1))。也就是说,位线bl在多个区块blk间,共通连接nand串sr。另外,选择晶体管st2的电流路径的另一端共通连接于源极线sl。源极线sl例如在多个区块间共通连接nand串sr。

[0071]

数据的读出及写入是对任一区块blk的任一串单元su中的共通连接于任一条字线wl的多个存储单元晶体管mt一次性进行。将该单位称为“页面”。

oxide-nitride-oxide-silicon,金属-氧化物-氮化物-氧化物-硅)型晶体管。

[0083]

如果以其它方式描述所述背栅极晶体管层l1的构成,那么隧道绝缘层35c是以包围连结部36b的方式形成。电荷蓄积层35b是以包围隧道绝缘层35c的方式形成。阻挡绝缘层35a是以包围电荷蓄积层35b的方式形成。背栅极导电层31是以包围阻挡绝缘层35a、电荷蓄积层35b、隧道绝缘层35c、及连结部36b的方式形成。

[0084]

另外,如果以其它方式描述所述存储单元晶体管层l2的构成,那么隧道绝缘层35c是以包围柱状部36a的方式形成。电荷蓄积层35b是以包围隧道绝缘层35c的方式形成。阻挡绝缘层35a是以包围电荷蓄积层35b的方式形成。字线导电层33a~33d是以包围阻挡绝缘层35a、电荷蓄积层35b、隧道绝缘层35c、及柱状部36a的方式形成。

[0085]

如图4及图5所示,选择晶体管层l3具有导电层37a及37b。导电层37a及37b沿第二方向d2延伸。导电层37a形成在一柱状部36a的上层,导电层37b形成在另一柱状部36a的上层。

[0086]

导电层37a及37b由例如多晶硅形成。导电层37a作为选择晶体管st2的栅极(选择栅极线sgs)发挥功能,导电层37b作为选择晶体管st1的栅极(选择栅极线sgd)发挥功能。

[0087]

如图5所示,选择晶体管层l3具有孔38a及38b。孔38a及38b分别贯通导电层37a及37b。另外,孔38a及38b分别与存储孔34对准。

[0088]

如图5所示,选择晶体管层l3具备栅极绝缘层39a及39b、以及半导体层40a及40b。栅极绝缘层39a及39b分别以与孔38a及38b相接的方式形成。半导体层40a及40b分别以与栅极绝缘层39a及39b相接的方式,形成为沿相对于半导体衬底30的表面垂直的方向延伸的柱状。

[0089]

栅极绝缘层39a及39b由例如氧化硅(sio2)形成。半导体层40a及40b由例如多晶硅形成。

[0090]

如果以其它方式描述所述选择晶体管层l3的构成,那么栅极绝缘层39a是以包围柱状的半导体层40a的方式形成。导电层37a是以包围栅极绝缘层39a及半导体层40a的方式形成。另外,栅极绝缘层39b是以包围柱状的半导体层40b的方式形成。导电层37b是以包围栅极绝缘层39b及半导体层40b的方式形成。

[0091]

如图4及图5所示,配线层l4形成在选择晶体管层l3的上层。配线层l4具有源极线层41、插塞层42、及位线层43。

[0092]

源极线层41沿第二方向d2延伸。源极线层41是以与导电层37a的上表面相接的方式形成。插塞层42与导电层37b的上表面相接,且沿第三方向d3延伸。位线层43沿第一方向d1延伸。位线层43是以与插塞层42的上表面相接的方式形成。源极线层41、插塞层42、及位线层43由例如钨(w)等金属形成。源极线层41作为源极线sl发挥功能,位线层43作为位线bl发挥功能。

[0093]

此外,存储单元阵列18的构成也可为其它构成。例如,nand串sr也可为1根柱状而并非u字型的形状。关于存储单元阵列18的构成,例如记载在题为“三维积层非易失性半导体存储器(three dimensional stacked nonvolatile semiconductor memory)”的在2009年3月19日提出申请的美国专利申请12/407,403号中。另外,记载在题为“三维积层非易失性半导体存储器(three dimensional stacked nonvolatile semiconductor memory)”的在2009年3月18日提出申请的美国专利申请12/406,524号、题为“非易失性半导体存储装置

及其制造方法(non-volatile semiconductor storage device and method of manufacturing the same)”的在2010年3月25日提出申请的美国专利申请12/679,991号、题为“半导体存储器及其制造方法(semiconductor memory and method for manufacturing same)”的在2009年3月23日提出申请的美国专利申请12/532,030号中。这些专利申请的全部内容通过参照而引用在本技术的说明书中。

[0094]

1.1.4关于读出放大器及数据寄存器的构成

[0095]

接下来,利用图6对读出放大器20及数据寄存器21的构成进行说明。

[0096]

读出放大器20包含分别对应于各位线bl0~bl(n-1)而设置的读出放大器单元sau0~sau(n-1)。图6的例子是与1条位线bl对应的读出放大器单元sau的电路图。

[0097]

数据寄存器21包含分别对应于各读出放大器单元sau而设置的多个锁存电路xdl。锁存电路xdl暂时保存从读出放大器单元sau接收到的读出数据rd及从输入输出电路10接收到的写入数据wd。更具体来说,输入输出电路10所接收到的写入数据wd经由锁存电路xdl被传输至读出放大器单元sau。另外,从读出放大器单元sau接收到的读出数据rd经由锁存电路xdl被传输至输入输出电路10。

[0098]

此外,在本实施方式中,以将流经位线bl的电流读出的电流读出方式的读出放大器单元sau为例进行说明,但也可使用电压读出方式的读出放大器单元sau。在以下的说明中,将晶体管的源极或漏极的一个称为“晶体管的一端”,将源极或漏极的另一个称为“晶体管的另一端”。

[0099]

如图6所示,读出放大器单元sau经由bl连结电路bhu而连接于位线bl。另外,读出放大器单元sau经由dbus开关电路dsw而连接于数据寄存器21内的锁存电路xdl。

[0100]

bl连结电路bhu包含高耐压n通道mos(metal oxide semiconductor,金属氧化物半导体)晶体管50。晶体管50的一端与对应的位线bl连接,晶体管50的另一端经由读出放大器线sal而连接于读出放大器单元sau。对晶体管50的栅极输入信号bls。信号bls是用来控制位线bl与读出放大器单元sau的电连接的信号。

[0101]

读出放大器单元sau包含读出电路sa、锁存电路sdl、及预充电电路lpc。

[0102]

读出电路sa包含低耐压n通道mos晶体管51~60、低耐压p通道mos晶体管61、及电容元件62。

[0103]

对晶体管51的栅极输入信号blc。晶体管51的一端连接于读出放大器线sal,晶体管51的另一端连接于节点scom。晶体管51用来将对应的位线bl箝位至与信号blc对应的电位。

[0104]

对晶体管52的栅极输入信号blx。晶体管52的一端连接于节点scom,晶体管52的另一端连接于节点ssrc。

[0105]

晶体管53的栅极连接于节点inv_s。晶体管53的一端连接于节点ssrc,晶体管53的另一端连接于节点srcgnd。对节点srcgnd施加例如接地电压vss。

[0106]

晶体管61的栅极连接于节点inv_s。对晶体管61的一端施加电源电压vddsa,晶体管61的另一端连接于节点ssrc。

[0107]

对晶体管54的栅极输入信号xxl。晶体管54的一端连接于节点scom,晶体管54的另一端连接于节点sen。

[0108]

对晶体管55的栅极输入信号hll。对晶体管55的一端施加电压vsenp,晶体管55的

另一端连接于节点sen。

[0109]

电容元件62的一电极连接于节点sen,对电容元件62的另一电极输入时钟信号clk。

[0110]

晶体管57的栅极连接于节点sen。晶体管57的一端连接于晶体管58的一端,对晶体管57的另一端输入时钟信号clk。晶体管57作为读出节点sen的电压的读出晶体管发挥功能。

[0111]

对晶体管58的栅极输入信号stb。晶体管58的另一端连接于总线lbus。

[0112]

对晶体管56的栅极输入信号blq。晶体管56的一端连接于节点sen,晶体管56的另一端连接于总线lbus。例如,在经由总线lbus对节点sen进行充电的情况下,晶体管56设为接通状态。

[0113]

晶体管59的栅极连接于总线lbus。晶体管59的一端连接于晶体管60的一端,对晶体管59的另一端施加电压vlsa。电压vlsa也可为例如接地电压vss。

[0114]

对晶体管60的栅极输入信号lsl。晶体管60的另一端连接于节点sen。

[0115]

在写入数据时,读出电路sa根据锁存电路sdl的保存数据控制位线bl。

[0116]

锁存电路sdl包含低耐压n通道mos晶体管70~73及低耐压p通道mos晶体管74~77。

[0117]

对晶体管70的栅极输入信号stl。晶体管70的一端连接于总线lbus,晶体管70的另一端连接于节点lat_s。

[0118]

对晶体管71的栅极输入信号sti。晶体管71的一端连接于总线lbus,晶体管71的另一端连接于节点inv_s。

[0119]

晶体管72的栅极连接于节点inv_s。晶体管72的一端接地(连接于接地电压配线),晶体管72的另一端连接于节点lat_s。

[0120]

晶体管73的栅极连接于节点lat_s。晶体管73的一端接地,晶体管73的另一端连接于节点inv_s。

[0121]

晶体管74的栅极连接于节点inv_s。晶体管74的一端连接于节点lat_s,晶体管74的另一端连接于晶体管76的一端。

[0122]

晶体管75的栅极连接于节点lat_s。晶体管75的一端连接于节点inv_s,晶体管75的另一端连接于晶体管77的一端。

[0123]

对晶体管76的栅极输入信号sll。对晶体管76的另一端施加电源电压vddsa。

[0124]

对晶体管77的栅极输入信号sli。对晶体管77的另一端施加电源电压vddsa。

[0125]

在锁存电路sdl中,由晶体管72及74构成第一反相器,由晶体管73及75构成第二反相器。锁存电路sdl以节点lat_s保存数据,且以节点inv_s保存其反转数据。

[0126]

此外,读出放大器单元sau例如也可具备具有与锁存电路sdl相同的构成的多个锁存电路,作为各个存储单元晶体管mt保存2位以上的数据的多值动作用锁存电路。在该情况下,锁存电路以能够收发数据的方式连接于总线lbus。

[0127]

预充电电路lpc对总线lbus进行预充电。预充电电路lpc包含例如低耐压n通道mos晶体管80。对晶体管80的栅极输入信号lbp。晶体管80的一端连接于总线lbus,对晶体管80的另一端施加电压vhlb。而且,预充电电路lpc通过对总线lbus传输电压vhlb而对总线lbus进行预充电。

[0128]

dbus开关电路dsw将总线lbus与总线dbus连接。也就是说,dbus开关电路dsw将读出放大器单元sau与数据寄存器21内的锁存电路xdl连接。dbus开关电路dsw包含例如低耐压n通道mos晶体管81。对晶体管81的栅极输入信号dbs。晶体管81的一端连接于总线lbus,晶体管81的另一端经由总线dbus而连接于数据寄存器21内的锁存电路xdl。

[0129]

此外,所述构成的bl连结电路bhu、读出放大器单元sau、及dbus开关电路dsw中的各种信号由例如定序器15赋予。

[0130]

1.2关于读出放大器及数据寄存器的配置

[0131]

接下来,利用图7对读出放大器20及数据寄存器21的配置进行说明。图7的例子表示设置在半导体衬底上的bl连结电路bhu、读出放大器单元sau及数据寄存器21。存储单元阵列18介隔层间绝缘膜设置在它们的上方。

[0132]

在本实施方式中,将和1条位线bl对应的读出放大器单元sau、与连接于该读出放大器单元sau的数据寄存器21的组合表述为“读出组gp”。另外,本实施方式的bl连结电路与2条位线bl对应,例如,将与位线bl0及bl1对应的bl连结电路表述为“bl连结电路bhu_0_1”。其它bl连结电路bhu也同样。进而,将1个bl连结电路bhu、及连接于该bl连结电路bhu的2个读出组gp的组合表述为“连接单元ut”。连接单元ut(bl连结电路bhu)对应于(n-1)个位线bl而设置m个(m是n/2以上的整数)。m个连接单元ut在半导体衬底上配置成例如矩阵状。

[0133]

另外,在以下的说明中,将与位线bl0~bl(n-1)对应的电路、配线等加以区别的情况下,对参照符号的末尾追加

““

与位线bl对应的数字

””

而记载。例如,像与位线bl0对应的读出组gp0、读出电路sa0、读出放大器线sal0、总线lbus0、总线dbus0、dbus开关电路dsw0、锁存电路xdl0或晶体管50_0、数据寄存器21_0这样表述。

[0134]

如图7所示,在本实施方式中,与各位线bl对应的读出放大器单元sau及数据寄存器21分散配置。更具体来说,连接单元ut0包含例如沿着第一方向d1依次配置的读出组gp0的数据寄存器21_0(设置着数据寄存器21_0的区域)及读出放大器单元sau0(设置着读出放大器单元sau0的区域)、bl连结电路bhu_0_1(设置着bl连结电路bhu_0_1的区域)、以及读出组gp1的读出放大器单元sau1(设置着读出放大器单元sau1的区域)及数据寄存器21_1(设置着数据寄存器21_1的区域)。也就是说,在连接单元ut0中,以bl连结电路bhu_0_1为中心,在bl连结电路bhu_0_1的两侧配置读出放大器单元sau0及sau1。换句话说,在读出放大器单元sau0及sau1之间配置对应的bl连结电路bhu_0_1。而且,在读出放大器单元sau0及sau1的外侧配置着数据寄存器21_0及21_1。

[0135]

位线bl0连接于bl连结电路bhu_0_1内的接触插塞cp1_0。接触插塞cp1贯通存储单元阵列18,将设置在存储单元阵列18的上方的配线、与设置在存储单元阵列18的下方的配线连接。接触插塞cp1_0经由晶体管50_0(未图示)及读出放大器线sal0而连接于读出放大器单元sau0的读出电路sa0。读出放大器单元sau0的读出电路sa0经由总线lbus0、dbus开关电路dsw0、及总线dbus0而连接于数据寄存器21_0的锁存电路xdl0。总线dbus针对每一读出放大器单元sau而设置,分别将对应的dbus开关电路dsw与数据寄存器21的锁存电路xdl连接。

[0136]

位线bl1与位线bl0同样地,连接于bl连结电路bhu_0_1的接触插塞cp1_1。而且,接触插塞cp1_1经由晶体管50_1(未图示)及读出放大器线sal1而连接于读出放大器单元sau1的读出电路sa1。读出放大器单元sau1的读出电路sa1经由总线lbus1、dbus开关电路dsw1、

及总线dbus1而连接于数据寄存器21_1的锁存电路xdl1。

[0137]

其次,连接单元ut1中的bl连结电路bhu_2_3、读出放大器单元sau2及sau3、以及数据寄存器21_2及21_3的配置与连接单元ut0相同。

[0138]

位线bl2连接于bl连结电路bhu_2_3的接触插塞cp1_2。而且,接触插塞cp1_2经由晶体管50_2(未图示)及读出放大器线sal2而连接于读出放大器单元sau2的读出电路sa2。读出放大器单元sau2的读出电路sa经由总线lbus2、dbus开关电路dsw2、及总线dbus2而连接于数据寄存器21_2的锁存电路xdl2。

[0139]

位线bl3与位线bl0同样地,连接于bl连结电路bhu_2_3的接触插塞cp1_3。而且,接触插塞cp1_3经由晶体管50_3(未图示)及读出放大器线sal3而连接于读出放大器单元sau3的读出电路sa3。读出放大器单元sau3的读出电路sa3经由总线lbus3、dbus开关电路dsw3、及总线dbus3而连接于数据寄存器21_3的锁存电路xdl3。

[0140]

此外,1个连接单元ut所对应的2条位线bl可任意地设定。例如,也可为连接单元ut0与位线bl0及bl2对应,且连接单元ut1与位线bl1及bl3对应。

[0141]

进而,在读出组gp内,读出放大器单元sau与数据寄存器21的配置可任意地设定。例如,在连接单元ut0的情况下,也可沿着第一方向d1依次排列有读出放大器单元sau0、数据寄存器21_0、bl连结电路bhu_0_1、数据寄存器21_1、读出放大器单元sau1。

[0142]

1.3关于存储单元阵列与读出放大器的连接

[0143]

接下来,利用图8及图9对存储单元阵列18与读出放大器20的连接进行说明。图8是表示存储单元阵列18与设置它的下方的连接单元ut0的连接关系的俯视图。图8中,上图是存储单元阵列18的俯视图,表示设置在存储单元阵列18的上方的位线bl。另外,下图表示配置在存储单元阵列18的下方、即周边电路区域pc的连接单元ut0的俯视图。图9是沿着图8的第一方向d1的剖视图,尤其表示看到位线bl0的部分的截面构成。

[0144]

以下,将设置在存储单元阵列18的上方的位线bl表述为“上部位线blu”,将设置在存储单元阵列18的下方的位线bl表述为“下部位线bll”。上部位线blu、下部位线bll、及接触插塞cp1相当于直到目前为止所说明的位线bl。也就是说,位线bl包含上部位线blu、下部位线bll、及连接两者的接触插塞cp1。

[0145]

如图8所示,在存储单元阵列18的上方,沿着第一方向d1设置着上部位线blu(blu0~blu(n-1))。在存储单元阵列18内,对应于m个连接单元ut而设置着m个连接部rcu。在图8的例子中,分别示出与连接单元ut0及ut1对应的连接部rcu0及rcu1。此外,在图8的例子中,在连接部rcu0的区域内,设置着接触插塞cp1_0及cp1_1。而且,上部位线blu0经由接触插塞cp1_0而连接于下部位线bll0,上部位线blu1经由接触插塞cp1_1而连接于下部位线bll1。此外,连接部rcu0中的接触插塞cp1_0及cp1_1的配置只要为分别可与位线bl0及bl1连接的位置,便可任意地设定。例如,也可沿着与第一方向d1及第二方向d2不同的方向配置,还可沿着第二方向d2配置。

[0146]

在bl连结电路bhu_0_1的区域中,下部位线bll0经由接触插塞cp2_0而连接于晶体管50_0的一端。而且,晶体管50_0的另一端经由接触插塞cp3_0而连接于读出放大器线sal0。

[0147]

在读出放大器单元sau0的区域中,读出放大器线sal0经由接触插塞cp4_0而连接于读出电路sa0内的晶体管50_0的一端。读出电路sa0经由接触插塞cp5_0而连接于总线

lbus0。总线lbus0经由接触插塞cp6_0而连接于dbus开关电路dsw0的一端。dbus开关电路dsw0的另一端经由接触插塞cp7_0而连接于总线dbus0。

[0148]

在数据寄存器21_0的区域中,总线dbus0经由接触插塞cp8_0而连接于锁存电路xdl0。

[0149]

另外,连接单元ut0中的接触插塞cp2_1、cp3_1、cp4_1、cp5_1、cp6_1、cp7_1、及cp8_1的连接分别与接触插塞cp2_0、cp3_0、cp4_0、cp5_0、cp6_0、cp7_0及cp8_0相同。

[0150]

更具体来说,在bl连结电路bhu_0_1的区域中,下部位线bll1经由接触插塞cp2_1而连接于晶体管50_1的一端。而且,晶体管50_1的另一端经由接触插塞cp3_1而连接于读出放大器线sal1。

[0151]

在读出放大器单元sau1的区域中,读出放大器线sal1经由接触插塞cp4_1而连接于读出电路sa1内的晶体管50_1的一端。读出电路sa1经由接触插塞cp5_1而连接于总线lbus1。总线lbus1经由接触插塞cp6_1而连接于dbus开关电路dsw1的一端。dbus开关电路dsw1的另一端经由接触插塞cp7_1而连接于总线dbus1。

[0152]

在数据寄存器21_1的区域中,总线dbus1经由接触插塞cp8_1而连接于锁存电路xdl1。

[0153]

接下来,对存储单元阵列18及读出放大器20的截面构成进行说明。图9的例子表示连接单元ut0中与位线bl0对应的晶体管50_0及读出放大器单元sau0的一部分(晶体管51_0),省略连接单元ut0内的其它电路等。

[0154]

如图9所示,在半导体衬底30的表面区域设置着高耐压晶体管用的阱区域90a及低耐压晶体管用的阱区域90b。阱区域90a包含n型阱91a及p型阱92a,阱区域90b包含n型阱91b及p型阱92b。在p型阱92a上形成着例如晶体管50_0。另外,在p型阱92b上形成着例如晶体管51_0。这些晶体管50_0及51_0包含作为源极或漏极发挥功能的n

+

扩散层93、及栅极电极94。

[0155]

晶体管50_0的一端经由接触插塞cp2_0而连接于作为下部位线bll0发挥功能的配线层95。晶体管50_0的另一端经由接触插塞cp3_0而连接于作为读出放大器线sal0发挥功能的配线层95。

[0156]

晶体管51_0的一端经由接触插塞cp4_0而连接于作为读出放大器线sal0发挥功能的配线层95。晶体管51_0的另一端经由接触插塞cp9_0而连接于读出放大器单元sau0内的作为节点scom发挥功能的配线层95。

[0157]

在半导体衬底30上形成着层间绝缘膜96,介隔层间绝缘膜96而在配线层95的上方形成着存储单元阵列18。具体来说,沿着第三方向d3依次设置着背栅极线bg、多条字线wl、及选择栅极线sgs或sgd。而且,呈u字型设置着成为nand串sr的电流路径的半导体层。nand串sr的一端例如连接于上部位线blu0,另一端连接于源极线sl。

[0158]

上部位线blu0经由贯通存储单元阵列18的接触插塞cp1_0而连接于下部位线bll0。

[0159]

此外,在本实施方式中,设为在存储单元阵列18的下方形成着1层配线层95的构造,但也可设为形成着2层配线层的配线构造,还可为3层以上的配线构造。进而,接触插塞cp1也可为配线形状的线接点。

[0160]

1.4关于写入动作

[0161]

接下来,简略地对写入动作进行说明。以下,对写入动作与就绪/忙碌信号r/bn的

关系进行说明。

[0162]

控制器110在对nand型高速缓冲存储器100发送写入命令(写入指令、地址add、写入数据wd)的情况下,将通常的写入指令或高速缓冲写入指令的任一个发送至nand型高速缓冲存储器100。

[0163]

nand型高速缓冲存储器100在接收到通常的写入指令的情况下,执行通常的写入动作。在通常的写入动作中,在正在将写入数据wd写入至存储单元阵列18的期间,信号r/bn设为“l”电平(忙碌状态)。

[0164]

另一方面,nand型高速缓冲存储器100在接收到高速缓冲写入指令的情况下,执行高速缓冲写入动作。对存储单元晶体管mt的写入与接收到通常的写入指令的情况相同,但信号r/bn的“l”电平的期间不同。在高速缓冲写入动作中,在从写入动作开始起至数据寄存器21结束写入数据wd向读出放大器20的传输为止的期间,信号r/bn设为“l”电平。数据寄存器21经由输入输出电路10而从控制器110接收写入数据wd。而且,数据寄存器21经由总线dbus而向读出放大器20传输写入数据wd。nand型高速缓冲存储器100当从数据寄存器21向读出放大器20的写入数据wd的传输结束而数据寄存器21内的锁存电路xdl变得能够使用时,在对存储单元阵列18的写入动作中,也将“h”电平(就绪状态)的信号r/bn发送至控制器110,而设为能够接收下一指令的状态。

[0165]

此外,高速缓冲写入动作例如记载在题为“输出内部动作的通过/失败结果的半导体集成电路(semiconductor integrated circuit adapted to output pass/fail results of internal operations)”的在2002年12月13日提出申请的美国专利申请10/318,167号中。该专利申请的全部内容通过参照而引用在本技术的说明书中。

[0166]

1.5关于读出动作

[0167]

接下来,简略地对读出动作进行说明。读出动作大致包含页面读出与高速缓冲读出。页面读出是将数据从存储单元晶体管mt读出至数据寄存器21、也就是锁存电路xdl的动作,高速缓冲读出是将数据从数据寄存器21读出至控制器110的动作。

[0168]

更具体来说,在页面读出中,读出放大器20将对应的存储单元晶体管mt的数据读出,并存储到例如锁存电路sdl中。然后,读出放大器20将存储在锁存电路sdl中的读出数据rd经由总线dbus而发送至数据寄存器21的锁存电路xdl。在高速缓冲读出中,将存储在数据寄存器21中的读出数据rd经由输入输出电路10而发送至控制器110。

[0169]

1.6关于本实施方式的效果

[0170]

如果为本实施方式的构成,那么能够提高处理能力。以下,对本效果进行详细叙述。

[0171]

例如,将页面读出中从存储单元阵列18(存储单元晶体管mt)向数据寄存器21传输数据的期间设为tr。这样一来,期间tr包含将数据从存储单元阵列18读出至读出放大器20的读出期间t1、及从读出放大器20向数据寄存器21传输数据的数据传输期间t2。例如,在多个读出放大器单元sau与多个锁存电路xdl通过共通的总线dbus连接的情况下,数据被串行发送至多个锁存电路xdl(多次进行数据传输),因此,数据传输期间t2变长。另外,例如,如果读出放大器单元sau与锁存电路xdl之间的距离较远,那么总线dbus变长,而总线dbus的配线电阻及配线间电容增加。由此,总线dbus的rc(resistance-capacitance,电阻-电容)时间常数变大。因此,总线dbus的充放电期间变长,而数据传输期间t2变长。另外,导致芯片

面积增加,因此,无法增大读出放大器单元sau或数据寄存器21内的晶体管尺寸(无法提高驱动能力)。因此,无法缩短总线dbsu的充放电期间而数据传输期间t2变长。

[0172]

与此相对,如果为本实施方式的构成,那么可在bl连结电路bhu的两侧配置连接于bl连结电路的读出放大器单元sau。也就是说,可在2个读出放大器单元sau之间配置对应的bl连结电路bhu。进而,可与读出放大器单元sau相邻地配置对应的数据寄存器21、也就是锁存电路xdl。而且,可通过专用地设置的总线dbus将1个读出放大器单元sau与1个锁存电路xdl连接。由此,可防止数据经由1条总线dbus串行发送至多个锁存电路xdl。另外,可缩短总线dbus的配线,因此可降低rc时间常数,而可缩短总线dbus的充放电期间。因此,可缩短数据传输期间t2,而可提高半导体存储装置的处理能力。

[0173]

进而,可缩短bl连结电路与读出放大器单元sau的距离,因此可抑制位线bl的充放电期间增加。因此,可抑制读出期间t1增加,而可提高半导体存储装置的处理能力。

[0174]

进而,在写入动作中,与页面读出同样地,可缩短从数据寄存器21向读出放大器单元sau传输数据的数据传输期间。因此,可提高半导体存储装置的处理能力。

[0175]

2.第二实施方式

[0176]

接下来,对第二实施方式进行说明。在第二实施方式中,对与第一实施方式不同的读出放大器20及数据寄存器21的配置进行说明。以下,仅对与第一实施方式的不同点进行说明。

[0177]

2.1关于读出放大器及数据寄存器的配置

[0178]

利用图10对读出放大器20及数据寄存器21的配置进行说明。图10的例子为简化说明而仅表示连接单元ut0。

[0179]

在本实施方式中,将和2条位线bl对应的2个读出放大器单元sau、与2个数据寄存器21的组合设为1个读出组gp。例如,将与位线bl0及bl1对应的读出放大器单元sau0及sau1、以及数据寄存器21_0及21_1的组合设为读出组gp01。另外,将与位线bl2及bl3对应的读出放大器单元sau2及sau3、以及数据寄存器21_2及21_3的组合设为读出组gp23。此外,1个读出组gp中包含的读出放大器单元sau及数据寄存器21也可为3个以上。

[0180]

如图10所示,连接单元ut0沿着第一方向d1依次排列有读出组gp01、与位线bl0~bl3对应的bl连结电路bhu_0_3、读出组gp23。更具体来说,沿着第一方向d1,依次排列有数据寄存器21_1、数据寄存器21_0、读出放大器单元sau1、读出放大器单元sau0、bl连结电路bhu_0_3、读出放大器单元sau2、读出放大器单元sau3、数据寄存器21_2、及数据寄存器21_3。也就是说,在连接单元ut0中,以bl连结电路bhu_0_3为中心,在bl连结电路bhu_0_1的两侧分别配置2个读出放大器单元sau0及sau1、以及读出放大器单元sau2及sau3。换句话说,在2个读出放大器单元sau0及sau1与2个读出放大器单元sau2及sau3之间配置对应的bl连结电路bhu_0_3。而且,在2个读出放大器单元sau0及sau1的更外侧配置着数据寄存器21_0及21_1,在2个读出放大器单元sau2及sau3的更外侧配置着数据寄存器21_2及21_3。此外,读出组gp内的读出放大器单元sau及数据寄存器21的配置可任意地设定。例如,也可沿着第一方向d1依次排列有读出放大器单元sau0、读出放大器单元sau1、bl连结电路bhu_0_3、读出放大器单元sau3、读出放大器单元sau2。另外,例如,也可沿着第一方向d1依次排列有读出放大器单元sau0、读出放大器单元sau2、bl连结电路bhu_0_3、读出放大器单元sau1、读出放大器单元sau3。数据寄存器21也同样。

[0181]

2.2关于本实施方式的效果

[0182]

如果为本实施方式的构成,那么可获得与第一实施方式相同的效果。

[0183]

进而,如果为本实施方式的构成,那么bl连结电路bhu与4条位线bl对应,因此,可抑制因bl连结电路区域增加而导致芯片面积增加。

[0184]

3.第三实施方式

[0185]

接下来,对第三实施方式进行说明。在第三实施方式中,对未设置bl连结电路的区域的情况进行说明。以下,仅对与第一及第二实施方式的不同点进行说明。

[0186]

3.1关于读出放大器及数据寄存器的配置

[0187]

利用图11对读出放大器20及数据寄存器21的配置进行说明。

[0188]

在本实施方式中,将和1条位线bl对应的读出放大器单元sau与数据寄存器21的组合设为1个读出组gp。另外,本实施方式将bl连结电路区域废除。例如,第一及第二实施方式中包含于bl连结电路bhu的晶体管50也可包含于读出电路sa。

[0189]

如图11所示,连接单元ut0对应于位线bl0及bl1而包含读出组gp01及gp23。更具体来说,沿着第一方向d1,依次排列有读出组gp0的数据寄存器21_0及读出放大器单元sau0、以及读出组gp1的读出放大器单元sau1及数据寄存器21_1。也就是说,在连接单元ut0中,在相邻的2个读出放大器单元sau0及sau1的外侧分别配置着数据寄存器21_0及21_1。

[0190]

连接单元ut1也与连接单元ut0同样地,包含沿着第一方向d1依次排列的读出组gp2的数据寄存器21_2及读出放大器单元sau2、以及读出组gp3的读出放大器单元sau3及数据寄存器21_3。

[0191]

此外,1个读出组gp中包含的读出放大器单元sau及数据寄存器21也可为2个以上。

[0192]

3.2关于本实施方式的效果

[0193]

如果为本实施方式的构成,那么可获得与第一及第二实施方式相同的效果。

[0194]

4.第四实施方式

[0195]

接下来,对第四实施方式进行说明。在第四实施方式中,对与第一实施方式不同的dbus开关电路dsw的构成表示9个例子。以下,仅对与第一至第三实施方式的不同点进行说明。

[0196]

4.1第一例

[0197]

首先,利用图12对第四实施方式的第一例进行说明。

[0198]

如图12所示,dbus开关电路dsw包含低耐压p通道mos晶体管200。

[0199]

对晶体管200的栅极输入信号dbs的反转信号即信号dbsn。晶体管200的一端连接于总线lbus,晶体管200的另一端连接于总线dbus。

[0200]

4.2第二例

[0201]

其次,利用图13对第四实施方式的第二例进行说明。

[0202]

如图13所示,dbus开关电路dsw包含低耐压n通道mos晶体管201及低耐压p通道mos晶体管202。

[0203]

对晶体管201的栅极输入信号dbs,对晶体管202的栅极输入信号dbsn。晶体管201及202的一端连接于总线lbus,晶体管201及202的另一端连接于总线dbus。

[0204]

4.3第三例

[0205]

其次,利用图14对第四实施方式的第三例进行说明。

[0206]

如图14所示,dbus开关电路dsw包含低耐压n通道mos晶体管203及204。

[0207]

晶体管203的栅极连接于总线lbus。晶体管203的一端连接于总线dbus,晶体管203的另一端连接于晶体管204的一端。对晶体管204的栅极输入信号dbs。晶体管204的另一端接地。

[0208]

dbus开关电路dsw当信号dbs及总线lbus为“h”电平时,将总线dbus放电而设为“l”电平。

[0209]

4.4第四例

[0210]

其次,利用图15对第四实施方式的第四例进行说明。

[0211]

如图15所示,dbus开关电路dsw包含低耐压p通道mos晶体管205及206。

[0212]

对晶体管205的栅极输入信号dbsn。对晶体管205的一端施加电源电压(连接于电源电压配线),晶体管205的另一端连接于晶体管206的一端。晶体管204的栅极连接于总线lbus,晶体管204的另一端连接于总线dbus。

[0213]

dbus开关电路dsw当信号dbs及总线lbus为“l”电平时,对总线dbus进行充电而设为“h”电平。

[0214]

4.5第五例

[0215]

其次,利用图16对第四实施方式的第五例进行说明。

[0216]

如图16所示,dbus开关电路dsw包含低耐压p通道mos晶体管207及208、以及低耐压n通道mos晶体管209及210。

[0217]

对晶体管207的栅极输入信号dbsn。对晶体管207的一端施加电源电压。晶体管205的另一端连接于晶体管208的一端。晶体管208及209的栅极连接于总线lbus。晶体管208的另一端及晶体管209的一端连接于总线dbus。晶体管209的另一端连接于晶体管210的一端。对晶体管210的栅极输入信号dbs,晶体管210的另一端接地。晶体管208及209作为反相器发挥功能。

[0218]

dbus开关电路dsw当信号dbs为“h”电平(信号dbsn为“l”电平)时,将总线lbus的反转信号发送至总线dbus。

[0219]

4.6第六例

[0220]

其次,利用图17对第四实施方式的第六例进行说明。

[0221]

如图17所示,dbus开关电路dsw包含低耐压n通道mos晶体管211~214。

[0222]

晶体管211的栅极连接于总线lbus及晶体管213的一端。晶体管211的一端连接于晶体管213的栅极及总线dbus。晶体管211的另一端连接于晶体管212的一端。对晶体管212的栅极输入信号dbs1,晶体管212的另一端接地。晶体管213的另一端连接于晶体管214的一端。对晶体管214的栅极输入信号dbs2,晶体管214的另一端接地。

[0223]

dbus开关电路dsw当信号dbs1为“h”电平时,如果总线lbus设为“h”电平,那么将总线dbus放电而设为“l”电平。另外,dbus开关电路dsw当信号dbs2为“h”电平时,如果总线dbus设为“h”电平,那么将总线lbus放电而设为“l”电平。

[0224]

4.7第七例

[0225]

其次,利用图18对第四实施方式的第七例进行说明。

[0226]

如图18所示,dbus开关电路dsw包含低耐压p通道mos晶体管215~218。

[0227]

对晶体管215的栅极输入信号dbsn1。对晶体管215的一端施加电源电压,晶体管

215的另一端连接于晶体管216的一端。对晶体管217的栅极输入信号dbsn2。对晶体管217的一端施加电源电压,晶体管217的另一端连接于晶体管218的一端。晶体管216的栅极连接于总线lbus及晶体管218的另一端。晶体管216的另一端连接于晶体管218的栅极及总线dbus。

[0228]

dbus开关电路dsw当信号dbsn1为“l”电平时,如果总线lbus设为“l”电平,那么对总线dbus进行充电而设为“h”电平。另外,dbus开关电路dsw当信号dbsn2为“l”电平时,如果总线dbus设为“l”,那么对总线lbus进行充电而设为“h”电平。

[0229]

4.8第八例

[0230]

其次,利用图19对第四实施方式的第八例进行说明。

[0231]

如图19所示,dbus开关电路dsw包含低耐压p通道mos晶体管219~222、以及低耐压n通道mos晶体管223~226。

[0232]

对晶体管219的栅极输入信号dbsn1。对晶体管219的一端施加电源电压,晶体管219的另一端连接于晶体管220的一端。晶体管220及223的栅极连接于总线lbus。晶体管220的另一端及晶体管223的一端连接于总线dbus。晶体管223的另一端连接于晶体管224的一端。对晶体管224的栅极输入信号dbs1,晶体管224的另一端接地。晶体管220及223作为第一反相器发挥功能。

[0233]

对晶体管221的栅极输入信号dbsn2。对晶体管221的一端施加电源电压,晶体管221的另一端连接于晶体管222的一端。晶体管222及225的栅极连接于总线dbus。晶体管222的另一端及晶体管225的一端连接于总线lbus,晶体管225的另一端连接于晶体管226的一端。对晶体管226的栅极输入信号dbs2,晶体管226的另一端接地。晶体管222及225作为第二反相器发挥功能。

[0234]

dbus开关电路dsw当信号dbs1为“h”电平(信号dbsn1为“l”电平)时,将总线lbus的反转信号发送至总线dbus。另外,dbus开关电路dsw当信号dbs2为“h”电平(信号dbsn2为“l”电平)时,将总线dbus的反转信号发送至总线ldbus。

[0235]

4.9第九例

[0236]

其次,利用图20对第四实施方式的第九例进行说明。

[0237]

如图20所示,dbus开关电路dsw包含锁存电路。dbus开关电路dsw包含低耐压p通道mos晶体管227~230、以及低耐压n通道mos晶体管231~236。

[0238]

对晶体管231的栅极输入信号dbs1,晶体管231的一端连接于总线lbus。晶体管231的另一端连接于晶体管232、233、及234的一端。对晶体管232的栅极输入信号dbs2,晶体管232的另一端连接于总线dbus。对晶体管233的栅极输入信号dbs3。晶体管233的另一端连接于节点n1。对晶体管234的栅极输入信号dbs4。晶体管234的另一端连接于节点n2。

[0239]

对晶体管227的栅极输入信号dbs5。对晶体管227的一端施加电源电压,晶体管227的另一端连接于晶体管228的一端。晶体管228的栅极连接于节点n2,晶体管228的另一端连接于节点n1。晶体管235的栅极连接于节点n2。晶体管235的一端连接于节点n1,晶体管235的另一端接地。晶体管228及235作为第一反相器发挥功能。

[0240]

对晶体管229的栅极输入信号dbs6。对晶体管229的一端施加电源电压,晶体管229的另一端连接于晶体管230的一端。晶体管230的栅极连接于节点n1,晶体管230的另一端连接于节点n2。晶体管236的栅极连接于节点n1。晶体管236的一端连接于节点n2,晶体管236的另一端接地。晶体管230及236作为第二反相器发挥功能。

[0241]

dbus开关电路dsw以节点n1保存数据,且以节点n2保存其反转数据。例如,在将总线lbus的数据传输至总线dbus的情况下,首先,信号dbs1及dbs3设为“h”电平,将总线lbus的数据保存在节点n1。然后,信号dbs1设为“l”电平,且信号dbs2设为“h”电平时,节点n1保存的数据被传输至总线dbus。

[0242]

此外,锁存电路的构成并不限定于本例。只要为可获得相同特性的构成,则可任意地设定。

[0243]

4.10关于本实施方式的效果

[0244]

可将本实施方式的构成应用于第一至第三实施方式。由此,可获得与第一至第三实施方式相同的效果。

[0245]

5.变化例等

[0246]

所述实施方式的半导体存储装置包含:连结电路(bhu_0_1),设置在半导体衬底(30)上,且包含连接于第一位线(bl0)的第一电路(晶体管50_0)及连接于第二位线(bl1)的第二电路(晶体管50_1);第一组(gp0),包含连接于第一电路的第一读出放大器电路(sau0)、及经由第一数据总线(dbus0)而连接于第一读出放大器电路的第一数据寄存器(21_0);第二组(gp1),包含连接于第二电路的第二读出放大器电路(sau1)、及经由第二数据总线(dbus1)而连接于所述第二读出放大器电路的第二数据寄存器(21_1);及存储单元阵列(18),介隔层间绝缘膜(96)设置在连结电路及第一及第二组的上方,且包含连接于第一位线的第一存储单元及连接于所述第二位线的第二存储单元。沿着与半导体衬底平行的第一方向,依次排列有第一组、连结电路、第二组。

[0247]

通过应用所述实施方式,可提供一种能够提高处理能力的半导体存储装置。

[0248]

此外,实施方式并不限定于所述说明的方式,可进行各种变化。

[0249]

5.1第一变化例

[0250]

例如,在所述实施方式中,nand串sr也可为1根柱状而并非u字型的形状。利用图21对nand串sr的一例进行说明。此外,图21的例子省略层间绝缘膜。

[0251]

如图21所示,nand串sr设置在设置于半导体衬底30上的周边电路区域pc的上方。更具体来说,在周边电路区域pc之上,介置层间绝缘膜而设置着作为源极线sl发挥功能的源极线层41。而且,在源极线层41的上方,分别介隔层间绝缘膜而依次积层有选择栅极线sgs、连接于存储单元晶体管mt0~mt7的字线wl0~wl7、及作为选择栅极线sgd发挥功能的10层配线层33。

[0252]

而且,形成着贯通10层配线层33并到达至配线层44的柱状的半导体层36。在半导体层36的侧面,依次形成着隧道绝缘层35c、电荷蓄积层35b、及阻挡绝缘层35a。半导体层36作为nand串sr的电流路径发挥功能,成为供形成各晶体管的通道的区域。而且,半导体层36的上端经由插塞层42而连接于沿第一方向d1延伸的位线层43。位线层43作为位线bl发挥功能。另外,设置着与源极线层41相接且沿第二方向d2延伸的源极线接点li。源极线接点li沿着第二方向d2具有例如线形状。在2个源极线接接点li之间,例如配置着1个串单元su。源极线接点li使用例如多晶硅。

[0253]

5.2其它变化例

[0254]

例如,第一实施方式及第四实施方式的各例中所说明的dbus开关电路dsw的构成也可在可能的范围内进行组合。

[0255]

进而,总线dbus也可使用例如像dbus开关电路dsw那样的开关电路而进行分割。

[0256]

进而,所述实施方式中的“连接”也包含在中间介置例如晶体管或电阻等其它某个构件而间接地连接的状态。

[0257]

此外,在与本发明相关的各实施方式中,也可如下述般。例如,存储单元晶体管mt能够保存2位(4值)的数据,当将保存有4值中的某一个时的阈值电平按照从低到高的顺序设为er电平(删除电平)、a电平、b电平、及c电平时,

[0258]

(1)读出动作中,

[0259]

在a电平的读出动作中施加至所选择字线的电压例如为0v~0.55v之间。并不限定于此,也可设为0.1v~0.24v、0.21v~0.31v、0.31v~0.4v、0.4v~0.5v、及0.5v~0.55v中的任一范围之间。

[0260]

在b电平的读出动作中施加至所选择字线的电压例如为1.5v~2.3v之间。并不限定于此,也可设为1.65v~1.8v、1.8v~1.95v、1.95v~2.1v及2.1v~2.3v中的任一范围之间。

[0261]

在c电平的读出动作中施加至所选择字线的电压例如为3.0v~4.0v之间。并不限定于此,也可设为3.0v~3.2v、3.2v~3.4v、3.4v~3.5v、3.5v~3.6v、及3.6v~4.0v中的任一范围之间。

[0262]

作为读出动作的时间(tr),也可设为例如25μs~38μs、38μs~70μs或70μs~80μs之间。

[0263]

(2)写入动作如上所述包含编程动作与验证动作。写入动作中,

[0264]

编程动作时最初施加至所选择字线的电压例如为13.7v~14.3v之间。并不限定于此,也可设为例如13.7v~14.0v及14.0v~14.6v中的任一范围之间。

[0265]

也可改变对第奇数条字线进行写入时最初施加至所选择字线的电压、与对第偶数条字线进行写入时最初施加至所选择字线的电压。

[0266]

当将编程动作设为ispp方式(incremental step pulse program,增量阶跃脉冲编程)时,作为升压电压,列举例如0.5v左右。

[0267]

作为施加至非选择字线的电压,也可设为例如6.0v~7.3v之间。并不限定于该情况,也可设为例如7.3v~8.4v之间,还可设为6.0v以下。

[0268]

也可根据非选择字线为第奇数条字线还是第偶数条字线来改变要施加的通路电压。

[0269]

作为写入动作的时间(tprog),也可设为例如1700μs~1800μs、1800μs~1900μs、或1900μs~2000μs之间。

[0270]

(3)删除动作中,

[0271]

最初施加至形成在半导体衬底上部且在上方配置着所述存储单元的阱的电压例如为12v~13.6v之间。并不限定于该情况,也可设为例如13.6v~14.8v、14.8v~19.0v、19.0~19.8v、或19.8v~21v之间。

[0272]

作为删除动作的时间(terase),也可设为例如3000μs~4000μs、4000μs~5000μs或4000μs~9000μs之间。

[0273]

已对本发明的若干实施方式进行了说明,但这些实施方式是作为例子提出的,并不意图限定发明的范围。这些新颖的实施方式能以其它各种方式实施,可以在不脱离发明

主旨的范围内进行各种省略、置换、变更。这些实施方式或其变化包含在发明的范围或主旨中,并且包含在权利要求书所记载的发明及其均等的范围内。

[0274]

[符号的说明]

[0275]1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储器系统

[0276]2ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

主机设备

[0277]

10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输入输出电路

[0278]

11

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

逻辑控制电路

[0279]

12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

状态寄存器

[0280]

13

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

地址寄存器

[0281]

14

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

指令寄存器

[0282]

15

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

定序器

[0283]

16

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

就绪/忙碌电路

[0284]

17

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电压产生电路

[0285]

18

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储单元阵列

[0286]

19

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

行解码器

[0287]

20

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

读出放大器

[0288]

21

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

数据寄存器

[0289]

22

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

列解码器

[0290]

30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

半导体衬底

[0291]

31、33a~33d、37a、37b 导电层

[0292]

35a

ꢀꢀꢀꢀꢀꢀꢀꢀ

阻挡绝缘层

[0293]

35b

ꢀꢀꢀꢀꢀꢀꢀꢀ

电荷蓄积层

[0294]

35c

ꢀꢀꢀꢀꢀꢀꢀꢀ

隧道绝缘层

[0295]

36、40a、40b 半导体层

[0296]

39a、39b

ꢀꢀꢀ

栅极绝缘层

[0297]

41

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极线层

[0298]

42

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

插塞层

[0299]

43

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

位线层

[0300]

50~61、70~77、80、81、200~236晶体管

[0301]

62

ꢀꢀꢀꢀꢀꢀꢀꢀ

电容元件

[0302]

90a、90b

ꢀꢀꢀ

阱区域

[0303]

91a、91b

ꢀꢀꢀ

n型阱

[0304]

92a、92b

ꢀꢀꢀ

p型阱

[0305]

93

ꢀꢀꢀꢀꢀꢀꢀꢀꢀn+

扩散层

[0306]

94

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极电极

[0307]

95

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

配线层

[0308]

96

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

层间绝缘膜

[0309]

100

ꢀꢀꢀꢀꢀꢀꢀꢀ

nand型高速缓冲存储器

[0310]

110

ꢀꢀꢀꢀꢀꢀꢀꢀ

控制器

[0311]

120

ꢀꢀꢀꢀꢀꢀꢀꢀ

主机接口电路

[0312]

130

ꢀꢀꢀꢀꢀꢀꢀꢀ

内置存储器

[0313]

140

ꢀꢀꢀꢀꢀꢀꢀꢀ

处理器

[0314]

150

ꢀꢀꢀꢀꢀꢀꢀꢀ

缓冲存储器

[0315]

160

ꢀꢀꢀꢀꢀꢀꢀꢀ

nand接口电路

[0316]

170

ꢀꢀꢀꢀꢀꢀꢀꢀ

ecc电路

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1