一种电压域转时域的存内计算电路的制作方法

1.本发明涉及存内计算技术领域,特别是涉及一种电压域转时域的存内计算电路。

背景技术:

2.随着边缘计算的需求增加,冯诺伊曼体系也逐渐到了瓶颈,随之出现了存内计算的概念,存内计算通过对原有的存储阵列增加计算结构,实现了在阵列中的乘累加计算,大大降低了计算功耗。存内计算针对神经网络进行加速,故需要较高的并行度,而计算结构相比原来的存储阵列不能过多的增加面积,否则将失去存储阵列增加计算结构的意义。

3.adc(analog-to-digitalconverter,模数转换器)已经成为了存内计算中一个不可忽略的功耗组成和面积开销,功耗可以占到整体的40%甚至更多,削弱模数转换部分的功耗开销成为了亟待解决的问题。

技术实现要素:

4.本发明的目的是提供一种电压域转时域的存内计算电路,降低存内计算的功耗和占用面积。

5.为实现上述目的,本发明提供了如下方案:

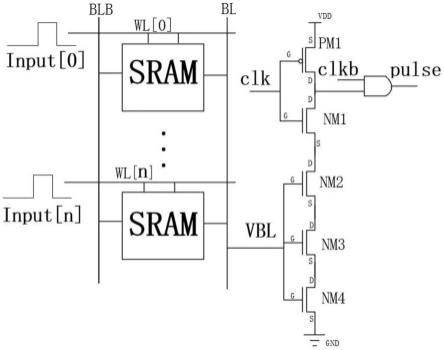

6.一种电压域转时域的存内计算电路,包括sram列单元和电压域时域转换电路;所述sram列单元为多个sram组成的一列,各所述sram的位线共线连接,各所述sram的反位线共线连接,每个所述sram的字线均连接一个输入信号,各所述sram用于存储权重;所述电压域时域转换电路的输入连接所述位线;

7.所述电压域时域转换电路包括晶体管pm1、晶体管nm1、晶体管nm2、晶体管nm3、晶体管nm4和与门,所述晶体管pm1的源极连接电源,所述晶体管pm1的栅极和所述晶体管nm1的栅极连接时钟信号,所述晶体管pm1的漏极分别与所述晶体管nm1漏极和所述与门的第一输入端连接,所述与门的第二输入端连接所述时钟信号的反相信号,所述晶体管nm2的栅极、所述晶体管nm3的栅极和所述晶体管nm4的栅极均与所述位线连接,所述晶体管nm1源极连接所述晶体管nm2的漏极,所述晶体管nm2的源极连接所述晶体管nm3的漏极,所述晶体管nm3的源极连接所述晶体管nm4的漏极,所述晶体管nm4的源极接地;

8.通过量化所述与门输出的脉冲宽度表示所述sram列单元的乘累加结果;所述乘累加结果为各行sram存储的权重与对应字线的输入信号的乘累加结果。

9.可选地,所述sram包括权重存储节点q和权重存储节点qb,各所述sram的权重存储节点q与所述位线连接,各所述sram的权重存储节点qb与所述反位线连接。

10.可选地,所述sram为6t sram,所述6t sram包括晶体管p1、晶体管p2、晶体管n1、晶体管n2、晶体管n3和晶体管n4,所述晶体管p1的源极和所述晶体管p2的源极均连接电源,所述晶体管p1的栅极分别与所述晶体管n1的栅极、所述晶体管p2的漏极、所述晶体管n2的漏极和所述晶体管n4的源极连接,所述晶体管p2的栅极分别与所述晶体管n2的栅极、所述晶体管p1的漏极、所述晶体管n1的漏极和所述晶体管n3的源极连接,所述晶体管n1的源极和

所述晶体管n2的源极均接地,所述晶体管n3的栅极和所述晶体管n4的栅极连接字线,所述晶体管n3的漏极连接所述位线,所述晶体管n4的漏极连接所述反位线;所述晶体管n3的源极与所述晶体管n1的漏极的连接处为权重存储节点q,所述晶体管n4的源极与所述晶体管n2的漏极为连接处为权重存储节点qb。

11.可选地,所述sram列单元包括32个sram。

12.可选地,所述晶体管pm1为pmos管,所述晶体管nm1、所述晶体管nm2、所述晶体管nm3和所述晶体管nm4均为nmos管。

13.可选地,所述晶体管p1和所述晶体管p2均为pmos管,所述晶体管n1、所述晶体管n2、所述晶体管n3和所述晶体管n4均为nmos管。

14.根据本发明提供的具体实施例,本发明公开了以下技术效果:

15.本发明公开了一种电压域转时域的存内计算电路,通过电压域时域转换电路将位线bl上累计的乘累加结果转换到时域进行累加,解决了模数转换器的功耗和占用面积大的问题,降低存内计算的功耗和占用面积。

附图说明

16.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

17.图1为本发明一种电压域转时域的存内计算电路结构示意图。

具体实施方式

18.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

19.本发明的目的是提供一种电压域转时域的存内计算电路,降低存内计算的功耗和占用面积。

20.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

21.图1为本发明一种电压域转时域的存内计算电路结构示意图,如图1所示,一种电压域转时域的存内计算电路,包括sram列单元和电压域时域转换电路;sram列单元为多个sram(static random-access memory,静态随机存取存储器)组成的一列,各sram的位线bl共线连接,各sram的反位线blb共线连接,每个sram的字线均连接一个输入信号,各sram用于存储权重;电压域时域转换电路的输入连接位线bl。

22.电压域时域转换电路包括晶体管pm1、晶体管nm1、晶体管nm2、晶体管nm3、晶体管nm4和与门,晶体管pm1的源极连接电源,晶体管pm1的栅极和晶体管nm1的栅极连接时钟信号clk,晶体管pm1的漏极分别与晶体管nm1漏极和与门的第一输入端连接,与门的第二输入端连接时钟信号的反相信号clkb,晶体管nm2的栅极、晶体管nm3的栅极和晶体管nm4的栅极

均与位线bl连接,晶体管nm1源极连接晶体管nm2的漏极,晶体管nm2的源极连接晶体管nm3的漏极,晶体管nm3的源极连接晶体管nm4的漏极,晶体管nm4的源极接地。

23.基于位线bl的放电量与门输出的脉冲宽度成正比,通过量化与门输出的脉冲宽度表示sram列单元的乘累加结果;乘累加结果为各行sram存储的权重与对应字线的输入信号的乘累加结果。

24.时钟信号clk为sram列单元进行存内计算提供时钟信号,sram列单元的一次乘累加运算在时钟信号的一个周期内完成。

25.如图1所示,sram列单元共n+1个sram,第1个sram的输入信号为input[0],第1个sram的字线为wl[0],第n+1个sram的输入信号为input[n],第n+1个sram的字线为wl[n]。

[0026]

sram包括权重存储节点q和权重存储节点qb,各sram的权重存储节点q与位线bl连接,各sram的权重存储节点qb与反位线blb连接。

[0027]

sram为6t sram,6t sram包括晶体管p1、晶体管p2、晶体管n1、晶体管n2、晶体管n3和晶体管n4,晶体管p1的源极和晶体管p2的源极均连接电源,晶体管p1的栅极分别与晶体管n1的栅极、晶体管p2的漏极、晶体管n2的漏极和晶体管n4的源极连接,晶体管p2的栅极分别与晶体管n2的栅极、晶体管p1的漏极、晶体管n1的漏极和晶体管n3的源极连接,晶体管n1的源极和晶体管n2的源极均接地,晶体管n3的栅极和晶体管n4的栅极连接字线,晶体管n3的漏极连接位线bl,晶体管n4的漏极连接反位线blb;晶体管n3的源极与晶体管n1的漏极的连接处为权重存储节点q,晶体管n4的源极与晶体管n2的漏极为连接处为权重存储节点qb。

[0028]

sram列单元包括32个sram。一个存储计算阵列包括多列sram列单元,多列sram列单元的位线均与电压域时域转换电路连接,阵列尺寸根据数据位宽的需求和实际芯片的功耗面积的要求进行改动,具有一定的灵活性。存储计算阵列按列对乘积(输入信号与权重的乘积)进行累加。

[0029]

晶体管pm1为pmos管,晶体管nm1、晶体管nm2、晶体管nm3和晶体管nm4均为nmos管。

[0030]

晶体管p1和晶体管p2均为pmos管,晶体管n1、晶体管n2、晶体管n3和晶体管n4均为nmos管。

[0031]

进行乘累加时,当一个sram对应的字线的输入信号为1时,输入信号为单bit输入数据0或1,sram对位线的放电通路打开,如果sram内q点存储的数据为1,则对应的qb点存储数据为0,通路打开时会产生放电,对应为1*1=1的情况;如果输入信号或者权重中有一者为0,则位线上不放电,对应1*0=0或0*0=0;如此在阵列上实现二值化乘法。每个sram对位线的放电作用会累积在位线bl上,使位线bl处于不同的电平vbl,电平vbl用于控制nm2-nm4的栅极,电平vbl增高,使得电压域时域转换电路(pm1,nm1-nm4)的下拉通路被限流,下拉过程变慢,在与时钟信号的反相信号clkb做与运算后,会得到一个脉冲pulse,由时钟信号下降沿开始,位线电压vbl越高,放电越少,pulse宽度越短,反之同理。通过量化脉冲pulse的宽度,得到sram列单元的乘累加结果。

[0032]

本发明将sram阵列的单bit数乘累加结果转到时域进行累加,不再需要adc进行电压域的模数转换。而adc通常会产生较大面积开销和功耗开销,并且制约输出结果精度。本发明将电压域转换到时域,使用时域模数转换,提升运算速度的同时,减小电流串扰产生的影响。

[0033]

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他

实施例的不同之处,各个实施例之间相同相似部分互相参见即可。

[0034]

本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1