一种基于STT和SOT协同作用的磁随机存储器结构的制作方法

一种基于stt和sot协同作用的磁随机存储器结构

技术领域

1.本发明属于信息存储领域,特别是涉及一种基于stt和sot协同作用的磁随机存储器结构。

背景技术:

2.在众多的新型非易失性存储器中,磁随机存储器(magnetic random-access memory,mram)以其具有的非易失性,高耐久性,高擦写次数,快速的读写速度以及与cmos后道工艺的兼容性,成为下一代通用存储技术的有力竞争者。mram的基本存储单元为磁性隧道结(magnetic tunnel junction,mtj)。mtj的基本结构为磁性层/隧穿层/磁性层,其中一层磁性层的矫顽力较大,磁化方向不易改变,称为钉扎层,另一层的磁性层矫顽力较小,磁化方向容易改变,称为自由层。由于隧穿磁电阻(tunneling magnetoresistance,tmr)效应,两磁性的平行和反平行对应于mtj的低阻和高阻状态。

3.第一代mram采用磁场写入方式,磁场靠电流产生。随着尺寸的减小,翻转mtj所需要的电流也越来越大,造成了功耗的提升,同时由于需要采用电流来产生磁场,面积也很难缩小。

4.第二代mram采用自旋转移力矩(spin transfer torque,stt)效应进行写入。相比采用磁场写入方式,利用stt效应大大降低了写入电流,随着mram单元尺寸的缩小,写入电流将进一步降低。然而,随着集成密度的提高,mtj的尺寸不断缩小,stt-mram较高的写入电流会导致隧穿层的损伤。同时,由于自旋转移效率的限制,stt-mram的写入电流无法进一步降低,传统stt-mram结构图如图1所示。

5.第三代mram采用自旋轨道转矩(spin orbit torque,sot)效应进行写入。相比stt效应,利用sot效应可以实现分离的读写通道,避免了隧穿层的快速老化。同时sot效应可以进一步降低写入电流。然而,为了打破对称性,sot-mram需要施加与电流平行的磁场。这限制了mram密度的提高。

6.虽然mtj具有cmos后道工序的兼容性,但在后道工序的温度(400℃)下制备的mtj的tmr比值很难高于100%。

技术实现要素:

7.本发明的目的是提供一种基于stt和sot协同作用的磁随机存储器结构,以解决上述现有技术存在的问题。

8.为实现上述目的,本发明提供了一种基于stt和sot协同作用的磁随机存储器结构,包括:

9.若干个互联的磁随机存储单元;其中,所述磁随机存储单元包括:

10.源线source line,字线word line,位线bit line,磁性隧道结mtj;

11.所述source line用于给所述磁随机存储器结构输送电力;

12.所述word line用于控制所述mtj的写入与读出;

13.所述bit line用于控制写入电流的输入并用于所述mtj的阻态的读出;

14.所述mtj用于对需要存储的数据进行随机存储。

15.可选的,所述word line基于所述source line的电力供给情况,控制结构回路的连接状态,进而控制所述mtj的写入与读出。

16.可选的,所述bit line包括自旋转移力矩位线stt bit line、自旋轨道转矩位线sot bit line。

17.可选的,所述mtj包括自由层、隧穿层、钉扎层、重金属层,其中,其中,重金属层、自由层、隧穿层、钉扎层从上到下依次相连。

18.可选的,所述钉扎层与所述stt bit line相连,所述重金属层与所述sot bit line相连。

19.可选的,基于对所述bit line供给电流的方式,改变所述磁性隧道结mtj中的自由层磁化状态,进而改变所述mtj的电阻大小,控制信息的写入和读出。

20.可选的,两个所述磁随机存储单元进行互联时,共用所述source line和所述sot bit line,互联完成后得到互联结构。

21.可选的,基于所述互联结构构建磁随机存储器结构。

22.本发明的技术效果为:

23.(1)将自由层设置在钉扎层上方,提高了tmr比值,进而提高了电路的稳定性。

24.(2)通过两个互联的磁随机存储单元共用一条位线bit line和源线source line的结构提高磁随机存储器的存储密度。

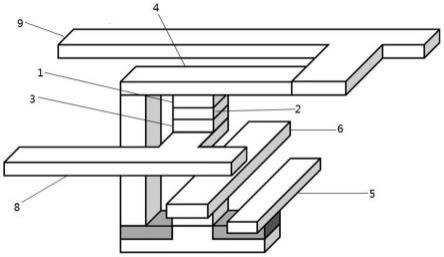

附图说明

25.构成本技术的一部分的附图用来提供对本技术的进一步理解,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。在附图中:

26.图1为传统stt-mram结构图;

27.图2为本发明实施例中的一种具有drain line的mram单元结构图;

28.图3为本发明实施例中的基于stt和sot单元结构图;

29.图4为本发明实施例中的根据基于stt和sot单元结构图构建的单元互联结构图;

30.图5为本发明实施例中的基于stt和sot协同作用的磁随机存储器结构;

31.图6为本发明实施例中的基于bit line的mram单元结构图;

32.图7为本发明实施例中的基于图6构建的单元互联结构图;

33.图8为本发明实施例中的基于图7构建的存储单元阵列图。

34.附图标记:1-自由层,2-隧穿层,3-钉扎层,4-重金属层,5-source line,6-word line,7-bit line,8-stt bit line,9-sot bit line,10-drain line。

具体实施方式

35.需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本技术。

36.实施例一

37.如图2-5所示,本实施例中提供一种基于stt和sot协同作用的磁随机存储器结构,

包括:

38.源线source line 5,字线word line 6,位线bit line 7,磁性隧道结mtj;

39.source line 5用于给磁随机存储器结构输送电力;

40.word line 6用于控制mtj的写入与读出;

41.bit line 7用于控制写入电流的输入并用于mtj的阻态的读出。

42.可选的,word line 6基于source line 5的电力供给情况,控制结构回路的连接状态,进而控制mtj的写入与读出。

43.可选的,bit line 7包括stt bit line 8、sot bit line 9。

44.可选的,mtj包括自由层1、隧穿层2、钉扎层3、重金属层4,其中,重金属层4、自由层1、隧穿层2、钉扎层3从上到下依次相连。

45.可选的,钉扎层3与stt bit line 8相连,重金属层4与sot bit line 9相连。

46.可选的,基于对bit line 7供给电流的方式,改变磁性隧道结mtj中的自由层1磁化状态,进而改变mtj的电阻大小,控制信息的写入和读出。

47.可选的,两个磁随机存储单元进行互联时,共用source line 5和sot bit line 9,互联完成后得到互联结构,磁随机存储单元如图3所示,互联结构如图4所示,通过word line 6上的选通晶体管来控制mtj的写入和读出。1代表mtj的自由层,2代表mtj的隧穿层,3代表mtj的钉扎层。4为重金属层。两个单元结构相同且共用sot bit line 9和source line 5。sot bit line 9为金属导线,控制产生sot效应的电流,stt bit line 8为金属导线,控制产生stt效应的电流并用于mtj的阻态的读出。在写操作时要求sot bit line 9和stt bit line 8等电势。

48.可选的,基于互联结构构建磁随机存储器结构,磁随机存储器结构如图5所示,互联结构之间共用bl

stti

,共用规则为地址(1,k)到(1+i,k+i)共用一条bl

stt

,地址前一位指bl

sot

的标号,地址后一位指wl的标号,其中,k为整数,i=1,2,3

…

,1代表mtj的自由层,2代表mtj的隧穿层,3代表mtj的钉扎层。4为重金属层。bl

soti

控制产生sot效应电流的写入,bl

stti

控制产生stt效应电流的写入并用于mtj的阻态的读出,wli控制mtj的写入和读出,sli代表源极线。

49.一种具有drain line的mram单元如图2所示。通过word line 6上的选通晶体管来控制mtj的写入和读出。sot bit line 9控制产生sot效应的电流,当电流流经sot bit line 9时,由于自旋霍尔等效应,电流会产生一个垂直于sot bit line 9的自旋流并注入mtj的自由层进而影响自由层的磁化状态。stt bit line 8控制产生stt效应的电流并用于mtj的阻态的读出。当电流流经stt bit line 8时,由于自旋转移力矩效应,流过钉扎层的电流会被自旋极化,极化的方向与钉扎层的方向相同,进而通过隧穿效应穿过隧穿层进入自由层进而改变自由层的磁化状态。在进行写操作时,sot bit line 9和stt bit line 8必须同时施加电流。当进行读操作时,在stt bit line 8中通入读电流,由于tmr效应,当自由层和钉扎层的磁化状态相同时,mtj呈低电阻,存储信息为0;当自由层和钉扎层的磁化状态相反时,mtj呈高电阻,存储信息为1。当把单元扩展为整列后,读写方式相同。

50.实施例二

51.一种基于bit line的mram单元如图6所示。通过word line 6上的选通晶体管来控制mtj的写入和读出。1代表mtj的自由层,2代表mtj的隧穿层,3代表mtj的钉扎层。4为重金

属层。bit line 7控制写入电流的输入并用于mtj的阻态的读出。当word line 6为高电平时,mtj被选通,当bit line 7中通入由source line 5流向bit line 7的电流时,mtj的自由层1和钉扎层3平行,为低阻态,即写0;当bit line 7中通入由bit line 7流向source line 5的电流时,mtj的自由层1和钉扎层3反平行,为高阻态,即写1。图6中bit line 7同时具有stt bit line 8和sot bit line 9的功能,相当于stt bit line 8和sot bit line 9合为一条bit line 7。

52.基于图6构建的单元互联结构如图7所示。通过word line 6上的选通晶体管来控制mtj的写入和读出。1代表mtj的自由层,2代表mtj的隧穿层,3代表mtj的钉扎层。4为重金属层。两个单元结构相同且共用bit line 7和source line 5,bit line 7控制写入电流的输入并用于mtj的阻态的读出。

53.基于图7构建的存储单元阵列如图8所示。1代表mtj的自由层,2代表mtj的隧穿层,3代表mtj的钉扎层。4为重金属层。bl控制写入电流的输入并用于mtj的阻态的读出,wl控制mtj的写入和读出,sl代表源极线。

54.以上所述,仅为本技术较佳的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应该以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1