测试芯片中SRAM模组可靠性的方法、装置、存储介质及芯片与流程

测试芯片中sram模组可靠性的方法、装置、存储介质及芯片

技术领域

1.本技术涉及芯片测试领域,尤其涉及一种测试芯片中sram模组可靠性的方法、装置、存储介质及计算机设备。

背景技术:

2.为了芯片的质量保证,目前主流的芯片可测试方法主要有dft(design for testability,可靠性测试)测试,cp(chip probing,晶圆测试)测试,ft(functional test,功能测试,是一种针对电器元件进行通电试验,以测试其是否可以正常工作的测试)测试,通过以上的几种测试可以大大提高芯片良率。

3.但是随着需求越来越复杂,芯片功能也就愈发复杂,芯片为了实现复杂的功能会增加很多sram(static random-access memory,静态随机读取存储器)模组,sram模组会由于制作工艺的偏差、芯片工作的温度和工作环境的不同,会出现数据丢失或存储单元损坏的情况,如何对芯片内sram模组进行可靠性测试是目前研究的热点。

技术实现要素:

4.本技术实施例提供了测试芯片中sram模组可靠性的方法、装置、存储介质及芯片,可以解决现有技术中离线训练模型的长时预测结果准确性不高的问题。所述技术方案如下:

5.第一方面,本技术实施例提供了一种测试芯片中sram模组可靠性的方法,所述芯片中设置有第一sram和第二sram,所述第一sram模组和所述第二sram模组的容量相等;

6.其中,所述方法包括:

7.在第一模式下,获取待写入的信息序列;

8.根据汉明码编码规则对所述信息序列进行编码得到校验序列;

9.遍历所述第一sram模组和所述第二sram模组中各个存储单元的地址;

10.向所述第一sram模组中地址指示的第一存储单元写入所述信息序列,以及向所述第二sram模组中所述地址指示的第二存储单元写入所述校验序列;

11.完成写操作后,在所述第一sram模组中所述地址指示的第一存储单元中读取信息序列,以及在所述第二sram模组中所述地址指示第二存储单元中读取校验序列;

12.将读取的信息序列和读取校验序列组成编码序列;

13.根据汉明码解码规则对组成的编码序列进行校验;

14.根据校验结果向上位机发送测试结果。

15.第二方面,本技术实施例提供了一种测试芯片中sram模组可靠性的装置,所述装置包括:

16.获取单元,用于在第一模式下,获取待写入的信息序列;

17.编码单元,用于根据汉明码编码规则对所述信息序列进行编码得到校验序列;

18.遍历单元,用于遍历第一sram模组和第二sram模组中各个存储单元的地址;

19.写入单元,用于向所述第一sram模组中地址指示的第一存储单元写入所述信息序列,以及向所述第二sram模组中所述地址指示的第二存储单元写入所述校验序列;

20.读取单元,用于完成写操作后,在所述第一sram模组中所述地址指示的第一存储单元中读取信息序列,以及在所述第二sram模组中所述地址指示第二存储单元中读取校验序列;

21.组合单元,用于将读取的信息序列和读取校验序列组成编码序列;

22.校验单元,用于根据汉明码解码规则对组成的编码序列进行校验;

23.收发单元,用于根据校验结果向上位机发送测试结果。

24.第三方面,本技术实施例提供一种计算机存储介质,所述计算机存储介质存储有多条指令,所述指令适于由处理器加载并执行上述的方法步骤。

25.第四方面,本技术实施例提供一种芯片,可包括:处理器和存储器;其中,所述存储器存储有计算机程序,所述计算机程序适于由所述处理器加载并执行上述的方法步骤。

26.本技术一些实施例提供的技术方案带来的有益效果至少包括:

27.分别在芯片内设置第一sram模组和第二sram模组,根据汉明码编码规则生成信息序列对应的校验序列,以及分别向第一sram模组写入信息序列和向第二sram模组写入校验序列,完成写操作后,从第一sram模组中读出信息序列和在第二sram模组中读出校验序列,将读取的信息序列和校验序列进行组装生成编码序列,利用汉明码解码规则对编码序列进行校验,实现对第一sram模组和第二sram模组中各个存储单元的可靠性测试,相对于现有技术中对芯片的sram模组每次对一个存储单元进行可靠性测试相比,本技术可以每次测试两个存储单元,对于相同容量的sram模组来说,从而提高测试效率和缩短测试时间。

附图说明

28.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

29.图1是本技术实施例提供的网络架构示意图;

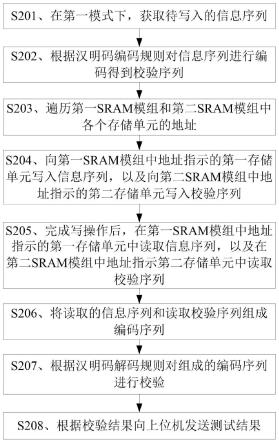

30.图2是本技术实施例提供的测试芯片中sram模组可靠性的方法的流程示意图;

31.图3是本技术提供的一种测试芯片中sram模组可靠性的装置的结构示意图;

32.图4是本技术提供的一种计算机设备的结构示意图。

具体实施方式

33.为使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术实施例方式作进一步地详细描述。

34.需要说明的是,本技术提供的芯片的测试方法一般由芯片执行,相应的,芯片的测试装置一般设置于芯片中。

35.图1示出了可以应用于本技术的芯片的测试方法或芯片的测试装置的示例性系统架构。

36.如图1所示,系统架构可以包括:上位机101、芯片(图1中未画出)和测试夹具102,

芯片设置在测试夹具中的芯片插座中,然后由测试夹具连接到上位机101。上位机101和芯片之间可以通过网络进行通信,网络用于上述各个单元之间提供通信链路的介质。网络可以包括各种类型的有线通信链路或无线通信链路,例如:有线通信链路包括光纤、双绞线或同轴电缆等,无线通信链路包括蓝牙通信链路、无线保真(wireless-fidelity,wi-fi)通信链路或微波通信链路等。

37.其中,芯片内置有第一sram模组和第二sram模组,芯片处于第一模式下,两个sram模组分别进行地址编码;在芯片处理第二模式下,两个sram模组统一进行编码。上位机101向芯片发送测试指令,指示芯片对内部的sram模组进行可靠性测试。

38.需要说明的是,当上位机101和芯片为硬件时,可以实现成多个芯片组成的分布式芯片集群,也可以实现成单个芯片。当上位机101和芯片为软件时,可以实现成多个软件或软件模块(例如用来提供分布式服务),也可以实现成单个软件或软件模块,在此不做具体限定。

39.本技术的上位机上可以安装有各种通信客户端应用,例如:视频录制应用、视频播放应用、语音交互应用、搜索类应用、即时通信工具、邮箱客户端、社交平台软件等。

40.上位机可以是硬件,也可以是软件。当上位机为硬件时,可以是具有显示屏的各种上位机,包括但不限于智能手机、平板电脑、膝上型便携式计算机和台式计算机等等。当上位机为软件时,可以是安装上述所列举的上位机中。其可以实现呈多个软件或软件模块(例如:用来提供分布式服务),也可以实现成单个软件或软件模块,在此不作具体限定。

41.当上位机为硬件时,其上还可以安装有显示设备和摄像头,显示设备显示可以是各种能实现显示功能的设备,摄像头用于采集视频流;例如:显示设备可以是阴极射线管显示器(cathode ray tube display,简称cr)、发光二极管显示器(light-emitting diode display,简称led)、电子墨水屏、液晶显示屏(liquid crystal display,简称lcd)、等离子显示面板(plasma display panel,简称pdp)等。用户可以利用上位机上的显示设备,来查看显示的文字、图片、视频等信息。

42.应理解,图1中的上位机、网络和芯片的数目仅是示意性的。根据实现需要,可以是任意数量的上位机、网络和芯片。

43.下面将结合附图2,对本技术实施例提供的测试芯片中sram模组可靠性的方法进行详细介绍。其中,本技术实施例中的测试芯片中sram模组可靠性的装置可以是图1所示的计算机设备。

44.请参见图2,为本技术实施例提供了一种测试芯片中sram模组可靠性的方法的流程示意图。如图2所示,本技术实施例的所述方法可以包括以下步骤:

45.s201、在第一模式下,获取待写入的信息序列。

46.其中,在第一模式下,对芯片的sram模组进行功能性测试,本技术的芯片内设置有第一sram模组和第二sram模组,第一sram模组和第二sram模组的容量相同。上位机向芯片发送测试指令,芯片接收到测试指令后进入到第一模式,在第一模式下,获取待写入的信息序列,芯片可以从寄存器中获取预设的信息序列,或接收来自上位机的信息序列,本技术不作限制,信息序列包含至少一个比特,信息序列的长度可以根据实际需求而定。

47.s202、根据汉明码编码规则对信息序列进行编码得到校验序列。

48.其中,芯片根据海明码编码规则对信息序列进行编码生成汉明码序列,汉明码序

列由信息序列和校验序列组成,校验序列包括至少一个比特,芯片记录生成的汉明码序列中信息序列的比特位置和校验序列的比特位置。

49.进一步,为了降低处理器的处理开销,芯片可以内置汉明码编码电路,芯片将信息序列输入到汉明码编码电路中后输出汉明码序列,然后确定汉明码序列中信息序列的比特位置和校验序列的比特位置,以及存储比特位置。

50.进一步的,在进行编码时,信息序列的长度为4比特,校验序列的长度也为4比特,通过上述长度的信息序列和校验序列,可以实现使用最少的校验序列实现1位纠错和2位检错的效果,减少数据冗余以及提高数据传输效率。

51.s203、遍历第一sram模组和第二sram模组中各个存储单元的地址。

52.其中,在第一模式下,第一sram模组和第二sram模组分别进行地址编码,第一sram模组和第二sram模组具有相同数量的存储单元以及每个存储单元的大小相等,例如:第一sram模组和第二sram模组的容量为4k字节,每个存储单元的大小为1个字节,那么第一sram模组和第二sram模组分别具有1000个存储单元,第一sram模组的地址范围为0~999(十进制表示),第二sram模组的地址范围为0~999。芯片遍历出各个存储单元的地址形成地址集合,地址集合中每个地址在第一sram模组中指示的存储单元称为第一存储单元,该地址在第二sram模组中指示的存储单元称为第二存储单元。在第一模式下,分别在两个独立的sram模组中执行写操作和读操作,可以减少数据处理瓶颈,提高读写操作的效率。

53.在一个或多个可能的实施例中,在芯片处于第二模式下,第一sram模组和第二sram模组的地址统一进行编码,在逻辑上为一个sram模组,例如:根据上面的例子,在第一sram模组和第二sram模组测试通过后,将第一sram模组和第二sram模组的地址统一进行编码:第一sram模组的地址范围为0~999,第二sram模组的地址范围为1000~1999,这样提高存储空间的利用率。

54.需要说明的是,本技术实施例也可以在数据高可靠性的场景下,启动第一模式,并不限于在对芯片进行测试时启动第一模式。

55.s204、向第一sram模组中地址指示的第一存储单元写入信息序列,以及向第二sram模组中地址指示的第二存储单元写入校验序列。

56.其中,对于每个地址来说,向该地址在第一sram模组中指示的第一存储单元写入信息序列,以及向该地址在第二sram模组中指示的第二存储单元写入校验序列。

57.例如:地址为125(十进制表示),将信息序列写入到第一sram模组中地址为125的存储单元中,以及将校验序列写入到第二sram模组中地址为125的存储单元中。

58.s205、完成写操作后,在第一sram模组中地址指示的第一存储单元中读取信息序列,以及在第二sram模组中地址指示第二存储单元中读取校验序列。

59.例如:根据s204中的例子,在完成写操作后,在第一sram模组中地址为125的存储单元中读取信息序列,以及在第二sram模组中地址为125的存储单元中读取校验序列。

60.s206、将读取的信息序列和读取校验序列组成编码序列。

61.其中,根据s202中记录的信息序列和校验序列的比特位置,组成编码序列。

62.s207、根据汉明码解码规则对组成的编码序列进行校验。

63.其中,根据汉明码解码规则对组成的编码序列进行校验,生成校验结果,校验结果包括未发生错误、1个比特发生错误、2个比特发生错误,芯片根据使用不同的比特值表示上

述各个校验结果。当编码序列未发生错误或1个比特发生错误时,校验结果为通过;当编码序列的2个比特发生错误时,校验结果为不通过。

64.进一步的,为了提高校验的准确性,排除临时干扰对sram模组的影响,当校验结果为2个比特发生错误时,根据预设的重复次数对该地址进行重复测试,如果存在至少一次校验结果为校验通过,那么最终的校验结果即为校验通过,否则,最终的校验结果为校验不通过。

65.进一步的,为了降低芯片的处理器的计算开销,可以通过芯片内置的汉明码解码电路对编码序列进行校验。

66.s208、根据校验结果向上位机发送测试结果。

67.其中,芯片在对第一sram模组和第二sram模组中所有存储单元的校验后,向上位机发送测试结果,测试结果包括校验不通过的存储单元的地址,上位机显示各个存储单元的地址,用户可以在上位机的显示单元查看测试结果。进一步的,对于校验不通过的存储单元,芯片可以对存储单元进行屏蔽,然后重新对屏蔽处理后的各个存储单元进行地址编码。

68.本技术的实施例在对芯片的sram模组进行可靠性测试时,分别在芯片内设置第一sram模组和第二sram模组,根据汉明码编码规则生成信息序列对应的校验序列,以及分别向第一sram模组写入信息序列和向第二sram模组写入校验序列,完成写操作后,从第一sram模组中读出信息序列和在第二sram模组中读出校验序列,将读取的信息序列和校验序列进行组装生成编码序列,利用汉明码解码规则对编码序列进行校验,实现对第一sram模组和第二sram模组中各个存储单元的可靠性测试,相对于现有技术中对芯片的sram模组每次对一个存储单元进行可靠性测试相比,本技术可以每次测试两个存储单元,从而提高测试效率和缩短测试时间。

69.下述为本技术装置实施例,可以用于执行本技术方法实施例。对于本技术装置实施例中未披露的细节,请参照本技术方法实施例。

70.请参见图3,其示出了本技术一个示例性实施例提供的测试芯片中sram模组可靠性的装置的结构示意图,以下简称装置3。该装置3可以通过软件、硬件或者两者的结合实现成为芯片的全部或一部分。装置3包括:获取单元301、编码单元302、遍历单元303、写入单元304、读取单元305、组合单元306、校验单元307和收发单元308。

71.获取单元301,用于在第一模式下,获取待写入的信息序列;

72.编码单元302,用于根据汉明码编码规则对所述信息序列进行编码得到校验序列;

73.遍历单元303,用于遍历第一sram模组和第二sram模组中各个存储单元的地址;

74.写入单元304,用于向所述第一sram模组中地址指示的第一存储单元写入所述信息序列,以及向所述第二sram模组中所述地址指示的第二存储单元写入所述校验序列;

75.读取单元305,用于完成写操作后,在所述第一sram模组中所述地址指示的第一存储单元中读取信息序列,以及在所述第二sram模组中所述地址指示第二存储单元中读取校验序列;

76.组合单元306,用于将读取的信息序列和读取校验序列组成编码序列;

77.校验单元307,用于根据汉明码解码规则对组成的编码序列进行校验;

78.收发单元308,用于根据校验结果向上位机发送测试结果。

79.在一个或多个可能的实施例中,编码序列中信息序列的长度为4个比特,校验序列

的长度为4个比特。

80.在一个或多个可能的实施例中,当所述编码序列中未发生比特错误或发生1个比特错误时,校验结果为通过;当所述编码序列中发生2个比特错误时,校验结果为不通过。

81.在一个或多个可能的实施例中,校验单元307还用于:

82.当所述地址的首次校验结果为不通过时,根据预设的重复次数对所述地址进行多次校验,若存在至少一次校验结果为通过时,则最终的校验结果为通过。

83.在一个或多个可能的实施例中,在第二模式下,所述第一sram模组和所述第二sram模组的地址是统一编码的。

84.在一个或多个可能的实施例中,所述获取待写入的信息序列,包括:

85.接收来自所述上位机的信息序列。

86.在一个或多个可能的实施例中,通过汉明码编码电路进行编码,以及通过汉明码解码电路进行解码和校验。

87.需要说明的是,上述实施例提供的装置3在执行测试芯片中sram模组可靠性的方法时,仅以上述各功能模块的划分进行举例说明,实际应用中,可以根据需要而将上述功能分配由不同的功能模块完成,即将设备的内部结构划分成不同的功能模块,以完成上述的全部或者部分功能。另外,上述实施例提供的测试芯片中sram模组可靠性的装置与测试芯片中sram模组可靠性的方法实施例属于同一构思,其体现实现过程详见方法实施例,这里不再赘述。

88.上述本技术实施例序号仅仅为了描述,不代表实施例的优劣。

89.本技术实施例还提供了一种计算机存储介质,所述计算机存储介质可以存储有多条指令,所述指令适于由处理器加载并执行如上述图2所示实施例的方法步骤,具体执行过程可以参见图2所示实施例的具体说明,在此不进行赘述。

90.本技术还提供了一种计算机程序产品,该计算机程序产品存储有至少一条指令,所述至少一条指令由所述处理器加载并执行以实现如上各个实施例所述的测试芯片中sram模组可靠性的方法。

91.请参见图4,为本技术实施例提供了一种芯片的结构示意图。如图4所示,所述芯片400可以包括:至少一个处理器401,至少一个网络接口404,sram模组403,只读存储器405,至少一个通信总线402。

92.其中,通信总线402用于实现这些组件之间的连接通信。

93.其中,sram模组403由第一sram模组和第二sram模组组成。

94.其中,网络接口404用于与外部设备进行通信,例如网络接口404可以包括标准的有线接口、无线接口(如wi-fi接口)。

95.其中,处理器401可以包括一个或者多个处理核心。处理器401利用各种接口和线路连接整个芯片400内的各个部分,通过运行或执行存储在存储器405内的指令、程序、代码集或指令集,以及调用存储在存储器405内的数据,执行芯片400的各种功能和处理数据。可选的,处理器401可以采用数字信号处理(digital signal processing,dsp)、现场可编程门阵列(field-programmable gate array,fpga)、可编程逻辑阵列(programmable logicarray,pla)中的至少一种硬件形式来实现。处理器401可集成中央处理器(central processing unit,cpu)、图像处理器(graphics processing unit,gpu)和调制解调器等中

的一种或几种的组合。其中,cpu主要处理操作系统、用户界面和应用程序等;gpu用于负责显示屏所需要显示的内容的渲染和绘制;调制解调器用于处理无线通信。可以理解的是,上述调制解调器也可以不集成到处理器401中,单独通过一块芯片进行实现。

96.其中,存储器405可以包括随机存储器(randomaccess memory,ram),也可以包括只读存储器(read-only memory)。可选的,该存储器405包括非瞬时性计算机可读介质(non-transitory computer-readable storage medium)。存储器405可用于存储指令、程序、代码、代码集或指令集。存储器405可包括存储程序区和存储数据区,其中,存储程序区可存储用于实现操作系统的指令、用于至少一个功能的指令(比如触控功能、声音播放功能、图像播放功能等)、用于实现上述各个方法实施例的指令等;存储数据区可存储上面各个方法实施例中涉及到的数据等。存储器405可选的还可以是至少一个位于远离前述处理器401的存储装置。如图4所示,作为一种计算机存储介质的存储器405中可以包括操作系统、网络通信模块、用户接口模块以及应用程序。

97.在图4所示的芯片400中,用户接口403主要用于为用户提供输入的接口,获取用户输入的数据;而处理器401可以用于调用存储器405中存储的应用程序,并具体执行如图2所示的方法,具体过程可参照图2所示,此处不再赘述。

98.本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,所述的程序可存储于一计算机可读取存储介质中,该程序在执行时,可包括如上述各方法的实施例的流程。其中,所述的存储介质可为磁碟、光盘、只读存储记忆体或随机存储记忆体等。

99.以上所揭露的仅为本技术较佳实施例而已,当然不能以此来限定本技术之权利范围,因此依本技术权利要求所作的等同变化,仍属本技术所涵盖的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1