存储单元、存储器、存储器结构以及存储器的工作方法与流程

本发明涉及存储器领域,尤其涉及一种存储单元、存储器、存储器结构以及存储器的工作方法。

背景技术:

1、半导体存储器根据存储数据的方式不同,可分为随机存取存储器(ram)和只读存储器(rom)两大类。其中,随机存取存储器(ram)又可分为静态随机存取存储器(sram)和动态随机存取存储器(dram)。与dram相比,sram具有更快的读写速度。而且sram不需要周期性刷新存储的信息,其设计和制造相对简单。

2、sram具有超低功耗特性,是电池应用领域中的基本要求,例如,物联网领域、移动和便携式电子产品领域以及无线传感器领域等。在这些领域中,考虑到应用程序需要更新,sram需要保持供电,由此导致sram功耗增加。

3、因此,如何降低sram的功耗,成为了亟待解决的问题。

技术实现思路

1、本发明解决的技术问题是提供一种存储单元、存储器、存储器结构以及存储器的工作方法,以减小sram的功耗。

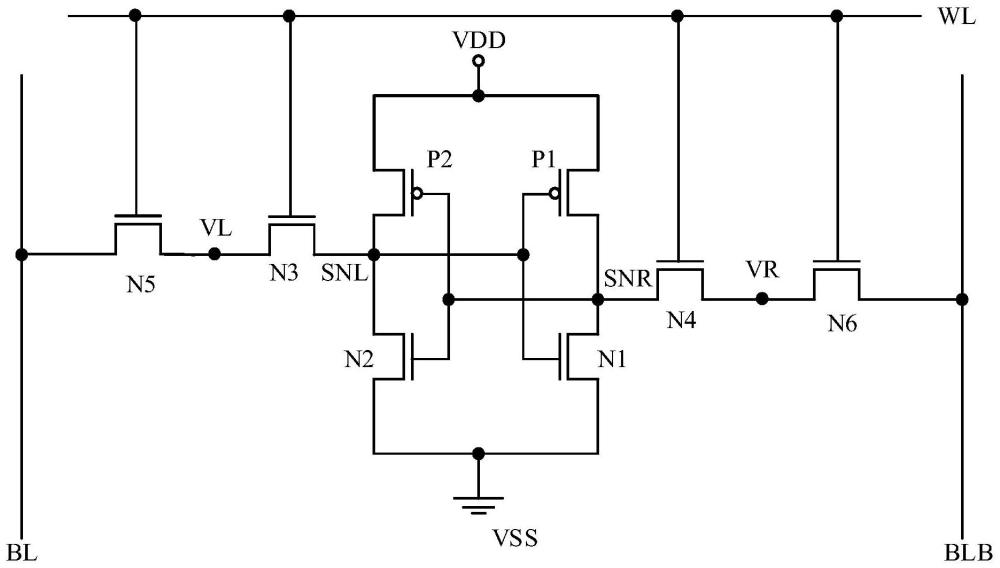

2、为解决上述技术问题,本发明技术方案提供一种存储单元,包括:第一反相器;第二反相器;第一访问晶体管,一端与所述第一反相器连接;第二访问晶体管,一端与所述第二反相器连接;第一节点,所述第一访问晶体管的另一端与所述第一节点连接;第二节点,所述第二访问晶体管的另一端与所述第二节点连接;第三访问晶体管,一端与所述第一节点连接;第四访问晶体管,一端与所述第二节点连接;第一位线,与所述第三访问晶体管的另一端连接;第二位线,与所述第四访问晶体管的另一端连接;字线,与所述第一访问晶体管、第二访问晶体管、第三访问晶体管和第四访问晶体管连接。

3、可选的,还包括:电源端和接地端,所述第一反相器的一端与电源端连接,所述第一反相器的另一端与接地端连接,所述第二反相器的一端与电源端连接,所述第二反相器的另一端与接地端连接。

4、可选的,所述第一反相器包括:相连接的第一上拉晶体管和第一下拉晶体管,所述第一上拉晶体管包括第一栅极、第一源极和第一漏极,所述第一下拉晶体管包括第二栅极、第二源极和第二漏极,所述第一源极与所述电源端连接,所述第一漏极与所述第二漏极连接,所述第二源极与所述接地端连接,所述第一栅极和所述第二栅极连接。

5、可选的,所述第二反相器包括:相连接的第二上拉晶体管和第二下拉晶体管,所述第二上拉晶体管包括第三栅极、第三源极和第三漏极,所述第二下拉晶体管包括第四栅极、第四源极和第四漏极,所述第三源极与所述电源端连接,所述第三漏极与所述第四漏极连接,所述第四源极与所述接地端连接,所述第三栅极和所述第四栅极连接。

6、可选的,所述第一访问晶体管包括第一端、第二端和第一控制端,所述第二访问晶体管包括第三端、第四端和第二控制端,所述第三访问晶体管包括第五端、第六端和第三控制端,所述第四访问晶体管包括第七端、第八端和第四控制端;所述第一访问晶体管的第一端与所述第一栅极和所述第二栅极连接,所述第一访问晶体管的第二端与所述第一节点连接;所述第二访问晶体管的第三端与所述第三栅极和所述第四栅极连接,所述第二访问晶体管的第四端与所述第二节点连接;所述第三访问晶体管的第五端与所述第一节点连接,所述第三访问晶体管的第六端与所述第一位线连接;所述第四访问晶体管的第七端与所述第二节点连接,所述第四访问晶体管的第八端与所述第二位线连接;所述字线与所述第一控制端、第二控制端、第三控制端和第四控制端连接。

7、可选的,所述第一端和第二端分别为源极和漏极,所述第三端和第四端分别为源极和漏极,所述第五端和第六端分别为源极和漏极,所述第七端和第八端分别为源极和漏极;所述第一控制端、第二控制端、第三控制端和第四控制端为栅极。

8、可选的,还包括:第一锁存点,所述第一访问晶体管的第一端与所述第一锁存点连接,所述第三漏极和所述第四漏极与所述第一锁存点连接;第二锁存点,所述第二访问晶体管的第三端与所述第二锁存点连接,所述第一漏极和所述第二漏极与所述第二锁存点连接。

9、可选的,所述第一上拉晶体管和所述第二上拉晶体管为pmos;所述第一下拉晶体管和所述第二下拉晶体管为nmos。

10、可选的,所述第一访问晶体管、所述第二访问晶体管、所述第三访问晶体管和所述第四访问晶体管为nmos。

11、相应地,本发明技术方案还提供一种存储器,包括:存储阵列,所述存储阵列包括若干上述存储单元,所述存储单元呈阵列分布。

12、相应地,本发明技术方案还提供一种存储器结构,包括:衬底,所述衬底包括沿第一方向排列的第一区、第二区、第三区和第四区,所述第一方向平行于衬底表面;位于第三区的第一上拉晶体管;位于第二区的第二上拉晶体管;位于第四区的第一下拉晶体管、第二访问晶体管和第四访问晶体管,所述第一下拉晶体管与所述第一上拉晶体管电连接,所述第二访问晶体管和第四访问晶体管电连接;位于第一区的第二下拉晶体管、第一访问晶体管和第三访问晶体管,所述第二下拉晶体管与所述第二上拉晶体管电连接,所述第一访问晶体管和第三访问晶体管电连接,所述第一访问晶体管与所述第一下拉晶体管和所述第一上拉晶体管电连接,所述第二访问晶体管与所述第二下拉晶体管和所述第二上拉晶体管电连接;位于衬底上的第一位线,与所述第三访问晶体管电连接;位于衬底上的第二位线,与所述第四访问晶体管电连接;位于衬底上的字线结构,与所述第一访问晶体管、第二访问晶体管、第三访问晶体管和第四访问晶体管连接。

13、可选的,所述衬底包括:基底;位于基底第一区上的第一鳍部结构,位于基底第二区上的第二鳍部结构,位于基底第三区上的第三鳍部结构,位于基底第四区上的第四鳍部结构,所述第一鳍部结构、第二鳍部结构、第三鳍部结构和第四鳍部结构平行于第二方向,所述第二方向平行于衬底表面且与第一方向相互垂直。

14、可选的,所述第一上拉晶体管包括:横跨第三鳍部结构的第一栅极,所述第一栅极平行于第一方向;位于第一栅极两侧第三鳍部结构内的第一源掺杂区和第一漏掺杂区;所述第二上拉晶体管包括:横跨第二鳍部结构的第三栅极,所述第三栅极平行于第一方向;位于第三栅极两侧第二鳍部结构内的第三源掺杂区和第三漏掺杂区;所述第一下拉晶体管包括:横跨第四鳍部结构的第二栅极,所述第二栅极平行于第一方向,所述第二栅极与所述第一栅极相连接;位于第二栅极两侧第四鳍部结构内的第二源掺杂区和第二漏掺杂区;所述第二下拉晶体管包括:横跨第一鳍部结构的第四栅极,所述第四栅极平行于第一方向,所述第四栅极与所述第三栅极相连接;位于第四栅极两侧第一鳍部结构内的第四源掺杂区和第四漏掺杂区。

15、可选的,所述第一访问晶体管包括:横跨第一鳍部结构的第五栅极,所述第五栅极平行于第一方向;分别位于第五栅极两侧第一鳍部结构内的第五源漏掺杂区;所述第二访问晶体管包括:横跨第四鳍部结构的第六栅极,所述第六栅极平行于第一方向;分别位于第六栅极两侧第四鳍部结构内的第六源漏掺杂区。

16、可选的,所述第三访问晶体管包括:横跨第一鳍部结构的第七栅极,所述第七栅极平行于第一方向;分别位于第七栅极两侧第一鳍部结构内的第七源漏掺杂区;所述第四访问晶体管包括:横跨第四鳍部结构的第八栅极,所述第八栅极平行于第一方向;分别位于第八栅极两侧第四鳍部结构内的第八源漏掺杂区。

17、可选的,还包括:位于第一漏掺杂层上和第二漏掺杂层上的第一连接层,所述第一连接层电连接所述第一漏掺杂层和第二漏掺杂层,所述第一连接层还电连接所述第六栅极一侧的第六源漏掺杂区;位于第三漏掺杂层上和第四漏掺杂层上的第二连接层,所述第二连接层电连接所述第三漏掺杂层和第四漏掺杂层,所述第二连接层还电连接所述第五栅极一侧的第五源漏掺杂区;位于第一源掺杂层上的第一电源层,所述第一电源层与所述第一源掺杂层电连接;位于第二源掺杂层上的第一接地层,所述第一接地层与所述第二源掺杂层电连接;位于第三源掺杂层上的第二电源层,所述第二电源层与所述第三源掺杂层电连接;位于第四源掺杂层上的第二接地层,所述第二接地层与所述第四源掺杂层电连接;位于所述第五栅极另一侧的第五源漏掺杂区上和第七栅极一侧的第七源漏掺杂区上的第一节点层,所述第一节点层与所述第五栅极另一侧的第五源漏掺杂区和第七栅极一侧的第七源漏掺杂区电连接;位于第七栅极另一侧的第七源漏掺杂区上的第一位线,所述第一位线与所述第七栅极另一侧的第七源漏掺杂区电连接;位于第六栅极另一侧的第六源漏掺杂区上和第八栅极一侧的第八源漏掺杂区上的第二节点层,所述第二节点层电连接所述第六栅极另一侧的第六源漏掺杂区和第八栅极一侧的第八源漏掺杂区;位于第八栅极另一侧的第八源漏掺杂区上的第二位线,所述第二位线与所述第八栅极另一侧的第八源漏掺杂区电连接;所述第一连接层、第二连接层、第一电源层、第二电源层、第一接地层、第二接地层、第一节点层、第二节点层、第一位线和第二位线平行于第一方向。

18、可选的,还包括:位于第一连接层上的第一金属层,所述第一金属层电连接所述第一连接层、第三栅极和第四栅极;位于第二连接层上的第二金属层,所述第二金属层电连接所述第二连接层、第一栅极和第二栅极;位于第五栅极上和第七栅极上的第一字线,所述第一字线与所述第五栅极和第七栅极电连接;位于第六栅极上和第八栅极上的第二字线,所述第二字线与所述第六栅极和第八栅极电连接;所述第一金属层、第二金属层、第一字线和第二字线平行于第二方向。

19、可选的,所述衬底还包括:位于基底第一区上的第五鳍部结构,所述第一鳍部结构位于所述第五鳍部结构和第二鳍部结构之间,所述第五鳍部结构平行于第二方向;位于基底第四区上的第六鳍部结构,所述第四鳍部结构位于所述第六鳍部结构和第三鳍部结构之间,所述第六鳍部结构平行于第二方向。

20、可选的,所述第三访问晶体管包括:横跨第五鳍部结构的第九栅极,所述第九栅极平行于第一方向,所述第九栅极与所述第五栅极连接;分别位于第九栅极两侧第五鳍部结构内的第九源漏掺杂区;所述第四访问晶体管包括:横跨第六鳍部结构的第十栅极,所述第十栅极平行于第一方向,所述第十栅极与所述第六栅极连接;分别位于第十栅极两侧第六鳍部结构内的第十源漏掺杂区。

21、可选的,还包括:位于第一漏掺杂层上和第二漏掺杂层上的第一连接层,所述第一连接层电连接所述第一漏掺杂层上和第二漏掺杂层,所述第一连接层还电连接所述第六栅极一侧的第六源漏掺杂区;位于第三漏掺杂层上和第四漏掺杂层上的第二连接层,所述第二连接层电连接所述第三漏掺杂层上和第四漏掺杂层,所述第二连接层还电连接所述第五栅极一侧的第五源漏掺杂区;位于第一源掺杂层上的第一电源层,所述第一电源层与所述第一源掺杂层电连接;位于第二源掺杂层上的第一接地层,所述第一接地层与所述第二源掺杂层电连接;位于第三源掺杂层上的第二电源层,所述第二电源层与所述第三源掺杂层电连接;位于第四源掺杂层上的第二接地层,所述第二接地层与所述第四源掺杂层电连接;位于所述第五栅极另一侧的第五源漏掺杂区上和第七栅极一侧的第七源漏掺杂区上的第一节点层,所述第一节点层与所述第五栅极另一侧的第五源漏掺杂区和第七栅极一侧的第七源漏掺杂区电连接;位于第七栅极另一侧的第七源漏掺杂区上的第一位线,所述第一位线与所述第七栅极另一侧的第七源漏掺杂区电连接;位于第六栅极另一侧的第六源漏掺杂区上和第八栅极一侧的第八源漏掺杂区上的第二节点层,所述第二节点层电连接所述第六栅极另一侧的第六源漏掺杂区和第八栅极一侧的第八源漏掺杂区;位于第八栅极另一侧的第八源漏掺杂区上的第二位线,所述第二位线与所述第八栅极另一侧的第八源漏掺杂区电连接;所述第一连接层、第二连接层、第一电源层、第二电源层、第一接地层、第二接地层、第一节点层、第二节点层、第一位线和第二位线平行于第一方向。

22、可选的,还包括:位于第一连接层上的第一金属层,所述第一金属层电连接所述第一连接层、第三栅极和第四栅极;位于第二连接层上的第二金属层,所述第二金属层电连接所述第二连接层、第一栅极和第二栅极;所述字线结构包括:位于第七栅极上的第一字线,所述第一字线与所述第五栅极和第七栅极电连接;位于第八栅极上的第二字线,所述第二字线与所述第六栅极和第八栅极电连接;所述第一金属层、第二金属层、第一字线和第二字线平行于第二方向。

23、可选的,所述第一上拉晶体管和所述第二上拉晶体管为pmos;所述第一下拉晶体管和所述第二下拉晶体管为nmos;所述第一访问晶体管、所述第二访问晶体管、所述第三访问晶体管和所述第四访问晶体管为nmos。

24、相应地,本发明技术方案还提供一种存储器的工作方法,包括:在所述字线输入高电平,使得所述第一访问晶体管、第二访问晶体管、第三访问晶体管和第四访问晶体管导通;当所述第一访问晶体管、第二访问晶体管、第三访问晶体管和第四访问晶体管导通后,自所述第一位线及第二位线获取电流信号,以进行读取操作;在进行所述读取操作之后,在所述字线输入低电平,关断所述第一访问晶体管、第二访问晶体管、第三访问晶体管和第四访问晶体管,使所述存储单元进入空闲状态。

25、可选的,获取所述存储单元的读取结果之前,还包括:在所述第一位线及第二位线分别输入互为反相的电平信号,以进行写入操作。

26、与现有技术相比,本发明的技术方案具有以下有益效果:

27、本发明的技术方案的存储单元,在第一访问晶体管与第一位线之间串联了第三访问晶体管,在第二访问晶体管与第二位线之间串联了第四访问晶体管n6,使得通过第一访问晶体管和第二访问晶体管的电流减小,在读操作之后的空闲状态,所述第一节点为正电位,所述第二节点为正电位,减小了第一访问晶体管和第二访问晶体管的漏电流,使得存储单元的漏电流减小。

28、本发明的技术方案的存储器结构,在第一区增加了第三访问晶体管,在第四区增加了第四访问晶体管,使得通过第一访问晶体管和第二访问晶体管的电流减小,在读操作之后的空闲状态,所述第一节点为正电位,所述第二节点为正电位,减小了第一访问晶体管和第二访问晶体管的漏电流,使得存储单元的漏电流减小。

- 还没有人留言评论。精彩留言会获得点赞!