刷新控制电路及存储器的制作方法

本技术涉及存储器技术,尤其涉及一种刷新控制电路及存储器。

背景技术:

1、伴随存储器技术的发展,存储器被广泛应用在多种领域,比如,动态随机存取存储器(dynamic random access memory,简称dram)的使用非常广泛。

2、实际应用中,随着存储器的尺寸越来越小,集成度越来越高,相邻存储单元之间存在干扰,可能导致行锤击(row hammer,简称rh)漏洞。具体的,rh漏洞指当存储器的某一存储单元被多次反复读写时,可能导致其它存储单元中的数据发生翻转。因此,需要提供一种有效的刷新控制方案来控制执行rh防护操作,以避免存储器中的存储单元发生错误翻转。

技术实现思路

1、本技术的实施例提供一种刷新控制电路及存储器。

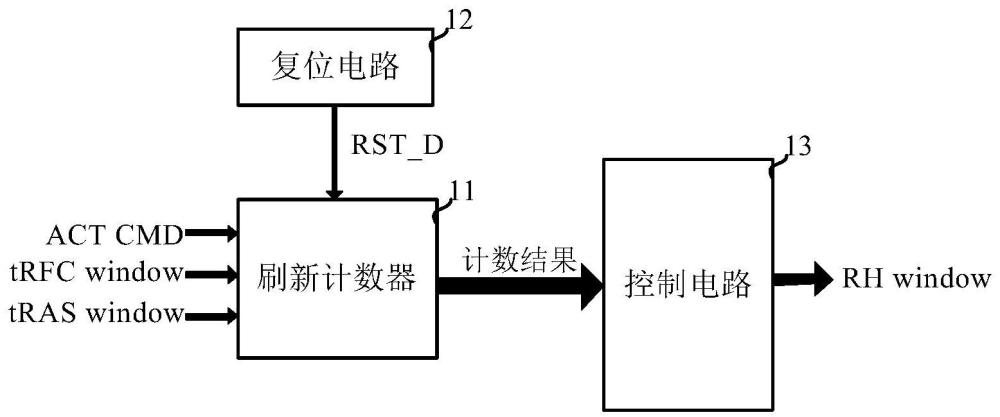

2、根据一些实施例,本技术第一方面提供刷新控制电路,包括:刷新计数器,接收激活命令、行激活窗口信号和刷新窗口信号,用于对刷新窗口信号的有效电平时段内且位于使能信号的有效电平时段内的行激活窗口信号的脉冲进行计数,输出计数结果;以及,响应于周期复位信号,执行计数复位;其中使能信号基于激活命令和周期复位信号生成;复位电路,复位电路的输入端与刷新计数器的输出端连接,复位电路的输出端与刷新计数器的复位端连接,用于在刷新计数器当前输出的计数结果达到预设次数时,输出周期复位信号;控制电路,控制电路的输入端与刷新计数器的输出端连接,用于根据刷新计数器当前输出的计数结果,输出防护刷新窗口信号;其中,当计数结果位于预设范围内时,防护刷新窗口信号处于有效电平。

3、在一些实施例中,刷新计数器,包括:使能电路,检测电路、脉冲产生电路和计数器;使能电路,接收激活命令和周期复位信号,用于基于激活命令和周期复位信号生成使能信号;其中,激活命令控制使能信号的有效电平的起始时刻,周期复位信号控制使能信号的有效电平的结束时刻;检测电路,接收使能信号、行激活窗口信号和刷新窗口信号,用于检测行激活窗口信号的脉冲是否位于刷新窗口信号的有效电平时段内以及是否位于使能信号的有效电平时段内;若位于,则输出行激活窗口信号的脉冲;脉冲产生电路,与检测电路的输出端连接,用于响应于检测电路输出的行激活窗口信号的脉冲到来,输出有效的计数时钟;计数器的时钟端与脉冲产生电路的输出端连接,计数器的复位端与复位电路连接,用于响应于有效的计数时钟累计计数,输出计数结果;以及,响应于周期复位信号执行计数复位。

4、在一些实施例中,检测电路包括:第一与门;第一与门的第一输入端接收刷新窗口信号,第一与门的第二输入端接收行激活窗口信号,第一与门的第三输入端与使能电路的输出端连接,第一与门的输出端与脉冲产生电路连接。

5、在一些实施例中,使能电路包括:第一非门、第二非门、第一与非门和第二与非门;第一非门的输入端接收激活命令,第一非门的输出端与第一与非门的第一输入端连接;第二非门的输入端接收周期复位信号,第二非门的输出端与第二与非门的第一输入端连接;第一与非门的第二输入端与第二与非门的输出端连接,第一与非门的输出端与第一与门的第三输入端连接;第二与非门的第二输入端与第一与非门的输出端连接。

6、在一些实施例中,脉冲产生电路,包括:第三非门、延时单元以及第二与门;第二与门的第一输入端与检测电路的输出端连接,第二与门的第二输入端与延时单元的输出端连接;第三非门的输入端与检测电路的输出端连接,第三非门的输出端与延时单元的输入端连接,延时单元的延时时长用于控制计数时钟的脉冲宽度;第二与门的输出端作为脉冲生成电路的输出端与计数器的时钟端连接。

7、在一些实施例中,计数器包括:多级第一触发器;首级第一触发器的时钟端与脉冲产生电路的输出端连接,其它第一触发器的时钟端与上一级第一触发器的反相输出端连接;每个第一触发器的输入端与该第一触发器的反相输出端连接,每级第一触发器的同相输出端输出的值组成计数器的输出,该输出为计数结果的二进制表示;每个第一触发器的复位端与复位电路的输出端连接。

8、在一些实施例中,复位电路包括:复位生成电路和输出电路;复位生成电路,与刷新计数器的输出端连接并接收周期设定信号,用于在刷新计数器输出的计数结果达到周期设定信号对应的预设次数时,向输出电路输出初始复位信号;输出电路的输入端与复位生成电路的输出端连接,输出电路用于在刷新窗口信号的有效电平时段内,响应于行激活窗口信号的脉冲结束,将初始复位信号输出为周期复位信号。

9、在一些实施例中,周期设定信号包括两个比特,预设次数包括四个取值,分别记为第一次数、第二次数、第三次数和第四次数。

10、在一些实施例中,复位生成电路包括:周期译码电路,周期译码电路接收周期设定信号,用于根据周期设定信号输出第一次数的选择信号、第二次数的选择信号、第三次数的选择信号以及第四次数的选择信号;每个次数对应的子译码器;每个子译码器接收计数结果的至少一个比特,用于在接收的至少一个比特当前表征的数值与该子译码器对应的次数一致时,输出该次数的标志信号;每个次数对应的第三与门;每个第三与门接收对应的次数的选择信号和对应的次数的标志信号;或运算单元,或运算单元的输入端分别与所有第三与门的输出端连接,或运算单元的输出端用于输出初始复位信号。

11、在一些实施例中,周期译码电路包括:第一或非门,第一或非门的第一输入端接收周期设定信号的一个比特,第一或非门的第二输入端接收周期设定信号的另一个比特,第一或非门用于输出第一次数的选择信号;第四非门和第二或非门,第四非门的输入端与第一或非门的第一输入端连接,第四非门的输出端与第二或非门的第一输入端连接,第二或非门的第二输入端与第一或非门的第二输入端连接,第二或非门用于输出第二次数的选择信号;第五非门和第三或非门,第三或非门的第一输入端与第一或非门的第一输入端连接,第五非门的输入端与第一或非门的第二输入端连接,第五非门的输出端与第三或非门的第二输入端连接,第三或非门用于输出第三次数的选择信号;第三与非门和第六非门,第三与非门的第一输入端与第一或非门的第一输入端连接,第三与非门的第二输入端与第一或非门的第二输入端连接,第三与非门的输出端与第六非门的输入端连接,第六非门用于输出第四次数的选择信号。

12、在一些实施例中,第一次数对应的子译码器包括第四与门;第四与门的输入端分别接收计数结果的第3比特和第2比特,第四与门的输出端用于输出第一次数的标志信号;第二次数对应的子译码器包括第五与门;第五与门的输入端分别接收计数结果的第4比特和第3比特,第五与门的输出端用于输出第二次数的标志信号;第三次数对应的子译码器包括第六与门;第六与门的输入端分别接收计数结果的第5比特和第2比特,第六与门的输出端用于输出第三次数的标志信号;第四次数对应的子译码器包括第七与门;第七与门的输入端分别接收计数结果的第5比特和第4比特,第七与门的输出端用于输出第四次数的标志信号。

13、在一些实施例中,输出电路包括:第七非门,第七非门的输入端接收行激活窗口信号;第八与门,第八与门的第一输入端接收刷新窗口信号,第八与门的第二输入端与第七非门的输出端连接;第二触发器,第二触发器的输入端与复位生成电路的输出端连接,第二触发器的输出端与刷新计数器的复位端连接,第二触发器的时钟端与第八与门的输出端连接。

14、在一些实施例中,预设范围为4至6。

15、在一些实施例中,控制电路包括:第一多输入与门、第二多输入与门、第三多输入与门以及第一多输入或门;第一多输入与门具有多个输入端,第一多输入与门的多个输入端分别接收计数结果的第1比特的反相信号、第2比特的反相信号以及第3比特;第二多输入与门具有多个输入端,第二多输入与门的多个输入端分别接收计数结果的第1比特、第2比特的反相信号以及第3比特;第三多输入与门具有多个输入端,第三多输入与门的多个输入端分别接收计数结果的第1比特的反相信号、第2比特以及第3比特;第一多输入或门的第一输入端与第一多输入与门的输出端连接,第一多输入或门的第二输入端与第二多输入与门的输出端连接,第一多输入或门的第三输入端与第三多输入与门的输出端连接,第一多输入或门的输出端用于输出防护刷新窗口信号。

16、根据一些实施例,本技术第二方面提供一种存储器,包括:指令译码器、刷新操作模块、存储块控制模块以及如前的刷新控制电路;指令译码器用于根据外部指令,解析生成激活命令和刷新指令;刷新操作模块与指令译码器连接,用于响应于刷新指令,输出刷新窗口信号和行激活窗口信号;刷新控制电路与指令译码器、刷新操作模块和存储块控制模块连接,用于根据激活命令、刷新窗口信号和行激活窗口信号,输出防护刷新窗口信号;存储块控制模块与刷新控制电路和刷新操作模块连接,用于响应于刷新操作模块输出的信号执行刷新,以及响应于防护刷新窗口信号执行行锤击防护刷新。

17、本技术实施例提供的刷新控制电路及存储器中,包括刷新计数器、复位电路以及控制电路,刷新计数器对既在刷新窗口信号且在使能信号的有效电平时段内的行激活窗口信号的脉冲进行计数,输出计数结果;复位电路在计数结果达到预设次数时,指示刷新计数器复位,控制电路则在计数结果位于预设范围内时,输出有效的防护刷新窗口信号,以在防护刷新窗口信号的有效电平时段内执行行锤击防护刷新。上述方案能够实现行锤击防护刷新,并且基于本方案支持设定预设次数和预设范围,可以在每轮预设次数的刷新中选取一定数量的刷新用于执行行锤击防护刷新,从而在实现行锤击防护刷新的同时,能够调节防护刷新的执行频率,提高行锤击防护的灵活性。

- 还没有人留言评论。精彩留言会获得点赞!