信号处理电路及存储器的制作方法

本公开涉及但不限定于一种信号处理电路及存储器。

背景技术:

1、存储器是存储数据的半导体器件,它可以根据接收到的命令/地址信号(command/address,ca)执行相应的数据处理,包括但不限于数据读取、数据写入和其他一些控制处理。存储器不仅会接收命令/地址信号,还会接收到时钟信号clk,以根据时钟信号对命令地址信号进行采样,并根据采样得到的命令地址信号进行数据处理。

2、现有技术中,存储器中设置有命令处理电路、时钟缓存电路、延迟电路和命令采样电路。其中,命令处理电路用于接收命令/地址信号以对其进行预处理以输出第一命令信号。时钟缓存电路用于接收时钟信号并缓存。延迟电路用于从时钟缓存电路中获取时钟信号并进行延迟,并将延迟后的时钟信号作为采样时钟信号输出,以使采样时钟信号在第一命令信号之后到达命令采样电路。命令采样电路用于根据采样时钟信号对第一命令信号进行采样,以生成并输出第二命令信号。

3、然而,上述存储器存在电路耗电较高的问题。

技术实现思路

1、本公开一实施例提供一种信号处理电路及存储器,用于降低电路耗电。

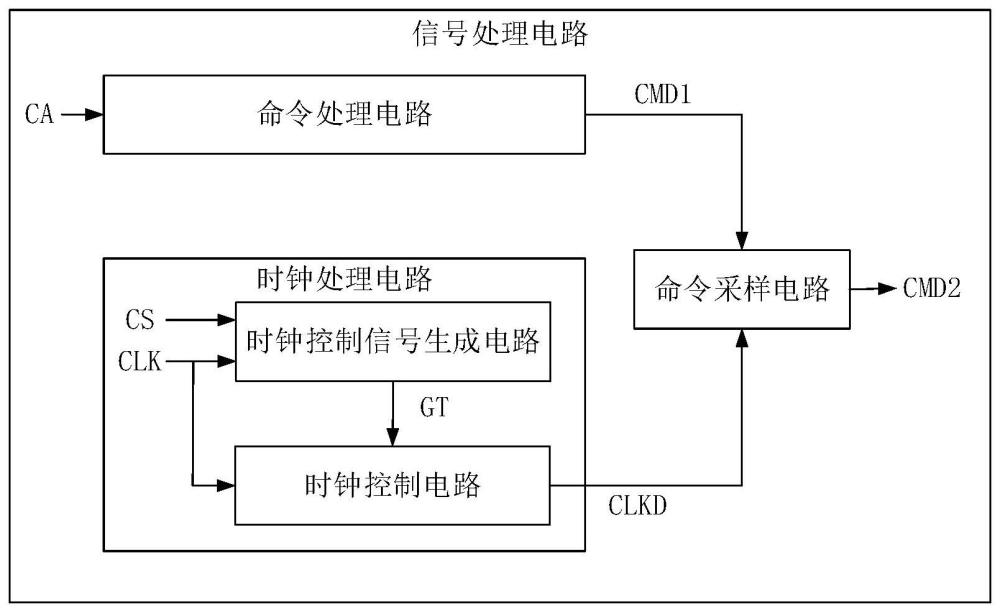

2、第一方面,本公开提供一种信号处理电路,包括:命令处理电路、时钟处理电路和命令采样电路;

3、所述命令处理电路,用于接收命令/地址信号ca,基于所述命令/地址信号生成并输出第一命令信号;

4、所述时钟处理电路,用于接收第一片选信号cs和第一时钟信号clk,基于所述第一片选信号和所述第一时钟信号生成时钟控制信号gt,并根据所述时钟控制信号对所述第一时钟信号进行处理,生成并输出采样时钟信号clkd;

5、所述命令采样电路,分别与所述命令处理电路和所述时钟处理电路耦接,基于所述采样时钟信号对所述第一命令信号进行采样以输出第二命令信号;

6、其中,所述时钟控制信号用于控制在所述第一命令信号到达所述命令采样电路前不输出所述采样时钟信号,以及在所述第一命令信号到达所述命令采样电路时输出所述采样时钟信号。

7、在一些实施例中,所述时钟处理电路包括:时钟控制信号生成电路和时钟控制电路;

8、所述时钟控制信号生成电路,用于接收所述第一片选信号和所述第一时钟信号,根据所述第一片选信号和所述第一时钟信号,生成并输出所述时钟控制信号;其中,所述时钟控制信号处于有效电平的起始时刻早于所述第一命令信号到达所述命令采样电路的时刻;

9、所述时钟控制电路,与所述时钟控制信号生成电路连接,用于根据所述时钟控制信号,控制是否基于所述第一时钟信号生成并输出所述采样时钟信号。

10、在一些实施例中,所述时钟控制信号生成电路包括:解码窗口信号生成电路和时钟控制信号生成器;

11、所述解码窗口信号生成电路,用于对所述第一片选信号的脉冲宽度进行调整处理,生成解码窗口信号,并将所述解码窗口信号从其输出端输出;

12、所述时钟控制信号生成器,用于根据第一时钟信号和所述解码窗口信号生成所述时钟控制信号,其中,所述时钟控制信号处于有效电平的起始时刻由所述解码窗口信号处于有效电平的起始时刻确定,且所述时钟控制信号的脉冲宽度等于预设数量的所述第一时钟信号的时钟周期,在所述时钟控制信号处于有效电平期间完成所述第二命令信号对应的处理操作。

13、在一些实施例中,所述时钟控制信号生成器包括时钟计数器、sr锁存器和第一可调延迟电路;

14、所述时钟计数器,用于接收解码窗口拓展信号和所述第一时钟信号,在所述解码窗口拓展信号处于有效电平后对所述第一时钟信号进行计数以生成计数值,并在所述计数值达到预设数量时产生复位信号,并将所述复位信号从其输出端输出;其中,所述时钟计数器基于所述复位信号进行复位操作;

15、所述sr锁存器,与所述时钟计数器连接,用于根据所述解码窗口信号和所述复位信号生成所述解码窗口拓展信号;

16、所述第一可调延迟电路,与所述sr锁存器连接,用于对所述解码窗口拓展信号进行延迟得到所述时钟控制信号。

17、在一些实施例中,所述第一可调延迟电路包括多个串联的反相器;

18、所述sr锁存器,包括:第一或非门、第二或非门和第一反相器,所述第一或非门的两个输入端分别连接所述解码窗口信号生成电路的输出端和所述第二或非门的输出端,所述第二或非门的两个输入端分别连接所述时钟计数器的输出端和所述第一或非门的输出端,所述第一或非门的输出端连接至所述第一反相器的输入端,所述第一反相器用于输出所述解码窗口拓展信号。

19、在一些实施例中,所述时钟处理电路还包括:第二可调延迟电路,分别与所述时钟控制电路的输出端和所述命令采样电路的输入端耦接,用于将所述时钟控制电路输出的所述采样时钟信号进行延迟,以将延迟后的采样时钟信号输入给所述命令采样电路。

20、在一些实施例中,当所述第一可调延迟电路包括奇数个反相器时,所述时钟控制电路包括:与非逻辑电路,用于将所述时钟控制信号和所述第一时钟信号进行与非逻辑运算,得到所述采样时钟信号;

21、当所述第一可调延迟电路包括偶数个反相器时,所述时钟控制电路包括与逻辑处理电路,用于将所述时钟控制信号和所述第一时钟信号进行与逻辑运算,得到所述采样时钟信号。

22、在一些实施例中,所述解码窗口信号生成电路包括:片选采样控制电路、片选信号采样电路和逻辑处理电路;

23、所述片选采样控制电路,用于接收所述第一时钟信号,并基于所述第一时钟信号生成多个片选采样控制信号;

24、所述片选信号采样电路,与所述片选采样控制电路连接,用于在所述多个片选采样控制信号的控制下,对所述第一片选信号进行采样,生成并输出多个第二片选信号,每个所述第二片选信号的脉冲宽度大于所述第一片选信号的脉冲宽度;

25、所述逻辑处理电路,与所述片选信号采样电路连接,用于对多个所述第二片选信号和所述第一片选信号进行逻辑运算生成所述解码窗口信号,在所述第一片选信号和/或至少一个所述第二片选信号处于有效电平时,所述解码窗口信号处于有效电平。

26、在一些实施例中,所述片选采样控制电路包括第一片选采样控制子电路和第二片选采样控制子电路;

27、所述第一片选采样控制子电路,包括依次串联的n级第二反相器,第一级所述第二反相器用于接收所述第一时钟信号,每一级所述第二反相器的输出信号作为一个所述片选采样控制信号;

28、所述第二片选采样控制子电路,包括依次串联的n级第三反相器,第一级所述第三反相器用于接收第二时钟信号,所述第二时钟信号为所述第一时钟信号的反相信号,每一级所述第三反相器的输出信号作为一个所述片选采样控制信号;

29、其中,所述第二反相器和所述第三反相器均为相同的反相器,对输入信号反相输出的延迟时间均为预设延迟;

30、所述片选采样控制信号包括第一片选采样控制信号和第二片选采样控制信号;所述第一时钟信号、奇数级所述第三反相器的输出信号和偶数级所述第二反相器的输出信号共同组成n+1个所述第一片选采样控制信号,n+1个所述第一片选采样控制信号依次具有预设延迟;所述第二时钟信号、奇数级所述第二反相器的输出信号和偶数级所述第三反相器的输出信号共同组成n+1个所述第二片选采样控制信号,n+1个所述第二片选采样控制信号依次具有预设延迟。

31、在一些实施例中,所述片选信号采样电路包括:第一片选采样子电路和第二片选采样子电路;

32、所述第一片选采样子电路包括:级联的n+1级第一触发器,第一级所述第一触发器的输入端接收所述第一片选信号,每一级所述第一触发器的输出端连接下一级所述第一触发器的输入端,每一级所述第一触发器的时钟端接收一个所述第一片选采样控制信号,每一级所述第一触发器的输出端输出一个所述第二片选信号;其中,第i级所述第一触发器的时钟端接收第(n+2-i)个所述第一片选采样控制信号,i为小于等于n+1的正整数;

33、所述第二片选采样子电路包括:级联的n+1级第二触发器,第一级所述第二触发器的输入端接收所述第一片选信号,每一级所述第二触发器的输出端连接下一级所述第二触发器的输入端,每一级所述第二触发器的时钟端接收一个所述第二片选采样控制信号,每一级所述第二触发器的输出端输出一个所述第二片选信号;其中,第j级所述第二触发器的时钟端接收第(n+2-j)个所述第二片选采样控制信号,j为小于等于n+1的正整数。

34、在一些实施例中,所述第一片选信号和所述第二片选信号的有效电平为低电平,所述解码窗口信号的有效电平为高电平,所述逻辑处理电路包括:第一与逻辑电路、第二与逻辑电路和与非逻辑电路;

35、所述第一与逻辑电路,用于接收所述第一片选采样子电路输出的n+1个所述第二片选信号,以将n+1个所述第二片选信号进行与逻辑运算,生成第一结果信号;

36、所述第二与逻辑电路,用于接收所述第二片选采样子电路输出的n+1个所述第二片选信号,以将n+1个所述第二片选信号进行与逻辑运算,生成第二结果信号;

37、所述与非逻辑电路,输入端连接至所述第一与逻辑电路和所述第二与逻辑电路,用于将所述第一结果信号、所述第二结果信号和所述第一片选信号进行与非逻辑运算,生成所述解码窗口信号。

38、第二方面,本公开提供一种存储器,包括前述第一方面的信号处理电路。

39、本公开实施例提供一种信号处理电路及存储器,包括命令处理电路、时钟处理电路和命令采样电路;命令处理电路,用于接收命令/地址信号ca,基于命令/地址信号生成并输出第一命令信号;时钟处理电路,用于接收第一片选信号cs和第一时钟信号clk,基于第一片选信号和第一时钟信号生成时钟控制信号gt,并根据时钟控制信号对第一时钟信号进行处理,生成并输出采样时钟信号clkd;命令采样电路,分别与命令处理电路和时钟处理电路耦接,基于采样时钟信号对第一命令信号进行采样以输出第二命令信号。其中,时钟控制信号用于控制在第一命令信号到达命令采样电路前不输出采样时钟信号,以及在第一命令信号到达命令采样电路时输出采样时钟信号。因此,可以降低信号处理电路的耗电。

- 还没有人留言评论。精彩留言会获得点赞!