数据缓冲结构及存储器的制作方法

本公开涉及半导体电路设计领域,特别涉及一种数据缓冲结构及存储器。

背景技术:

1、在dram的设计中,数据缓冲电路(data buffer)是数据输入和数据输出的通道,是用来接收外部数据和读取内部数据的重要接口。

2、在ddr5/lpddr5的电路中,数据缓冲电路包括决策反馈均衡模块(decisionfeedback equalization,dfe),dfe是一种通过使用在先数据来反馈处理在后数据,从而来减少码间干扰的方法。采用dfe技术有利于张来数据眼图,增大时域跨度和电压域跨度,保证内存总线能够以更高的传输速率进行信号传输。

3、对于dram而言,数字眼图用于存储器的性能分析,数字眼图可以基于数据缓冲电路输入端波形的眼图结合临界比较时间推导获取。

4、然而,当dfe开启后,数据从“0”跳转到“1”的临界比较时间会被缩短,而数据从“1”跳转到“0”的临界比较时间不变,这一非对称的数据跳转的时间变化,使得当dfe开启后,数字眼图的不对称性(数字眼图的左右不对称)增加,非对称的数字眼图不利于存储器应用时的训练过程。

技术实现思路

1、本公开实施例提供一种数据缓冲结构及存储器,以优化dfe开启后的临界比较时间,从而提高数字眼图的对称性。

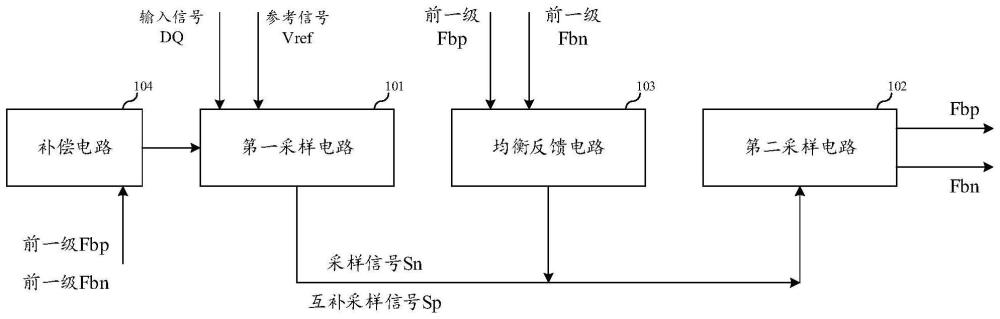

2、本公开一实施例提供了一种数据缓冲结构,包括:多个级联的数据缓冲单元,每一数据缓冲单元包括:第一采样电路,被配置为,基于输入信号和参考信号,生成采样信号和互补采样信号;其中,若输入信号的电位大于参考信号的电位,则生成的互补采样信号的电位大于采样信号的电位,若参考信号的电位大于输入信号的电位,则生成的采样信号的电位大于互补采样信号的电位;第二采样电路,被配置为,基于采样信号和互补采样信号,生成数据信号和互补数据信号;其中,若采样信号的电位大于互补采样信号的电位,则生成的互补数据信号的电位大于数据信号的电位,若互补采样信号的电位大于采样信号的电位,则生成的数据信号的电位大于互补数据信号的电位;均衡反馈电路,被配置为,基于前一级数据缓冲单元输出的数据信号和互补数据信号,反馈调节采样信号和互补采样信号,以减弱相邻输入信号之间的码间干扰;补偿电路,连接第一采样电路,被配置为,增大采样信号和互补采样信号的变化速率。

3、通过补偿电路增大采样信号和互补采样信号的变化速率,相当于缩短了临界比较时间,因此,新增补偿电路后且均衡反馈电路开启后,临界比较时间不对称变化的程度减小,从而在一定程度上提高数字眼图的对称性。

4、例如,第一采样电路,包括:第一开关晶体管,第一端子用于接收第一电源信号,控制端用于接收时钟信号;第一p型晶体管,第一端子耦接第一开关晶体管的第二端子,控制端用于接收输入信号;第二p型晶体管,第一端子耦接第一开关晶体管的第二端子,控制端用于接收参考信号;第一n型晶体管,第一端子耦接第一p型晶体管的第二端子,并用于输出采样信号,第二端子用于接收第二电源信号,控制端用于接收时钟信号;第二n型晶体管,第一端子耦接第二p型晶体管的第二端子,并用于输出互补采样信号,第二端子用于接收第二电源信号,控制端用于接收时钟信号;其中,第一电源信号提供的电源电压大于第二电源信号提供的电源电压。

5、例如,补偿电路,包括:第一电流补偿晶体管,第一端子用于接收第三电源信号,第二端子耦接第一开关晶体管的第二端子,控制端用于接收补充控制信号;其中,补充控制信号基于前一级数据缓冲单元输出的数据信号或互补数据信号生成,第三电源信号提供的电源电压大于第二电源信号提供的电源电压。

6、例如,补偿电路,包括:第二电流补偿晶体管,第一端子耦接第一n型晶体管和第二n型晶体管的第二端子,第二端子用于接收第二电源信号,控制端用于接收补充控制信号;其中,补充控制信号基于前一级数据缓冲单元输出的数据信号和互补数据信号生成。

7、例如,补偿电路,包括:第二开关晶体管,第一端子用于接收第一电源信号,控制端用于接收第一延时信号,第一延时信号基于时钟信号经过预设延时生成,第二开关晶体管为p型晶体管;第一控制晶体管,第一端子耦接第二开关晶体管的第二端子,第二端子耦接第二控制晶体管的控制端,控制端用于接收采样信号;第二控制晶体管的第一端子耦接第二开关晶体管的第二端子,第二端子耦接第一控制晶体管的控制端,控制端用于接收互补采样信号。

8、例如,补偿电路,包括:第三控制晶体管,第一端子耦接第四控制晶体管的控制端,控制端用于接收采样信号;第二控制晶体管的第一端子耦接第三控制晶体管的控制端,控制端用于接收互补采样信号;第三开关晶体管,第一端子耦接第三控制晶体管和第四控制晶体管的第二端子,第二端子用于接收第二电源信号,控制端用于接收第二延时信号,第二延时信号基于时钟信号经过预设延时生成。

9、例如,均衡反馈电路,包括:第四开关晶体管,第一端子用于接收第一电源信号,控制端用于接收均衡时钟信号,均衡时钟信号用于驱动均衡反馈电路;第一反馈控制晶体管,第一端子耦接第四开关晶体管的第二端子,控制端用于接收前一级数据缓冲单元输出的互补数据信号;第一调整晶体管组,包括多个并联的第一调整晶体管,每一第一调整晶体管基于第一调整信号组控制,以改变第一调整晶体管组的导通程度;其中,第一调整晶体管组的第一端子耦接第一反馈控制晶体管的第二端子,第二端子耦接第一n型晶体管的第一端子;第二反馈控制晶体管,第一端子耦接第四开关晶体管的第二端子,控制端用于接收前一级数据缓冲单元输出的数据信号;第二调整晶体管组,包括多个并联的第二调整晶体管,每一第二调整晶体管基于第二调整信号组控制,以改变第一调整晶体管组的导通程度;其中,第二调整晶体管组的第一端子耦接第二反馈控制晶体管的第二端子,第二端子耦接第二n型晶体管的第一端子。

10、例如,第一调整晶体管组中第一调整晶体管的宽长比大于第一反馈控制晶体管的宽长比,第二调整晶体管组中调整晶体管的宽长比大于第二反馈控制晶体管的宽长比。

11、例如,第一调整晶体管组中调整晶体管的宽长比依次呈2倍比例设置。

12、例如,均衡反馈电路,还包括:第三反馈控制晶体管,第一端子耦接第一调整晶体管组的第二端子,控制端用于接收前一级数据缓冲单元输出的互补数据信号;第四反馈控制晶体管,第一端子耦接第二调整晶体管组的第二端子,控制端用于接收前一级数据缓冲单元输出的数据信号;其中,第三反馈控制晶体管和第一反馈控制晶体管的晶体管类型不同,第四反馈控制晶体管和第二反馈控制晶体管的晶体管类型不同;第五开关晶体管,第一端子耦接第三反馈控制晶体管和第四反馈控制晶体管的第二端子,第二端子用于接收第二电源信号,控制端用于接收均衡时钟信号,均衡时钟信号用于驱动均衡反馈电路;其中,第一电源信号提供的电源电压大于第二电源信号提供的电源电压。

13、例如,第三反馈控制晶体管的宽长比小于第一反馈控制晶体管的宽长比,第四反馈控制晶体管的宽长比小于第二反馈控制晶体管的宽长比。

14、例如,均衡反馈电路,包括:第一调整晶体管组,包括多个并联的调整晶体管,每一调整晶体管基于第一调整信号组控制,以改变第一调整晶体管组的导通程度;其中,第一调整晶体管组的第一端子耦接第一n型晶体管的第一端子;第二调整晶体管组,包括多个并联的调整晶体管,每一调整晶体管基于第二调整信号组控制,以改变第一调整晶体管组的导通程度;其中,第二调整晶体管组的第一端子耦接第二n型晶体管的第一端子;第三反馈控制晶体管,第一端子耦接第一调整晶体管组的第二端子,控制端子用于接收前一级数据缓冲单元输出的互补数据信号;第四反馈控制晶体管,第一端子耦接第二调整晶体管组的第二端子,控制端子用于接收前一级数据缓冲单元输出的数据信号;第五开关晶体管,第一端子耦接第三反馈控制晶体管和第四反馈控制晶体管的第二端子,第二端子用于接收第二电源信号,控制端用于接收均衡时钟信号,均衡时钟信号用于驱动均衡反馈电路。

15、例如,第一调整晶体管组中调整晶体管的宽长比大于第三反馈控制晶体管的宽长比,第二调整晶体管组中调整晶体管的宽长比大于第四反馈控制晶体管的宽长比。

16、本公开另一实施例还提供了一种存储器,包括上述实施例提供的数据缓冲结构,以优化dfe开启后的临界比较时间,从而提高数字眼图的对称性。

- 还没有人留言评论。精彩留言会获得点赞!