刷新控制电路及存储器的制作方法

本技术涉及但不限定于一种刷新控制电路及存储器。

背景技术:

1、存储器用于存储数据,一些存储器可以临时性的存储数据,为了避免这些存储器丢失数据,需要不断对存储器进行数据刷新。这里的数据刷新可以理解为从存储器中读取数据,以重写写入相同数据的过程。

2、现有技术中,存储器中设置有刷新控制电路,以控制存储器进行数据刷新。具体地,当刷新控制电路接收到同存储体刷新(same bank refresh,refsb)命令时,对各存储组中指定存储体进行数据刷新。当刷新控制电路接收到全存储体刷新(all bank refresh,refab)命令时,对各存储组中的所有存储体均进行数据刷新。在进行同存储体刷新的过程中,如果接收到全存储体刷新命令时,对各存储组中所有存储体重新进行数据刷新。

3、然而,上述方案可能会导致存储器的功耗较高。

技术实现思路

1、本技术一实施例提供一种刷新控制电路及存储器,以降低存储器的功耗。

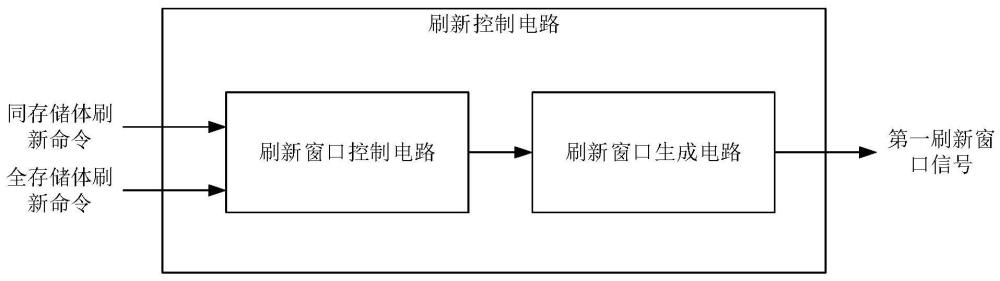

2、第一方面,本技术实施例提供一种刷新控制电路,包括:

3、刷新窗口控制电路和刷新窗口生成电路;

4、所述刷新窗口控制电路的输出端连接至所述刷新窗口生成电路的输入端,所述刷新窗口控制电路用于接收同存储体刷新命令和全存储体刷新命令,以在执行所述同存储器刷新命令对应的同存储体刷新过程中,接收到所述全存储体刷新命令时,控制所述刷新窗口生成电路向已完成同存储体刷新的存储体输出具有第一电平的第一刷新窗口信号,在所述第一刷新窗口信号处于第一电平时,已完成同存储体刷新的所述存储体停止数据刷新。

5、在一实施例中,所述刷新窗口生成电路包括:刷新窗口生成子电路和刷新窗口输出电路;

6、所述刷新窗口生成子电路用于接收刷新命令,以根据所述刷新命令生成第二刷新窗口信号,所述刷新命令为所述同存储体刷新命令或所述全存储体刷新命令;

7、所述刷新窗口输出电路的两个输入端分别连接至所述刷新窗口控制电路的输出端和所述刷新窗口生成子电路的输出端,用于接收所述刷新窗口控制电路输出的刷新窗口控制信号,以及所述刷新窗口生成子电路输出的所述第二刷新窗口信号,以在所述刷新窗口控制信号的控制下,向已完成同存储体刷新的所述存储体输出具有所述第一电平的所述第一刷新窗口信号,向未完成同存储体刷新的所述存储体输出具有第二电平的第一刷新窗口信号,在所述第一刷新窗口信号处于所述第二电平时,未完成同存储体刷新的所述存储体执行数据刷新。

8、在一实施例中,当所述刷新窗口控制信号为高电平有效时,所述刷新窗口输出电路包括第一反相电路和第一与逻辑电路;

9、所述第一反相电路的输入端连接至所述刷新窗口控制电路的输出端,用于接收所述刷新窗口控制电路输出的所述刷新窗口控制信号,以生成所述刷新窗口控制信号的反相信号;

10、所述第一与逻辑电路的两个输入端分别连接至所述第一反相电路的输出端和所述刷新窗口生成子电路的输出端,用于接收所述第一反相电路输出的所述刷新窗口控制信号的反相信号,以及,所述刷新窗口生成子电路输出的所述第二刷新窗口信号,以通过与逻辑运算生成所述第一刷新窗口信号。

11、在一实施例中,所述刷新窗口控制电路包括:同存储体刷新窗口生成电路和窗口控制信号输出电路;

12、所述同存储体刷新窗口生成电路用于接收所述同存储体刷新命令,以根据所述同存储体刷新命令生成同存储体刷新窗口信号,所述同存储体刷新窗口信号处于第二电平时,与所述同存储体刷新窗口信号对应的所述存储体执行同存储体刷新;

13、所述窗口控制信号输出电路用于接收所述同存储体刷新窗口生成电路输出的所述同存储体刷新窗口信号和所述全存储体刷新命令,以在所述同存储体刷新窗口信号处于第二电平的过程中接收到所述全存储体刷新命令时,输出具有所述第二电平的所述刷新窗口控制信号。

14、在一实施例中,所述窗口控制信号输出电路包括:重复刷新判断电路和窗口控制信号输出子电路;

15、所述重复刷新判断电路用于接收所述同存储体刷新窗口信号和所述全存储体刷新命令,以在所述同存储体刷新窗口信号和所述全存储体刷新命令均处于第二电平时,输出具有所述第二电平的重复刷新指示信号;

16、所述窗口控制信号输出子电路的输入端连接至所述重复刷新判断电路的输出端,用于接收所述重复刷新判断电路输出的重复刷新指示信号,以在所述重复刷新指示信号处于所述第二电平时,输出具有所述第二电平的刷新窗口控制信号。

17、在一实施例中,所述窗口控制信号输出子电路包括:第一锁存器;所述窗口控制信号输出电路还包括窗口控制复位信号生成电路;

18、所述窗口控制复位信号生成电路用于接收所述刷新窗口生成子电路输出的所述第二刷新窗口信号和行激活脉冲信号,以在所述行激活脉冲信号中的脉冲数量大于或等于所述存储体已完成同存储体刷新的行数时,输出窗口控制复位信号;

19、所述第一锁存器的置位端和复位端,分别连接至所述重复刷新判断电路的输出端和所述窗口控制复位信号生成电路的输出端,用于在所述重复刷新指示信号处于所述第二电平时,输出具有所述第二电平的刷新窗口控制信号,或,在所述窗口控制复位信号处于所述第二电平时,输出具有所述第一电平的刷新窗口控制信号。

20、在一实施例中,所述窗口控制复位信号生成电路包括:第一脉冲信号生成电路和计数电路;

21、所述第一脉冲信号生成电路用于接收所述刷新窗口生成子电路输出的所述第二刷新窗口信号、所述行激活脉冲信号和所述窗口控制信号输出电路输出的所述刷新窗口控制信号,以在所述刷新窗口控制信号处于所述第二电平时输出与所述行激活脉冲信号对应的第一脉冲信号;

22、所述计数电路的输入端连接至所述第一脉冲信号生成电路的输出端,用于接收所述第一脉冲信号,以对所述第一脉冲信号中的脉冲数量进行计数,并在计数到目标数值时,输出具有所述第二电平的所述窗口控制复位信号,所述目标数值为所述存储体已完成同存储体刷新的行数。

23、在一实施例中,所述第一脉冲信号生成电路,包括:第二脉冲信号生成电路和第一脉冲信号生成子电路;

24、所述第二脉冲信号生成电路用于接收所述第二刷新窗口信号和所述行激活脉冲信号,以生成第二脉冲信号;

25、所述第一脉冲信号生成子电路的多个输入端分别连接至所述第二脉冲信号生成电路的输出端和所述窗口控制信号输出电路的输出端,用于接收所述第二脉冲信号和所述刷新窗口控制信号,以生成所述第一脉冲信号。

26、在一实施例中,所述第二脉冲信号生成电路包括:多个与所述存储体分别对应的第二与逻辑电路,以及或逻辑电路;

27、每个所述第二与逻辑电路的一个输入端连接至对应所述存储体的所述刷新窗口生成子电路的输出端,用于接收对应所述刷新窗口生成子电路输出的所述第二刷新窗口信号,另一个输入端接收所述行激活脉冲信号,以通过与逻辑运算生成对应所述存储体的行刷新信号;

28、所述或逻辑电路的多个输入端连接至所述存储组中各所述存储体的所述第二与逻辑电路的输出端,用于接收各所述存储体的所述行刷新信号,以通过或逻辑运算生成所述第二脉冲信号。

29、在一实施例中,所述刷新窗口控制电路还包括:同存储体刷新复位信号生成电路,所述同存储体刷新窗口生成电路为第二锁存器,所述第二锁存器的置位端用于接收所述同存储体刷新命令,所述第二锁存器的复位端连接至所述同存储体刷新复位信号生成电路的输出端;

30、所述同存储体刷新复位信号生成电路的多个输入端分别连接至同一存储组中各存储体的第二锁存器的输出端和所述窗口控制复位信号生成电路的输出端,用于接收所述窗口控制复位信号生成电路输出的窗口控制复位信号和同一存储组中各所述存储体的同存储体刷新窗口信号,以在各所述同存储体刷新窗口信号均为第二电平,且所述窗口控制复位信号为第一电平时,生成第二电平的同存储体刷新复位信号。

31、在一实施例中,所述同存储体刷新复位信号生成电路,包括:第三与逻辑电路、第二反相电路和第四与逻辑电路;

32、所述第三与逻辑电路的多个输入端分别连接至同一存储组中各存储体的所述第二锁存器的输出端,用于接收各存储体的同存储体刷新窗口信号,以通过与逻辑运算生成同存储体循环结束信号;

33、所述第二反相电路的输入端连接至所述窗口控制复位信号生成电路的输出端,用于接收所述窗口控制复位信号,以生成所述窗口控制复位信号的反相信号;

34、所述第四与逻辑电路连接至所述第三与逻辑电路和所述第二反相电路,用于接收所述同存储体循环结束信号和所述反相信号,以通过与逻辑运算生成所述同存储体刷新复位信号。

35、在一实施例中,所述刷新控制电路还包括:刷新命令生成电路和延迟电路;

36、所述刷新命令生成电路的多个输出端分别连接至所述刷新窗口控制电路的输入端和所述延迟电路的输入端,所述刷新命令生成电路用于接收外部的命令地址信号,以生成所述同存储体刷新命令和全存储体刷新命令,并输出给所述刷新窗口控制电路和所述延迟电路;

37、所述延迟电路的输出端连接至所述刷新窗口生成电路的输入端,所述延迟电路用于匹配所述刷新窗口控制电路引入的时间延迟。

38、在一实施例中,所述刷新控制电路还包括:行地址生成电路;

39、所述行地址生成电路的输入端连接至所述刷新窗口控制电路的输出端,用于接收所述刷新窗口控制电路输出的刷新窗口控制信号,以在所述刷新窗口控制信号处于第一电平时,输出待刷新行地址。

40、在一实施例中,所述刷新控制电路还包括:激活电路;

41、所述激活电路的输入端连接至所述刷新窗口生成电路的输出端,用于接收所述刷新窗口生成电路输出的第一刷新窗口信号,以根据第一刷新窗口信号生成行激活脉冲信号,所述行激活脉冲信号用于激活存储体中的行,以进行数据刷新。

42、第二方面,本技术实施例提供一种存储器,包括第一方面所述的刷新控制电路。

43、本技术实施例提供一种刷新控制电路及存储器,包括:刷新窗口控制电路和刷新窗口生成电路。刷新窗口控制电路的输出端连接至刷新窗口生成电路的输入端,刷新窗口控制电路用于接收同存储体刷新命令和全存储体刷新命令,以在执行同存储器刷新命令对应的同存储体刷新过程中,接收到全存储体刷新命令时,控制刷新窗口生成电路向已完成同存储体刷新的存储体输出具有第一电平的第一刷新窗口信号,在第一刷新窗口信号处于第一电平时,已完成同存储体刷新的存储体停止数据刷新。这样,可以尽可能的避免同存储体刷新和全存储体刷新重复刷新,可以降低存储器的功耗。

- 还没有人留言评论。精彩留言会获得点赞!