存储器的操作方法、存储器及存储器系统与流程

本公开涉及存储器,尤其涉及一种存储器的操作方法、存储器及存储器系统。

背景技术:

1、nand闪存是一种非易失性存储技术,即断电后仍能保存数据,具有存储成本低和存储容量高等优点。现有的nand闪存芯片通常采用递进步长脉冲编程(incremental steppulse programming,ispp)方法进行编程,利用逐步增大的编程电压对存储单元进行编程,每一个编程脉冲后都有相对应的验证脉冲,来检验存储单元阈值电压是否达到目标值。

2、随着存储器单元中存储的比特数增加,编程所需要的时间也在增加。其中,施加编程脉冲的次数以及进行编程验证操作的次数,是决定编程时间的重要因素。因此,如何在保证编程质量的前提下,缩短编程时间,成为亟待解决的问题。

技术实现思路

1、本公开的实施例提供一种存储器的操作方法、存储器及存储器系统,旨在解决如何缩短编程时间的问题。

2、为达到上述目的,本公开的实施例采用如下技术方案。

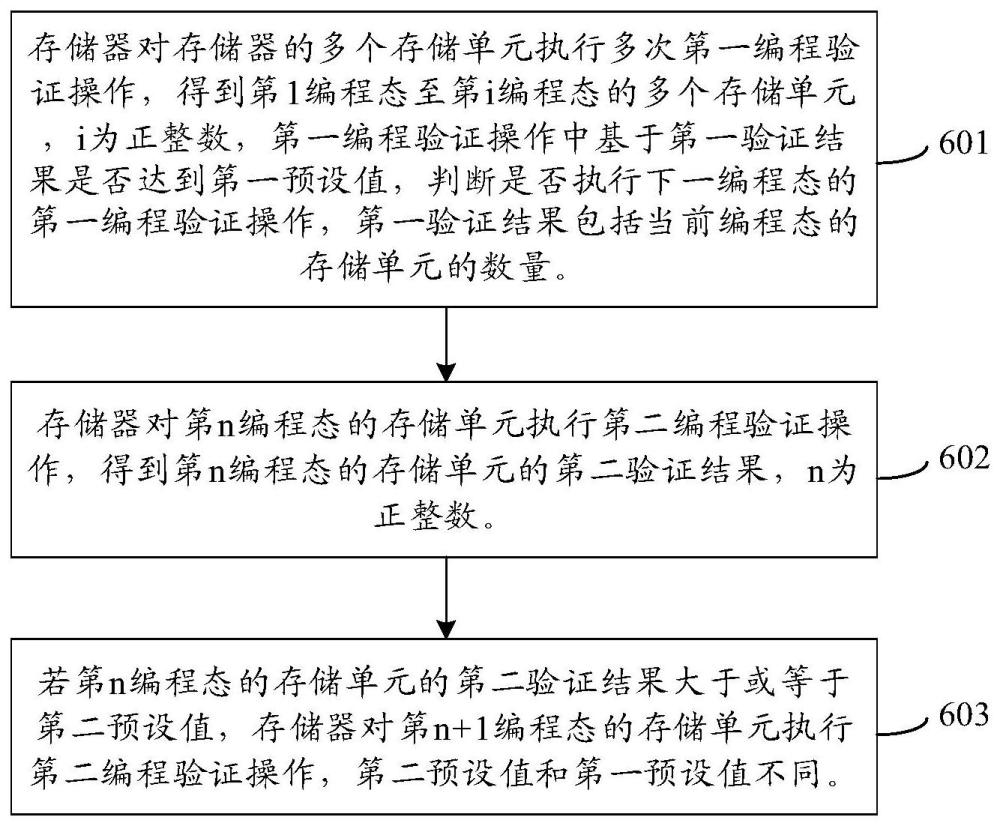

3、第一方面,提供一种存储器的操作方法,该方法包括:对存储器的多个存储单元执行多次第一编程验证操作,得到第1编程态至第i编程态的多个存储单元,i为正整数,第一编程验证操作中基于第一验证结果是否达到第一预设值,判断是否执行下一编程态的第一编程验证操作,第一验证结果包括当前编程态的存储单元的数量。对第n编程态的存储单元执行第二编程验证操作,得到第n编程态的存储单元的第二验证结果,n为正整数。若第n编程态的存储单元的第二验证结果大于或等于第二预设值,对第n+1编程态的存储单元执行第二编程验证操作,第二预设值和第一预设值不同。

4、本公开的上述实施例提供的存储器的操作方法,采用两步编程的方法,包括粗略编程和精细编程。其中,粗略编程中基于第一预设值判断是否进行下一编程态的第一编程验证操作,精细编程中基于第二预设值判断是否进行下一编程态的第二编程验证操作。相较于粗略编程和精细编程采用相同的预设值,本技术实施例提供的存储器的操作方法在粗略编程和精细编程中采用不同的预设值,可以减少粗略编程对精细编程的影响,从而减少精细编程的验证次数,减少编程时间。

5、在一些实施例中,对第n编程态的存储单元执行第二编程验证操作,得到第n编程态的存储单元的第二验证结果之前,方法还包括:基于第二编程验证操作的验证电压获取第n编程态的存储单元的预验证结果。

6、这些实施例中,预验证结果为在完成粗略编程后,已达到第n编程态的存储单元的数量,预验证结果可以理解为粗略编程对精细编程的影响,基于预验证结果可以调整精细编程中第二预设值的取值,从而减少精细编程的验证操作,减少编程时间。

7、在一些实施例中,第二验证结果包括第n编程态的存储单元的数量,第二预设值大于第一预设值。

8、这些实施例中,如果第二验证结果包括第n编程态的存储单元的数量,相当于第二验证结果包括粗略编程对精细编程的影响,此时第二预设值大于第一预设值,可以减少粗略编程对精细编程的影响,从而减少精细编程的验证操作,减少编程时间。

9、在一些实施例中,第二验证结果包括除预验证结果对应的存储单元的数量以外的第n编程态的存储单元的数量,第二预设值小于第一预设值。

10、这些实施例中,如果第二验证结果不包括第n编程态的存储单元的数量,相当于第二验证结果中已提出了粗略编程对精细编程的影响,此时第二预设值小于第一预设值,可以减少粗略编程对精细编程的影响,从而减少精细编程的验证操作,减少编程时间。

11、在一些实施例中,对存储器的多个存储单元执行多次第一编程验证操作,得到第1编程态至第i编程态的多个存储单元,包括:对第m编程态的存储单元执行第一编程验证操作,得到第m编程态的存储单元的第一验证结果,m为正整数。若第m编程态的存储单元的第一验证结果大于或等于第一预设值,对第m+1编程态的存储单元执行第一编程验证操作。若第m编程态的存储单元的第一验证结果小于第一预设值,对第m编程态的存储单元执行第一编程验证操作。若对最高编程态的存储单元执行第一编程验证操作得到的第一验证结果大于或等于第一预设值,得到第1编程态至第i编程态的多个存储单元。

12、这些实施例中,根据第m编程态的存储单元的第一验证结果与第一预设值的比较结果,判断继续进行当前编程态的第一编程验证操作还是进行下一编程态的第一编程验证操作,可以动态确定每个待验证的编程态的起始时刻,可以提高确定的每个待验证的编程态的起始时刻的准确性,减少验证次数以缩短编程时间。

13、在一些实施例中,第一编程验证操作的多个编程脉冲的步长大于第二编程验证操作的多个编程脉冲的步长。

14、这些实施例中,多次第一编程验证操作可以理解粗略编程,多次第二编程验证操作可以理解为精细编程。本技术实施例提供的存储器的操作方法先进行粗略编程以快速到达不同的编程态,提高编程速度,再进行精细编程以获得较好的编程质量,缩短编程时间。

15、在一些实施例中,若第n编程态的存储单元的第二验证结果小于第二预设值,对第n编程态的存储单元执行第二编程验证操作。

16、这些实施例中,如果第二验证结果小于第二预设值,则表征只有较少的存储单元到达了第n编程态,则可以预测在施加下一个编程脉冲后,几乎没有目标编程态为第n+1编程态的存储单元能够到达第n+1编程态,此时无需对第n+1编程态的存储单元执行第二编程验证操作。如此,可以减少第二编程验证操作的次数,有利于缩短编程时间,并减少待处理的第二验证结果数量,提高编程效率。

17、在一些实施例中,该方法还包括:获取第一编程验证操作的第一次数,并根据第一次数,确定第一预设值。获取第二编程验证操作的第二次数,并根据第二次数,确定第二预设值。

18、这些实施例中,通过获取编程验证操作的次数,并根据次数确定预设值,可以在编程验证操作追踪到随着循环次数变化而变化的编程特性,进行灵活调整预设值的范围,减少因为预设值确定不当导致的编程速度慢,有利于提高编程速度,保证编程质量。

19、第二方面,提供一种存储器,存储器包括:存储单元阵列,存储单元阵列包括多个存储单元。外围电路,外围电路耦合到存储单元阵列,外围电路被配置为:对存储器的多个存储单元执行多次第一编程验证操作,得到第1编程态至第i编程态的多个存储单元,i为正整数,第一编程验证操作中基于第一验证结果是否达到第一预设值,判断是否执行下一编程态的第一编程验证操作,第一验证结果包括当前编程态的存储单元的数量。对第n编程态的存储单元执行第二编程验证操作,得到第n编程态的存储单元的第二验证结果,n为正整数。若第n编程态的存储单元的第二验证结果大于或等于第二预设值,对第n+1编程态的存储单元执行第二编程验证操作,第二预设值和第一预设值不同。

20、第二方面的有益效果可以参见第一方面的说明。

21、在一些实施例中,外围电路还被配置为:基于第二编程验证操作的验证电压获取第n编程态的存储单元的预验证结果。

22、在一些实施例中,第二验证结果包括第n编程态的存储单元的数量,第二预设值大于第一预设值。

23、在一些实施例中,第二验证结果包括除预验证结果对应的存储单元的数量以外的第n编程态的存储单元的数量,第二预设值小于第一预设值。

24、在一些实施例中,外围电路还被配置为:对第m编程态的存储单元执行第一编程验证操作,得到第m编程态的存储单元的第一验证结果,m为正整数。若第m编程态的存储单元的第一验证结果大于或等于第一预设值,对第m+1编程态的存储单元执行第一编程验证操作。若第m编程态的存储单元的第一验证结果小于第一预设值,对第m编程态的存储单元执行第一编程验证操作。若对最高编程态的存储单元执行第一编程验证操作得到的第一验证结果大于或等于第一预设值,得到第1编程态至第i编程态的多个存储单元。

25、在一些实施例中,第一编程验证操作的多个编程脉冲的步长大于第二编程验证操作的多个编程脉冲的步长。

26、在一些实施例中,外围电路还被配置为:若第n编程态的存储单元的第二验证结果小于第二预设值,对第n编程态的存储单元执行第二编程验证操作。

27、在一些实施例中,外围电路还被配置为:获取第一编程验证操作的第一次数,并根据第一次数,确定第一预设值。获取第二编程验证操作的第二次数,并根据第二次数,确定第二预设值。

28、第三方面,提供一种存储器系统,该存储器系统包括:一个或多个第二方面的存储器,以及耦合到存储器并且被配置为控制存储器的存储器控制器。

29、可以理解地,本公开的上述实施例提供的存储器的操作方法、存储器及存储器系统其所能达到的有益效果可参考上文中半导体结构的有益效果,此处不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!