闪存阵列的控制方法、系统、设备、介质及装置与流程

本技术涉及存储领域,特别涉及一种闪存阵列的控制方法、系统、设备、介质及装置。

背景技术:

1、3d nand闪存阵列由于其高并发读写、高容量、高存储密度和低成本等优势,在数据中心、自动驾驶、高性能存储以及电子消费品等领域得到广泛应用。与2d nand闪存相比,垂直沟道3d nand闪存的存储单元沟道与衬底之间没有直接接触,电荷只能从两端提供。因此,如果沟道中的某两个阈值电压较大的存储单元由于栅极电压小于开通阈值而关断,整个沟道的传导通路将会关闭,导致存储单元处于浮动状态,如图1所示。当存储单元的栅极电压进一步降低到0v时,两个关断存储单元之间的沟道电势将会降低到负电势,即解耦合现象。

2、解耦合现象通常发生在读取操作和编程验证结束时,随着wl(word line,字线)上电压逐渐降低。每个存储单元串(位线连接的若干个存储单元被称为一个存储单元串)中的编程单元具有不同的编程态,阈值电压较大的存储单元先关断,因此沟道内任意两个具有局部阈值电压峰值的存储单元之间都可能发生解耦合现象。解耦合后的电势值由两个存储单元中较小阈值决定,从而将沟道电势划分为多个电势区域。

3、为了抑制解耦合现象,常用的方法是软压降和预打开。软压降是指在编程验证结束时不将电压降低到0v,从而提升沟道电势,减轻栅极应力。预打开则是在预充电时施加一个预打开电压在存储单元上,提高沟道电势。然而,软压降和预打开方法存在一些缺点:在软压降和预打开方案中,对所有已编程wl中的存储单元施加恒定电压,这会导致在解耦合现象较小时仍对所有已编程单元施加电压,增加栅极应力,同时增加读串扰几率。此外,在解耦合现象影响较小时使用恒定电压,也增加了整体功耗。

技术实现思路

1、本技术的目的是提供一种闪存阵列的控制方法、系统、设备、介质及装置,可以避免对所有已编程字线对应的存储单元施加恒定电压,从而减轻栅极应力和读串扰几率;同时,通过根据存储单元的个数来确定软压降电压值,可以根据解耦合现象的情况自适应调整软压降电压,降低功耗。

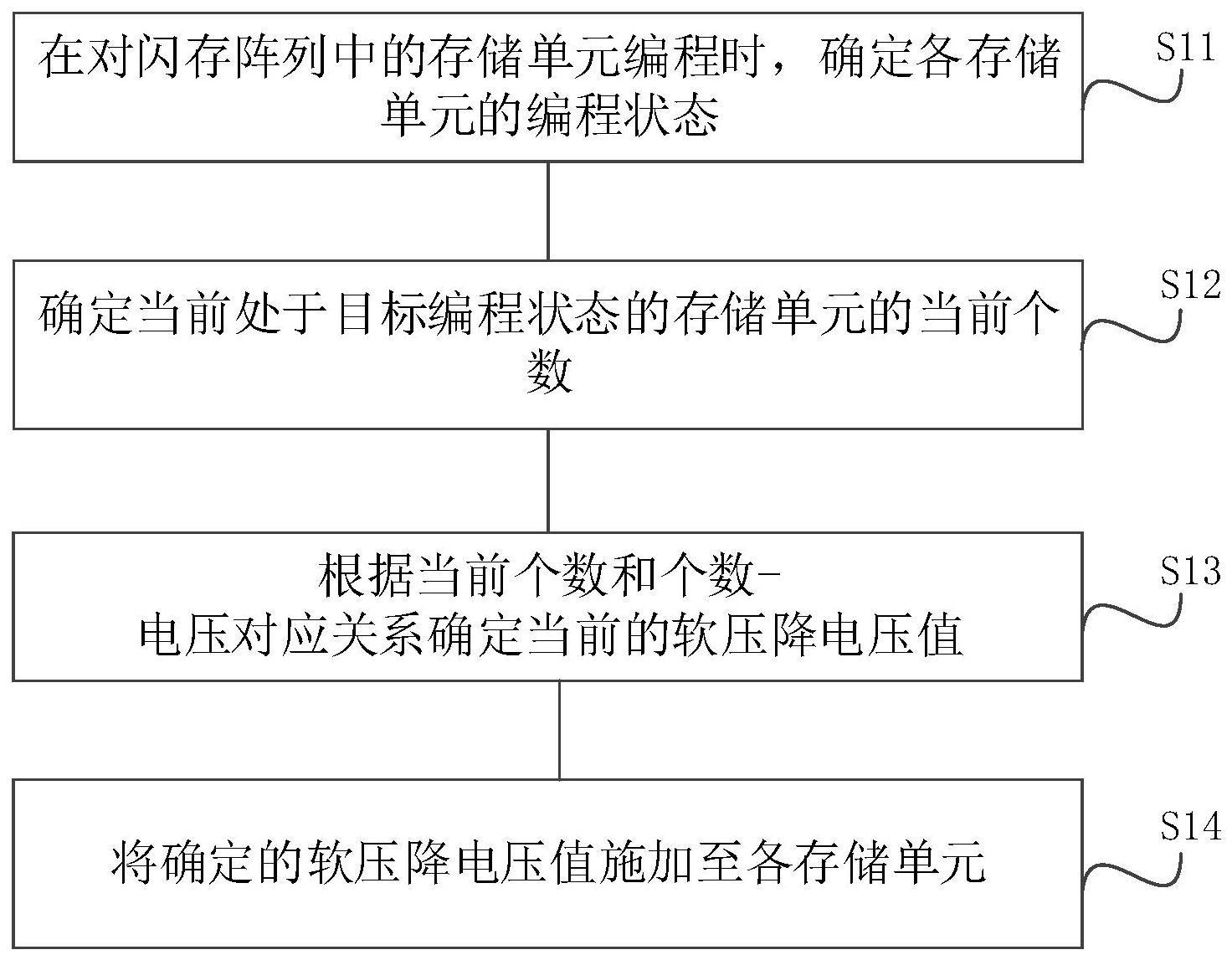

2、为解决上述技术问题,本技术提供了一种闪存阵列的控制方法,包括:

3、在对所述闪存阵列中的存储单元编程时,确定各所述存储单元的编程状态;

4、确定当前处于目标编程状态的存储单元的当前个数;

5、根据所述当前个数和个数-电压对应关系确定当前的软压降电压值;

6、将确定的所述软压降电压值施加至各所述存储单元。

7、在一种实施例中,确定当前处于目标编程状态的存储单元的当前个数,包括:

8、确定每个位线对应的存储单元串中当前处于目标编程状态的存储单元的当前个数。

9、在一种实施例中,确定每个位线对应的存储单元串中当前处于目标编程状态的存储单元的当前个数之后,还包括:

10、确定每个所述存储单元串中当前处于目标编程状态的存储单元的当前个数是否达到2;

11、若达到,则将当前处于目标编程状态的存储单元的当前个数是否达到2的存储单元串作为目标存储单元串;

12、根据所述当前个数和个数-电压对应关系确定当前的软压降电压值,包括:

13、根据所述目标存储单元串的个数及所述个数-电压对应关系确定对应的软压降电压值。

14、在一种实施例中,在对所述闪存阵列中的存储单元编程时,确定各所述存储单元的编程状态,包括:

15、在对所述闪存阵列中的存储单元编程时,根据各所述存储单元对应的位线和字线上的施加电压确定各所述存储单元的编程状态。

16、在一种实施例中,在所述存储单元为多比特存储单元时,确定当前处于目标编程状态的存储单元的当前个数,包括:

17、确定当前处于最高阈值电压对应的编程状态的存储单元的当前个数。

18、为解决上述技术问题,本技术还提供了一种闪存阵列的控制装置,包括:

19、计数电路,用于在对所述闪存阵列中的存储单元编程时,对当前处于目标编程状态的存储单元的个数进行计数;

20、比较电路,与所述计数电路连接,用于将所述计数电路的输出值与设定值进行比较,输出比较结果;

21、控制电路,与所述比较电路连接,用于根据所述比较结果和电压的映射关系确定与所述比较结果对应的软压降电压值,并将所述软压降电压值施加至各个所述存储单元。

22、在一种实施例中,所述计数电路包括:

23、多个计数器,与多个位线一一对应,每个所述计数器与和自身对应的位线连接,用于对和自身对应的存储单元串中处于所述目标编程状态的存储单元的个数进行计数。

24、在一种实施例中,所述计数电路还包括:

25、多个信令器,与多个所述计数器一一对应,每个所述信令器与对应的所述计数器连接,用于在所述计数器的计数值达到预设值时,将自身的状态调整为预设状态;

26、所述比较电路的输入端分别与多个所述信令器的输出端连接,所述比较电路具体用于根据处于所述预设状态的信令器的个数确定目标存储单元串的个数,并将所述目标存储单元串的个数与设定值进行比较,输出比较结果;

27、所述目标存储单元串为处于目标编程状态的存储单元的个数达到预设值的存储单元串。

28、在一种实施例中,所述信令器具体用于在所述计数器的计数值达到预设值时置1:

29、所述比较电路包括:

30、目标存储单元计数模块,与各个信令器的输出端连接,用于将多个信令器的输出值转换为十进制的数值输出,得到所述目标存储单元串的个数;

31、比较器,与所述目标存储单元计数模块连接,用于将目标存储单元计数模块输出的所述目标存储单元串的个数与设定值比较,输出所述比较结果。

32、为解决上述技术问题,本技术还提供了一种闪存阵列的控制系统,包括:

33、状态确定单元,用于在对所述闪存阵列中的存储单元编程时,确定所述存储单元的编程状态;

34、个数确定单元,用于确定当前处于目标编程状态的存储单元的当前个数;

35、电压确定单元,用于根据所述当前个数和个数-电压对应关系确定当前的软压降电压值;

36、软压降单元,用于将确定的所述软压降电压值施加在各所述存储单元的栅极。

37、为解决上述技术问题,本技术还提供了一种电子设备,包括:

38、存储器,用于存储计算机程序;

39、处理器,用于在存储计算机程序时,实现如上述所述的闪存阵列的控制方法的步骤。

40、为解决上述技术问题,本技术还提供了一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如上述所述的闪存阵列的控制方法的步骤。

41、本技术提供了一种闪存阵列的控制方法、系统、设备、介质及装置,涉及存储领域,用于解决闪存阵列中存在的栅极应力大、读串扰几率大及功耗较大的问题。该方案通过根据存储单元对应的位线和字线上的施加电压来确定存储单元的编程状态,并根据目标编程状态的存储单元的个数来确定软压降电压值,最后将软压降电压施加在存储单元的栅极上。相比于传统的软压降和预打开方法,可以避免对所有已编程字线对应的存储单元施加恒定电压,从而减轻栅极应力和读串扰几率;同时,通过根据存储单元的个数来确定软压降电压值,可以根据解耦合现象的情况灵活调整软压降电压,降低功耗。

- 还没有人留言评论。精彩留言会获得点赞!