存储单元及其写入、读取、计算方法、存储器

本发明涉及半导体制造领域,尤其涉及一种存储单元及其写入、读取、计算方法、存储器。

背景技术:

1、自旋转移矩磁随机存储器(stt-mram)具有优异的保持特性、超快的读写速度和与cmos工艺的良好兼容性,是存算一体(compute-in-memory,cim)架构领域的主要候选器件之一。传统的cim架构需要对存储单元或其级联方式进行设计,以复用行或列实现充当特定过程的计算加速器。

2、然而,常规的存算一体架构在进行卷积操作的过程中往往需要对输入数据和权重进行分批的多次写入,且调用特定单元承担卷积核运算时需要复杂的时序设计,增加了架构的复杂性与延迟,进一步降低了存储器的计算并行度以及增加了功耗。

技术实现思路

1、本发明解决的技术问题是提供一种存储单元及其写入、读取、计算方法、存储器,提高存储器的计算并行度以及降低存储器的功耗。

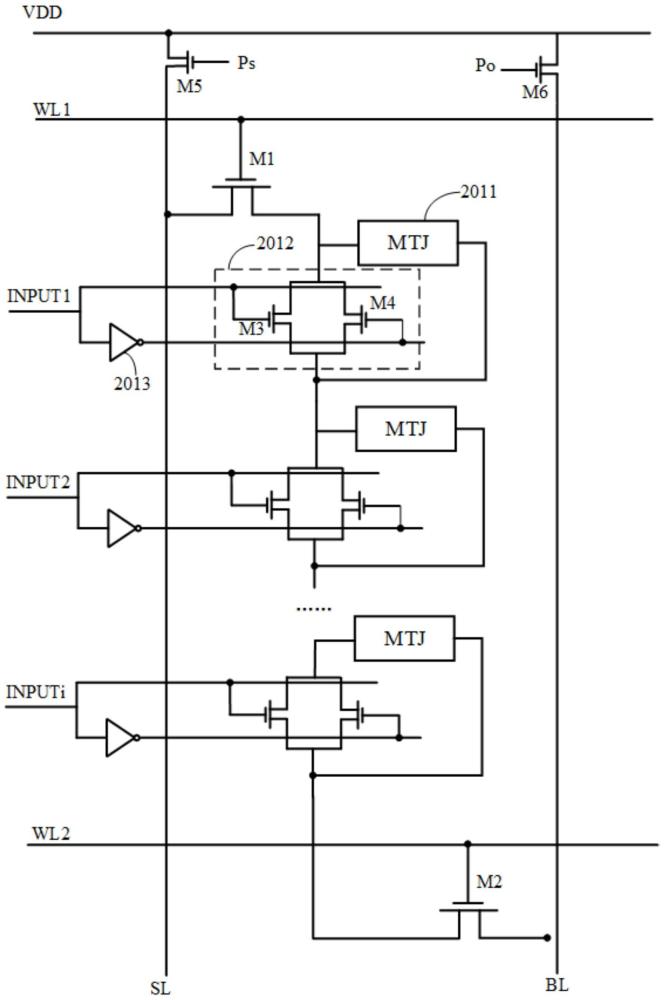

2、为解决上述技术问题,本发明实施例提供一种存储单元,包括:第一字线以及第二字线;源极线以及位线;第一晶体管,所述第一晶体管的栅极连接至所述第一字线,所述第一晶体管的源极或漏极之一连接至所述源极线;若干串联连接的存储模块,各所述存储模块包括输入端、第一端以及第二端,所述输入端用于接收输入信号,驱动所述存储模块,所述存储模块的第一端连接所述源极线,所述存储模块的第二端连接位线;第二晶体管,所述第二晶体管的栅极连接至所述第二字线,所述第二晶体管的源极或漏极之一连接至所述位线,所述第二晶体管的另一源极或漏极连接至所述存储模块的第二端。

3、可选的,各所述存储模块包括:磁性隧道结单元,所述磁性隧道结单元包括第一端和第二端,所述磁性隧道结单元的第一端连接所述第一晶体管的另一源极或漏极;传输门单元,所述传输门单元包括第一端以及第二端,所述传输门单元的第一端连接所述磁性隧道结单元的第一端,所述传输门单元的第二端连接所述磁性隧道结单元的第二端。

4、可选的,所述存储单元还包括:在所述输入端与所述存储模块之间接入反相器,所述反相器包括输入端和输出端;各所述传输门包括第三晶体管和第四晶体管,所述第三晶体管的栅极连接所述输入端,所述第三晶体管的源极或漏极之一连接至所述第四晶体管的源极或漏极之一,所述第三晶体管的另一源极或漏极连接至所述第四晶体管的另一源极或漏极,所述第四晶体管的栅极连接至所述反相器的输出端,所述反相器的输入端连接所述输入端。

5、可选的,各所述磁性隧道结单元与一个传输门单元并联连接。

6、可选的,所述存储单元还包括:所述第三晶体管和所述第四晶体管的类型相反。

7、可选的,所述存储单元还包括:第五晶体管、第六晶体管以及电源线,所述第五晶体管的栅极连接第一控制电压端,所述第六晶体管的栅极连接第二控制电压端,所述第五晶体管的源极或漏极之一连接所述电源线,所述第五晶体管的另一源极或漏极连接所述源极线,所述第六晶体管的源极或漏极之一连接所述电源线,所述第六晶体管的另一源极或漏极连接所述位线。

8、可选的,所述存储单元还包括:所述第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管以及第六晶体管包括nmos管或pmos管。

9、可选的,所述存储单元还包括:写入操作单元,所述写入操作单元用于:施加第一电平至与待写入数据的传输门连接的所述输入端、所述第一字线以及第二字线,使得所述待写入数据的磁性隧道结单元处于导通状态;施加第一电压至所述源极线,施加第二电压至所述位线,使得所述存储单元内产生写入电流,对待写入数据的磁性隧道结单元写入数据。

10、可选的,在对待写入数据的磁性隧道结单元写入数据之前,还包括:施加第一电平至与待写入数据的传输门连接的所述输入端、所述第一字线以及第二字线,使得全部所述磁性隧道结单元处于导通状态;施加第一电压至所述源极线,施加第二电压至所述位线,使得所述写入电流由位线流向源极线,对全部所述磁性隧道结单元写入初始数据;其中所述第一电压小于第二电压。

11、可选的,所述存储单元还包括:读取操作单元,所述读取操作单元用于:施加第一电平至与待写入数据的传输门连接的所述输入端、所述第一字线以及第二字线,使得所述待写入数据的磁性隧道结单元处于导通状态;施加第一电压至所述源极线,施加第二电压至所述位线,使得所述存储单元内产生读取电流,获取待写入数据的磁性隧道结单元上的读取电流。

12、可选的,所述存储单元还包括:卷积计算单元,所述卷积计算单元用于:根据流经磁性隧道结单元上的电流以及所述位线上的存储电压,得到所述磁性隧道结单元的阻值rmtj;获取每一列存储单元内输入端的信号状态input;对所述磁性隧道结单元的阻值与所述输入端的信号状态进行卷积运算,得到卷积核rmtj*input。

13、可选的,所述存储单元还包括:求和计算单元,所述求和计算单元用于:获取每一列的若干所述卷积核rmtji*inputi;对每一列的若干所述卷积核进行求和运算,得到感测列阻rcol=∑inputi*rmtji。

14、可选的,所述存储模块的数量为n2,n为正整数。

15、相应的,本发明技术方案还提供一种存储器,包括上述存储单元,所述存储单元呈阵列排布,每一行的存储单元均连接至同一第一字线以及第二字线,每一列的存储单元均连接至同一源极线以及位线。

16、可选的,所述存储器还包括:读取电路,所述读取电路用于:获取所述存储器内每一列存储单元的感测列阻rcol以及参考列的参考感测列阻rref,并比较所述感测列阻rcol与参考感测列阻rref,得到各列阻值。

17、可选的,所述读取电路包括差分放大电路以及功率放大器。

18、相应的,本发明技术方案还提供一种存储单元写入方法,包括:施加第一电平至与待写入数据的传输门连接的输入端、所述第一字线以及第二字线,使得所述待写入数据的磁性隧道结单元处于导通状态;施加第一电压至源极线,施加第二电压至位线,使得所述存储单元内产生写入电流,对待写入数据的磁性隧道结单元写入数据。

19、可选的,在对待写入数据的磁性隧道结单元写入数据之前,还包括:施加第一电平至与待写入数据的传输门连接的所述输入端、所述第一字线以及第二字线,使得全部所述磁性隧道结单元处于导通状态;施加第一电压至所述源极线,施加第二电压至所述位线,使得所述写入电流由位线流向源极线,对全部所述磁性隧道结单元写入初始数据;其中所述第一电压小于第二电压。

20、相应的,本发明技术方案还提供一种存储单元的读取方法,包括:施加第一电平至与待写入数据的传输门连接的输入端、所述第一字线以及第二字线,使得所述待写入数据的磁性隧道结单元处于导通状态;施加第一电压至源极线,施加第二电压至位线,使得所述存储单元内产生读取电流,获取待写入数据的磁性隧道结单元上的读取电流。

21、相应的,本发明技术方案还提供一种存储单元的计算方法,包括:根据流经磁性隧道结单元上的电流以及位线上的存储电压,得到所述磁性隧道结单元的阻值rmtj;获取每一列存储单元内输入端的信号状态input;对所述磁性隧道结单元的阻值与所述输入端的信号状态进行卷积运算,得到卷积核rmtj*input。

22、可选的,所述存储单元计算方法还包括:获取每一列的若干所述卷积核rmtji*inputi;对每一列的若干所述卷积核进行求和运算,得到感测列阻rcol=∑inputi*rmtji。

23、相应的,本发明技术方案还提供一种存储器的读取方法,包括:获取存储器内每一列存储单元的感测列阻rcol以及参考列的参考感测列阻rref,并比较所述感测列阻rcol与参考感测列阻rref,得到各列阻值。

24、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

25、本发明技术方案提供的存储单元,通过在第一字线和第二位线之间接入若干串联连接的存储模块,且所述若干存储模块均连接至同一位线,实现在同一时间内控制若干存储模块的写入或读取操作,提高了存储单元的工作效率,进而实现了后续在进行卷积操作的过程中对多个输入数据和权重的同时写入以及计算,提高了存储器的计算并行度,且所述存储单元中的若干存储模块通过串联的方式连接,减小了读取电流,降低了存储器的功耗以及提高了器件稳定性;此外,各所述存储模块包括输入端,通过控制输入端的电平状态不同,对不同存储模块的写入或读取操作,实现对所述存储单元的灵活控制。

26、进一步,本发明技术方案中通过所述传输门单元与所述磁性隧道结单元的并联连接,当需要进行写入或读取操作时,通过关断所述传输门,使得所述写入或读取电流仅流经所述磁性隧道结,对所述磁性隧道结进行数据的写入或读取,当不需要进行写入或读取操作时,通过导通所述传输门,使得所述写入或读取电流仅流经所述传输门,所述磁性隧道结所在的电路被短路,即当前磁性隧道结无法进行写入或读取操作,最终实现灵活控制存储单元中磁性隧道结单元的工作状态,提高了所述存储单元的利用率。

27、进一步,本发明技术方案中,所述输入端与所述传输门连接,通过所述输入端控制各个所述传输门的导通或关断,进而控制所述存储单元中的一个或多个磁性隧道结的写入或读取操作,进一步实现灵活控制存储单元中磁性隧道结单元的工作状态,提高了所述存储单元的利用率。

28、进一步,本发明技术方案中,通过控制第五晶体管和第六晶体管的导通或关断,使得流经所述存储单元的写入电流的方向不同,进而实现不同数据的写入,且在电源端和存储单元之间接入第五晶体管和第六晶体管,减少电源与存储单元之间的串扰,提高器件的稳定性。

29、本发明技术方案提供的存储器,将存储单元通过阵列排布,且每一列的存储单元连接至同一第一字线、第二字线、源极线以及位线,使得所述存储器能够对任意一列的存储单元进行写入或读取操作,提高了存储单元的工作效率,进而实现了后续在进行卷积操作的过程中对多个输入数据和权重的同时写入以及计算,提高了存储器的计算并行度。

30、进一步,本发明技术方案中,通过将感测列阻rcol与参考感测列阻rref进行比较后,得到各列阻值,提高了输出结果的精确性,且本发明的读取电路能够对输出结果进行增大感测裕度以及降低噪声的操作,进一步优化了输出结果。

- 还没有人留言评论。精彩留言会获得点赞!