一种引脚复用的智能熔丝修调电路的制作方法

本发明涉及电路,具体涉及一种引脚复用的智能熔丝修调电路。

背景技术:

1、芯片制造过程中存在的工艺偏差,会导致芯片最终实现的参数与仿真数据有很大偏差,从而影响到芯片电路系统的性能指标,由于这类误差无法在芯片设计之初通过仿真工具进行有效的模拟,因此可以在电路设计时引入修调技术,在芯片生产完成后再根据实际测试数据对芯片的参数进行调整。

2、目前芯片生产中的修调技术存在激光熔丝修调、晶圆测试修调以及封装后熔丝修调,激光熔丝修调是通过激光来烧断金属熔丝,晶圆测试修调是在封装之前通过探针卡来烧断熔丝,封装后熔丝修调是在芯片封装之后进行的修调,通过芯片的某个功能管脚(通常为芯片的使能管脚)上加修调信号,在芯片内部产生大电流来烧断熔丝。激光修调精度较好,但需要专门的修调设备及苛刻的外部环境,因此成本较高,不易操作;晶圆测试阶段修调是在晶圆封装之前进行修调,需要许多pad端口,占用很大的芯片面积,并且在对晶圆进行封装时,芯片切割和封装也会对芯片的物理特性产生影响,造成修调后的芯片在封装之后产生偏差;封装后熔丝修调需要芯片具有特定的管脚来施加修调信号,不需要新增pad端口,复用已有的芯片管脚,是一种低成本,高可靠性的熔丝修调方式。

3、efuse,即一次性可编程存储器。efuse的诞生源于几年前ibm工程师的一个发现,与更旧的激光熔断技术相比,电子迁移(em)特性可以用来生成小得多的熔丝结构。em熔丝可以在芯片上编程,不论是在晶圆探测阶段还是在封装中。采用i/o电路的片上电压(通常为2.5v),一个持续200微秒的10毫安直流脉冲就足以编程单根熔丝。

4、在目前的封装后熔丝修调方式中,芯片设计为了修正在芯片制造过程中产生的工艺偏差,可以通过封装后熔丝修调的方式对电路进行调整,达到需要的精确值。为了实现一次熔丝修调就能够保证芯片的偏差得到永久性的修正,我们需要通过非易失性的存储器进行偏差值的存贮。通常我们使用otp(one time programme)电路进行修调,熔丝电路是常见的修调电路。但是传统的熔丝电路如果需要对修调的精度进行提高,其修调的位数也会增加,其需要配置的熔丝pin脚也会增加,进行多少位的修调就需要添加相应位数的pin脚,这不仅增加了芯片的生产面积以及生产成本,而且同时也增加了电路出现故障的风险。

技术实现思路

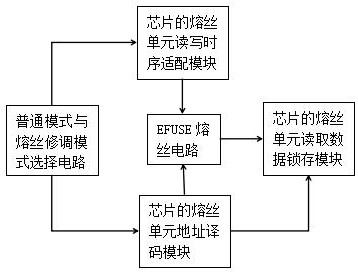

1、为解决现有技术中的问题,本发明提供了一种引脚复用的智能熔丝修调电路,通过在引脚复用的智能熔丝修调电路中设置相互配合的普通工作模式与熔丝修调模式选择电路、efuse熔丝电路、芯片的熔丝单元读写时序适配模块、芯片的熔丝单元地址译码模块和芯片的熔丝单元读取数据锁存模块,能够采用复用芯片引脚的方式,在不引入新的熔丝引脚情况下,输入不同输入电压去改变芯片引脚的功能,节省芯片面积,提高了熔丝修调的效率,并且通过时序控制逻辑,将需要进行复用的芯片引脚数量进一步降低,进一步减小了熔丝修调电路的芯片面积,降低了芯片生产成本,提高芯片的稳定性,解决了现有技术中芯片的熔丝修调方式如果需要提高修调精度需要增加多位熔丝pin脚导致芯片的生产面积增大、生产升本大幅度升高、同时降低了电路稳定性的问题。

2、本发明提供的一种引脚复用的智能熔丝修调电路,包括普通工作模式与熔丝修调模式选择电路、efuse熔丝电路、芯片的熔丝单元读写时序适配模块、芯片的熔丝单元地址译码模块和芯片的熔丝单元读取数据锁存模块,所述普通工作模式与熔丝修调模式选择电路的输入端能够通过芯片引脚接收控制信号en和控制信号rd,所述普通工作模式与熔丝修调模式选择电路的输出端与所述芯片的熔丝单元读写时序适配模块的输入端、所述芯片的熔丝单元地址译码模块的输入端相连,所述芯片的熔丝单元读写时序适配模块的输出端与所述efuse熔丝电路控制连接,所述芯片的熔丝单元地址译码模块的输出端与所述efuse熔丝电路的输入端相连,所述efuse熔丝电路的输出端、所述芯片的熔丝单元地址译码模块的输出端与所述熔丝单元读取数据锁存模块的输入端相连,所述普通工作模式与熔丝修调模式选择电路能够接收控制信号en启动熔丝修调模式并输出信号至所述芯片的熔丝单元读写时序适配模块和所述芯片的熔丝单元地址译码模块进而控制所述efuse熔丝电路完成芯片的熔丝修调作业。

3、本发明作进一步改进,所述普通工作模式与熔丝修调模式选择电路设有普通工作模式启动信号检测电路、熔丝修调模式启动信号检测电路和计数器enb,所述普通工作模式启动信号检测电路的输入端能够接收控制信号rd,所述熔丝修调模式启动信号检测电路的输入端能够接收控制信号en,所述普通工作模式启动信号检测电路的输出端、所述熔丝修调模式启动信号检测电路的输出端与所述计数器enb的输入端相连,所述计数器enb的输出端与所述芯片的熔丝单元读写时序适配模块的输入端、所述芯片的熔丝单元地址译码模块的输入端相连。

4、本发明作进一步改进,所述熔丝修调模式启动信号检测电路内设有场效应管mp1、场效应管mp2、场效应管mp3、场效应管mp4、场效应管mp5、场效应管mn1、场效应管mn2、场效应管mn3和场效应管mn4,其中,所述场效应管mp3的漏极能够接收控制信号en,所述场效应管mp3的源极与所述场效应管mn2的漏极、所述场效应管mn3的栅极相连,所述场效应管mn2的栅极与所述场效应管mn1的栅极、所述场效应管mn1的漏极、所述场效应管mp1的源极相连,所述场效应管mp1的漏极与所述场效应管mp2的源极相连,所述场效应管mn3的漏极与所述场效应管mp4的源极、所述场效应管mp5的栅极、所述场效应管mn4的栅极相连,所述场效应管mp5的源极与所述场效应管mn4的漏极、所述计数器enb的输入端相连,所述场效应管mp3的栅极、所述场效应管mp2的漏极、所述场效应管mp4的漏极、所述场效应管mp5的漏极接电压源vdd,所述场效应管mp1的栅极、所述场效应管mp2的栅极、所述场效应管mp4的栅极、所述场效应管mn1的源极、所述场效应管mn2的源极、所述场效应管mn3的源极、所述场效应管mn4的源极接地。

5、本发明作进一步改进,所述efuse熔丝电路内设有场效应管mp6、场效应管mp7、场效应管mp8、场效应管mp9、场效应管mn5、场效应管mn6、电阻r1、倒相放大器inv1和倒相放大器inv2,其中,所述场效应管mp6的栅极、所述场效应管mp8的栅极、所述场效应管mp9的栅极接电压源vb,所述场效应管mp6的漏极、所述场效应管mp8的漏极接电压源vdd,所述场效应管mp6的源极与所述场效应管mp7的漏极相连,所述场效应管mp7的栅极与所述芯片的熔丝单元读写时序适配模块的输出端相连,所述场效应管mp7的源极与所述场效应管mn5的漏极、所述场效应管mn5的栅极、所述场效应管mn6的栅极相连,所述场效应管mn6的源极与所述电阻r1的一端相连,所述电阻r1的另一端与所述芯片的熔丝单元读写时序适配模块的输出端、需要被熔断的熔丝金属的一端相连,所述场效应管mp8的源极与所述场效应管mp9的漏极相连,所述场效应管mp9的源极与所述场效应管mn6的漏极、所述倒相放大器inv1的输入端相连,所述倒相放大器inv1的输出端与所述倒相放大器inv2的输入端相连,所述倒相放大器inv2的输出端与所述熔丝单元读取数据锁存模块的输入端相连,所述场效应管mn5的源极、需要被熔断的熔丝金属的另一端接地。

6、本发明作进一步改进,所述熔丝修调模式启动信号检测电路的输入端能够接收控制信号en,当控制信号en为连续n个高于电压源vdd与所述场效应管mn3的导通电压vth之和以上的脉冲信号时,即en>vdd+vth,激活熔丝修调模式,其中,n≥8,n为自然数,导通电压vth的初始设定值为0.7v。

7、本发明作进一步改进,当激活熔丝修调模式时,芯片正常工作时的6个引脚功能为电源vdd、时钟信号clk、地址信号addr、烧录使能信号pgm、读取使能信号rd和地线gnd。

8、本发明作进一步改进,当激活熔丝修调模式时,所述芯片的熔丝单元读写时序适配模块输出烧录信号burn至所述电阻r1的另一端、输出烧录使能信号pgm至所述场效应管mp7的栅极,所述芯片的熔丝单元地址译码模块输出地址选择信号addr至所述场效应管mp7的栅极。

9、本发明作进一步改进,所述普通工作模式启动信号检测电路的输入端能够接收控制信号rd,当控制信号rd为连续m个高于电压源vdd与所述场效应管mn3的导通电压vth之和以上的脉冲信号时,即rd>vdd+vth,退出熔丝修调模式,进入普通工作模式,其中,m≥1,m为自然数,导通电压vth的初始设定值为0.7v。

10、本发明作进一步改进,当选择普通工作模式时,芯片正常工作时的6个引脚功能为电源vdd、芯片使能信号en、限流点配置端口ilim、标志位输出信号flg、开关输出端口out和地线gnd。

11、与现有技术相比,本发明的有益效果是:提供了一种引脚复用的智能熔丝修调电路,通过在引脚复用的智能熔丝修调电路中设置相互配合的普通工作模式与熔丝修调模式选择电路、efuse熔丝电路、芯片的熔丝单元读写时序适配模块、芯片的熔丝单元地址译码模块和芯片的熔丝单元读取数据锁存模块,普通工作模式与熔丝修调模式选择电路能够接收控制信号en启动熔丝修调模式并输出信号至芯片的熔丝单元读写时序适配模块和芯片的熔丝单元地址译码模块进而控制efuse熔丝电路完成芯片的熔丝修调作业,能够采用复用芯片引脚的方式,在不引入新的熔丝引脚情况下,输入不同输入电压去改变芯片引脚的功能,节省芯片面积,提高了熔丝修调的效率,并且通过时序控制逻辑,将需要进行复用的芯片引脚数量进一步降低,进一步减小了熔丝修调电路的芯片面积,降低了芯片生产成本,提高芯片的稳定性;而且可以对系统进行多次烧录,在烧录完成以后,如果还需要对其余未能够烧断的熔丝进行烧录,只需要重新编程即可;熔丝修调过程中,熔丝烧录的控制方法以及读取的方式,并非是并行处理,而是通过地址选择来进行操作,减少了烧录时过大的电流所带来的风险,在普通工作模式下通过周期性读取efuse烧录的信息,避免需要重复进入烧录模式,减少了芯片使用的复杂度,解决了现有技术中芯片的熔丝修调方式如果需要提高修调精度需要增加多位熔丝pin脚导致芯片的生产面积增大、生产升本大幅度升高、同时降低了电路稳定性的问题。

- 还没有人留言评论。精彩留言会获得点赞!