内存芯片的信号优化方法、计算机程序产品、设备及介质与流程

本技术涉及存储,特别涉及一种内存芯片的信号优化方法、系统及设备。

背景技术:

1、随着信息技术的不断发展,人们对于信息的存储和读取要求也越来越严格,因此对于ssd存储介质的容量要求和存取速率要求也越来越高;为满足该要求,ssd产品在内存芯片(nand,electrically erasable programmable read only memory,eeprom)总线设计时通过增加内存芯片负载数量来扩大容量,并同步提升内存芯片信号的运行速率。

2、现有的技术方案还停留在依靠对内存芯片进行拓扑优化,而仅仅依靠拓扑优化已经无法满足要求,因此亟需一种从端接电阻配置出发的信号优化方法以解决上述技术问题。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种内存芯片的信号优化方法、计算机程序产品、设备及介质。

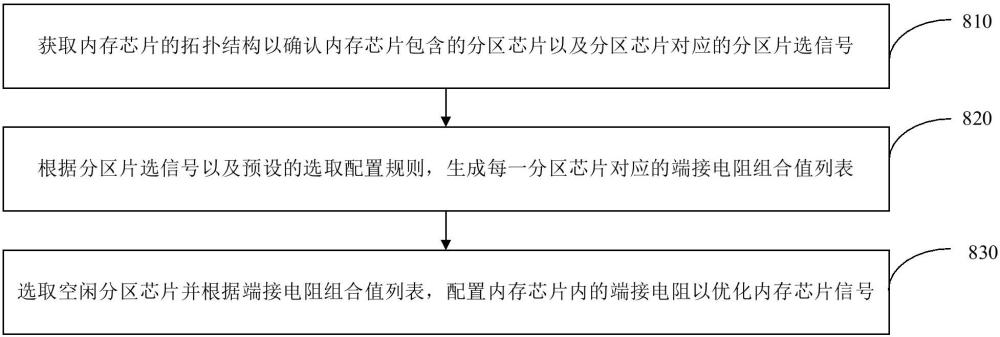

2、第一方面,本技术提供一种内存芯片的信号优化方法,方法包括:

3、获取所述内存芯片的拓扑结构以确认所述内存芯片包含的分区芯片以及所述分区芯片对应的分区片选信号;

4、根据所述分区片选信号以及预设的选取配置规则,生成每一分区芯片对应的端接电阻组合值列表;

5、选取空闲分区芯片并根据所述端接电阻组合值列表,配置所述内存芯片内的端接电阻以优化所述内存芯片信号。

6、在一些实施例中,所述根据所述分区片选信号以及预设的选取配置规则,以生成每一分区芯片对应的端接电阻组合值列表,包括:

7、获取每一分区芯片内包含的分区片选信号的数量,确定可选分区片选信号数;

8、选取与所述可选片选信号数匹配的第一分区片选信号;

9、配置所述第一分区片选信号对应的信号线上的端接电阻值以生成每一分区芯片对应的端接电阻组合值列表。

10、在一些实施例中,所述获取每一分区芯片内包含的分区片选信号的数量,确定可选分区片选信号数,包括:

11、若所述分区芯片内包含的分区片选信号的数量大于2,则根据所述分区片选信号数量与1的差值确定所述分区芯片匹配的所述可选分区片选信号数的个数;

12、若所述分区芯片内包含的分区片选信号的数量等于2,则确定所述可选分区片选信号数与所述分区芯片内包含的分区片选信号匹配;

13、若所述分区芯片内包含的分区片选信号的数量等于1,则停止生成所述分区芯片对应的端接电阻组合值列表。

14、在一些实施例中,所述选取与所述可选片选信号数匹配的第一分区片选信号,包括:

15、若所述分区芯片内包含的分区片选信号的数量大于2,针对每一个分区片选信号数,随机选取所述分区芯片内与所述可选分区片选信号数匹配的分区片选信号为第一分区片选信号;

16、若所述分区芯片内包含的分区片选信号的数量等于2,选取所述分区芯片内所有的分区片选信号为第一分区片选信号。

17、在一些实施例中,所述配置所述第一分区片选信号对应的信号线上的端接电阻值以生成每一分区芯片对应的端接电阻组合值列表,包括:

18、获取端接电阻默认值列表中包含的多个端接电阻初始值,以构建每一个所述第一分区片选信号对应的端接电阻值集合;

19、输入所述第一分区片选信号对应的端接电阻值集合至嵌套循环脚本并运行所述嵌套循环脚本以生成所述分区芯片对应的端接电阻组合值列表。

20、在一些实施例中,所述配置所述第一分区片选信号对应的信号线上的端接电阻值以生成每一分区芯片对应的端接电阻组合值列表,包括:

21、获取端接电阻默认值列表中包含的多个端接电阻初始值,以构建每一个所述第一分区片选信号对应的端接电阻值集合;

22、输入所述第一分区片选信号对应的端接电阻值集合至递归循环脚本并运行所述递归循环脚本以生成所述分区芯片对应的端接电阻组合值列表。

23、在一些实施例中,所述方法还包括:

24、获取生成的所述端接电阻组合值列表;

25、合并所述端接电阻组合值列表中相同端接电阻组合值;

26、根据所述端接电阻组合值的大小对所述端接电阻组合值列表进行排序。

27、在一些实施例中,所述合并所述端接电阻组合值列表中相同端接电阻组合值,包括:

28、比较所述相同端接电阻组合值匹配的第一分区片选信号配置,所述第一分区片选配置包括第一分区片选信号的个数和第一分区片选信号对应配置的端接电阻值;

29、若存在所述相同端接电阻组合值匹配的第一分区片选信号配置重复,则合并重复的第一分区片选信号配置;

30、若不存在所述相同端接电阻组合值匹配的第一分区片选信号配置重复,则保留所述相同端接电阻组合值匹配的多个不同分区片选信号。

31、在一些实施例中,所述选取空闲分区芯片并根据所述端接电阻组合值列表,配置所述内存芯片内的端接电阻以优化所述内存芯片信号,包括:

32、响应于检测到读写优化配置,选取所述内存芯片接收到的读写操作对应的目标分区芯片远端的空闲分区芯片;

33、根据第一预设规则,确定所述端接电阻组合值列表内与所述空闲分区芯片匹配的目标端接电阻组合值;

34、根据所述目标端接电阻组合值配置所述空闲分区芯片内包含的分区片选信号对应的信号线上的端接电阻值以优化所述内存芯片信号。

35、在一些实施例中,所述选取空闲分区芯片并根据所述端接电阻组合值列表,配置所述内存芯片内的端接电阻以优化所述内存芯片信号,包括:

36、响应于检测到多负载优化配置,选取所述内存芯片接收到的读操作对应的目标分区芯片远端的第一分区芯片以及目标分区芯片近端的第二分区芯片;

37、根据所述第一分区芯片和第二分区芯片确定所述空闲分区芯片;

38、根据第二预设规则,确定所述端接电阻组合值列表内与所述空闲分区芯片匹配的目标端接电阻组合值;

39、根据所述目标端接电阻组合值配置所述空闲分区芯片内包含的分区片选信号对应的信号线上的端接电阻值以优化所述内存芯片信号。

40、在一些实施例中,所述根据第二预设规则,查找所述端接电阻组合值列表内与所述空闲分区芯片匹配的目标端接电阻组合值,包括:

41、根据所述端接电阻组合值列表内包含的所有端接电阻组合值生成所述组合配置列表,所述组合配置列表包括第一分区芯片可配置的端接电阻组合值和第二分区芯片可配置的端接电阻组合值的所有组合配置;

42、根据所述组合配置列表,逐一配置所述第一分区芯片内的分区片选信号对应的信号线上的端接电阻值以及第二分区芯片内的分区片选信号对应的信号线上的端接电阻值,并对配置后的所述信号线进行仿真以生成待选仿真结果,所述待选仿真结果表征所述信号线上传输的待选信号质量;

43、确定表征的待选信号质量最优的待选仿真结果匹配的组合配置中包含的第一分区芯片的端接电阻组合值为与第一分区芯片匹配的目标端接电阻组合值;

44、确定表征的待选信号质量最优的待选仿真结果匹配的组合配置中包含的第二分区芯片的端接电阻组合值为与第二分区芯片匹配的目标端接电阻组合值。

45、在一些实施例中,所述根据第一预设规则,查找所述端接电阻组合值列表内与所述空闲分区芯片匹配的目标端接电阻组合值,包括:

46、顺序读取所述端接电阻组合值列表以获取第一端接电阻组合值;

47、根据读取出的所述第一端接电阻组合值配置所述空闲分区芯片内的分区片选信号对应的信号线上的端接电阻值;

48、对所述信号线进行仿真以获取所述空闲分区芯片配置为第一端接电阻组合值时的第一仿真结果,所述第一仿真结果表征所述信号线上传输的第一信号质量;

49、比较所述第一信号质量与预设仿真结果表征的预设信号质量;

50、若所述第一信号质量优于所述预设信号质量,则确定所述第一端接电阻组合值为目标端接电阻组合值。

51、在一些实施例中,所述根据第一预设规则,查找所述端接电阻组合值列表内与所述空闲分区芯片匹配的目标端接电阻组合值,包括:

52、顺序读取所述端接电阻组合值列表以获取第一端接电阻组合值;

53、根据读取出的所述第一端接电阻组合值配置所述空闲分区芯片内的分区片选信号对应的信号线上的端接电阻值,并定义所述第一端接电阻组合值为目标端接电阻组合值;

54、对所述信号线进行仿真以获取所述空闲分区芯片配置为目标端接电阻组合值时的第一仿真结果;

55、执行第一操作直至第一仿真结果表征的所述信号线上传输的第一信号质量优于生成的第二仿真结果表征所述信号线上传输的第二信号质量;

56、其中,所述第一操作包括:

57、顺序读取所述端接电阻组合值列表中所述目标端接电阻组合值相邻的第二端接电阻组合值;

58、根据读取出的第二端接电阻组合值配置所述空闲分区芯片内的分区片选信号对应的信号线上的端接电阻值;

59、对所述信号线进行仿真以获取所述空闲分区芯片配置为第二端接电阻组合值时的第二仿真结果;

60、若所述第二仿真结果表征的所述信号线上传输的第二信号质量优于所述第一仿真结果表征所述信号线上传输的第一信号质量,则更新所述第二端接电阻组合值为目标端接电阻组合值。

61、在一些实施例中,所述根据第一预设规则,查找所述端接电阻组合值列表内与所述空闲分区芯片匹配的目标端接电阻组合值,包括:

62、读取所述端接电阻组合值列表包含的所有端接电阻组合值;

63、针对读取出的所有端接电阻组合值,逐一配置所述空闲分区芯片内的分区片选信号对应的信号线上的端接电阻值并对配置后的所述信号线进行仿真;

64、获取依据每一端接电阻组合值配置所述空闲分区芯片的分区片选信号对应的信号线上的端接电阻值对应的待选仿真结果,所述待选仿真结果表征所述信号线上传输的待选信号质量;

65、确定表征的待选信号质量最优的待选仿真结果对应的端接电阻组合值为目标端接电阻组合值。

66、在一些实施例中,所述比较所述第一信号质量与预设的预设信号质量,包括:

67、获取所述第一仿真结果对应的第一眼图的眼高和眼宽;

68、获取所述预设仿真结果对应的预设眼图的眼高和眼宽;

69、比较所述第一仿真结果对应的第一眼图的眼高和预设仿真结果对应的预设眼图的眼高以获取第一比较结果;

70、比较所述第一仿真结果对应的第一眼图的眼宽和预设仿真结果对应的预设眼图的眼宽以获取第二比较结果;

71、根据所述第一比较结果和第二比较结果判断所述第一信号质量是否优于所述预设信号质量。

72、在一些实施例中,所述根据所述第一比较结果和第二比较结果判断所述第一信号质量是否优于所述预设信号质量,包括:

73、若所述第一比较结果为第一眼图的眼高高于所述预设眼图的眼高,且所述第二比较结果为第一眼图的眼宽宽于所述预设眼图的眼宽,则判定所述第一信号质量优于所述预设信号质量;

74、若所述第一比较结果为第一眼图的眼高低于所述预设眼图的眼高,且所述第二比较结果第一眼图的眼宽窄于所述预设眼图的眼宽,则判定所述预设信号质量优于所述第一信号质量。

75、在一些实施例中,所述方法包括:

76、根据所述内存芯片的传输线模块、特性阻抗以及互连线长度建立信号线模型;

77、根据信号线模型,对所述内存芯片内的信号线进行仿真以获取表征信号线上传输的信号质量的眼图。

78、第二方面,本技术提供一种内存芯片的信号优化系统,系统包括:

79、处理模块,用于获取所述内存芯片的拓扑结构以确认所述内存芯片包含的分区芯片以及所述分区芯片对应的分区片选信号;

80、所述处理模块,还用于根据所述分区片选信号以及预设的选取配置规则,生成每一分区芯片对应的端接电阻组合值列表;

81、配置模块,用于选取空闲分区芯片并根据所述端接电阻组合值列表,配置所述内存芯片内的端接电阻以优化所述内存芯片信号。

82、第三方面,本技术提供一种计算机程序产品,包括计算机程序,其特征在于,该计算机程序被处理器执行时实现以下步骤:

83、获取所述内存芯片的拓扑结构以确认所述内存芯片包含的分区芯片以及所述分区芯片对应的分区片选信号;

84、根据所述分区片选信号以及预设的选取配置规则,生成每一分区芯片对应的端接电阻组合值列表;

85、选取空闲分区芯片并根据所述端接电阻组合值列表,配置所述内存芯片内的端接电阻以优化所述内存芯片信号。

86、第四方面,本技术提供了一种电子设备,电子设备包括:

87、一个或多个处理器;

88、以及与一个或多个处理器关联的存储器,存储器用于存储程序指令,程序指令在被一个或多个处理器读取执行时,执行如下操作:

89、获取所述内存芯片的拓扑结构以确认所述内存芯片包含的分区芯片以及所述分区芯片对应的分区片选信号;

90、根据所述分区片选信号以及预设的选取配置规则,生成每一分区芯片对应的端接电阻组合值列表;

91、选取空闲分区芯片并根据所述端接电阻组合值列表,配置所述内存芯片内的端接电阻以优化所述内存芯片信号。

92、第五方面,本技术还提供了一种计算机可读存储介质,存储介质上存储计算机程序,计算机程序使得计算机执行如下操作:

93、获取所述内存芯片的拓扑结构以确认所述内存芯片包含的分区芯片以及所述分区芯片对应的分区片选信号;

94、根据所述分区片选信号以及预设的选取配置规则,生成每一分区芯片对应的端接电阻组合值列表;

95、选取空闲分区芯片并根据所述端接电阻组合值列表,配置所述内存芯片内的端接电阻以优化所述内存芯片信号。

96、本技术实现的有益效果为:

97、本技术提供了一种内存芯片的信号优化方法,包括:获取所述内存芯片的拓扑结构以确认所述内存芯片包含的分区芯片以及所述分区芯片对应的分区片选信号;根据所述分区片选信号以及预设的选取配置规则,生成每一分区芯片对应的端接电阻组合值列表;选取空闲分区芯片并根据所述端接电阻组合值列表,配置所述内存芯片内的端接电阻以优化所述内存芯片信号。增加了odt参数值的可配置数量,实现了odt步进精度的提升,并通过新增读写参数独立配置,进一步实现信号品质优化。

- 还没有人留言评论。精彩留言会获得点赞!