基于内嵌式逻辑分析的DRAM测试机台、方法与流程

本发明涉及半导体测试,更为具体地,涉及一种基于内嵌式逻辑分析的dram测试机台、方法。

背景技术:

1、在进行dram(dynamic random access memory,动态随机存取存储器)测试时,通常通过外接逻辑分析仪设备进行测试,通过外接逻辑分析仪设备进行测试时,往往通过ate(automated test equipment,自动化测试设备)机台将测试向量施加到dram芯片的输入管脚,再通过ate测试机台实时采集dram芯片输出管脚的信号行为,而后将采集到的实际输出数据与预期输出数据进行比较,判断dram芯片的功能是否正常。但是该种方式会存在以下技术问题:

2、①探测困难:dram 芯片通常采用 bga 封装,引脚位于芯片下方,难以直接将探头连接到引脚上进行测量。为了解决这个问题,可能需要使用特殊的探测方法,如背部过孔转接板、dimm 串行电阻或转接板等方式,但这些方法可能会引入额外的信号干扰或复杂度;②读写突发区分困难:dram 数据总线是双向的,需要区分读和写操作对应的传输突发,在信号噪声和反射较大的情况下,仅通过观测 dqs 和 dq 数据边沿的关系可能难以明确区分,可能需要额外的数字信号设备采集dram的命令总线,根据命令类型来确定读写属性,可能需要示波器支持更多的探测通道数量,一般的示波器难以满足要求; ③无法满足高速和高精度要求:为了准确测量高速的 dram 信号,高速示波器需要具备足够的带宽、采样率和测量精度。同时,示波器的探头也需要具有低负载和良好的高频响应特性,以避免对信号造成过大的衰减或失真,因此dram测试对示波器的要求很高,一般示波器难以满足需求;④复杂的测试设置:进行dram测试时,需要正确设置示波器的参数,如触发模式、采样方式、测量选项等,以确保能够准确捕获和分析所需的信号特征。此外,可能还需要结合特定的dram测试软件或分析工具,来执行符合标准的测试和测量;⑤高速示波器与dramate测试机是独立的测试设备,在实现自动化等功能上无法做到完美配合,只能对单颗dram芯片或者是dram条进行测试,无法满足dramate测试需求。

3、因此,亟需一种实现高效实时监测,能够多通道同时分析,提高深入分析能力,紧凑集成,灵活配置,便于数据分析,节省测试时间的基于内嵌式逻辑分析的dram测试机台、方法。

技术实现思路

1、鉴于上述问题,本发明的目的是提供一种基于内嵌式逻辑分析的dram测试机台,以解决现有的通过外接逻辑分析仪设备进行测试的方法中存在的如下技术问题:①探测困难;②读写突发区分困难,通过观测 dqs 和 dq 数据边沿的关系可能难以明确区分; ③无法满足高速和高精度要求;④测试设置复杂;⑤高速示波器与dram ate测试机是独立的测试设备,在实现自动化等功能上无法做到完美配合,只能对单颗dram芯片或者是dram条进行测试,无法满足dram ate测试需求。

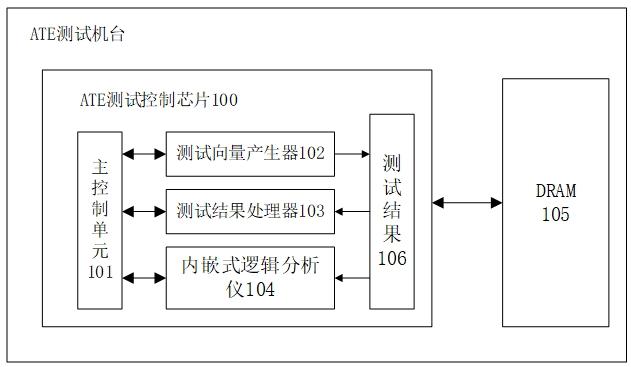

2、本发明提供的一种基于内嵌式逻辑分析的dram测试机台,其中,包括测试机台和设置在所述测试机台中的各个ate测试控制芯片;其中,

3、在所述ate测试控制芯片中集成有主控单元、测试向量产生器、测试结果处理器,以及内嵌式逻辑分析仪;

4、所述主控单元用于接收所述测试机台的命令以控制所述测试向量产生器、测试结果处理器,以及内嵌式逻辑分析仪;

5、所述测试向量产生器用于根据待测试dram的规格和测试要求生成测试向量和预期输出;

6、所述测试结果处理器用于采集待测试dram接收到所述测试向量后所产生的时序行为信息,并基于所述预期输出对所述时序行为信息进行分析判断以获取dram分析结果;

7、所述内嵌式逻辑分析仪用于基于所述dram分析结果根据所述时序行为信息锁定所述待测试dram的故障点位,并对所述故障点位的时序行为信息进行分析以获取测试结果。

8、优选地,所述内嵌式逻辑分析仪包括逻辑分析仪配置模块、采样模块、缓存器、触发模块和逻辑输出单元。

9、优选地,所述逻辑分析仪配置模块与所述主控单元相连接,用于接收所述主控单元发出的逻辑分析命令,控制或终止所述采样模块对所述待测试dram进行采样,控制或终止所述缓存器进行数据缓存,开启或关闭所述触发模块。

10、优选地,所述采样模块包括预设数量个采样通道,所述采样通道用于通过预设的采样程序对所述待测试dram进行实时采样,以获取输入至所述待测试dram的测试向量、预期输出,所述待测试dram所产生的时序行为信息,以及dram分析结果;

11、所述采样通道为2048个。

12、优选地,在所述ate测试控制芯片上还集成有测试接口;

13、所述测试接口与所述测试向量产生器、所述测试结果处理器,所述内嵌式逻辑分析仪,以及待测试dram通信连接。

14、优选地,所述缓存器用于缓存预设时间内经过所述采样通道所采集的所有数据信息。

15、优选地,所述触发模块包括16组触发逻辑单元,每个触发逻辑单元包含六种信号跳变边沿触发指令。

16、优选地,其中一种信号跳变边沿触发指令为故障触发,

17、所述故障触发为:若所述采样通道所采集的dram分析结果为所述待测试dram故障,则触发所述逻辑输出单元,以使所述逻辑输出单元对与所述故障触发相对应的时序行为信息进行判定,形成测试数字波形,并根据所述测试数字波形匹配出相应的测试结果。

18、本发明还提供一种基于内嵌式逻辑分析的dram测试方法,其中,基于如前所述的基于内嵌式逻辑分析的dram测试机台实现dram测试,包括:

19、将内嵌式逻辑分析仪集成在具有主控单元、测试向量产生器、测试结果处理器的ate测试控制芯片中;

20、使所述主控单元接收测试机台的命令,并基于所述命令通过所述测试向量产生器根据待测试dram的规格和测试要求生成测试向量和预期输出;

21、利用所述测试结果处理器采集待测试dram接收到所述测试向量后所产生的时序行为信息,并基于所述预期输出对所述时序行为信息进行分析判断以获取dram分析结果;

22、通过所述内嵌式逻辑分析仪基于所述dram分析结果根据所述时序行为信息锁定所述待测试dram的故障点位,并对所述故障点位的时序行为信息进行分析以获取测试结果。

23、优选地,基于所述dram分析结果根据所述时序行为信息锁定所述待测试dram的故障点位,并对所述故障点位的时序行为信息进行分析以获取测试结果,包括:

24、通过预设的采样程序对所述待测试dram进行实时采样,以获取输入至所述待测试dram的测试向量、预期输出,所述待测试dram所产生的时序行为信息,以及dram分析结果;

25、若所述采样通道所采集的dram分析结果为所述待测试dram故障,则触发所述逻辑输出单元,以使所述逻辑输出单元对与所述故障触发相对应的时序行为信息进行判定,形成测试数字波形,并根据所述测试数字波形匹配出相应的测试结果。

26、从上面的技术方案可知,本发明提供的基于内嵌式逻辑分析的dram测试机台、方法, 在ate测试控制芯片中集成有内嵌式逻辑分析仪,将内嵌式逻辑分析仪集成在具有主控单元、测试向量产生器、测试结果处理器的ate测试控制芯片中,使所述主控单元接收测试机台的命令,并基于所述命令通过所述测试向量产生器根据待测试dram的规格和测试要求生成测试向量和预期输出,利用所述测试结果处理器采集待测试dram接收到所述测试向量后所产生的时序行为信息,并基于所述预期输出对所述时序行为信息进行分析判断以获取dram分析结果,通过所述内嵌式逻辑分析仪基于所述dram分析结果根据所述时序行为信息锁定所述待测试dram的故障点位,并对所述故障点位的时序行为信息进行分析以获取测试结果,该种方式克服了现有技术中的缺陷,能够实现:高效的实时监测:能够实时捕捉和分析dram芯片的信号,帮助测试工程师快速发现问题,提高测试效率;多通道同时分析:可以同时监测多个信号通道,这对于dram这种复杂芯片中多个相关信号的同步分析非常重要;提高深入分析能力:具备强大的触发功能和数据解析能力,能够设置特定的触发条件来捕获关键数据,并对各种dram复杂的时序行为进行解码和分析;节省测试时间:相较于示波器等使用多个单独的测试设备,嵌入式逻辑分析仪集成在 ate 测试机中,减少设备切换和连接的时间;达到系统级洞察:有助于ate测试工程师深入了解dram芯片测试情况,包括硬件和软件的交互,从而更好地进行系统级的测试和验证;达到灵活的测试设置:可以根据不同的测试需求进行灵活配置和编程,适应多种芯片和测试场景;紧凑集成:不占用额外的空间,嵌入式逻辑分析仪集成在ate测试控制芯片内部,与 ate 测试控制芯片的其他部件紧密集成,使整个测试系统更加简洁和高效;降低成本提高效益:由于不需要购买多个独立的逻辑分析仪器,能够在一定程度上降低成本;便于数据分析:直接将测试数据提供给 ate测试机的主控制系统,便于进行统一的数据管理和分析;缩短反馈时间:能够快速提供测试结果和反馈,有助于缩短dram芯片的测试时间,加快测试进度。

- 还没有人留言评论。精彩留言会获得点赞!