ZQ校准模块及存储器的制作方法

本发明涉及一种zq校准模块及具有该zq校准模块的存储器,尤其涉及一种适用于zq焊盘的焊盘电容较大的情况下进行zq校准的zq校准模块及具有该zq校准模块的存储器。

背景技术:

1、在当前的动态随机存取存储器dram(dynamic random access memory)的内存架构中,不论是个人电脑还是服务器系统都存在数据、命令和地址与主机host之间的交互,接口的信号的完整性非常重要。zq调整的目的是通过将内部阻抗与一个外接且不随环境变化的精准电阻240ω来进行比较,以实现输出驱动能力ron或片上终端阻抗odt的实时调整,纠正工作环境和工艺偏差的影响对其精度的影响,从而保证dram与主机host之间正常的数据交互。

2、首先,为了实现该功能,动态随机存取存储器dram保留了一个zq焊盘pad,用以连接外部的精准电阻240ω,但是,随着内存架构存储容量的增加,zq校准的协议越来越复杂,有时需要多个动态随机存取存储器dram分时地使用外接的精准电阻240ω,由此,使得zq焊盘pad上接入的器件越来越多,zq焊盘pad上的寄生电容增加,从而导致需要更多的感应时间使zq端的电压准确地反应内部电阻阻值。

3、其次,为了实现该功能,在设计中输出驱动能力ron往往需要更多的校正位数来覆盖更大范围的阻抗变化,由此来保证因工艺、温度、电压的变化对信号的完整性所带来的影响。

4、再者,因为动态随机存取存储器dram的工作频率越来越高,由此对于zq校准时间提出了更为严格的要求,需要一个快速校准机制在有限的时间内完成精确的zq校准。

5、固态技术协会jedec是微电子产业的领导标准机构,jedec对于主机host发出的zq命令分为zqcl(zq calibration long:长zq命令)和zq cs(calibration short:短zq命令)。

6、首先,zqcl是在系统上电或者系统重置reset之后,或者长时间没有调整时所进行的一次完整的zq调整过程。虽然,系统允许有稍长一点的完成时间,除了上电后首次进行zq校准之外,例如通常为zqcs的两倍时间,但是要求在当前电压、温度、工艺的状态下找到最佳代码来完成输出驱动能力ron或片上终端阻抗odt的实时调整。

7、其次,zqcs是系统发出的短zq命令,它可以在当前代码的基础上进行查找,要求在较短的时间内完成输出驱动能力ron或片上终端阻抗odt的实时调整。

8、在现有技术所涉及的zq校准模块中,一般包括2个上拉设备和下拉设备,先由主上拉设备通过其自身的感应点与外接的精准电阻240ω进行比较、即上拉设备与精准电阻进行分压,根据比较结果来校准主上拉设备的内部电阻。在完成主上拉设备的内部电阻的调整之后,将主上拉设备的基准代码发送至副上拉设备,并以调整后的副上拉设备为参照,对下拉设备进行校准。其中,主上拉设备的内部电阻的校准过程与下拉设备的内部电阻的校准过程基本是相同的,而且,无论是zqcl还是zqcs命令,zq校准的机制是一样的,一般都采用逐次逼近法。

9、其中,上拉设备的感应点是外部感应点。然而,随着zq焊盘pad的端部上的寄生电容越来越大,上拉设备的感应点所需的稳定时间越来越长,如果采取逐次逼近法,并假设需要调整的代码有n位,则需要2n步才能遍历上拉设备中所有调整代码code,留给每一步的时间就非常有限,这可能造成上拉设备和下拉设备的感应点还未充分感应分压点电压就已经开始与基准电压进行比较,这样会造成比较结果无法反映真正的分压情况,由此会给zq校准带来较大的误差。

10、另一方面,下拉设备是内部感应点,而它的寄生电容与zq焊盘pad相比会小很多,所以它的感应速度相对于上拉设备而言会快很多。然而,如果上拉设备提供的基准代码存在误差,则同样会给下拉设备带来误差,导致下拉设备的校准也不够准确。

技术实现思路

1、发明所要解决的技术问题

2、本发明正是为了解决上述这些问题而完成的,其目的在于,提供一种zq校准模块以及具有该zq校准模块的存储器,通过在zq校准单元内设置针对长校准模式zqcl的情况采用二分法来产生上拉校准代码和下拉校准代码的第一校准代码产生部、以及针对短校准模式zqcs的情况采用逐次逼近法来产生上拉校准代码和下拉校准代码的第二校准代码产生部,由此,在长校准模式zqcl的情况下,能够大大地减小比较的次数,从而在规定的时间内使每次zq校准的时间增加,以此来使感应电压准确地表示上拉设备和外部标准电阻rzq之间的分压情况,从而保证最终得到准确的上拉校准代码。

3、进一步地,根据本发明的zq校准模块以及具有该zq校准模块的存储器,在针对短校准模式zqcs采用逐次逼近法来进行zqcs校准的情况下,考虑到spec规定中zqcs校准的时间比zqcl校准的时间少,通过使产生下拉校准代码的最终值的时间缩短至产生上拉校准代码的最终值的时间的一半,把更多的时间分配给了上拉设备的zqcs过程,使上拉设备既可以完成更多步数的zqcs校准,又能够充分感应达到准确的分压点,而下拉设备由于需要的较小的感应时间,也依然可以完成同样步数的zqcs校准,找到准确的下拉校准代码。

4、用于解决技术问题的技术手段

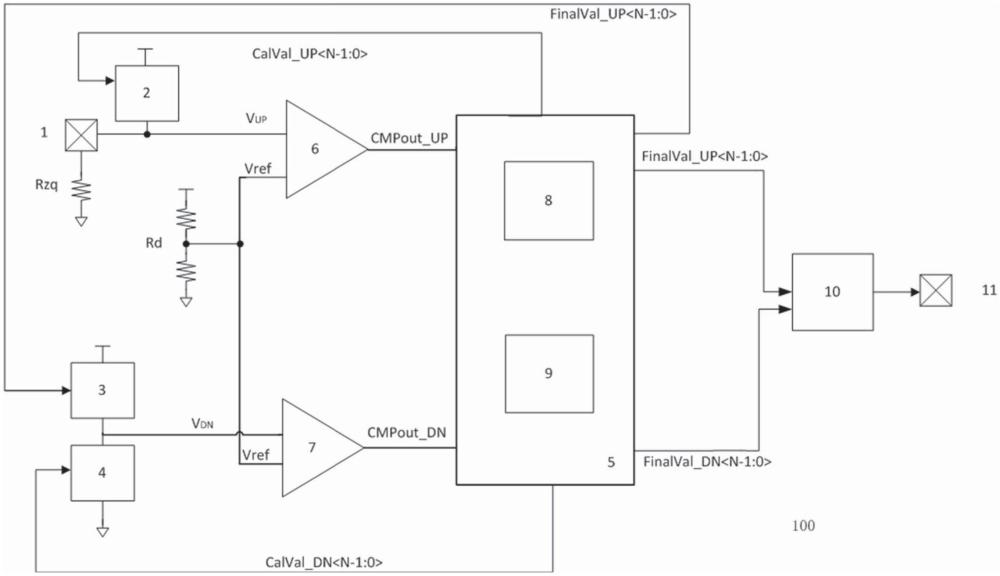

5、本发明一种zq校准模块,该zq校准模块具备:

6、zq焊盘,所述zq焊盘与外部标准电阻rzq连接;

7、第一上拉设备,所述第一上拉设备通过所述zq焊盘与所述外部标准电阻串联连接;

8、第二上拉设备;

9、下拉设备,所述下拉设备与所述第二上拉设备串联连接;

10、内部分压电阻;

11、第一比较器,所述第一比较器的一端与所述第一上拉设备和所述外部标准电阻的连接点相连接,所述第一比较器的另一端与所述内部分压电阻相连接;

12、第二比较器,所述第二比较器的一端与所述第二上拉设备和所述下拉设备的连接点相连接,所述第二比较器的另一端与所述内部分压电阻相连接;以及

13、zq校准单元,所述zq校准单元产生上拉校准代码来校准所述第一上拉设备、且产生下拉校准代码来校准所述下拉设备,且所述zq校准单元具有:

14、第一校准代码产生部,所述第一校准代码产生部在长校准模式的情况下采用二分法来产生所述上拉校准代码和所述下拉校准代码;以及

15、第二校准代码产生部,所述第二校准代码产生部在短校准模式的情况下采用逐次逼近法来产生所述上拉校准代码和所述下拉校准代码。

16、进一步地,本发明所涉及的zq校准模块中,在利用所述zq校准单元对所述第一上拉设备进行校准之后,所述第二上拉设备复制所述上拉校准代码。

17、进一步地,本发明所涉及的zq校准模块中,所述第一上拉设备和所述第二上拉设备均具有:

18、上拉主单元,所述上拉主单元包括上拉主电阻、和与所述上拉主电阻串联连接的上拉主开关;以及

19、上拉校准单元,所述上拉校准单元包括上拉校准电阻、和与所述上拉校准电阻串联连接的相互并联连接的多个上拉校准开关,

20、所述上拉主单元与所述上拉校准单元并联连接。

21、进一步地,本发明所涉及的zq校准模块中,所述上拉主电阻是大于240ω的电阻。

22、进一步地,本发明所涉及的zq校准模块中,所述上拉主开关和所述多个上拉校准开关均是pmos管。

23、进一步地,本发明所涉及的zq校准模块中,所述下拉设备具有:

24、下拉主单元,所述下拉主单元包括下拉主电阻、和与所述下拉主电阻串联连接的下拉主开关;以及

25、下拉校准单元,所述下拉校准单元包括下拉校准电阻、和与所述下拉校准电阻串联连接的相互并联连接的多个下拉校准开关,

26、所述下拉主单元与所述下拉校准单元并联连接。

27、进一步地,本发明所涉及的zq校准模块中,所述下拉主电阻是大于240ω的电阻。

28、进一步地,本发明所涉及的zq校准模块中,所述下拉主开关和所述多个下拉校准开关均是nmos管。

29、进一步地,本发明所涉及的zq校准模块中,所述第一校准代码产生部由多个多路选择器、多个触发器、多个求和平均器以及时钟发生器构成,

30、在校准所述第一上拉设备时,所述第一校准代码产生部根据所述第一比较器的比较结果,基于所述上拉校准代码的初始值、最大值和最小值并采用所述二分法来产生所述上拉校准代码的最终值,

31、在校准所述下拉设备时,所述第一校准代码产生部根据所述第二比较器的比较结果,基于所述下拉校准代码的初始值、最大值和最小值并采用所述二分法来产生所述下拉校准代码的最终值。

32、进一步地,本发明所涉及的zq校准模块中,在采用所述二分法时,产生所述上拉校准代码的最终值的时间与产生所述下拉校准代码的最终值的时间相同。

33、进一步地,本发明所涉及的zq校准模块中,产生所述上拉校准代码的最终值的时间和产生所述下拉校准代码的最终值的时间均为所述时钟发生器所产生的zq时钟的整数倍。

34、进一步地,本发明所涉及的zq校准模块中,所述第二校准代码产生部由多路选择器、多个触发器、加法器、以及时钟发生器构成,

35、在校准所述第一上拉设备时,所述第二校准代码产生部根据所述第一比较器的比较结果,基于所述上拉校准代码的当前值并采用所述逐次逼近法来产生所述上拉校准代码的最终值,

36、在校准所述下拉设备时,所述第二校准代码产生部根据所述第二比较器的比较结果,基于所述下拉校准代码的当前值并采用所述逐次逼近法来产生所述下拉校准代码的最终值。

37、进一步地,本发明所涉及的zq校准模块中,在采用所述逐次逼近法时,产生所述下拉校准代码的最终值的时间是产生所述上拉校准代码的最终值的时间的一半。

38、进一步地,本发明所涉及的zq校准模块中,产生所述上拉校准代码的最终值的时间和产生所述下拉校准代码的最终值的时间均为所述时钟发生器所产生的zq时钟的整数倍。

39、进一步地,本发明所涉及的zq校准模块中,所述外部标准电阻是一个240ω的低公差参考电阻。

40、本发明提供一种存储器,包括:如上所述的zq校准模块。

41、进一步地,本发明所涉及的存储器中,存储器是动态随机存取存储器。

42、发明效果

43、首先,根据本发明所涉及的zq校准模块以及具有该zq校准模块的存储器,通过在zq校准单元内设置针对长校准模式zqcl的情况采用二分法来产生上拉校准代码和下拉校准代码的第一校准代码产生部、以及针对短校准模式zqcs的情况采用逐次逼近法来产生上拉校准代码和下拉校准代码的第二校准代码产生部,由此,在长校准模式zqcl的情况下,能够大大地减小比较的次数,从而在规定的时间内使每次zq校准的时间增加,以此来使感应电压准确地表示上拉设备和外部标准电阻rzq之间的分压情况,从而保证最终得到准确的上拉校准代码。

44、更进一步地,根据本发明所涉及的zq校准模块以及具有该zq校准模块的存储器,在针对短校准模式zqcs采用逐次逼近法来进行zqcs校准的情况下,考虑到spec规定中zqcs校准的时间比zqcl校准的时间少,通过使产生下拉校准代码的最终值的时间缩短至产生上拉校准代码的最终值的时间的一半,就把更多的时间分配给了上拉设备的zqcs过程,使上拉设备既可以完成更多步数的zqcs校准,又能够充分感应达到准确的分压点,而下拉设备由于需要的较小的感应时间,也依然可以完成同样步数的zqcs校准,找到准确的下拉校准代码。

- 还没有人留言评论。精彩留言会获得点赞!