一种用于sub-6g频段的射频开关

技术领域

[0001]

本发明是一种用于sub-6g频段的射频开关,涉及集成电路设计及信号处理技术领域。

背景技术:[0002]

目前的5g通讯网络集中的频率都在6ghz以下,因此也称为sub-6g频段,随着5g无线通信技术的快速发展,射频应用越来越多,射频开关是射频接收机前端的关键模块,其电路拓扑图如图1所示,射频开关位于天线与收路的低噪声放大器(low-noise amplifier,lna)和发路的功率放大器(power-amplifier,pa)之间,对系统性能具有决定性的影响,其三个主要性能参数是:插入损耗(insertion loss)、隔离度(isolation)和抗静电(electro-static discharge)。传统射频开关由于担心引起额外的寄生电容等,在开关模块内部一般不加抗静电模块,而是将抗静电功能放在pa和lna模块中,这样还是会导致射频开关本身由于静电而引起失效。

技术实现要素:[0003]

本发明的目的是推出一种用于sub-6g频段的射频开关,可以根据频段工作需要来放置射频开关的个数,从而实现各种应用,具体开关在电路设计中采用两级式结构,具有低插入损耗和高隔离度的优点,同时在输入pa端和输出lna端都加入了抗静电电路结构,可以有效防止静电对芯片的损坏。

[0004]

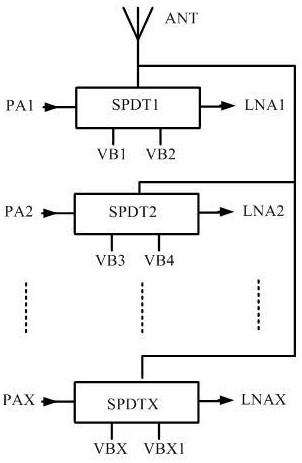

本发明的目的是这样实现的:一种用于sub-6g频段的射频天线开关,包含系统框图和具体电路图,具体的单刀双掷射频开关spdt(single-pole-double-throw, spdt)电路图含ant端、pa端、lna端、vb1端、vb2端和地线,其中ant端为天线发射端,pa端为射频信号输出端,lna端为射频信号输入端,vb1端、vb2端均为模式控制端,其特征在于,该基于绝缘体上硅工艺的cmos射频开关还含第一mos管m1、第二mos管m2、第三mos管m3、第四mos管m4、第五mos管m5、第六mos管m6、第七mos管m7、第八mos管m8、第九mos管m9、第十mos管m10、第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第五电阻r5、第六电阻r6、第七电阻r7、第八电阻r8、第九电阻r9、第十电阻r10,其中第一mos管m1、第二mos管m2、第三mos管m3、第四mos管m4、第五mos管m5、第六mos管m6、第七mos管m7、第八mos管m8、第九mos管m9、第十mos管m10均为nmos管。系统框图中包含一个天线端ant,以及多个射频开关,其特征在于每个射频开关的天线端ant都连接在一起,天线为共用端口;第一个射频开关spdt1,输入端为pa1,输出端为lna1,对应控制端为vb1和vb2;第二个射频开关spdt2,输入端为pa2,输出端为lna2,对应控制端为vb3和vb4;以此类推,第x个射频开关spdtx,输入端为pax,输出端为lnax,对应控制端为vbx和vbx1。

[0005]

一种用于sub-6g频段的射频开关的具体电路连接,第一mos管m1的栅极与第一电阻r1的一端连接,第二mos管m2的栅极与第二电阻r2的一端连接,第三mos管m3的栅极与第三电阻r3的一端连接,第四mos管m4的栅极与第四电阻r4的一端连接,第五mos管m5的栅极

与第五电阻r5的一端连接,第六mos管m6的栅极与第六电阻r6的一端连接,第七mos管m7的栅极与第七电阻r7的一端连接,第八mos管m8的栅极与第八电阻r8的一端连接, 第九mos管m9的栅极与第九电阻r9的一端连接,第十mos管m10的栅极与第十电阻r10的一端连接;第一电阻r1、第四电阻r4、第五电阻r5及第八电阻r8的另一端连接在一起后与vb2端连接;第二电阻r2、第三电阻r3、第六电阻r6及第七电阻r7的另一端连接在一起后与vb1端连接;第九电阻r9和第十电阻r10的另一端分别和地线连接在一起;第一mos管m1的漏极与第二mos管m2的漏极连接在一起后与ant端连接;第一mos管m1的源极、第三mos管m3的漏极与第五mos管m5的漏极连接在一起;第二mos管m2的源极、第四mos管m4的漏极与第六mos管m6的漏极连接在一起;第五mos管m5的源极、第七mos管m7的漏极和pa端连接在一起;第六mos管m6的源极、第八mos管m8管的漏极和lna端连接在一起;第三mos管m3、第四mos管m4、第七mos管m7及第八mos管m8的源极与地线连接;第九mos管m9的漏极和pa端相连,m9管的源极和地线相连;第十mos管m10的漏极和lna端相连,m10管的源极和地线相连。

[0006]

本发明能够通过简单电路结构实现高性能的射频开关,并对该射频开关进行可控单刀双掷(single-pole-double-throw, spdt)切换,同时在pa端和lna端加入抗静电模块,与传统的射频开关相比,本发明的优点在于:

⑴

、在电路设计中采用两级式结构,恰当选择主开关管器件尺寸,降低串联晶体管的沟道电阻,从而具有低插入损耗和高隔离度的优点;本发明具有极低的插入损耗,其插入损耗在关注频率2.4ghz处为-1db,而传统的射频开关的典型值为-2db,插入损耗改善最高可达1db。本发明具有较高的端口隔离度,本发明的双向隔离度在关注频率2.4ghz处为40db,而传统的射频开关的典型值为20~30db左右。

[0007]

⑵

、本发明在输入pa端和输出lna端加入抗静电模块,能够有效提高芯片的抗静电能力,从而减小由于静电而引起的失效。由于该种抗静电结构引入的寄生电容较小,因此对射频开关的性能几乎没有影响。

[0008]

第九mos管m9和第十mos管m10,是esd保护电路,其特征需要按照图4的尺寸进行设计,其尺寸参数直接决定esd性能。经过实际测试,本发明的抗静电达到了8kv的水平。传统的抗静电一般只有2kv的水平。

附图说明

[0009]

图1为本发明的电路拓扑图;图2为本发明的射频开关的系统框图;图3为本发明的射频开关电路图;图4为本发明的esd管的版图尺寸参数。

具体实施方式

[0010]

本发明的技术方案就是具体的实施例,这里就不再赘述实施例。下面详尽介绍本发明的工作过程。

[0011]

多模多频的工作原理参阅图2,当第一频段对应的spdt1需要工作时,就控制对应的控制端vb1和vb2,其他控制端口关闭,其他端口所对应的射频开关也就处于关闭状态。当第二频段对应的spdt2需要工作时,就控制对应的控制端vb3和vb4,其他控制端口关闭,其

他端口所对应的射频开关也就处于关闭状态;当第x频段对应的spdtx需要工作时,就控制对应的控制端vbx和vbx1,其他控制端口关闭,其他端口所对应的射频开关也就处于关闭状态。采用这种控制方式从而实现多模多频的应用。

[0012]

单个射频开关的工作原理参阅图3,当vb2端为高电平,vb1端为低电平时,本发明的射频开关处于发射模式。由于第一mos管m1及第五mos管m5的栅极电压为正,第三mos管m3及第七mos管m7的栅极电压为负,所以第一mos管m1及第五mos管m5导通,第三mos管m3及第七mos管m7截止,从pa端来的功率放大器输出信号可以传导到天线ant端;由于第二mos管m2及第六mos管m6的栅极电压为负,第四mos管m4及第八mos管m8的栅极电压为正,所以第二mos管m2及第六mos管m6截止,第四mos管m4及第八mos管m8导通,天线ant端到低噪声放大器路径关闭,且导通的第四mos管m4及第八mos管m8提供了到地的电流泻放路径。

[0013]

当vb2端为低电平,vb1端为高电平时,本发明的射频开关处于接收模式。由于第一mos管m1及第五mos管m5的栅极电压为负,第三mos管m3及第七mos管m7的栅极电压为正,所以第一mos管m1及第五mos管m5截止,第三mos管m3及第七mos管m7导通,从pa端到天线ant端关闭;由于第二mos管m2及第六mos管m6的栅极电压为正,第四mos管m4及第八mos管m8的栅极电压为负,所以第二mos管m2及第六mos管m6导通,第四mos管m4及第八mos管m8截止,天线ant端来的微小射频信号传送至低噪声放大器lna的输入端,且导通的第三mos管m3及第七mos管m7提供了到地的电流泻放路径。

[0014]

由于插入损耗主要由串联晶体管的沟道电阻决定,在给定频率下,适当增加选择主开关管第一mos管m1、第二mos管m2、第五mos管m5、第六mos管m6的尺寸,可以减小沟道电阻,但是过高的开关管面积会增加寄生电容,增加衬底耦合并降低隔离度。综合插入损耗和隔离度的折中考虑,仿真得到最合适的第一mos管m1、第二mos管m2、第五mos管m5、第六mos管m6的尺寸分别为400μm /0.25μm、400μm /0.25μm、160μm /0.25μm、160μm /0.25μm。第一电阻r1到第八电阻r8均为栅电阻,它们的作用是提高输入级线性度,阻值均为6k欧姆。

[0015]

第九mos管m9和第九电阻r9组成了pa端的抗静电模块,第十mos管m10和第十电阻r10组成了lna端的抗静电模块,m9管和m10管的尺寸都为400μm /0.25μm,电阻r9和电阻r10都为栅电阻,其阻值都为300欧姆。针对m9管和m10管,需要按照图示的尺寸设计版图,gate是栅极,source是源极,drain是漏极,contact是接触孔,栅极到源极接触孔的距离为0.5um,栅极到漏极接触孔的距离为3.5um,然后每条mos管的宽度w应该是50um,这些尺寸非常关键,直接影响最终的esd性能。

[0016]

虽然本发明利用具体的实施例进行说明,但是对实施例的说明并不限制本发明的范围。本领域内的熟练技术人员通过参考本发明的说明,在不背离本发明的精神和范围的情况下,容易进行各种修改或者可以对实施例进行组合。