制造III-V族半导体装置的互连件的方法及III-V族半导体装置与流程

制造iii-v族半导体装置的互连件的方法及iii-v族半导体装置

技术领域

1.本发明涉及一种iii-v族半导体装置及其制造方法,特别是涉及一种制造iii-v族半导体装置的互连件的方法,及iii-v族半导体装置。

背景技术:

2.以

ⅲ-ⅴ

族(如gan、gaas)为材料制成的异质结双极型晶体管(hbt)及高速电子迁移率晶体管(hemt)等功率元件,由于具有高功率、线性度佳、高截止频率和低损耗功率等优点,因此,被认为是可用于制作高频功率元件的最佳材料。

3.然而,因为高频功率元件是在大电压、大电流及高频率的操作条件下进行,因此,相较一般元件需要更高的电流承载能力及散热能力,但是目前常用于非高频的功率元件的2微米金属连接导线,其厚度并不足以承受大电压及大电流的操作条件。此外,对高频元件而言,当元件的操作频率提高,若金属连接导线的厚度不足,也会使得元件的寄生阻抗大幅增加而影响元件于高频的操作特性。因此,为了符合高频功率元件的操作特性,如何提供具有更高厚度的金属连接导线则为相关技术开发的重点。

4.例如,公开号为us2007/0040274a1的美国专利公开一种iii-v族半导体装置内连接导线的方法。其主要是以铜为内连接导线金属,通过介电层与光致抗蚀剂的层叠结构,提高可用以沉积铜金属内连接导线的厚度的空间,并利用在铜金属内连接导线与半导体层之间形成氮化钨(wnx)阻障层,以避免厚铜金属导线的铜原子扩散到与该厚铜金属导线连接的半导体层,而得到具有厚铜金属内连接导线的iii-v族半导体装置。

技术实现要素:

5.本发明的目的在于提供一种用于制造iii-v族半导体装置的互连件的方法。

6.本发明的制造iii-v族半导体装置的互连件的方法,包含下列步骤。

7.a)将具有第一厚度的正型光致抗蚀剂层施用于该iii-v族半导体装置的导性零件上。

8.b)将具有第二厚度的图像反转型光致抗蚀剂层施用于该正型光致抗蚀剂层上。

9.c)使该图像反转型光致抗蚀剂层及该正型光致抗蚀剂层接受图案式曝光,以使该图像反转型光致抗蚀剂层及该正型光致抗蚀剂层的每一者形成呈可显影型式的第一部分及呈不可显影型式的第二部分,且该图像反转型光致抗蚀剂层的该第一部分及该第二部分分别重叠于该正型光致抗蚀剂层的该第一部分及该第二部分上。

10.d)使该图像反转型光致抗蚀剂层接受图像反转烘烤,以使该图像反转型光致抗蚀剂层的该第一部分及该第二部分从可显影型式及不可显影型式转换成不可显影型式及可显影型式。

11.e)使该图像反转型光致抗蚀剂层及该正型光致抗蚀剂层接受全曝光,以使该正型光致抗蚀剂层的该第二部分从该不可显影型式转换成该可显影型式。

12.f)使该图像反转型光致抗蚀剂层及该正型光致抗蚀剂层接受显影,而自该图像反转型光致抗蚀剂层该第二部分向下移除至该iii-v族半导体装置的导性零件露出而形成开口,其中,该图像反转型光致抗蚀剂层及该正型光致抗蚀剂层共同形成下切侧壁,该下切侧壁围成该开口,而令该开口具有自该图像反转型光致抗蚀剂层向下渐增的径宽。

13.g)将扩散障壁层经由该开口沉积于该iii-v族半导体装置的该导性零件上。

14.h)将铜层经由该开口沉积于该扩散障壁层上形成该互连件。

15.较佳地,本发明所述的方法,还包含实施于步骤h)后的步骤i),移除该图像反转型光致抗蚀剂层及该正型光致抗蚀剂层。

16.较佳地,本发明所述的方法,其中,该步骤a)是通过将正型光致抗蚀剂以从500rpm至4500rpm的旋转速度旋涂于该iii-v族半导体装置的该导性零件上持续从5秒至60秒的一段时间而实施。

17.较佳地,本发明所述的方法,其中,该步骤b)是通过将图像反转型光致抗蚀剂以从500rpm至6000rpm的旋转速度旋涂于该正型光致抗蚀剂层上持续从5秒至60秒的一段时间而实施。

18.较佳地,本发明所述的方法,其中,该第二厚度小于该第一厚度。

19.较佳地,本发明所述的方法,其中,该第一厚度介于2μm至12μm,且该第二厚度介于1.14μm至2.3μm。

20.较佳地,本发明所述的方法,其中,该步骤c)中的该图案式曝光是通过使该图像反转型光致抗蚀剂层及该正型光致抗蚀剂层曝置于通过光罩的具有范围从365nm至436nm的波长的辐射,持续照射从0.3秒至2秒的一段时间而实施。

21.较佳地,本发明所述的方法,其中,该步骤d)中的该图像反转烘烤是于范围从100℃至120℃的烘烤温度持续范围从90秒至150秒的一段时间而实施。

22.较佳地,本发明所述的方法,其中,该步骤e)中的该全曝光是通过使该图像反转型光致抗蚀剂层及该正型光致抗蚀剂层曝置于具有范围从365nm至436nm的波长的辐射,持续照射5秒至15秒的一段时间而实施。

23.较佳地,本发明所述的方法,其中,该步骤f)中的该显影是于搅拌下的显影剂中持续从1.5分钟至5分钟的一段时间而实施。

24.较佳地,本发明所述的方法,其中,该步骤g)包含下列子步骤:

25.g1)将范围从10nm至50nm的厚度的第一钛层喷溅沉积于该iii-v族半导体装置的该导性零件上;

26.g2)将范围从30nm至60nm的厚度的氮化钨层喷溅沉积于该第一钛层上;以及

27.g3)将范围从10nm至50nm的厚度的第二钛层喷溅沉积于该氮化钨层上。

28.较佳地,本发明所述的方法,其中,该步骤h)是通过使用电子枪蒸发系统实施。

29.较佳地,本发明所述的方法,其中,该图像反转型光致抗蚀剂层及该正型光致抗蚀剂层是通过掀离(lift-off)程序移除。

30.本发明的另一目的在于提供iii-v族半导体装置。

31.本发明的iii-v族半导体装置,包含:基材、导性零件,及互连件。

32.该导性零件形成于该基材上,且该互连件是通过上文所述的方法形成于该导性零件上。

33.较佳地,本发明所述的iii-v族半导体装置,其中,该互连件具有大于3μm,且最高达10μm的厚度。

34.本发明的有益效果在于:利用图像反转型光致抗蚀剂层及该正型光致抗蚀剂层的层叠及显影特性,通过该正型光致抗蚀剂层增加厚度,而得以提升可用于沉积的开口空间,而得以沉积形成较大厚度的互连件。此外,还可通过显影形成的下切侧避,避免沉积过程互连件与光致抗蚀剂接触,而影响最终形成的互连件的结构。

附图说明

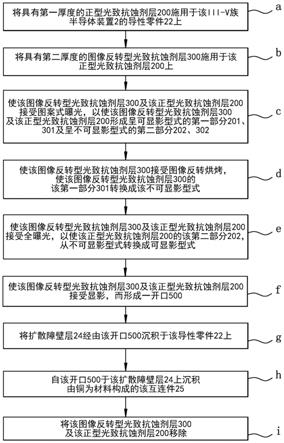

35.图1是说明本发明方法的该实施例的文字流程图;

36.图2是辅助说明图1该步骤(a)~(b)的流程示意图;

37.图3是辅助说明图1该步骤(c)的流程示意图;

38.图4是辅助说明图1该步骤(d)的流程示意图;

39.图5是辅助说明图1该步骤(e)的流程示意图;

40.图6是辅助说明图1该步骤(f)的流程示意图;

41.图7是辅助说明图1该步骤(g)~(h)的流程示意图;

42.图8是辅助说明图1该步骤(i)的流程示意图;及

43.图9是说明由该实施例制得的该iii-v族半导体装置的示意图。

具体实施方式

44.下面结合附图及实施例对本发明进行详细说明:

45.在本发明被详细描述前,应当注意在以下的说明内容中,类似的组件是以相同的编号来表示。

46.参阅图9,本发明用于制造互连件的方法的一实施例是可用制造用于如图9所示含有该互连件25的iii-v族半导体装置2。利用本发明的方法可制得厚度大于3μm且最高达10μm的厚度的互连件25,而可令该iii-v族半导体装置2可更适用于高频元件。

47.配合参阅图8,该iii-v族半导体装置2具有一iii-v族半导体元件21、一位于该iii-v族半导体元件21的顶面的导性零件22,一覆盖该导性零件22并具有一令该导性零件22的顶面露出的开口的介电绝缘层23、一经由该开口与该导性零件22的顶面连接的互连件25,以及一介于该导性零件22的顶面与该互连件25之间的扩散障壁层24。其中,该互连件25是一由导电性及散热性均佳的铜所构成。

48.参阅图1,详细地说,本发明用于制造该互连件25的方法的该实施例包含以下步骤。

49.配合参阅图2,首先进行步骤(a),将具有一第一厚度的一正型光致抗蚀剂层200施用于该iii-v族半导体元件21的导性零件22上。

50.该iii-v族半导体元件21可以是一般半导体功率元件,例如由砷化镓(gaas)为材料构成的异质结晶体管(hbt)、高电子迁移率晶体管(hemt)、或金属氧化物半导体场效应晶体管(mosfet)等。该导性零件22是位于该iii-v族半导体元件21的顶面用于令该iii-v族半导体元件21对外连接的电极。

51.该步骤(a)是利用旋转涂布(spin coating)方式,将一正型光致抗蚀剂涂布于该

导性零件22表面,经干燥后而形成该正型光致抗蚀剂层200。该正型光致抗蚀剂为一般半导体制程常用,于受光(例如uv光)照射后可溶解的光致抗蚀剂。本实施例中该正型光致抗蚀剂是以厚膜正型光致抗蚀剂(厂牌:merck,型号:az4620)为例说明。

52.接着,进行步骤(b),将具有一第二厚度的一图像反转型(image-reversible)光致抗蚀剂层300施用于该正型光致抗蚀剂层200上。

53.详细的说,该图像反转型光致抗蚀剂层300是利用旋转涂布方式将一图像反转型光致抗蚀剂涂布于该正型光致抗蚀剂层200上后经干燥而得。

54.该图像反转型光致抗蚀剂具有正型光致抗蚀剂特性,并可经由反转烤(reversal back)以及全面曝光(flood exposure)后,将原曝光可溶区域转成不可溶,而具有负光致抗蚀剂特性,并可在显影后于光致抗蚀剂层产生纵向内切的下切侧壁(undercut)。本实施例中该图像反转型光致抗蚀剂是以az5214e(厂牌:merck)为例说明。

55.利用该步骤(a)、(b)的旋转涂布参数控制可得到预设厚度的该正型光致抗蚀剂层200及图像反转型光致抗蚀剂层300。

56.于一些实施例中,该步骤(a)的旋转涂布是在转速500~4500rpm、时间5~60秒的条件下进行,且该正型光致抗蚀剂层200的第一厚度约介于2~12μm,该步骤(b)的旋转涂布是在转速500~6000rpm、时间5~60秒的条件下进行,且该图像反转型光致抗蚀剂层300的第二厚度约介于1.14~2.3μm。较佳地,该正型光致抗蚀剂层200的厚度大于该图像反转型光致抗蚀剂层300的厚度。

57.接着,配合参阅图3,进行步骤(c),使该图像反转型光致抗蚀剂层300及该正型光致抗蚀剂层200接受图案式曝光(pattern wise exposure)。以使该图像反转型光致抗蚀剂层300及该正型光致抗蚀剂层200的每一者形成呈可显影型式的一第一部分201、301及呈不可显影型式的一第二部分202、302,且该图像反转型光致抗蚀剂层300的该第一部分301及该第二部分302分别重叠于该正型光致抗蚀剂层200的该第一部分201及该第二部分202上。

58.详细的说,该步骤(c)是利用波长365~436nm的近紫外光(nuv)透过光罩400,持续照射该图像反转型光致抗蚀剂层300及该正型光致抗蚀剂层200约0.3~2秒,令该图像反转型光致抗蚀剂层300及该正型光致抗蚀剂层200于受到光照射的区域转变成可显影型式的该第一部分201、301,而未受到光照射的区域则维持为不可显影型式的该第二部分202、302。图3中,x表示可显影(溶)区域,即为该第一部分201、301。

59.于本实施例中该步骤(c)是利用波长365nm的uv光,曝光时间1.2秒,进行图案化曝光为例说明。

60.接着,配合参阅图4,进行步骤(d),使该图像反转型光致抗蚀剂层接受图像反转烘烤(image reversal bake),以令该图像反转型光致抗蚀剂层300的该第一部分301从该可显影型式转换成该不可显影型式。

61.详细的说,该步骤(d)是将经过图案式曝光后的光致抗蚀剂于100~120℃下进行反转烘烤约90~150秒,令该图像反转型光致抗蚀剂层300的第一部分301于烘烤后从可显影型式转换成不可显影型式,该第二部分302则从不可显影型式转换成可显影型式。而该正型光致抗蚀剂层200因不受反转烘烤影响,因此,其第一部分201及第二部分202,仍分别维持为可显影型式及不可显影型式。图4中,x表示可显影(溶)区域。于本实施例中,该步骤(d)是在110℃、烘烤时间120秒的条件下进行反转烘烤。

62.接着,配合参阅图5,进行步骤(e),使该图像反转型光致抗蚀剂层300及该正型光致抗蚀剂层200接受全曝光(flood exposure),以使该正型光致抗蚀剂层200的该第二部分202,从该不可显影型式转换成该可显影型式。

63.详细的说,该步骤(e)是将经过反转烘烤的光致抗蚀剂,曝置于具有波长范围从365nm至436nm的辐射照射下,持续照射5秒至15秒接受全曝光,从而令该正型光致抗蚀剂层200于该步骤(c)中未照射到紫外光而呈不可显影型式的该第二部分202,于该步骤(e)照光后转变成可显影型式。也就是说,经过该步骤(e)后,该图像反转型光致抗蚀剂层300的该第一部分301及该第二部分302分别呈不可显影型式及可显影型式,而该正型光致抗蚀剂层200该第一部分201及第二部分202则均为可显影型式。

64.然后,配合参阅图6,进行步骤(f),使该图像反转型光致抗蚀剂层300及该正型光致抗蚀剂层200接受显影,自该图像反转型光致抗蚀剂层300的该第二部分302向下移除至该导性零件22露出而形成一开口500。

65.详细的说,该步骤(f)是利用显影液自该图像反转型光致抗蚀剂层300的第二部分302向下移除该图像反转型光致抗蚀剂层300的第二部分302以及该正型光致抗蚀剂层200的第二部分202,并于显影过程令该图像反转型光致抗蚀剂层300及该正型光致抗蚀剂层200共同形成一下切侧壁(undercut)303,该下切侧壁303会围成该开口500,而令显影后形成的该开口500具有自该图像反转型光致抗蚀剂层300向下渐增的径宽。

66.接着,配合参阅图7,进行步骤(g),将一扩散障壁层24经由该开口500沉积于该iii-v族半导体元件21的该导性零件22上。

67.详细的说,该步骤(g)是经由该开口500先沉积该扩散障壁层24,以避免后续预形成的厚铜层的铜原子扩散至该半导体元件21,而影响该半导体元件21特性的问题,且该扩散障壁层24可视需求及后续制程而为单层或多层结构。于本实施例中,是以该扩散障壁层24为多层结构为例说明。

68.详细的说,该步骤(g)是包含以下子步骤。

69.首先,进行子步骤(g1),利用喷溅方式于该导性零件22上形成一层由钛构成的第一钛层241,且该第一钛层241的厚度介于10nm至50nm。

70.接着,进行子步骤(g2),利用喷溅方式于该第一钛层241上形成一层由氮化钨构成的氮化钨层242,且该氮化钨层242的厚度介于30nm至60nm。

71.最后,进行子步骤(g3),利用喷溅方式于该氮化钨层242上形成一层由钛构成的第二钛层243,且该第二钛层243的厚度介于10nm至50nm,而得到该扩散障壁层31。

72.然后,续配合参阅图7,进行步骤(h),自该开口500于该扩散障壁层24上沉积一层由铜为材料构成并具有预定厚度的铜层,而形成该互连件25。于沉积该厚铜层的过程中,因为该步骤(g)形成的该开口500为具有向下渐增的径宽,因此,于沉积过程中可维持令该厚铜层不与该下切侧壁303接触,而可令最终形成于该开口500内的该互连件25可与该下切侧壁303形成间距而不相接触。

73.于一些实施例中,该步骤(h)的铜层是利用电子枪蒸镀方式沉积而得。

74.最后,配合参阅图8、9,进行该步骤(i),将该图像反转型光致抗蚀剂层300及该正型光致抗蚀剂层200利用掀离(lift-off)程序移除,即可完成该互连件25的制作,而得到如图9所示具有该互连件25的iii-v族半导体装置2。

75.综上所述,本发明利用正型光致抗蚀剂跟图像反转型光致抗蚀剂搭配,让正型光致抗蚀剂以厚膜方式先形成一具有较大预定厚度的正型光致抗蚀剂层200,通过该正型光致抗蚀剂层200增加厚度,而得以提升后续可用于沉积该连接件25的空间,而可得到具较大厚度的互连件25。并利用形成于该正型光致抗蚀剂层200上的图像反转型光致抗蚀剂层300的绕射特性,而可在经图像反转后将光致抗蚀剂上端接受曝光剂量较多的光致抗蚀剂保留下来,因此,于显影后可形成负侧壁角度(即下切侧壁),而得到上窄下宽形态的开口500,利用该开口500上窄下宽的特性,使得后续沉积该厚铜层时,可避免铜层与该下切侧壁303接触,因此,可更易移除该图像反转型光致抗蚀剂层300及该正型光致抗蚀剂层200,而不影响该连接件25的结构及该连接件25结构的完整性,故确实可达成本发明的目的。

76.以上所述仅为本发明较佳实施例,然其并非用以限定本发明的范围,任何熟悉本项技术的人员,在不脱离本发明的精神和范围内,可在此基础上做进一步的改进和变化,因此本发明的保护范围当以本申请的权利要求书所界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1