包括芯层的嵌入式迹线基板(ETS)中的高密度互连的制作方法

包括芯层的嵌入式迹线基板(ets)中的高密度互连

背景技术:

[0001]

相关申请的交叉引用

[0002]

本申请要求于2018年11月13日在美国专利商标局提交的非临时申请no.16/189,128以及于2018年7月6日在美国专利商标局提交的临时申请no.62/694,839的优先权和权益,这些申请的全部内容通过援引如同在下文全面阐述那样且出于所有适用目的被纳入于此。

技术领域

[0003]

各种特征涉及用于集成器件的基板,但更具体地涉及包括芯层的嵌入式迹线基板(ets)中的高密度互连。

[0004]

背景技术

[0005]

图1解说了包括基板102和管芯104的集成器件100。管芯104通过多个焊料互连140耦合到基板102。集成器件100被设计成在小型便携式设备(诸如移动电话)中使用。基板102可以是嵌入式迹线基板(ets),其被设计和制造成用于具有小占用面积的设备,诸如移动设备。类似地,管芯104可被设计和制造成在移动设备中使用。

[0006]

基板102包括多个电介质层120和多个互连122。每个电介质层120包括图案化的金属层和通孔。基板102包括第一阻焊层124、第二阻焊层126和多个焊料互连130。基板102是无芯基板。由于被用于制造基板102的工艺,基板102和集成器件100没有被设计成用于大于移动设备的设备。尽管嵌入式迹线基板(ets)可能适用于在移动设备或具有小占用面积的设备中使用,但嵌入式迹线基板(ets)不适合大型设备,诸如机动交通工具中使用的设备。重新设计最初被设计成用于移动设备的管芯,以使其可以在机动交通工具中使用可能会非常昂贵,并且因此不是成本有效的。

[0007]

因此,存在对于提供能在较大设备(诸如机动交通工具)中实现而不必重新设计管芯的集成器件的需要。理想地,此类设备可以使用已被设计成用于移动设备、但可以在交通工具(例如,车载应用)中使用的管芯。

[0008]

概述

[0009]

各种特征涉及用于集成器件的基板,但更具体地涉及包括芯层的嵌入式迹线基板(ets)中的高密度互连。

[0010]

一个示例提供了一种包括管芯和耦合到该管芯的基板的集成器件。该基板包括芯基板部分、无芯基板部分、和第二电介质层。该芯基板部分包括:具有第一芯表面的芯层以及多个芯基板互连,每个芯基板互连具有第一最小宽度,其中该多个芯基板互连包括形成在该芯层的第一表面上的多个表面芯基板互连。该无芯基板部分包括:具有第一电介质表面的第一电介质层以及多个基板互连,第一电介质表面面向该芯层的第一芯表面,每个基板互连具有第二最小宽度,第二最小宽度小于第一最小宽度,其中该多个基板互连包括形成在第一电介质表面上的多个互连。第二电介质层被形成在该芯基板部分与该无芯基板部分之间,以使得该多个表面芯基板互连和该多个基板互连位于第二电介质层中。

[0011]

另一示例提供了一种包括第一基板部分、第二基板部分、和第二电介质层的基板。第一基板部分包括:具有第一芯表面的芯层以及多个芯基板互连,每个芯基板互连具有第一最小宽度,其中该多个芯基板互连包括形成在该芯层的第一芯表面上的多个表面芯基板互连。第二基板部分包括:具有第一电介质表面的第一电介质层以及多个基板互连,第一电介质表面面向该芯层的第一芯表面,每个基板互连具有第二最小宽度,第二最小宽度小于第一最小宽度,其中该多个基板互连包括形成在第一电介质表面上的多个互连。第二电介质层被形成在第一基板部分与第二基板部分之间,以使得该多个表面芯基板互连和该多个基板互连位于第二电介质层中。

[0012]

另一示例提供了一种用于制造基板的方法。该方法提供一种芯基板,该芯基板包括:(i)具有第一芯表面的芯层;以及(ii)多个芯基板互连,每个芯基板互连具有第一最小宽度,其中该多个芯基板互连包括形成在该芯层的第一芯表面上的多个表面芯基板互连。该方法在该芯基板上提供第二电介质层。该方法在第二电介质层和该芯基板上提供嵌入式迹线基板(ets),以使得第二电介质层位于该芯基板与该ets之间。该ets包括:(i)具有第一电介质表面的第一电介质层,第一电介质表面面向该芯层的第一芯表面;以及(ii)多个基板互连,每个基板互连具有第二最小宽度,第二最小宽度小于第一最小宽度。该多个基板互连包括形成在第一电介质表面上的多个互连。该多个表面芯基板互连和该多个基板互连位于第二电介质层中。

[0013]

附图简述

[0014]

在结合附图理解下面阐述的详细描述时,各种特征、本质和优点会变得明显,在附图中,相像的附图标记贯穿始终作相应标识。

[0015]

图1解说了包括管芯和基板的器件的剖视图。

[0016]

图2解说了包括管芯和具有芯层的嵌入式迹线基板(ets)的封装的剖视图。

[0017]

图3解说了芯基板的凸块部分的平面视图。

[0018]

图4解说了嵌入式迹线基板的凸块部分的平面视图。

[0019]

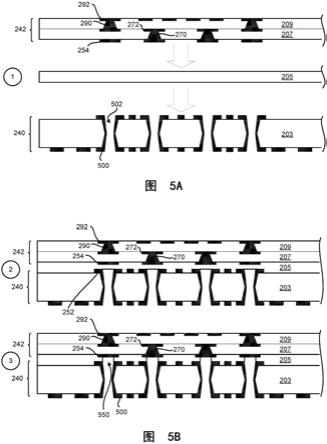

图5(包括图5a-5d)解说了用于制造包括具有芯层的嵌入式迹线基板(ets)的基板的示例性序列。

[0020]

图6解说了包括管芯和具有芯层的嵌入式迹线基板(ets)的另一封装的剖视图,该芯层包括加盖通孔。

[0021]

图7(包括图7a-7f)解说了用于制造包括具有芯层的嵌入式迹线基板(ets)的基板的示例性序列,该芯层包括加盖通孔。

[0022]

图8解说了包括管芯和具有芯层的嵌入式迹线基板(ets)的另一封装的剖视图,该芯层包括未加盖通孔。

[0023]

图9(包括图9a-9e)解说了用于制造包括具有芯层的嵌入式迹线基板(ets)的基板的示例性序列,该芯层包括未加盖通孔。

[0024]

图10解说了用于制造包括具有芯层的嵌入式迹线基板(ets)的基板的方法的示例性流程图。

[0025]

图11(包括图11a-11b)解说了用于制造具有芯层的基板的示例性序列。

[0026]

图12解说了用于制造具有芯层的另一基板的示例性序列。

[0027]

图13解说了用于制造具有芯层的基板的方法的示例性流程图。

[0028]

图14(包括图14a-14b)解说了用于制造无芯基板的示例性序列。

[0029]

图15解说了用于制造无芯基板的方法的示例性流程图。

[0030]

图16解说了可集成本文所描述的管芯、晶片、集成器件、集成无源器件(ipd)、器件封装、封装、集成电路和/或pcb的各种电子设备。

[0031]

详细描述

[0032]

在以下描述中,给出了具体细节以提供对本公开的各个方面的透彻理解。然而,本领域普通技术人员将理解,没有这些具体细节也可以实践这些方面。例如,电路可能用框图示出以避免使这些方面湮没在不必要的细节中。在其他实例中,公知的电路、结构和技术可能不被详细示出以免湮没本公开的这些方面。

[0033]

本公开内容描述了一种基板,其包括第一基板部分、第二基板部分、和第二电介质层。第一基板部分可以是芯基板。第一基板部分包括:具有第一芯表面的芯层以及多个芯基板互连,每个芯基板互连具有第一最小宽度,其中该多个芯基板互连包括形成在芯层的第一表面上的多个表面芯基板互连。第二基板部分可以是无芯基板,诸如嵌入式迹线基板(ets)。第二基板部分包括:具有第一电介质表面的第一电介质层以及多个基板互连,该第一电介质表面面向芯层的第一芯表面。每个基板互连具有第二最小宽度。第二最小宽度小于第一最小宽度。多个基板互连包括形成在第一电介质表面上的多个互连。第二电介质层被形成在第一基板部分与第二基板部分之间以使得该多个表面芯基板互连和该多个基板互连位于第二电介质层中。在一些实现中,基板是交通工具(例如,汽车)中实现的集成器件的一部分。在一些实现中,基板是包括管芯的器件(例如,集成器件)的一部分,其中该管芯被设计成用于移动设备。

[0034]

包括具有芯层的嵌入式迹线基板(ets)的示例性器件

[0035]

图2解说了包括基板202和管芯208的器件200的剖视图。器件200可以是在交通工具(例如,汽车、卡车、摩托车)中实现的集成器件。管芯208可具有高密度凸块互连。例如,管芯208可包括具有在0.35-0.4毫米(mm)的范围中的节距的凸块互连。管芯208可最初设计成在移动设备中实现。被设计成用于移动设备的管芯可具有低的电压和/或电流要求。比移动设备大的设备(诸如机动交通工具中的设备)可能比移动设备在更高的电压和/或电流下操作。

[0036]

如将在下面进一步描述的,基板202的第一表面(例如,面向管芯208的表面)可具有第一多个凸块互连,该第一多个凸块互连可具有在0.35-0.4毫米(mm)的范围中的节距,并且基板202的第二表面(例如,背向管芯208的表面、与基板的第一表面相对的表面)可具有第二多个凸块互连,该第二多个凸块互连可具有在0.7-0.8毫米(mm)的范围中的节距。

[0037]

基板202包括第一基板部分240(例如,芯基板部分)和第二基板部分242(例如,无芯基板部分)。第一基板部分240可以是芯基板,而第二基板部分可以是嵌入式迹线基板(ets)。第二基板部分242可以是无芯基板。第一基板部分240通过电介质层205(例如,第二电介质层)耦合到第二基板部分242。如将在下面进一步描述的,电介质层205包括两个图案化金属层,即来自第一基板部分240的图案化金属层和来自第二基板部分242的图案化金属层。在一些实现中,第一基板部分240的图案化金属层限定第一基板部分240的多个互连,并且第二基板部分242的图案化金属层限定第二基板部分242的多个互连。

[0038]

第一基板部分240包括芯层203、电介质层201、以及多个芯基板互连210(例如,芯

焊盘、芯迹线、芯通孔)。第一基板部分240可以是芯基板。多个芯基板互连210包括焊盘222、通孔214、焊盘212、芯通孔230和焊盘252。多个芯基板210中的一些可以是表面芯基板互连。例如,多个表面芯基板互连可以包括:焊盘212、焊盘252、焊盘612、焊盘622、焊盘812、焊盘822、和/或形成在芯层203的表面(例如,第一芯表面、第二芯表面)上的任何互连(例如,焊盘、迹线)。芯通孔230穿过芯层203。如图2中所示,芯通孔230包括非垂直壁(例如,对角壁、倾斜的壁)。在一些实现中,来自多个芯基板互连210中的每个芯基板互连具有最小宽度15微米(μm),并且相邻芯基板互连之间的最小间隔为10微米(μm)。多个芯基板互连210可以使用半加成法(sap)或改良型半加成法(msap)来制造。

[0039]

多个芯基板互连210可以包括具有在0.7-0.8毫米(mm)的范围中的节距的第二多个凸块互连。第二多个凸块互连可以包括形成在电介质层201上的焊盘(例如,焊盘222)。第二多个凸块互连可被耦合到多个焊料互连(例如,焊球(未示出))。

[0040]

第二基板部分242包括电介质层207、电介质层209、多个基板互连280(例如,基板焊盘、基板迹线、基板通孔)。电介质层207可以是第一电介质层。第二基板部分242可以是无芯基板(例如,嵌入式迹线基板(ets))。

[0041]

多个基板互连280包括:基板焊盘254、基板通孔270、基板焊盘272、基板通孔290和基板焊盘292。第二基板部分242的每个电介质层包括一个图案化金属层和多个通孔。电介质层207可包括面向芯层203的第一芯表面的第一电介质表面。可以在电介质层207的第一电介质表面上形成多个互连。例如,基板焊盘254(例如,互连)在电介质层207(例如,第一电介质层)的第一电介质表面上形成。基板焊盘254可以是电介质层207的图案化金属层的一部分。类似地,电介质层209包括基板焊盘292,其是电介质层209的图案化金属层的一部分。在一些实现中,来自多个基板互连280中的每个基板互连具有最小宽度6微米(μm),并且相邻基板互连之间的最小间隔为8微米(μm)。

[0042]

多个基板互连280可以包括可具有在0.35-0.4毫米(mm)的范围中的节距的第一多个凸块互连。该第一多个凸块互连可以包括形成在电介质层209中的焊盘(例如,基板焊盘292)。第一多个凸块互连可被耦合到多个焊料互连262(例如,焊球),该多个焊料互连262被耦合到管芯208。多个焊料互连262可以是将管芯208耦合到基板202的互连(例如,柱、铜柱)的一部分。

[0043]

电介质层205(例如,第二电介质层)耦合在并且位于第一基板部分240(例如,芯基板)与第二基板部分242(例如,无芯基板、嵌入式迹线基板(ets))之间。电介质层205可以是单个电介质层。电介质层205被耦合到第一基板部分240的芯层203、以及第二基板部分242的电介质层207。

[0044]

电介质层205被形成在第一基板部分240与第二基板部分242之间以使得来自多个芯基板互连210中的一些芯基板互连(例如,焊盘252)和来自多个基板互连280中的一些基板互连(例如,焊盘254)位于电介质层205中。因此,如图2中所示,电介质层205包括两个图案化金属层,即来自第一基板部分240的一个图案化金属层和来自第二基板部分242的一个图案化金属层。

[0045]

电介质层205还包括多个通孔250,其被耦合到多个芯基板互连210和多个基板互连280。

[0046]

如将在下面进一步描述的,第一基板部分240、电介质层205和第二基板部分242可

被耦合在一起(例如,层压在一起)以形成基板202。该工艺允许第一多个凸块互连(例如,被耦合到焊料的互连)具有在0.35-0.4毫米(mm)的范围中的节距,以及第二多个凸块互连具有在0.7-0.8毫米(mm)的范围中的节距。芯层203的总厚度可以在150-250微米(μm)的范围中。在一些实现中,基板202的总厚度可以在150-1200微米(μm)的范围中。图2解说了包括3个金属层的第二基板部分242。然而,应注意,不同的实现可以使用具有不同金属层(例如,2个金属层)和/或不同数目的电介质层的基板部分。不同的实现可以使用具有不同厚度的芯层。例如,本公开中的不同基板可具有芯层203,该芯层203可具有在150-1200微米(μm)的范围中的总厚度。

[0047]

图3和4解说了基板202的不同部分的示例性平面视图。图3解说了第一基板部分240的一部分300的平面视图,而图4解说了第二基板部分242的一部分400的平面视图。图3和4的平面视图可以表示沿着基板的一个或多个x-y平面的视图。

[0048]

图3可以解说形成在电介质层201中和/或上的互连。该部分300包括多个互连302(例如,芯基板互连)和多个凸块区域304。凸块区域304可以是基板202的耦合到焊料互连(例如,焊球、球栅阵列(bga))的区域。该部分300可以是第一基板部分240的一部分,该部分背离耦合到基板202的管芯。凸块区域304可具有在0.7-0.8毫米(mm)的范围中的节距。在一些实现中,多个互连302可具有最小宽度(w

c

)值15微米(μm)、最小间隔(s

c

)值10微米(μm)、以及最小节距值25微米(μm)。

[0049]

图4可以解说形成在电介质层209中和/或上的互连。该部分400包括多个互连402(例如,芯互连)和多个凸块区域404。凸块区域404可以是基板202的耦合到管芯(例如,208)的焊料互连的区域。该部分400可以是第二基板部分242的一部分,该部分面向耦合到基板202的管芯。凸块区域可具有在0.35-0.4毫米(mm)的范围中的节距。在一些实现中,多个互连402具有最小宽度(w

e

)值6微米(μm)、最小间隔(s

e

)值8微米(μm)、以及最小节距值14微米(μm)。

[0050]

图3和4解说了第一基板部分240包括具有比第二基板部分242的互连和凸块区域的最小宽度、最小间隔、和/或最小节距更大的最小宽度、最小间隔、和/或最小节距的互连和凸块区域。

[0051]

在一些实现中,基板的以上配置允许被配置成用于移动应用的管芯被用于车载应用而无需重新设计该管芯。基板可被设计成容适管芯的间隔、节距和互连密度要求,同时还容适较大设备(诸如交通工具中的设备)的间隔、节距和互连密度要求。例如,移动设备的管芯由于其精细的互连宽度、间隔和节距而具有较大密度的互连,而比移动设备更大的设备包括具有较大的最小宽度、间隔和节距互连要求的互连。在一些实现中,所公开的基板可使用所公开的工艺来制造,这些工艺实现一种基板,该基板具有针对该基板的不同部分的不同的最小宽度、间隔和节距的互连设计。

[0052]

已经描述了包括针对基板的不同部分的不同的最小宽度、间隔和节距的互连设计的一种基板,现在将在下面描述用于制造所公开的基板的方法。

[0053]

用于制造具有芯层的嵌入式迹线基板(ets)的示例性序列

[0054]

在一些实现中,制造基板包括若干过程。图5(其包括图5a-5d)解说了用于提供或制造基板(例如,具有芯层的嵌入式迹线基板(ets))的示例性序列。在一些实现中,图5a-5d的序列可被用来提供或制造图2的基板、其他基板、和/或本公开中所描述的其他器件。

[0055]

应当注意,图5a-5c的序列可以组合一个或多个阶段以便简化和/或阐明用于提供或制造基板的序列。在一些实现中,各过程的次序可被改变或修改。在一些实现中,可以在不脱离本公开的精神的情况下替代或置换一个或多个过程。

[0056]

如图5a中所示,阶段1解说了第二基板部分242被耦合到第一基板部分240以使得电介质层205在第一基板部分240与第二基板部分242之间。层压工艺可被用于耦合第一基板部分240、电介质层205、以及第二基板部分242。在一些实现中,第一基板部分240包括芯层203和穿过芯层203的多个空腔502。第一基板部分240包括在第一基板部分240的表面上的至少一个图案化金属层500。如图2中所描述的,至少一个图案化金属层500可限定第一基板部分240的互连(例如,芯基板互连)。例如,至少一个图案化金属层500可以限定焊盘252、通孔230和焊盘212。至少一个图案化金属层500可以包括晶种层。芯层203可以包括不同的电介质材料,诸如硅、玻璃、石英、环氧树脂或其组合。第一基板部分240的芯层203可具有在150-250微米(μm)的范围中的厚度。电介质层205可以包括干膜,诸如增层绝缘膜(abf)和/或预浸料。电介质层207和/或电介质层209可以包括聚酰亚胺。

[0057]

如图5b中所示,阶段2解说了在第二基板部分242已经通过电介质层205耦合到第一基板部分240之后的状态。层压工艺可被用于耦合第一基板部分240、电介质层205、以及第二基板部分242。电介质层205封装来自第一基板部分240的一些互连(例如,焊盘252)和来自第二基板部分242的一些互连(例如,焊盘254)。

[0058]

阶段3解说了在电介质层205中形成空腔550之后的状态。不同实现可使用不同工艺来形成空腔。在一些实现中,激光蚀刻工艺被用于形成空腔。在一些实现中,光刻工艺可被用于形成空腔。

[0059]

如图5c中所示,阶段4解说了在电介质层205中形成多个通孔250并且焊盘252和通孔230的剩余部分被形成之后的状态。镀敷工艺可被用来形成金属层,该金属层限定多个通孔250、焊盘252和通孔230。在一些实现中,通孔250、焊盘252和/或通孔230可以共享相同的金属(例如,相同的金属层)。例如,在一些实现中,在通孔250、焊盘252和/或通孔230之间可以不存在水平界面。在图7d中描述了共享相同金属(例如,金属层)的示例。

[0060]

阶段5解说了在芯层203上形成电介质层201并且该电介质层201的各部分已被选择性地移除之后的状态。例如,已经在电介质层201中形成空腔510。

[0061]

如图5d中所示,阶段6解说了在电介质层201中和/或上形成互连之后的状态。在一些实现中,镀敷工艺被用于形成互连(例如,焊盘212、通孔214、焊盘222)。

[0062]

阶段7解说了在基板202上形成第一阻焊层204和第二阻焊层206之后的状态。

[0063]

图5a-5d解说了允许制造一种基板的过程,该基板包括针对该基板的不同部分的不同的最小宽度和最小间隔。

[0064]

包括具有芯层的嵌入式迹线基板(ets)的示例性器件

[0065]

图6解说了包括基板602和管芯208的另一器件600的剖视图。器件600可以是在交通工具(例如,汽车、卡车、摩托车)中实现的集成器件。图6的器件600类似于图2的器件200。器件600包括具有加盖通孔的基板。器件600可具有与针对器件200所描述的类似尺寸、最小宽度、最小间隔和/或最小节距。

[0066]

基板602包括第一基板部分640(例如,芯基板部分)和第二基板部分242(例如,无芯基板部分)。第一基板部分640可以是芯基板,而第二基板部分可以是嵌入式迹线基板

(ets)。第二基板部分242可以是无芯基板。第一基板部分640通过电介质层205耦合到第二基板部分242。如以上描述的,电介质层205包括两个图案化金属层,即来自第一基板部分240的图案化金属层和来自第二基板部分242的图案化金属层。第一基板部分640的图案化金属层限定第一基板部分640的多个互连,并且第二基板部分242的图案化金属层限定第二基板部分242的多个互连。

[0067]

第一基板部分640类似于图2的第一基板部分240。然而,第一基板部分640可包括具有与图2中描述的多个通孔230不同的形状和/或成分的多个通孔630和多个通孔650。

[0068]

图6解说了穿过芯层203的芯通孔630。芯通孔630包括插栓(plug)材料632和金属层634。插栓材料可以是非导电插栓材料。插栓材料可以是复合材料。插栓材料的示例包括thp-100dx。插栓材料632被金属层634、焊盘612和焊盘252围绕。例如,插栓材料632被金属层634横向围绕。因此,在一些实现中,插栓材料632不与电介质材料(例如,芯层203、电介质层201、电介质层205)直接接触。如下面将在图7中进一步描述的,焊盘612可以由两个或更多个金属层形成。与焊盘612相同的金属层上的其他互连也可以由两个或更多个金属层形成。通孔与芯通孔630的中心大致上垂直地对准。芯通孔630可具有大致上垂直的至少一个壁。

[0069]

图6解说了穿过芯层203的芯通孔650。芯通孔650包括插栓材料652和金属层654。金属层654横向围绕插栓材料652,而焊盘252覆盖插栓材料652的第一表面(例如,顶表面)。插栓材料652的第二表面(例如,底表面)被焊盘622覆盖。焊盘622可以与芯通孔650的中心偏移。焊盘622可包括两个或更多个金属层。在一些实现中,芯通孔630和芯通孔650可被称为加盖通孔(例如,加盖芯通孔)。

[0070]

在一些实现中,插栓材料可以不被金属层完全封装。以下在图8中解说并描述了此类示例。不同的实现可以使用芯通孔630和芯通孔650的不同布置。在一些实现中,(i)芯层203中的所有通孔可以类似于芯通孔630,(ii)芯层203中的所有通孔可以类似于芯通孔650,或者(iii)芯层203中的通孔可具有芯通孔630和芯通孔650的组合。

[0071]

在一些实现中,当芯层203具有大于250微米(μm)的厚度时,可以使用芯通孔630和/或芯通孔650。在芯层203的这种厚度下,用插栓材料来填充芯通孔的空腔比用更多金属来填充空腔更高效和/或更成本有效,而不会牺牲基板的性能(例如,通孔的导电性)。在一些实现中,基板602的总厚度可以在400-1200微米(μm)的范围中。

[0072]

如以上所提及的,电介质层205(例如,第二电介质层)耦合在并且位于第一基板部分640(例如,芯基板)与第二基板部分242(例如,无芯基板、嵌入式迹线基板(ets))之间。电介质层205是单个电介质层。电介质层205被耦合到第一基板部分640的芯层203、以及第二基板部分242的电介质层207。

[0073]

电介质层205被形成在第一基板部分640与第二基板部分242之间以使得来自多个芯基板互连210中的一些芯基板互连(例如,焊盘252)和来自多个基板互连280中的一些基板互连(例如,焊盘254)位于电介质层205中。因此,如图6中所示,电介质层205包括两个图案化金属层,即来自第一基板部分640的一个图案化金属层和来自第二基板部分242的一个图案化金属层。

[0074]

电介质层205还包括多个通孔250,其被耦合到多个芯基板互连210和多个基板互连280。

[0075]

第一基板部分640、电介质层205和第二基板部分242可被层压在一起以形成基板602。该工艺允许第一多个凸块互连具有在0.35-0.4毫米(mm)的范围中的节距,以及第二多个凸块互连具有在0.7-0.8毫米(mm)的范围中的节距。

[0076]

已经描述了一种基板,该基板包括针对该基板的不同部分的不同的最小宽度、间隔和节距的互连设计,现在将在下面描述用于制造所公开的基板的方法。

[0077]

用于制造具有芯层的嵌入式迹线基板(ets)的示例性序列

[0078]

在一些实现中,制造基板包括若干过程。图7(其包括图7a-7f)解说了用于提供或制造基板的示例性序列。在一些实现中,图7a-7f的序列可被用来提供或制造图6的基板602、其他基板、和/或本公开中所描述的其他器件。图7a-7f的序列类似于图5a-5d的序列。在一些实现中,图7a-7f的序列可以在芯层为400微米(μm)或更大时使用。

[0079]

应当注意,图7a-7f的序列可以组合一个或多个阶段以便简化和/或阐明用于提供或制造基板的序列。在一些实现中,各过程的次序可被改变或修改。在一些实现中,可以在不脱离本公开的精神的情况下替代或置换一个或多个过程。

[0080]

如图7a中所示,阶段1解说了第二基板部分242被耦合到第一基板部分640以使得电介质层205在第一基板部分640与第二基板部分242之间。层压工艺可被用于耦合第一基板部分640、电介质层205、以及第二基板部分242。在一些实现中,第一基板部分640包括芯层203和穿过芯层203的多个空腔702。多个空腔702具有大致上垂直的侧壁。第一基板部分640包括在第一基板部分640的表面上的至少一个图案化金属层500。如图6中所所描述的,至少一个图案化金属层500可限定第一基板部分640的互连(例如,芯基板互连、芯通孔)。例如,至少一个图案化金属层500可以限定焊盘252、通孔230、焊盘612和焊盘622。至少一个图案化金属层500可以包括晶种层。芯层203可以包括不同的电介质材料,诸如硅、玻璃、石英、环氧树脂或其组合。第一基板部分640的芯层203可具有在400-1200微米(μm)的范围中的厚度。电介质层205可以包括干膜,诸如增层绝缘膜(abf)和/或预浸料。电介质层207和/或电介质层209可以包括聚酰亚胺。

[0081]

如图7b中所示,阶段2解说了在第二基板部分242已经通过电介质层205耦合到第一基板部分640之后的状态。电介质层205封装来自第一基板部分640的互连(例如,焊盘252)和来自第二基板部分242的互连(例如,焊盘254)。

[0082]

阶段3解说了在电介质层205中形成空腔550之后的状态。不同实现可使用不同工艺来形成空腔。在一些实现中,激光蚀刻工艺被用于形成空腔。在一些实现中,光刻工艺可被用于形成空腔。

[0083]

如图7c中所示,阶段4解说了在电介质层205中形成多个通孔250之后的状态。镀敷工艺可被用来形成金属层,该金属层限定多个通孔250。镀敷工艺还可形成焊盘252。在一些实现中,焊盘252和通孔250可以共享相同的金属(例如,相同的金属层)。

[0084]

阶段5解说了用插栓材料(例如,632、652)来填充空腔702之后的状态。不同的实现可以不同地用插栓材料来填充空腔702。插栓材料可以是非导电插栓材料。插栓材料可以是复合材料。

[0085]

如图7d中所示,阶段6解说了在形成金属层以覆盖一些或全部插栓材料之后的状态。例如,插栓材料632被焊盘612覆盖。更具体地,插栓材料632被焊盘612的金属层700覆盖。结果是芯通孔630具有被金属围绕的插栓材料632。如特写视图中所示,焊盘612包括两

个金属层,即金属层500和金属层700。在一些实现中,可以对所形成的(诸)金属层应用抛光工艺。

[0086]

应注意,在制造通孔230的过程中,通孔230可以与焊盘252共享金属,如在焊盘254、通孔250和焊盘252的特写视图中所解说的。在一些实现中,在通孔250与焊盘252之间可能不存在水平界面。

[0087]

如图7e中所示,阶段7解说了在芯层203上形成电介质层201并且该电介质层201的各部分已被选择性地移除之后的状态。例如,已经在电介质层201中形成空腔510。

[0088]

阶段8解说了在电介质层201中形成互连之后的状态。在一些实现中,镀敷工艺被用于形成互连(例如,通孔214、焊盘222)。

[0089]

如图7f中所示,阶段9解说了在基板602上形成第一阻焊层204和第二阻焊层206之后的状态。

[0090]

图7a-7f解说了允许制造一种基板的过程,该基板包括针对该基板的不同部分的不同的最小宽度和最小间隔。

[0091]

包括具有芯层的嵌入式迹线基板(ets)的示例性器件

[0092]

图8解说了包括基板802和管芯208的另一器件800的剖视图。器件800可以是在交通工具(例如,汽车、卡车、摩托车)中实现的集成器件。图8的器件800类似于图6的器件600。器件800可具有与器件600和/或器件200中所描述的类似尺寸、最小宽度、最小间隔和/或最小节距。如将在下面描述的,器件800与器件600之间的一个区别在于器件800在芯层中包括未加盖通孔。

[0093]

基板802包括第一基板部分840(例如,芯基板部分)和第二基板部分242(例如,无芯基板部分)。第一基板部分840可以是芯基板,而第二基板部分可以是嵌入式迹线基板(ets)。第二基板部分242可以是无芯基板。第一基板部分840通过电介质层205耦合到第二基板部分242。如以上描述的,电介质层205包括两个图案化金属层,即来自第一基板部分840的图案化金属层和来自第二基板部分242的图案化金属层。第一基板部分840的图案化金属层限定第一基板部分840的多个互连,并且第二基板部分242的图案化金属层限定第二基板部分242的多个互连。

[0094]

第一基板部分840类似于图6的第一基板部分640。第一基板部分840可包括具有与图6中描述的多个通孔630和/或650不同的形状、配置和/或成分的多个通孔830和/或830。

[0095]

图8解说了穿过芯层203的芯通孔830。芯通孔830包括插栓材料832和金属层834。插栓材料可以是非导电插栓材料。插栓材料可以是复合材料。金属层834横向围绕插栓材料832,而焊盘252覆盖插栓材料832的第一表面(例如,顶表面)。然而,插栓材料832的第二表面(例如,底表面)未被金属层覆盖。取而代之,插栓材料832的第二表面被电介质层201覆盖。在一些实现中,芯通孔830可被称为未加盖通孔(例如,未加盖芯通孔)。焊盘812以偏移方式耦合到芯通孔830,并且通孔214耦合到焊盘812。芯通孔830可具有大致上垂直的至少一个壁。图8还解说了芯通孔850,其可以类似于芯通孔830。

[0096]

不同的实现可以使用芯通孔830、芯通孔630、芯通孔650和/或芯通孔850的不同布置。在一些实现中,(i)芯层203中的所有通孔可以类似于芯通孔830,(ii)芯层203中的所有通孔可以类似于芯通孔630和/或芯通孔650,或者(iii)芯层203中的通孔可具有芯通孔830、芯通孔630和/或芯通孔650的组合。

[0097]

在一些实现中,当芯层203具有大于250微米(μm)的厚度时,可以使用芯通孔830。在芯层203的这种厚度下,用插栓材料来填充芯通孔的空腔比用更多金属来填充该空腔更高效和/或更成本有效,而不会牺牲基板性能(例如,通孔的导电性)。在一些实现中,基板802的总厚度可以在400-1200微米(μm)的范围中。

[0098]

第一基板部分840、电介质层205和第二基板部分242可被层压在一起以形成基板802。该工艺允许第一多个凸块互连具有在0.35-0.4毫米(mm)的范围中的节距,以及第二多个凸块互连具有在0.7-0.8毫米(mm)的范围中的节距。

[0099]

已经描述了一种基板,该基板包括针对该基板的不同部分的不同的最小宽度、间隔和节距的互连设计,现在将在下面描述用于制造所公开的基板的方法。

[0100]

用于制造具有芯层的嵌入式迹线基板(ets)的示例性序列

[0101]

图9(其包括图9a-9e)解说了用于提供或制造基板的示例性序列。在一些实现中,图9a-9e的序列可被用来提供或制造图8的基板802、其他基板、和/或本公开中所描述的其他器件。图9a-9e的序列类似于图7a-7f的序列。在一些实现中,图9a-9e的序列可以在芯层为400微米(μm)或更大时使用。

[0102]

应当注意,图9a-9e的序列可以组合一个或多个阶段以便简化和/或阐明用于提供或制造基板的序列。在一些实现中,各过程的次序可被改变或修改。在一些实现中,可以在不脱离本公开的精神的情况下替代或置换一个或多个过程。应注意,图9a-9d的阶段1-5可类似于图7a-7c的阶段1-5。

[0103]

如图9a中所示,阶段1解说了第二基板部分242被耦合到第一基板部分840以使得电介质层205在第一基板部分240与第二基板部分242之间。第一基板部分840、电介质层205和第二基板部分242可被层压在一起以形成基板802。在一些实现中,第一基板部分840包括芯层203和穿过芯层203的多个空腔702。多个空腔702具有大致上垂直的侧壁。第一基板部分840包括在第一基板部分840的表面上的至少一个图案化金属层500。如图8中所示,至少一个图案化金属层500可限定第一基板部分840的互连(例如,芯基板互连)。例如,至少一个图案化金属层500可以限定焊盘252、通孔230和焊盘812。至少一个图案化金属层500可以包括晶种层。芯层203可以包括不同的电介质材料,诸如硅、玻璃、石英、环氧树脂或其组合。第一基板部分840的芯层203可具有在400-1200微米(μm)的范围中的厚度。电介质层205可以包括干膜,诸如增层绝缘膜(abf)和/或预浸料。电介质层207和/或电介质层209可以包括聚酰亚胺。

[0104]

如图9b中所示,阶段2解说了在第二基板部分242已经通过电介质层205耦合到第一基板部分840之后的状态。电介质层205封装来自第一基板部分840的互连(例如,焊盘252)和来自第二基板部分242的互连(例如,焊盘254)。

[0105]

阶段3解说了在电介质层205中形成空腔550之后的状态。不同实现可使用不同工艺来形成空腔。在一些实现中,激光蚀刻工艺被用于形成空腔。在一些实现中,光刻工艺可被用于形成空腔。

[0106]

如图9c中所示,阶段4解说了在电介质层205中形成多个通孔250之后的状态。镀敷工艺可被用来形成金属层,该金属层限定多个通孔250。应注意,在制造通孔250的过程中,通孔250可以与焊盘252共享金属,如在焊盘254、通孔250和焊盘252的特写视图中所解说的。在一些实现中,在通孔250与焊盘252之间可能不存在水平界面。

[0107]

如图9d中所示,阶段5解说了用插栓材料(例如,832、852)来填充空腔702之后的状态。不同的实现可以不同地用插栓材料来填充空腔702。插栓材料可以是非导电插栓材料。插栓材料可以是复合材料。

[0108]

阶段6解说了在芯层203上形成电介质层201并且该电介质层201的各部分已被选择性地移除之后的状态。例如,已经在电介质层201中形成空腔510。

[0109]

如图9e中所示,阶段7解说了在电介质层201中形成互连之后的状态。在一些实现中,镀敷工艺被用于形成互连(例如,通孔214、焊盘222)。

[0110]

阶段8解说了在基板202上形成第一阻焊层204和第二阻焊层206之后的状态。

[0111]

图9a-9e解说了允许制造一种基板的过程,该基板包括针对该基板的不同部分的不同的最小宽度和最小间隔。

[0112]

用于制造具有芯层的嵌入式迹线基板(ets)的方法的示例性流程图

[0113]

在一些实现中,制造基板包括若干过程。图10解说了用于提供或制造基板的方法1000的示例性流程图。在一些实现中,图10的方法1000可被用来提供或制造本公开中所描述的图2、图6、和/或图8的基板。例如,图10的方法可被用来制造基板202、602和/或802。

[0114]

应当注意,图10的序列可以组合一个或多个过程以简化和/或阐明用于提供或制造基板的方法。在一些实现中,各过程的次序可被改变或修改。

[0115]

方法1000提供(在1005)芯基板,该芯基板包括具有第一多个最小宽度、最小间隔和最小节距的互连。在一些实现中,芯基板可以是第一基板部分(例如,240、640、840),如图2、6和8中所描述的。在图11a-11b和12中描述了制造和/或提供芯基板的示例。在一些实现中,芯基板包括芯层203和穿过芯层203的多个空腔(例如,502、702)。芯基板部分包括在该芯基板的表面上的至少一个图案化金属层500。

[0116]

方法1000在芯基板上提供(在1010)干膜电介质层。干膜电介质层可以包括干膜,诸如增层绝缘膜(abf)和/或预浸料。在一些实现中,干膜电介质层可以是电介质层205。

[0117]

方法1000提供(在1015)嵌入式迹线基板(ets),该嵌入式迹线基板包括具有第二多个最小宽度、最小间隔和最小节距的互连。在一些实现中,该ets是无芯基板。在一些实现中,该ets是第二基板部分242,如图2、6和8中所描述的。在图14a-14b中描述了制造和/或提供ets的示例。ets可以包括一个或多个若干电介质层(例如,207、209)。电介质层可包括聚酰亚胺。

[0118]

方法1000将ets耦合(在1020)到干膜电介质层和芯基板。在一些实现中,层压工艺被用于将ets耦合到干膜电介质层和芯基板。在图5a-5b、7a-7b和9a-9b中描述和解说了将ets耦合到干膜电介质层和芯基板的示例。

[0119]

方法1000在干膜电介质层中提供(在1025)金属以形成互连(例如,通孔),这些互连将来自ets的互连与来自芯基板的互连进行耦合。在一些实现中,可以在干膜电介质层中形成空腔(例如,光刻、激光工艺)以使得可以在该干膜电介质层的空腔中形成金属。该金属可以使用镀敷工艺来形成。金属的形成可以形成共享相同金属的通孔和焊盘。在图7b-7c的阶段3和4中解说并描述了形成空腔并在该空腔中提供镀敷的示例。

[0120]

方法1000在芯基板的空腔(例如,芯层203的空腔)中提供(在1030)金属和/或插栓材料(例如,632)。在一些实现中,在芯层的空腔中提供金属还是塞材料可取决于芯层203的厚度。插栓材料可以是非导电插栓材料。插栓材料可以是复合材料。镀敷工艺可被用来在芯

层203的空腔中提供金属。在图5c-5d的阶段4-6和图7c-7f的阶段5-8中描述了提供金属和/或插栓材料的示例。该方法可以在芯层上提供附加的金属层和/或电介质层。

[0121]

该方法可以在芯层上提供(在1035)互连(例如,金属层、焊盘、通孔)和/或(诸)电介质层。镀敷工艺可被用来形成互连。

[0122]

方法1000在芯层和ets上提供(在1040)(诸)阻焊层(例如,204、206)。

[0123]

用于制造芯基板的示例性序列

[0124]

在一些实现中,制造芯基板包括若干过程。图11(其包括图11a-11b)解说了用于提供或制造芯基板的示例性序列。在一些实现中,图11a-11b的序列可被用于提供或制造图2的基板(例如,240)。在一些实现中,当芯基板具有在150-250微米(μm)的范围中的芯层时,可以使用图11a-11b的序列。

[0125]

应当注意,图11a-11b的序列可以组合一个或多个阶段以便简化和/或阐明用于提供或制造基板的序列。在一些实现中,各过程的次序可被改变或修改。在一些实现中,可以在不脱离本公开的精神的情况下替代或置换一个或多个过程。

[0126]

如图11a中所示,阶段1解说了提供芯层203。芯层203可以包括不同的电介质材料,诸如硅、玻璃、石英、环氧树脂或其组合。

[0127]

阶段2解说了在形成穿过芯层203的第一表面的多个空腔1110之后的状态。在一些实现中,可使用激光工艺来形成空腔1110。

[0128]

阶段3解说了在形成穿过芯层203的第二表面(其可以与第一表面相对)的多个空腔1112之后的状态。在一些实现中,可使用激光工艺来形成空腔1110。空腔1112可被形成为使得它们与空腔1110组合以形成完全穿过芯层203的空腔。如阶段3中所示,经组合的空腔1110和1112具有相对于芯层203的第一表面和第二表面倾斜或非垂直的侧壁。

[0129]

如图11b中所示,阶段4解说了在芯层203的第一表面和第二表面、以及空腔1100和1112的表面上形成金属层500(例如,铜)之后的状态。镀敷工艺可被用来形成金属层500。该金属层500可以包括晶种层和/或金属层。因此,金属层500可以包括一层以上金属层。

[0130]

阶段5解说了已图案化金属层500以形成和/或限定用于芯基板的互连(例如,通孔、迹线、焊盘)之后的状态。在一些实现中,芯基板可以是第一基板部分240。

[0131]

用于制造芯基板的示例性序列

[0132]

图12解说了用于提供或制造芯基板的另一示例性序列。在一些实现中,图12的序列可被用于提供或制造图6和/或图8的基板(例如,640、840)。在一些实现中,当芯基板具有在400-1200微米(μm)的范围中的厚度的芯层时,可以使用图12的序列。

[0133]

应当注意,图12的序列可以组合一个或多个阶段以简化和/或阐明用于提供或制造基板的序列。在一些实现中,各过程的次序可被改变或修改。在一些实现中,可以在不脱离本公开的精神的情况下替代或置换一个或多个过程。

[0134]

阶段1解说了提供芯层203。芯层203可以包括不同的电介质材料,诸如硅、玻璃、石英、环氧树脂或其组合。

[0135]

阶段2解说了在形成穿过芯层203的多个空腔1210之后的状态。在一些实现中,可使用钻孔工艺(例如,机械钻孔)来形成空腔1210。空腔1210可被形成为使得这些空腔具有与芯层203的第一表面和/或第二表面大致上垂直的侧壁。

[0136]

阶段3解说了在芯层203的第一表面和第二表面、以及空腔1210的表面上形成金属

层500(例如,铜)之后的状态。镀敷工艺可被用来形成金属层500。该金属层500可以包括晶种层和/或金属层。因此,金属层500可以包括一层以上金属层。

[0137]

阶段4解说了已图案化金属层500以形成和/或限定用于芯基板的互连(例如,通孔、迹线、焊盘)之后的状态。在一些实现中,芯基板可以是第一基板部分640或第一基板部分840。

[0138]

用于制造芯基板的方法的示例性流程图

[0139]

在一些实现中,制造芯基板包括若干过程。图13解说了用于提供或制造芯基板的方法1300的示例性流程图。在一些实现中,图13的方法1300可被用来提供或制造本公开中所描述的图6和/或图8的芯基板。例如,图13的方法可被用来制造第一基板部分640和/或840。

[0140]

应当注意,图13的序列可以组合一个或多个过程以简化和/或阐明用于提供或制造芯基板的方法。在一些实现中,各过程的次序可被改变或修改。

[0141]

方法1300提供(在1305)芯层203。芯层203可以包括不同的电介质材料,诸如硅、玻璃、石英、环氧树脂或其组合。

[0142]

可任选地,方法1300可以移除(在1310)芯层203上的金属层。在一些实现中,芯层203可伴随有形成在芯层203的第一和/或第二表面上的一个或多个金属层。在此类实例中,金属层可被移除(例如,通过使用蚀刻工艺)。

[0143]

方法形成(在1315)穿过芯层203的多个空腔。多个空腔(例如,1110、1112、1210)可以使用激光工艺或钻孔工艺来形成,如在图11a-11b和12中所描述的。

[0144]

该方法在芯层203的第一表面和第二表面、以及空腔(例如,1110、1112、1210)的表面上形成(在1320)金属层(例如,500)。镀敷工艺可被用来形成金属层。金属层可以包括晶种层和/或金属层。

[0145]

该方法选择性地移除(在1325)金属层(例如,500)的各部分。阶段5解说了已图案化金属层(例如,500)以形成和/或限定用于芯基板的互连(例如,通孔、迹线、焊盘)之后的状态。在一些实现中,芯基板可以是第一基板部分640或第一基板部分840。

[0146]

用于制造无芯基板的示例性序列

[0147]

在一些实现中,制造无芯基板包括若干过程。图14(其包括图14a-14b)解说了用于提供或制造无芯基板的示例性序列。在一些实现中,图14a

–

14b的序列可被用于提供或制造图2、图6和/或图8的无芯基板(例如,242)。

[0148]

应当注意,图14a-14b的序列可以组合一个或多个阶段以便简化和/或阐明用于提供或制造基板的序列。在一些实现中,各过程的次序可被改变或修改。在一些实现中,可以在不脱离本公开的精神的情况下替代或置换一个或多个过程。

[0149]

如图14a中所示,阶段1解说了提供载体1400并且在该载体1400上形成金属层之后的状态。金属层可被图案化以形成互连,诸如焊盘292。镀敷工艺可被用来形成金属层和互连。

[0150]

阶段2解说了在载体1400和各互连上形成电介质层209之后的状态。电介质层209可包括聚酰亚胺。

[0151]

阶段3解说了在电介质层209中形成多个空腔1490之后的状态。可以使用蚀刻工艺或激光工艺来形成多个空腔1490。

[0152]

阶段4解说了在电介质层209中和电介质层209上形成互连之后的状态。例如,通孔290和焊盘272被形成。镀敷工艺可被用来形成互连。

[0153]

阶段5解说了在电介质层209上形成另一电介质层207之后的状态。

[0154]

如图14b中所示,阶段6解说了在电介质层207中形成多个空腔1470之后的状态。蚀刻工艺或激光工艺可被用来形成空腔1470。

[0155]

阶段7解说了在电介质层207中和电介质层209上形成互连之后的状态。例如,通孔270和焊盘254被形成。镀敷工艺可被用来形成互连。

[0156]

阶段8解说了将载体1400与电介质层209解耦(例如,移除、研磨)之后,留下无芯基板。在一些实现中,无芯基板是嵌入式迹线基板(ets)。在一些实现中,无芯基板是第二基板部分242。

[0157]

用于制造芯基板的方法的示例性流程图

[0158]

在一些实现中,制造无芯基板包括若干过程。图15解说了用于提供或制造无芯基板的方法1500的示例性流程图。在一些实现中,图15的方法1500可被用来提供或制造本公开中所描述的图2、图6、和/或图8的无芯基板。例如,图15的方法可被用来制造第二基板部分242。

[0159]

应当注意,图15的序列可以组合一个或多个过程以简化和/或阐明用于提供或制造无芯基板的方法。在一些实现中,各过程的次序可被改变或修改。

[0160]

该方法提供(在1505)载体1400。该方法在载体1400上形成(在1510)金属层。金属层可被图案化以形成互连,诸如焊盘292。镀敷工艺可被用来形成金属层和互连。

[0161]

该方法在载体1400和互连上形成(在1515)电介质层209。电介质层209可包括聚酰亚胺。形成电介质层还可包括在电介质层209中形成多个空腔(例如,1490)。可以使用蚀刻工艺或激光工艺来形成多个空腔。

[0162]

该方法在电介质层中和电介质层上形成(在1520)互连。例如,通孔290和焊盘272可被形成。镀敷工艺可被用来形成互连。形成互连可包括在电介质层上和/或中提供图案化金属层。

[0163]

该方法在电介质层209和互连上形成(在1525)电介质层207。电介质层207可包括聚酰亚胺。形成电介质层还可包括在电介质层207中形成多个空腔(例如,1470)。可以使用蚀刻工艺或激光工艺来形成多个空腔。

[0164]

该方法在电介质层中和/或上形成(在1530)互连。例如,通孔270和焊盘254可被形成。镀敷工艺可被用来形成互连。形成互连可包括在电介质层上和中提供图案化金属层。

[0165]

该方法还可将载体(例如,1400)与电介质层209解耦(例如,移除、研磨),留下无芯基板。在一些实现中,无芯基板是嵌入式迹线基板(ets)。在一些实现中,无芯基板是第二基板部分242。

[0166]

示例性电子设备

[0167]

图16解说了可集成有前述器件、集成器件、集成电路(ic)封装、集成电路(ic)器件、半导体器件、集成电路、管芯、中介体、封装或层叠封装(pop)中的任一者的各种电子设备。例如,移动电话设备1602、膝上型计算机设备1604、固定位置终端设备1606、可穿戴设备1608、或机动交通工具1610可包括如本文中所描述的器件1600。器件1600可以是例如本文中所描述的器件和/或集成电路(ic)封装中的任一者。图16中所解说的设备1602、1604、

1606和1608、以及交通工具1610仅仅是示例性的。其他电子设备也能以器件1600为其特征,此类电子设备包括但不限于包括以下设备的设备(例如,电子设备)组:移动设备、手持式个人通信系统(pcs)单元、便携式数据单元(诸如个人数字助理)、启用全球定位系统(gps)的设备、导航设备、机顶盒、音乐播放器、视频播放器、娱乐单元、固定位置数据单元(诸如仪表读取装备)、通信设备、智能电话、平板计算机、计算机、可穿戴设备(例如,手表、眼镜)、物联网(iot)设备、服务器、路由器、机动交通工具(例如,自动驾驶交通工具)中所实现的电子设备、或者存储或检索数据或计算机指令的任何其他设备,或者其任何组合。

[0168]

图2-4、5a

–

5d、6、7a

–

7f、10、11a

–

11b、12、13、14a

–

14b、和/或15-16中解说的组件、过程、特征和/或功能中的一者或多者可被重新安排和/或组合成单个组件、过程、特征或功能,或可在若干组件、过程、或功能中实施。也可添加附加元件、组件、过程、和/或功能而不会脱离本公开。还应当注意,本公开中的图2-4、5a

–

5d、6、7a

–

7f、10、11a

–

11b、12、13、14a

–

14b、和/或15-16及其对应描述并不限于管芯和/或ic。在一些实现中,图2-4、5a

–

5d、6、7a

–

7f、10、11a

–

11b、12、13、14a

–

14b和/或15-16及其对应描述可被用来制造、创建、提供、和/或生产器件和/或集成器件。在一些实现中,器件可包括管芯、晶片、集成器件、集成无源器件(ipd)、管芯封装、集成电路(ic)器件、器件封装、集成电路(ic)封装、半导体器件、层叠封装(pop)器件、和/或中介体。

[0169]

措辞“示例性”在本文中用于表示“用作示例、实例、或解说”。本文中描述为“示例性”的任何实现或方面不必被解释为优于或胜过本公开的其他方面。同样,术语“方面”不要求本公开的所有方面都包括所讨论的特征、优点或操作模式。术语“耦合”在本文中用于指两个对象之间的直接或间接耦合。例如,如果对象a物理地接触对象b,且对象b接触对象c,则对象a和c仍可被认为是彼此耦合的——即便它们并非彼此直接物理接触。进一步注意到,如在本申请中在一个组件位于另一组件之上的上下文中所使用的术语搮之上厰可被用于表示组件在另一组件上和/或在另一组件中(例如,在组件的表面上或被嵌入在组件中)。由此,例如,第一组件在第二组件之上可表示:(1)第一组件在第二组件上方,但是不直接接触第二组件;(2)第一组件在第二组件上(例如,在第二组件的表面上);和/或(3)第一组件在第二组件中(例如,被嵌入在第二组件中)。如本公开中所使用的术语“大约

‘

值x

’”

或“大致上”应当意味着在“值x”的百分之十以内。例如,大约1的值或大致上1的值将意味着在0.9-1.1范围中的值。

[0170]

在一些实现中,器件和/或封装的高度可以沿该封装的z方向来定义,该z方向在本公开的附图中示出。在一些实现中,器件和/或封装的z方向可以沿该器件和/或封装的顶部部分与底部部分之间的轴线来定义。术语“顶部”和“底部”可被任意地指派,然而,作为一示例,器件和/或封装的顶部部分可以是包括包封层的部分,而封装的底部部分则可以是包括重分布部分或多个焊球的部分。在一些实现中,封装的顶部部分可以是封装的背侧,而封装的底部部分则可以是封装的前侧。封装的前侧可以是封装的有效侧。顶部部分可以是相对于较低部分的较高部分。底部部分可以是相对于较高部分的较低部分。

[0171]

器件和/或封装的x-y方向或x-y平面可以指该器件和/或封装的横向方向和/或占用面积。x-y方向的示例在本公开的附图中示出。物体的宽度、长度和/或直径可以指沿x-y维度和/或x-y平面的(诸)尺寸。在本公开的许多附图中,跨x-z截面或x-z平面示出器件和/或封装及其相应组件。然而,在一些实现中,可跨y-z截面或y-z平面表示封装及其代表性组

件。

[0172]

还注意到,本文中所包含的各种公开可以作为被描绘为流程图、流图、结构图或框图的过程来描述。尽管流程图可以将操作描述为按次序的过程,但很多操作可以并行地或同时地进行。另外,可以重新排列操作的顺序。过程在其操作完成时终止。

[0173]

本文中所描述的本公开的各种特征可实现于不同系统中而不会脱离本公开。应当注意,本公开的以上各方面仅是示例,且不应被解释成限定本公开。对本公开的各方面的描述旨在是解说性的,而非限定所附权利要求的范围。由此,本发明的教导可以现成地应用于其他类型的装置,并且许多替换、修改和变形对于本领域技术人员将是显而易见的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1