形成硅化镍材料的方法与流程

[0001]

本揭示案的实施方式大体涉及沉积硅化镍(nisi)材料的方法,所述硅化镍材料具有提高的电导率或低电阻率及/或小于10纳米(nm)的电子平均自由程(electron mean free path;emfp)。

背景技术:

[0002]

在诸如集成电路的半导体器件中,互连用于连接及整合器件的各种部件。通常,器件由多层导电部件组成,由绝缘材料隔开,以协助使信号路径减至最小且缩小器件尺寸。为了在层间建立连续性,导电互连(触点或通孔)在绝缘层之间延伸并连接导电层。因此,互连是用导电材料填充的垂直开口,用于将器件各层上的部件彼此连接并连接到半导体基板。

[0003]

随着半导体器件集成度的提高,互连的尺寸已减小,且其深宽比(亦即,互连的高度与宽度的比率)已增大。因而,过去足以填充互连的方法已被证实不足以用于较小的互连。通常,使用诸如铜的金属材料填充互连孔,所述材料通过化学气相沉积(chemical vapor deposition;cvd)、物理气相沉积(physical vapor deposition;pvd)、电镀或其组合沉积在孔内。

[0004]

集成电路(integrated circuit;ic)中的互连分配时钟及其他信号,并为电路内的各个部分提供电源/接地。随着集成电路特征尺寸的不断缩小,互连正成为决定系统性能的主要因素,系统性能例如信号传播延迟及功率消耗,此与互连线电阻有关。在过去的20年中,由于铜(cu)的低电阻率,铜始终是互连的首选材料。然而,发明人已观察到,随着互连线宽度收缩至低于材料的电子平均自由程(emfp),由于线表面及晶粒边界处的侧壁电子散射,材料的有效电阻率增大。因此,发明人已观察到,对于宽度为20纳米或更小的铜互连,有效电阻率的增大会招致问题,因为铜具有39纳米的emfp。此外,发明人亦观察到铜在低温下会与硅发生有问题的相互作用,或者扩散到周围的电介质中。通常需要阻挡层来防止扩散,这会不利地增大铜的总电阻率。发明人已观察到对寻找集成电路互连中铜的替代材料的需求。

[0005]

因此,发明人提供了在基板上形成硅化镍材料的改良方法,及降低硅化镍材料的电阻率的方法。

技术实现要素:

[0006]

本文提供了在基板上形成硅化镍材料及降低硅化镍材料的电阻率的实施方式。在一些实施方式中,一种用于在基板上形成硅化镍材料的方法包括:在约15℃至约27℃的温度下,在基板顶部沉积第一硅化镍种晶层;在诸如超过350℃、或在400℃或更低的温度下使第一硅化镍种晶层退火;及在约15℃至约27℃的温度下,在第一硅化镍种晶层上沉积第二硅化镍层,以形成硅化镍材料。在实施方式中,硅化镍材料具有小于20微欧姆

×

厘米的电阻,比如1-20微欧姆

×

厘米(μω

.

cm)。

[0007]

在一些实施方式中,一种降低硅化镍材料的电阻率的方法包括:a)在约15℃至约

27℃的温度下,在基板顶部沉积硅化镍层;b)在高于350℃的温度下使第一硅化镍种晶层退火;及c)重复a)、或a)和b),直到硅化镍材料具有预定厚度。在一些实施方式中,第一硅化镍种晶层在氩气中在400℃或更低的温度下退火长达2分钟。在一些实施方式中,当达到硅化镍材料的期望厚度之后,硅化镍材料在约350℃的温度及20巴的压力(氩气环境)下退火长达10分钟。

[0008]

在一些实施方式中,一种在基板上形成互连的方法包括:在约15℃至约27℃的温度下,在基板上物理气相沉积第一硅化镍种晶层;在高于350℃的温度下使第一硅化镍种晶层退火;及在约15℃至约27℃的温度下,在第一硅化镍种晶层上物理气相沉积第二硅化镍层,以形成硅化镍材料。

[0009]

在一些实施方式中,本揭示案涉及一种基板处理系统,所述系统包括:物理气相沉积腔室,被配置为用于在约15℃至约27℃的温度下在基板上物理气相沉积第一硅化镍种晶层,及在约15℃至约27℃的温度下在第一硅化镍种晶层顶部物理气相沉积第二硅化镍层,以形成硅化镍材料;及热处理腔室,所述腔室被配置为用于在超过350℃的温度下使第一硅化镍种晶层退火。

[0010]

在一些实施方式中,本揭示案涉及其上储存有指令的计算机可读介质,当执行所述指令时,使得整合系统执行在基板上形成硅化镍材料的方法,所述方法包括:在约15℃至约27℃的温度下在基板顶部沉积第一硅化镍种晶层;在高于350℃的温度下使第一硅化镍种晶层退火;及在约15℃至约27℃的温度下,在第一硅化镍种晶层上沉积第二硅化镍层,以形成硅化镍材料。

[0011]

下文描述本揭示案的其他及更多实施方式。

附图说明

[0012]

通过参考附图中描述的本揭示案的说明性实施方式,可理解上文简要概述且下文更详细论述的本揭示案的实施方式。然而,附图仅示出了本揭示案的典型实施方式,因此不应被视为对范围的限制,因为本揭示案可允许其他同等有效的实施方式。

[0013]

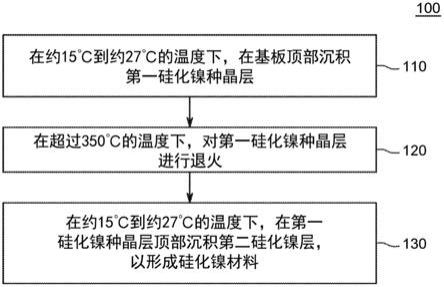

图1绘示了根据本揭示案的一些实施方式的用于处理基板的方法的流程图。

[0014]

图2a至2d绘示了根据本揭示案的一些实施方式的填充高深宽比开口的各个阶段。

[0015]

图3绘示了根据本揭示案的一些实施方式的物理气相沉积(pvd)腔室的截面示意图。

[0016]

图4绘示了根据本揭示案的一些实施方式的用于处理基板的方法的流程图。

[0017]

图5绘示了根据本揭示案的一些实施方式的在基板上形成互连的方法的流程图。

[0018]

图6绘示了根据本揭示案的一些实施方式的包括图3的设备的处理工具的俯视平面图。

[0019]

为了便于理解,已尽可能使用相同的元件符号来表示各图中共用的相同元件。附图并非按比例绘制,且为清楚起见可被简化。一个实施方式的元件及特征可有利地并入其他实施方式中,而无需进一步叙述。

具体实施方式

[0020]

本文提供了在基板上形成硅化镍材料的实施方式。发明人已观察到,对于宽度为

20纳米或更小的铜(cu)互连,有效电阻率的增大会招致问题,因为铜具有39纳米的emfp。此外,发明人观察到铜的问题在于铜在低温下与硅相互作用,或铜扩散到周围的电介质中。通常需要阻挡层来防止铜扩散,此将不利地影响铜的整体电阻率。发明人已观察到需要找到集成电路互连中铜的替代材料。本发明方法的实施方式可有利地利用硅化镍(nisi)材料对包括毯覆基板表面或例如高深宽比特征的基板表面提供连续覆盖,所述硅化镍(nisi)材料具有提高的电导率或低电阻率,及/或小于10纳米(nm)的emfp。

[0021]

图1绘示了根据本揭示案的一些实施方式的用于在基板200上形成硅化镍材料的方法100的流程图。在下文中关于图2a、图2b及图2c所示的填充高深宽比特征的各个阶段对方法100进行说明性的描述。然而,硅化镍材料可形成为基板上方或顶部的片材或毯覆层,例如,不具有诸如高深宽比特征的特征。在一些实施方式中,硅化镍材料可形成为基板上的片材或毯覆层,且经受额外工艺流程,如蚀刻、填充及/或覆盖。方法100可在具有脉冲dc及射频(radio frequency;rf)电源的任何合适的pvd处理腔室中执行,如下文描述及图3中绘示的处理腔室300。

[0022]

方法100从110开始,在诸如室温或约15℃至约27℃或约20℃至25℃的温度下,在基板200顶部沉积第一硅化镍种晶层220。例如,可将基板200(图2a所示)提供至pvd腔室,如处理腔室300(图3)。在实施方式中,基板200包括高深宽比开口,诸如形成在基板200的第一表面204中且朝向基板200的相对第二表面206延伸到基板200中的开口202。基板200可为任何合适的基板,包括但不限于其上形成有高深宽比开口的基板。例如,基板200可包括硅(si)、氧化硅(sio2)、氮化硅(sin)或其他介电材料中的一或更多者。在实施方式中,基板可包括薄金属层,如氮化钛(tin)、氮化钽(tan)或其他薄金属层。此外,基板200可包括额外材料层,或者可在其中或其上形成有一或更多个完成的或部分完成的结构。

[0023]

开口202可为具有高深宽比的任何开口,比如用于形成通孔、沟槽、双镶嵌结构等。在一些实施方式中,开口202可具有至少约5:1的高宽比(例如,高深宽比)。例如,在一些实施方式中,深宽比可为约10:1或更大,比如约15:1或更大。开口202可通过使用任何合适的蚀刻工艺蚀刻基板来形成。如图所示,开口202包括底表面208及侧壁210。

[0024]

在一些实施方式中,如下所述,在沉积硅化镍原子之前,可利用一或更多层覆盖底表面208及侧壁210。例如,如图2a中虚线所示,开口202的底表面和侧壁及基板200的第一表面可被介电层或氧化物层212覆盖,诸如氧化硅(sio2)、(si)、(sin)或其他介电材料。在将基板200提供至pvd腔室之前,可例如在化学气相沉积(chemical vapor deposition;cvd)腔室或氧化腔室中沉积或生长氧化物层。介电层或氧化物层212可充当基板与随后将沉积在开口中的含硅化镍层之间的电及/或物理阻挡物,且/或可在下文论述的沉积工艺期间充当比基板的原生表面更佳的附着表面。在实施方式中,氧化物以外的材料可替代氧化物层212。

[0025]

在一些实施方式中,若不存在氧化物层,则可将阻挡层214沉积在氧化物层212的顶部(如图所示),或者介电层的顶部,或者开口的底表面及侧壁及基板的第一表面的顶部。阻挡层214可起到与上述介电层或氧化物层212类似的作用。在一些实施方式中,阻挡层214可包括钛(ti)、氮化钛(tin)、钽(ta)、氮化钽(tan)或其他材料中的至少一者。阻挡层214可通过任何合适的方法沉积,比如通过cvd或pvd,包括通过使用下文描述的方法100在开口202中形成连续阻挡层。

[0026]

在一些实施方式中,如图2a中的虚线所示,开口202可完全延伸穿过基板200,并且第二基板218的表面216可形成开口202的底表面208。第二基板218可设置邻近于基板200的第二表面206。此外(如图2d所示及下文论述的),诸如逻辑器件或类似物的器件,或者需要电连接的器件的一部分,诸如栅极、接触垫、导电通孔或类似物可设置在第二基板218的表面216中且与开口202对准。

[0027]

在110处,第一硅化镍种晶层在基板200上的沉积可发生在pvd腔室中,在该pvd腔室中,将射频功率(诸如来自射频电源318,如下所述)以vhf频率施加到设置在基板200上方的包括硅化镍的靶材,以由等离子体成形气体形成等离子体。例如,靶材可为下文论述的靶材306。此外,靶材可包括适于在开口202的表面及基板200的第一表面204上形成第一硅化镍种晶层220的硅化镍合金或类似物中之一或更多者。例如,靶材可包括比率为1

±

x:1(x=0.01至0.1)的镍、硅或硅化镍中的一或更多者。诸如金属的其他成分可以小于总靶材重量的5%的量存在,诸如钛(ti)、钽(ta)、铜(cu)、铝(al)或类似物。等离子体成形气体可包括惰性气体,诸如稀有气体或其他惰性气体。例如,合适的等离子体成形气体的非限制性实例可包括氩(ar)、氦(he)、氙(xe)、氖(ne)、氢(h2)或类似物。在实施方式中,等离子体成形气体是氩,其具有约5-15sccm的流率,比如10sccm、11sccm或12sccm。

[0028]

在110处,第一硅化镍种晶层220在基板200上的沉积可发生在pvd腔室中,在该pvd腔室中可以vhf频率施加射频功率,以用于以下的一或更多者:由等离子体成形气体形成等离子体及由等离子体离子化从靶材溅射的金属原子。如本文所使用的,vhf频率是在从约27mhz到约100mhz范围内的频率。在一些实施方式中,所施加的vhf频率为约60mhz。例如,增大vhf频率可增大等离子体密度及/或从靶材溅射的硅化镍原子中的离子化量。在一些实施方式中,射频功率可以0.5至3kw的功率施加,例如1kw、2kw或3kw。

[0029]

在110处,基板200顶部的第一硅化镍种晶层的沉积可发生在pvd腔室中,在该pvd腔室中,可例如从耦接到靶材306的脉冲dc电源320将脉冲dc功率施加到靶材306,以将等离子体引向靶材306,如下所述。dc功率的范围可从约1千瓦(kw)到约4kw。在一些实施方式中,脉冲dc功率可为约1-4kw,或者约2kw、3kw或4kw。在实施方式中,施加脉冲dc功率以降低第一硅化镍种晶层220的电阻率。可调节脉冲dc功率来控制溅射的硅化镍原子在基板200上的沉积速率。例如,增大脉冲dc功率可导致等离子体与靶材的相互作用增大及硅化镍原子从靶材306的溅射增大,或者硅化镍晶粒尺寸增大。

[0030]

在110处,第一硅化镍种晶层在基板200上的沉积可发生在pvd腔室中,在该pvd腔室中,使用等离子体从靶材306溅射硅化镍原子,同时在pvd腔室中保持足以使从靶材溅射的硅化镍原子的主要部分离子化的第一压力。例如,硅化镍原子的主要部分可在等离子体溅射的硅化镍原子总数的约30%至约70%的范围内。除了施加的第一射频功率及脉冲dc功率之外,第一压力可取决于处理腔室几何形状(比如基板尺寸、靶材到基板的距离等)。例如,在配置有约60至90毫米(mm)的靶材与基板间隙的腔室中,第一压力可在约0.2至约100毫托(mtorr)的范围内。在一些实施方式中,第一压力为约0.5至约5mtorr,或0.5mt。腔室中的第一压力可由等离子体成形气体的流率及/或可与等离子体成形气体共流的额外气体(比如惰性气体)的流率来维持。第一压力可在靶材与基板之间提供高密度的气体分子,溅射的硅化镍原子可与该气体分子碰撞并被离子化。压力可额外用于控制从靶材306溅射的硅化镍原子的离子化量。例如,增大靶材306到基板的间隙中的压力可增加与金属原子碰撞

的次数,从而增加离子化硅化镍原子的量。

[0031]

在110处,在一个实施方式中,第一硅化镍种晶层220在基板200顶部的沉积可在pvd腔室中在氩等离子体下以约11sccm的流量、约0.5mt的工艺压力、1-4kw脉冲dc功率或约1kw射频功率而进行。在110处,在一个实施方式中,第一硅化镍种晶层220在基板200上的沉积可在pvd腔室中在氩等离子体下以11sccm的流量、0.5mt的工艺压力、1-4kw脉冲dc功率而进行。

[0032]

在110处,第一硅化镍种晶层220在基板200顶部的沉积可发生在pvd腔室中,其中第一多个硅化镍原子221沉积在基板200的第一表面204及开口202的底表面208上,如图2b所示。第一多个硅化镍原子221可使用上述处理条件沉积,诸如第一压力、第一射频功率、脉冲dc功率及/或vhf或射频频率。如图2b所示,此种处理条件可促进第一多个硅化镍原子221的方向近似垂直于基板200。在一些实施方式中,在沉积第一多个硅化镍原子221期间,可将可选的射频功率施加到基板200(例如,施加到设置在基板200下方的电极,比如在基板支撑件内)。射频功率(亦称为射频偏压功率)可以约0.5至约13.56mhz的频率及高达50w或约5至50w的功率施加。在一些实施方式中,若另一射频功率源额外地耦接pvd腔室的基板支撑基座(或包含在其中的电极),则射频偏压功率的频率可为约2mhz及/或约13.56mhz。沉积第一多个硅化镍原子221时提供的可选射频偏压功率可较小,以使沉积硅化镍原子的能量降至最低。

[0033]

在一些实施方式中,在110处,将第一射频功率(在本文中亦称为第一射频偏压功率)施加到设置在基板200下方的电极,以将第一多个硅化镍原子中的至少一些从开口202的底表面208重新分布到开口202的侧壁210。第一射频偏压功率可以约2至约13.56mhz的频率施加。例如,在一些实施方式中,若可选的第二射频偏压功率源(图3中示出的第二射频偏压功率源363)如图3所示及下文所述额外地耦接基板支撑基座302,则第一射频偏压功率的频率可为约2mhz及/或13.56mhz。第一射频偏压功率可用于增大离子能量及/或入射到基板200上的离子的入射角。例如,入射到基板200上的离子可包括离子化的硅化镍原子、来自等离子体的离子化的元素或其组合。如图2b所示,可增大第一射频偏压功率以增大离子能量,例如以增大离子对开口202的底表面208上沉积的硅化镍原子的影响。离子对开口底表面208的增大的影响可促进金属原子的第一多个金属原子中的至少一些重新分布到侧壁210上,如图所示。第一射频偏压功率可显著大于如上所述的在沉积第一多个硅化镍原子221期间施加的可选射频偏压功率。例如,第一射频偏压功率可大于约50w,或者在约0至约200w的范围内。在一些实施方式中,第一射频偏压功率为约50w。

[0034]

在同时使用第一射频偏压功率及第二射频偏压功率的一些实施方式中,第一射频偏压功率可用于控制基板200附近的离子能量,而第二射频偏压功率可用于控制基板200附近的离子能量分布。

[0035]

在一些实施方式中,在110处,用于沉积第一硅化镍种晶层的温度是室温,或约20℃至约25℃、22℃、23℃、24℃或25℃。

[0036]

在一些实施方式中,在110处,第一硅化镍种晶层220形成为预定厚度。在实施方式中,第一硅化镍种晶层220的厚度为约10埃至100埃、20埃至60埃、30埃至50埃、35埃至45埃、约20埃、约25埃、约30埃、约35埃、约40埃、约50埃、约60埃。在实施方式中,第一硅化镍种晶层220的厚度为硅化镍总厚度的约30%至70%,例如,100埃硅化镍膜总厚度中的50埃。

[0037]

在一些实施方式中,在110处,第一硅化镍种晶层220以多晶为特征。

[0038]

返回参看图1,在120处,在实施方式中,例如在基板200顶部形成第一硅化镍种晶层220之后,在高于350℃的温度下进行第一硅化镍种晶层220的退火,比如原位退火。在实施方式中,例如在基板200顶部形成第一硅化镍种晶层220之后,在400度或低于400度的温度下进行第一硅化镍种晶层220的退火,比如原位退火。例如,可在约355℃至400℃、375℃至405℃、或约400℃的温度下对第一硅化镍种晶层220进行退火。在实施方式中,沉积后退火(诸如快速热退火(rapid thermal anneal;rta)或动态表面退火(dynamic surface anneal;dsa))使得基板200顶部的第一硅化镍种晶层220的种晶晶粒更大,且在实施方式中沿着纵向方向更长。在一些实施方式中,退火可在上述温度下进行足够长的持续时间,以增大第一硅化镍种晶层220的种晶晶粒的晶粒尺寸,比如增大至足够的尺寸,或预定的尺寸,比如200纳米、1微米或更大。在一些实施方式中,退火可在上述温度下进行足够长的持续时间,以增大第一硅化镍种晶层220的种晶晶粒的晶粒尺寸,诸如沿着水平中轴、垂直中轴及/或纵向中轴增大到足够的尺寸或预定的尺寸,比如200纳米、1微米或更大。在实施方式中,基板200可移动到适于退火的腔室中,比如在热处理腔室中,或者退火可在原位进行,比如在包括热处理腔室的整合系统中,在该系统中,腔室之间的移送在真空下进行。

[0039]

在一些实施方式中,退火之后,允许基板200冷却至较低的温度,比如室温。

[0040]

返回参看图1,在130处,在实施方式中,在约15℃至约27℃的温度下,在第一硅化镍种晶层220顶部沉积第二硅化镍层240,以形成硅化镍材料250。在实施方式中,沉积130的条件与上文关于110的条件相同。例如,在130处,第二硅化镍层在第一硅化镍种晶层220顶部的沉积可发生在pvd腔室中,在该pvd腔室中,使用等离子体从靶材306溅射硅化镍原子,同时在pvd腔室中保持足以使从靶材溅射的硅化镍原子的主要部分离子化的第一压力。在一个实施方式中,第二硅化镍层240在第一硅化镍种晶层220顶部的沉积可在pvd腔室中在氩等离子体下以约11sccm的流量、约0.5mt的工艺压力、1-4kw脉冲dc功率或约1kw射频功率而进行。在130处,在一个实施方式中,第二硅化镍层240在第一硅化镍种晶层220上的沉积可在pvd腔室中在氩等离子体下以11sccm的流量、0.5mt的工艺压力、1-4kw脉冲dc功率而进行。在实施方式中,在130处,硅化镍原子的主要部分可在等离子体溅射的硅化镍原子总数的约30%至约70%的范围内。除了施加的第一射频功率及脉冲dc功率之外,第一压力可取决于处理腔室几何形状(诸如基板尺寸、靶材到基板的距离等)。例如,在配置有约60至90毫米(mm)的靶材与基板间隙的腔室中,第一压力可在约0.5至约140毫托(mt)的范围内。在一些实施方式中,第一压力为约0.5mtorr。腔室中的第一压力可由等离子体成形气体的流率及/或可与等离子体成形气体共流的额外气体(比如惰性气体)的流率来维持。第一压力可在靶材与基板之间提供高密度的气体分子,溅射的硅化镍原子可与这些气体分子碰撞并被离子化。压力可额外用于控制从靶材306溅射的硅化镍原子的离子化量。例如,增大靶材306与基板的间隙中的压力可增加与金属原子碰撞的次数,从而增大离子化的硅化镍原子的量。

[0041]

在130处,第一硅化镍种晶层220上的第二硅化镍层240的沉积可发生在pvd腔室中,在该pvd腔室中第二多个硅化镍原子沉积在第一硅化镍种晶层220的上表面225上,如图2c所示。可使用上文论述的处理条件,比如第一压力、第一射频功率、脉冲dc功率及/或vhf频率,沉积多个硅化镍原子。在一些实施方式中,在沉积第一多个硅化镍原子221期间,可将

可选的射频功率施加到基板200(例如,施加到设置在基板200下方的电极,比如基板支撑件内)。射频功率(亦称为射频偏压功率)可以约2至约13.56mhz的频率及高达约50w的功率施加。在一些实施方式中,若另一射频功率源额外地耦接pvd腔室的基板支撑基座(或包含在其中的电极),则射频偏压功率的频率可为约2mhz及/或约13.56mhz。沉积第一多个硅化镍原子221时提供的可选射频偏压功率可较小,以将沉积硅化镍原子的能量降至最低。

[0042]

在一些实施方式中,在130处,第二射频功率(在本文中亦称为第二射频偏压功率)被施加至设置在基板200下方的电极。第二射频偏压功率可在约2至约13.56mhz的频率范围内施加。例如,在一些实施方式中,若可选的第二射频偏压功率源(图3中示出的第二射频偏压功率源363)如图3所示及下文所述额外地耦接基板支撑基座302,则第一射频偏压功率的频率可为约2mhz及/或13.56mhz。第二射频偏压功率可用于增大离子能量及/或入射到基板200上的离子的入射角。在同时使用第一射频偏压功率及第二射频偏压功率的一些实施方式中(如上所述),第一射频偏压功率可用于控制基板200附近的离子能量,且第二射频偏压功率可用于控制基板200附近的离子能量分布。

[0043]

在一些实施方式中,在130处,用于沉积第二硅化镍种晶层的温度是室温,或约20℃至约25℃、22℃、23℃、24℃或25℃。

[0044]

在一些实施方式中,在130处,第二硅化镍层240形成达预定的厚度。在实施方式中,第二硅化镍层240具有总硅化镍厚度的约30%至70%的厚度,例如,100埃硅化镍膜的总厚度中的50埃。在实施方式中,第二硅化镍层240具有约50埃至200埃、50埃至175埃、50埃至150埃、约50埃、约60埃、约70埃、约80埃、约100埃、约125埃、约150埃或约175埃的厚度。

[0045]

在130处形成第二硅化镍层240之后,方法100可结束,或者基板200可继续进行进一步处理,例如通过在第二硅化镍层240顶部沉积覆盖层260来填充开口202,如图2c所示。覆盖层260材料可由任何合适的技术沉积,诸如原位技术,以防止氧化。覆盖层260的材料可包括金属、金属合金或类似物。在一些实施方式中,所述材料包括铜(cu)或钨(w)或氮化钛(tin)中的一或更多者。在一个实施方式中,覆盖层260包括沉积在第二硅化镍层240顶部的tin。进一步处理的另一个实例可选地包括对基板200的第二次退火。在一些实施方式中,第二次退火的特征在于异位。在实施方式中,第二次退火可在约300至400℃,比如350℃的温度下,在约20巴的压力下进行约10分钟。第二次退火可在例如退火腔室中进行。在实施方式中,第二次退火在适于进行退火的热处理腔室中进行,该热处理腔室在整合系统中,该整合系统适于将基板保持在真空下。

[0046]

在实施方式中,硅化镍材料250被形成为具有预定的薄层电阻。例如,在实施方式中,在10纳米的厚度下,硅化镍材料250具有20至50欧姆/平方(ohm/square)、20至40欧姆/平方、20至30欧姆/平方、20至30欧姆/平方、20欧姆/平方、21欧姆/平方、22欧姆/平方、23欧姆/平方、24欧姆/平方、25欧姆/平方、26欧姆/平方、27欧姆/平方、28欧姆/平方、29欧姆/平方、30欧姆/平方、35欧姆/平方,或40欧姆/平方的量的薄层电阻。

[0047]

现在参考图2d,在一些实施方式中,且如以上参考图2a所论述的,在执行上述110-130之前,可能已经提供了第二基板218。因此,如图2d所示,第二基板218可设置成相邻于基板200的第二表面206,其中开口202完全延伸穿过基板200,且第二基板218的表面216形成开口202的底表面。此外,器件或导电特征234可设置在第二基板中并在表面216处暴露,其中器件或导电特征234与开口202对准。基板200的第一表面204可被进一步处理以移除沉积

的硅化镍原子。例如,如图2d所示,化学机械抛光技术、蚀刻或类似者可用于从第一表面204移除沉积的硅化镍原子。

[0048]

在一些实施方式中,在如上所述沉积材料250之后,可从基板200的第二表面206移除材料,以暴露至少一个第一层230或沉积的硅化镍材料250(第一层230在图2d中示出为暴露的)。可通过化学机械抛光或如上所述用于从基板200的第一表面204移除沉积金属的类似技术来执行从第二表面206的材料移除。

[0049]

在从第二表面206移除材料以暴露至少一个第一层230或沉积材料232之后,基板200的第二表面206可耦接到第二基板218的表面216。在一些实施方式中,在第二基板218的表面216处暴露的器件或导电特征234可与基板200中的开口202对准。

[0050]

图3绘示了根据本揭示案的一些实施方式的物理气相沉积腔室(处理腔室300)的截面示意图。合适的pvd腔室的实例包括或多阴极处理腔室、plus及sippvd处理腔室,所有这些腔室均可从加利福尼亚州圣克拉拉的应用材料公司购得。来自应用材料公司或其他制造商的其他处理腔室亦可受益于本文揭示的发明设备。

[0051]

处理腔室300包含用于在其上接收基板304的基板支撑基座302,及溅射源,诸如靶材306。基板支撑基座302可位于接地腔室壁308内,接地腔室壁308可为腔室壁(如图所示)或接地屏蔽件,诸如覆盖处理腔室300中靶材306上方至少一些部分的接地屏蔽件340。在一些实施方式中,接地屏蔽件340可延伸到靶材下方,以包围基板支撑基座302。

[0052]

在一些实施方式中,处理腔室包括用于将射频及脉冲dc能量耦接到靶材306的馈送结构。馈送结构是用于将射频及脉冲dc能量耦接到例如靶材或包含靶材的组件的装置,如本文所述。馈送结构的第一端可耦接到射频功率源318及脉冲dc功率源320,这些功率源可分别用于向靶材306提供射频及脉冲dc能量。例如,dc功率源320可用于向靶材306施加负电压或偏压。在一些实施方式中,由射频功率源318提供的射频能量可适合于提供如上所述的频率,或者其频率范围从约2mhz到约60mhz,或者例如,可使用诸如2mhz、13.56mhz、27.12mhz或60mhz的非限制性频率。在一些实施方式中,可提供多个射频功率源(亦即,两个或更多个)以提供多个上述频率的射频能量。馈送结构可由合适的导电材料制成,以传导来自射频功率源318及脉冲dc功率源320的射频及脉冲dc能量。

[0053]

在一些实施方式中,馈送结构可具有合适的长度,从而有助于围绕馈送结构的周边基本均匀地分配相应的射频及脉冲dc能量。例如,在一些实施方式中,馈送结构可具有约1至约12英寸之间、或者约4英寸的长度。在一些实施方式中,主体可具有至少约1:1的长度与内径之比。至少1:1或更长的比率提供了来自馈送结构的更均匀的射频传递(亦即,射频能量更均匀地围绕馈送结构分布,以近似射频耦接到馈送结构的真实中心点。馈送结构的内径可尽可能小,例如从约1英寸到约6英寸,或者直径约4英寸。提供较小的内径有助于在不增加馈送结构长度的情况下提高长度与内径(id)之比。

[0054]

馈送结构的第二端可耦接到源分配板322。源分配板包括穿过源分配板322设置的孔324,且所述孔与馈送结构的中心开口对齐。源分配板322可由合适的导电材料制成,以传导来自馈送结构的射频及脉冲dc能量。

[0055]

源分配板322可经由导电构件325耦接到靶材306。导电构件125可为管状构件,其

第一端326靠近源分配板322的周边边缘而耦接到源分配板322的面向靶材的表面328。导电构件325进一步包括第二端330,该第二端330靠近靶材306的周边边缘而耦接到靶材306的面向源分配板的表面332(或者耦接到靶材306的背板346)。

[0056]

可由导电构件325的面向内部的壁、源分配板322的面向靶材的表面328及靶材306的面向源分配板的表面332限定空腔334。空腔334经由源分配板322的孔324流体耦接到主体的中心开口315。空腔334及主体的中心开口315可用于至少部分容纳可旋转磁控管组件336的一或更多个部分,如图3所示且如下文进一步描述。在一些实施方式中,空腔可至少部分填充冷却流体,例如水(h2o)或类似流体。

[0057]

可提供接地屏蔽件340来覆盖处理腔室300的盖的外表面。接地屏蔽件340可例如经由腔室主体的接地连接件来耦接到接地。接地屏蔽件340具有中心开口,以允许馈送结构穿过接地屏蔽件340,从而耦接到源分配板322。接地屏蔽件340可包括任何合适的导电材料,诸如铝、铜或类似材料。在接地屏蔽件340与源分配板322、导电构件325及靶材306(及/或背板346)的外表面之间提供绝缘间隙339,以防止射频及脉冲dc能量直接被引导到接地。绝缘间隙可填充有空气或一些其他合适的介电材料,诸如陶瓷、塑料或类似材料。

[0058]

在一些实施方式中,可围绕馈送结构的主体及下部设置接地环。接地环耦接到接地屏蔽件340,且可为接地屏蔽件340的一体部分或者是耦接到接地屏蔽件的独立部分,以提供馈送结构的接地。接地环可由合适的导电材料制成,诸如铝或铜。在一些实施方式中,设置在接地环的内径与馈送结构主体的外径之间的间隙可保持最小,且刚好足以提供电隔离。所述间隙可填充有隔离材料,如塑胶或陶瓷,或者可为空气间隙。接地环防止射频馈送(例如,下文论述的电馈送205)与主体之间的串扰,从而改善等离子体及处理的均匀性。

[0059]

隔离板338可设置在源分配板322与接地屏蔽件340之间,以防止射频及脉冲dc能量直接被引导到接地。隔离板338具有中心开口,以允许馈送结构穿过隔离板338并耦接到源分配板322。隔离板338可包括合适的介电材料,诸如陶瓷、塑料或类似材料。或者,可提供气隙来代替隔离板338。在提供气隙来代替隔离板的实施方式中,接地屏蔽件340可在结构上足够坚固,以支撑放置在接地屏蔽件340上的任何部件。

[0060]

靶材306可通过介电隔离体344支撑在接地的导电铝适配器上,如342。靶材306包括溅射期间待沉积在基板304上的材料,诸如硅化镍。在一些实施方式中,背板346可耦接到靶材306的面向源分配板的表面332。背板346可包括导电材料,诸如硅化镍,或者与靶材相同的材料,使得射频及脉冲dc功率可经由背板346耦接到靶材306。或者,背板346可为非导电的,且可包括导电元件(未示出),诸如电馈通或类似物,以用于将靶材306的面向源分配板的表面332耦接到导电构件325的第二端330。例如,可包括背板346,以提高靶材306的结构稳定性。

[0061]

基板支撑基座302具有面向靶材306的主表面的材料接收表面,且在与靶材306的主表面相对的平面位置支撑待溅射涂覆的基板304。基板支撑基座302可在处理腔室300的中心区域348中支撑基板304。中心区域348被定义为处理期间基板支撑基座302上方的区域(例如,当处于处理位置时,在靶材306与基板支撑基座302之间)。

[0062]

在一些实施方式中,基板支撑基座302可通过连接到底部腔室壁352的波纹管350垂直移动,以允许基板304通过处理处理腔室300的下部中的装载锁定阀(未示出)被移送到基板支撑基座302上,且随后升高至沉积或处理位置。一或更多种处理气体可从气体源354

经过质量流量控制器356供应到处理腔室300的下部。可提供排气口358,且所述排气口358经由阀360耦接到泵(未示出),以用于排出处理腔室300的内部气体,且有助于保持处理腔室300内部的期望压力。

[0063]

射频偏压功率源362可耦接到基板支撑基座302,以便在基板304上诱导负dc偏压。此外,在一些实施方式中,在处理期间,负dc自偏压可形成在基板304上。例如,由射频偏压功率源362提供的射频功率的频率范围可从约2mhz至约60mhz,例如,可使用诸如2mhz、13.56mhz或60mhz的非限制性频率。此外,第二射频偏压功率源可耦接到基板支撑基座302且提供上文论述的任何频率以与射频偏压功率源362一起使用。在其他应用中,基板支撑基座302可接地或保持电浮动。例如,对于可能不期望使用射频偏压功率的应用,可将电容调谐器364耦接到基板支撑基座,以用于调节基板304上的电压。

[0064]

可旋转的磁控管组件336可位于靶材306的后表面(例如,面向源分配板的表面332)附近。可旋转的磁控管组件336包括由基底板368支撑的多个磁体366。基底板368连接到旋转轴370,旋转轴370与处理腔室300及基板304的中轴重合。马达372可耦接到旋转轴370的上端,以驱动磁控管组件336的旋转。磁体366在处理腔室300内产生磁场,所述磁场大体平行于并靠近靶材306的表面,以俘获电子并增大局部等离子体密度,此继而增大溅射速率。磁体366在处理腔室300的顶部周围产生电磁场,且磁体366旋转以旋转电磁场,这影响工艺的等离子体密度,从而更均匀地溅射靶材306。例如,旋转轴370可每分钟旋转约0至约150转。

[0065]

在一些实施方式中,处理腔室300可进一步包括连接到适配器342的凸缘376的处理配件屏蔽件374。适配器342又被密封并接地到铝腔室侧壁,诸如腔室壁308。通常,处理配件屏蔽件374沿着适配器342的壁及腔室壁308向下延伸到基板支撑基座302的上表面下方,并向上返回,直到到达基板支撑基座302的上表面(例如,在底部形成u形部分384)。或者,处理配件屏蔽件的最底部不需要是u形部分384,且可具有任何合适的形状。当基板支撑基座302处于下部装载位置时,盖环386搁置在处理配件屏蔽件374的向上延伸的唇缘388的顶部,但当基板支撑基座302处于上部沉积位置时,盖环386则搁置在基板支撑基座302的外周上,以保护基板支撑基座302免于溅射沉积。额外的沉积环(未示出)可用于防止基板304的周边发生沉积。下文根据本揭示案论述处理配件屏蔽件的实施方式。

[0066]

在一些实施方式中,磁体390可围绕处理腔室300设置,用于选择性地在基板支撑基座302与靶材306之间提供磁场。例如,如图3所示,当处于处理位置时,磁体390可在刚好位于基板支撑基座302上方的区域中围绕腔室壁308的外部设置。在一些实施方式中,磁体390可额外地或替代地设置在其他位置,诸如邻近适配器342。磁体390可为电磁体,且可耦接至电源(未示出),用于控制电磁体产生的磁场的大小。

[0067]

控制器310可被提供并耦接到处理腔室300的各种部件,以控制其操作。控制器310包括中央处理单元(central processing unit;cpu)312、存储器314及支持电路316。控制器310可直接控制处理腔室300,或者经由与特定处理腔室及/或支持系统部件相关联的计算机(或控制器)来控制处理腔室300。控制器310可为任何形式的通用计算机处理器中的一种,其可在工业环境中用于控制各种腔室及子处理器。控制器310的存储器或计算机可读介质434可为可方便获得的存储器中之一或更多者,诸如随机存取存储器(random access memory;ram)、只读存储器(read only memory;rom)、软盘、硬盘、光储存介质(例如,光盘或

数字影盘)、快闪存储器驱动器、或本地或远程的任何其他形式的数字储存器。支持电路316耦接到cpu 312,用于以常规方式支持处理器。这些电路包括快取存储器、电源、时钟电路、输入/输出电路系统及子系统等。本文所述的发明方法可作为软件程序储存在存储器314中,所述软件程序可被执行或调用来以本文所述的方式控制处理腔室300的操作。软件程序亦可由位于正在受cpu 312控制的硬件的远端的第二cpu(未示出)储存及/或执行。

[0068]

在一些实施方式中,本揭示案涉及被配置为用于在基板上形成硅化镍材料的物理气相沉积腔室。例如,在实施方式中,物理气相沉积腔室被配置为用于在约15℃至约27℃的温度下在基板顶部沉积第一硅化镍种晶层;且/或在约15℃至约27℃的温度下在第一硅化镍种晶层顶部沉积第二硅化镍层,以形成硅化镍材料。

[0069]

因此,本文提供了用于在基板上形成的高深宽比特征中沉积金属的方法。本发明方法有利地用金属连续覆盖高深宽比特征的表面,同时减少可能导致在高深宽比特征中形成空隙的突出物或小面(facet)。本发明方法可用于硅穿孔(through silicon via;tsv)应用,例如,用于最先通孔或或最后通孔的制造方法,及沉积连续金属层可为有利的其他合适的应用。

[0070]

现参考图4,该图图示降低硅化镍材料电阻率的方法400。方法400包括:a)在410处,在约15℃至约27℃的温度下,在基板顶部沉积硅化镍层;b)在420处,在超过350℃的温度下,或者在实施方式中,在400℃或更低的温度下,对第一硅化镍种晶层进行退火;及c)在430处重复a)(410)及b)(420),直到硅化镍材料具有预定的厚度。在实施方式中,工艺条件与上文关于方法100描述的条件相同。在实施方式中,可进一步处理基板,诸如通过在第二硅化镍层顶部沉积tin覆盖层。在实施方式中,沉积硅化镍层的温度为约20℃至约25℃、22℃、23℃、24℃或25℃。在实施方式中,硅化镍种晶层具有约20埃至60埃、约30埃至50埃、约35埃至45埃、约20埃、约25埃、约30埃、约35埃、约40埃、约50埃、约60埃的厚度。在一些实施方式中,通过在物理气相沉积工艺中将基板暴露于硅化镍来沉积第一硅化镍种晶层及第二硅化镍层。在实施方式中,使用包括镍及硅靶材的物理气相沉积工艺形成第一硅化镍种晶层及第二硅化镍层,所述靶材具有约1:1的镍与硅比率。在一些实施方式中,硅化镍材料具有20至50欧姆/平方、20至40欧姆/平方、20至30欧姆/平方、20至35欧姆/平方、20欧姆/平方、20欧姆/平方、21欧姆/平方、22欧姆/平方、23欧姆/平方、24欧姆/平方、25欧姆/平方、26欧姆/平方、27欧姆/平方、28欧姆/平方、29欧姆/平方、30欧姆/平方、35欧姆/平方或40欧姆/平方的量的薄层电阻。

[0071]

在一些实施方式中,本揭示案涉及物理气相沉积腔室,其被配置为用于降低硅化镍材料的电阻率。例如,在实施方式中,物理气相沉积腔室被配置为用于在约15℃至约27℃的温度下在基板顶部沉积硅化镍层,直到硅化镍材料具有预定厚度。

[0072]

现参考图5,该图图示在基板上形成互连的方法500。实施方式包括,在510处,在约15℃至约27℃的温度下,在基板上物理气相沉积第一硅化镍种晶层;在超过350℃的温度下对第一硅化镍种晶层进行退火520;以及在约15℃至约27℃的温度下,在第一硅化镍种晶层顶部物理气相沉积530第二硅化镍层,以形成硅化镍材料。在一些实施方式中,在约15℃至约27℃的温度下,在基板上物理气相沉积第一硅化镍种晶层;在400℃或更低的温度下对第一硅化镍种晶层进行退火520;且在约15℃至约27℃的温度下,在第一硅化镍种晶层顶部物理气相沉积530第二硅化镍层,以形成硅化镍材料。

[0073]

在一些实施方式中,本揭示案涉及被配置为用于在基板上形成互连的物理气相沉积腔室。例如,在实施方式中,物理气相沉积腔室被配置为用于在约15℃至约27℃的温度下在基板上物理气相沉积第一硅化镍种晶层,且/或在约15℃至约27℃的温度下在第一硅化镍种晶层顶部物理气相沉积第二硅化镍层,以形成硅化镍材料。

[0074]

图6是示例性整合系统600的俯视示意平面图,该系统包括至少一个沉积处理腔室300,比如根据本揭示案配置的处理腔室。在一些实施方式中,整合系统600可为整合处理系统,该系统可从位于加利福尼亚州圣克拉拉的应用材料公司购得。其他处理系统(包括来自其他制造商的处理系统)可经调适以从本揭示案中受益。

[0075]

在一些实施方式中,整合系统600包括真空密封处理平台(诸如处理平台604)、工厂界面602及系统控制器644。处理平台604包括至少一个沉积处理腔室300、被配置用于根据本揭示案进行退火的至少一个热处理腔室601、及可选地多个处理腔室628、620、610及耦接到真空基板移送腔室(诸如移送腔室636)的至少一个装载锁定腔室622。图6中示出了两个装载锁定腔室622。工厂界面602通过装载锁定腔室622耦接到移送腔室636。

[0076]

在一个实施方式中,工厂界面602包括至少一个对接站608及至少一个工厂界面机器人614,以便于基板的移送。对接站608被配置为接受一或更多个前开式统一晶片盒(front opening unified pod;foup)。在图6的实施方式中示出了两个foup 606a-b。具有设置在工厂界面机器人614一端上的叶片616的工厂界面机器人614被配置为通过装载锁定腔室622将基板从工厂界面602移送至处理平台604,以用于进行处理。可选地,一或更多个处理腔室610、620、628、至少一个沉积处理腔室300、被配置用于根据本揭示案进行退火的至少一个热处理腔室601可连接到工厂界面602的端子626,以便于处理来自foup 606a-b的基板

[0077]

每个装载锁定腔室622具有耦接到工厂界面602的第一端口及耦接到移送室636的第二端口。装载锁定腔室622耦接到压力控制系统(未示出),该压力控制系统对装载锁定腔室622抽真空及通气,以便于在移送室636的真空环境与工厂界面602的大体上周围(例如大气)环境之间递送基板。

[0078]

移送室636中设置有真空机器人630。真空机器人630具有能够在装载锁定腔室622、至少一个沉积处理腔室300、被配置用于根据本揭示案进行退火的至少一个热处理腔室601与处理腔室610、620及628之间移送基板的叶片634。

[0079]

在整合系统600的一些实施方式中,整合系统600可包括至少一个沉积处理腔室300及其他处理腔室610、620、628、被配置用于根据本揭示案进行退火的至少一个热处理腔室601。在一些实施方式中,处理腔室610、620、628可为沉积腔室、蚀刻腔室、热处理腔室或其他类似类型的半导体处理腔室。

[0080]

系统控制器644耦接到整合系统600。系统控制器644可包括计算装置641或被包括在计算装置441内,该系统控制器644使用对整合系统600的处理腔室610、620、628、至少一个沉积处理腔室300、被配置用于根据本揭示案进行退火的至少一个热处理腔室601的直接控制来控制整合系统600的操作。或者,系统控制器644可控制与处理腔室610、620、628、至少一个沉积处理腔室300、被配置用于根据本揭示案进行退火的至少一个热处理腔室601及整合系统600相关联的计算机(或控制器)。在操作中,系统控制器644亦使得能够从各个腔室及处理腔室(例如至少一个沉积处理腔室300、被配置用于根据本揭示案进行退火的至少

一个热处理腔室601)收集数据并进行反馈,以使整合系统600的效能最佳化。

[0081]

系统控制器644大体包括中央处理单元(cpu)638、存储器640及支持电路642。cpu 638可为可在工业环境中使用的任何形式的通用计算机处理器中的一者。支持电路642常规地耦接到cpu 638,且可包括快取存储器、时钟电路、输入/输出子系统、电源等。软件程序将cpu 638转换成专用计算机(系统控制器)644。软件程序亦可由在整合系统600远端定位的第二控制器(未示出)储存及/或执行。可包括存储器或cpu的计算机可读介质,其中包括可方便获得的存储器中的一或更多者,诸如随机存取存储器(ram)、只读存储器(rom)、软盘、硬盘或本地或远程的任何其他形式的数字储存器。

[0082]

在一些实施方式中,本揭示案包括整合系统,所述系统包括:真空基板移送室;至少一个沉积处理腔室,该腔室被配置为根据本揭示案进行沉积;至少一个热处理腔室,该腔室被配置为根据本揭示案进行退火,其中整合系统被配置为在真空下将基板从被配置为根据本揭示案进行沉积的至少一个沉积处理腔室移动至被配置为根据本揭示案进行退火的至少一个热处理腔室。在一些实施方式中,本揭示案涉及一基板处理系统,该系统包括:物理气相沉积腔室,该腔室被配置为用于在约15℃至约27℃的温度下在基板上物理气相沉积第一硅化镍种晶层,且在约15℃至约27℃的温度下在第一硅化镍种晶层顶部物理气相沉积第二硅化镍层以形成硅化镍材料;及热处理腔室,该腔室被配置为用于在超过350℃的温度下对第一硅化镍种晶层进行退火。在一些实施方式中,基板处理系统进一步包括真空基板移送室,其中物理气相沉积腔室耦接到真空基板移送腔室;以及耦接到真空基板移送腔室的热处理腔室,其中基板处理系统被配置成在真空下将基板从物理气相沉积腔室移动到热处理腔室。

[0083]

在一些实施方式中,本揭示案包括其上储存有指令的计算机可读介质,所述指令在被执行时,使整合系统执行在基板上形成硅化镍材料的方法,所述方法包括:在约15℃至约27℃的温度下在基板顶部沉积第一硅化镍种晶层;在高于350℃的温度下对第一硅化镍种晶层进行退火;及在约15℃至约27℃的温度下,在第一硅化镍种晶层顶部沉积第二硅化镍层,以形成硅化镍材料。

[0084]

在一些实施方式中,本揭示案包括其上储存有指令的计算机可读介质,所述指令在被执行时,使整合系统执行降低硅化镍材料电阻率的方法,所述方法包括:a)在约15℃至约27℃的温度下在基板顶部沉积硅化镍层;b)在高于350℃的温度下对硅化镍层进行退火;及c)重复a)及b),直到硅化镍材料具有预定厚度。

[0085]

在一些实施方式中,本揭示案包括其上储存有指令的计算机可读介质,所述指令在被执行时,使整合系统执行在基板上形成互连的方法,所述方法包括:在约15℃至约27℃的温度下在基板上物理气相沉积第一硅化镍种晶层;在高于350℃的温度下对第一硅化镍种晶层进行退火;及在约15℃至约27℃的温度下,在第一硅化镍种晶层顶部物理气相沉积第二硅化镍层,以形成硅化镍材料。

[0086]

尽管前文针对本揭示案的实施方式,但在不脱离本揭示案的基本范围的情况下,可设计本揭示案的其他及更多实施方式。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1