显示装置及其制造方法与流程

[0001]

本发明涉及显示装置及其制造方法。

背景技术:

[0002]

使用低温多晶硅的薄膜晶体管(tft)因驱动能力高且载流子迁移率高而被用于有机电致发光显示器、高清液晶显示器,但截止电流高且漏电流的抑制困难。因而,近年来,开发了使用氧化物半导体的tft(专利文献1及2)。

[0003]

现有技术文献

[0004]

专利文献

[0005]

专利文献1:日本特开2016-100521号公报

[0006]

专利文献2:日本特开2012-104639号公报

技术实现要素:

[0007]

发明要解决的课题

[0008]

在底栅型的tft中,在半导体层之上对金属膜进行蚀刻以形成源电极及漏电极。由于金属与半导体的蚀刻选择比小,因此,金属的蚀刻中较多使用的氯气会导致半导体层的无谓的蚀刻。特别是,在与源电极及漏电极邻接的部分,半导体层的膜厚变得很不均匀。氧化物半导体tft虽然截止电流低,但由于载流子迁移率低,因此,不均匀的膜厚对特性造成的影响较大。

[0009]

本发明目的在于抑制氧化物半导体层的膜厚不均匀化。

[0010]

用于解决课题的手段

[0011]

本发明的显示装置的特征在于,具有用于控制图像显示的多个薄膜晶体管,所述多个薄膜晶体管中的各自分别为底栅型且具有:栅电极、覆盖所述栅电极的栅极绝缘膜、位于所述栅极绝缘膜之上的氧化物半导体层、与所述氧化物半导体层的第1上表面区域接触的硅氧化物、与所述氧化物半导体层的第2上表面区域接触的硅氮化物、和位于所述栅极绝缘膜的上方的源电极及漏电极,所述第2上表面区域在所述源电极与所述漏电极之间的方向上与所述第1上表面区域的两侧中的各自分别邻接,所述氧化物半导体层包含所述硅氧化物紧下的半导体部和所述硅氮化物紧下的导电部。

[0012]

根据本发明,还原剂层所接触的第2上表面区域与氧化剂层所接触的第1上表面区域的两侧中的各自分别邻接。由第1上表面区域被氧化而成的半导体部不与源电极及漏电极邻接。因此,在与第1上表面区域邻接的部分,氧化物半导体层的膜厚的不均匀化得到抑制。

[0013]

本发明的显示装置的制造方法的特征在于,包含下述工序:形成栅电极的工序;以覆盖所述栅电极的方式形成栅极绝缘膜的工序;在所述栅极绝缘膜之上形成氧化物半导体层的工序;经所述氧化物半导体层之上的成膜及蚀刻,以避开所述氧化物半导体层的第1上表面区域及第2上表面区域的方式形成源电极及漏电极的工序;以与所述氧化物半导体层

的所述第1上表面区域接触的方式形成氧化剂层,在所述第1上表面区域中将所述氧化物半导体层氧化的工序;和以与所述氧化物半导体层的所述第2上表面区域接触的方式形成还原剂层,在所述第2上表面区域中将所述氧化物半导体层还原的工序,所述制造方法中,所述第2上表面区域在所述源电极与所述漏电极之间的方向上与所述第1上表面区域的两侧中的各自分别邻接。

[0014]

根据本发明,还原剂层所接触的第2上表面区域与氧化剂层所接触的第1上表面区域的两侧中的各自分别邻接。用于由氧化剂层氧化的第1上表面区域不与源电极及漏电极邻接。因此,在与第1上表面区域邻接的部分中,能够抑制由蚀刻引起的氧化物半导体层的膜厚的不均匀化。

附图说明

[0015]

图1是本发明第1实施方式的显示装置的俯视图。

[0016]

图2是显示装置的电路图。

[0017]

图3是示出连同像素的元件构造的俯视图。

[0018]

图4是示出图1所示的显示装置的截面的示意图。

[0019]

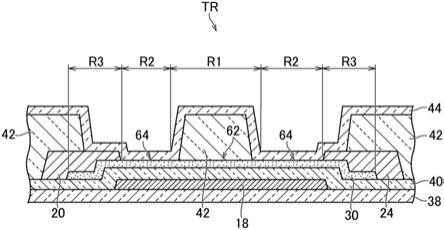

图5是薄膜晶体管的详细剖视图。

[0020]

图6是薄膜晶体管的详细俯视图。

[0021]

图7是示出第1实施方式的变形例的显示装置的薄膜晶体管的详细剖视图。

[0022]

图8是示出第2实施方式的显示装置的薄膜晶体管的详细剖视图。

[0023]

图9是薄膜晶体管的详细俯视图。

[0024]

图10是示出第3实施方式的显示装置的薄膜晶体管的详细剖视图。

[0025]

图11是第4实施方式的显示装置的剖视图。

[0026]

图12是示出显示装置的整体电路的图。

[0027]

图13是示出图12所示的像素的电路构成的图。

具体实施方式

[0028]

以下,参照附图说明本发明的实施方式。但是,本发明能够在不脱离其要旨的范围内以多种方式实施,并非限定地解释为以下例示的实施方式的记载内容。

[0029]

为了使说明更加明确,附图中存在将各部分的宽度、厚度、形状等与实际形态相比示意性示出的情况,但只不过是一例,并非限定本发明的解释。在本说明书和各附图中,存在针对与关于已有的附图说明过的要素具有相同功能的要素标注同一附图标记并省略重复说明的情况。

[0030]

此外,在本发明的详细说明中,在规定某个构成物与其他构成物的位置关系时,“在

……

上”、“在

……

下”不仅是位于某个构成物的紧上或紧下的情况,只要没有特别说明,也包含在其间还存在其他构成物的情况。

[0031]

[第1实施方式]

[0032]

图1是本发明第1实施方式的显示装置的俯视图。显示装置实际上弯折使用,因此,图1是将显示装置弯折前的展开图。显示装置包含显示器dp。显示器dp具有挠性,在位于显示图像的显示区域da的外侧的弯曲对应区域ba中弯折。在显示器dp上,搭载有用于驱动用

于显示图像的元件的集成电路芯片cp。在显示器dp上,在显示区域da的外侧连接有柔性印刷基板fp。显示装置例如为有机电致发光显示装置。在显示区域da中,例如,将由红、绿及蓝组成的多个颜色的像素(子像素)组合以显示全彩图像。

[0033]

图2是显示装置的电路图。电路具有与扫描电路gd连接的多条扫描线gl和与信号驱动电路sd连接的多条信号线dl。在图1所示的集成电路芯片cp内,配置有信号驱动电路sd。由邻接的2条扫描线gl和邻接的2条信号线dl包围的区域为1个像素px。像素px包含作为驱动晶体管的薄膜晶体管tr及开关元件sw和保持电容cs。通过对扫描线gl施加栅极电压,从而开关元件sw成为on状态(导通状态),从信号线dl供给影像信号,在保持电容cs中蓄积电荷。通过在保持电容cs中蓄积电荷,从而薄膜晶体管tr成为on状态,电流从电源线pwl流入发光元件od。在该电流的作用下,发光元件od发光。

[0034]

图3是示出连同像素的元件构造的俯视图。图2中示出的扫描线gl的一部分为开关元件sw(例如薄膜晶体管)的栅电极10。图2中示出的信号线dl的一部分为开关元件sw的一个源/漏电极12(源电极及漏电极中的一者)。开关元件sw的半导体层14以多晶硅为主原料。需要说明的是,使用低温多晶硅的薄膜晶体管虽然电子迁移率高,但截止电流高且漏电流的抑制困难。

[0035]

开关元件sw的另一源/漏电极16(源电极及漏电极中的另一者)与薄膜晶体管tr的栅电极18连接。电源线pwl的一部分为薄膜晶体管tr的一个源/漏电极20(源电极及漏电极中的一者)。

[0036]

薄膜晶体管tr的栅电极18与第1电容电极22连接。薄膜晶体管tr的另一源/漏电极24(源电极及漏电极中的另一者)与第2电容电极26连接。第1电容电极22及第2电容电极26相互对置,构成保持电容cs。第2电容电极26与像素电极28连接。薄膜晶体管tr具有氧化物半导体层30。

[0037]

图4是示出图1所示的显示装置的截面的示意图。基板32由聚酰亚胺形成。需要说明的是,若是为了构成薄片状显示器或柔性显示器而具有充分的挠性的基材,则也可以使用其他树脂材料。也可以在基板32的背面介由压敏粘接剂粘贴加强膜。

[0038]

在基板32上层叠有底涂层34。底涂层34包含硅氧化膜34a及硅氧化膜34b。下层的硅氧化膜34a被设置以用于提高与基板32的密合性,上层的硅氧化膜34b被设置以作为阻止氢原子扩散至开关元件sw的半导体层14的阻挡膜,但并非特别限定于该构造,也可以具有其他叠层或为单层。

[0039]

在开关元件sw的下方配置有用于抑制由光从沟道背面侵入等引起的特性变化或赋予背栅效应的附加膜36。在此,在形成硅氧化膜34a后,对应于形成有开关元件sw的部位而将附加膜36形成为岛状,之后通过层叠硅氧化膜34b从而在底涂层34中封入附加膜36,但不限于此,也可以先在基板32上形成附加膜36,之后形成底涂层34。

[0040]

在底涂层34上形成有开关元件sw。以多晶硅薄膜晶体管为例,在此仅示出nch晶体管,但也可以同时形成pch晶体管。开关元件sw的半导体层14采用在沟道区域与源/漏区域之间设有低浓度杂质区域的构造。作为栅极绝缘膜38,在此使用硅氧化膜。

[0041]

在栅电极10之上层叠有绝缘膜40(硅氧化膜及硅氮化膜)。以贯通绝缘膜40的方式形成有源/漏电极12、16。在此,采用ti、al及ti的三层层合构造。开关元件sw为顶栅极型,在半导体层14的上方具有栅电极10。

[0042]

薄膜晶体管tr的栅电极18位于与开关元件sw的栅电极10同层的位置。绝缘膜40为覆盖开关元件sw的栅电极10的层间绝缘膜,并且,也是薄膜晶体管tr的栅极绝缘膜。在栅电极18的上方,存在氧化物半导体层30。氧化物半导体层30形成在绝缘膜40之上。一对源/漏电极20、24(源电极及漏电极)也形成在绝缘膜40之上。一对源/漏电极20、24还载置于氧化物半导体层30的端部。

[0043]

薄膜晶体管tr具有氧化物半导体层30作为沟道区域,因此能够减小电流波动。薄膜晶体管tr位于比开关元件sw靠上的层位置。因此,薄膜晶体管tr在开关元件sw之后形成,因此不会受到形成由低温多晶硅形成的半导体层14时的热量的影响。薄膜晶体管tr的详情见后述(参照图5)。

[0044]

第1电容电极22也形成在绝缘膜40之上。以覆盖薄膜晶体管tr及第1电容电极22的方式层叠有氧化剂层42及还原剂层44(详细见后述)。在该氧化剂层42及还原剂层44上形成有第2电容电极26。氧化剂层42及还原剂层44成为图2中示出的保持电容cs的电介质。

[0045]

以覆盖还原剂层44及第2电容电极26的方式设有平坦化有机膜46。平坦化有机膜46与通过cvd(chemical vapor deposition:化学气相沉积)等形成的无机绝缘材料相比,表面的平坦性优异,因此使用感光性丙烯酸树脂等树脂。

[0046]

在平坦化有机膜46之上层叠有像素电极28。像素电极28形成为反射电极,成为氧化铟锌膜、ag膜、氧化铟锌膜的三层层合构造。在此,也可以取代氧化铟锌膜而使用氧化铟锡膜。

[0047]

以载置于平坦化有机膜46之上且载置于像素电极28的周缘的方式,形成有被称为隔堤(突肋)且成为相邻的像素区域的分隔壁的绝缘有机膜48。作为绝缘有机膜48,与平坦化有机膜46同样地使用感光性丙烯酸树脂等。绝缘有机膜48以使像素电极28的表面作为发光区域而露出的方式开口,优选其开口端成为平滑的锥形状。若开口端成为陡峭的形状,则会导致在其上形成的有机电致发光层50的覆盖不良。

[0048]

在像素电极28之上层叠有由有机材料形成的有机电致发光层50。有机电致发光层50可以是单层,但也可以是从像素电极28侧起依次层叠有空穴传输层、发光层及电子传输层的构造。这些层可以通过蒸镀形成,或是通过溶剂分散后的涂布形成,或是针对像素电极28(各子像素)选择性地形成,或是整面形成为覆盖显示区域da的整个面。在整面形成的情况下,成为在全部子像素中得到白色光并利用滤色器(未图示)取出希望的颜色波长部分的构成。

[0049]

在有机电致发光层50之上设有对置电极52。在此,由于形成为顶部发光构造,因此对置电极52是透明的。例如,将mg层及ag层形成为可供来自有机电致发光层50的出射光透射程度的薄膜。依照前述的有机电致发光层50的形成顺序,像素电极28成为阳极,对置电极52成为阴极。由多个像素电极28、对置电极52、和存在于多个像素电极28各自的中央部与对置电极52之间的有机电致发光层50构成发光元件od。

[0050]

在对置电极52之上,形成有封固层54。封固层54的功能之一是防止来自外部的水分侵入在先形成的有机电致发光层50,要求高阻气性。封固层54成为封固有机膜54b及从上下夹着该封固有机膜54b的一对封固无机膜54a、54c(例如硅氮化膜)的层合构造。一对封固无机膜54a、54c在封固有机膜54b的周围接触并重叠。出于提高密合性作为目的之一,在封固无机膜54a、54c与封固有机膜54b之间设有硅氧化膜、非晶硅层。在封固层54上层叠有加

强有机膜56。在加强有机膜56上介由粘合层58粘贴有偏光板60。偏光板60为例如圆偏光板。

[0051]

图5是薄膜晶体管tr的详细剖视图。图6是薄膜晶体管tr的详细俯视图。

[0052]

显示装置具有用于控制图像显示的多个薄膜晶体管tr。多个薄膜晶体管tr中的各自分别为底栅型。薄膜晶体管tr具有栅电极18。薄膜晶体管tr具有覆盖栅电极18的绝缘膜40。薄膜晶体管tr具有位于绝缘膜40的上方的一对源/漏电极20、24(源电极及漏电极)。

[0053]

薄膜晶体管tr具有位于绝缘膜40之上的氧化物半导体层30。氧化物半导体层30由例如铟/镓/锌/氧(igzo;氧化铟镓锌)形成。这样的薄膜晶体管tr具有截止电流低的特性。

[0054]

氧化物半导体层30具有第1上表面区域r1。氧化物半导体层30的第1上表面区域r1与氧化剂层42接触。氧化剂层42具有硅氧化物。氧化物半导体层30包含从第1上表面区域r1从氧化剂层42出发经氧化而形成的半导体部62。半导体部62因氧化使得电子减少而显示出半导体性,从而能够实现晶体管的动作。氧化剂层42还载置于一对源/漏电极20、24(源电极及漏电极)。

[0055]

氧化物半导体层30具有第2上表面区域r2。第2上表面区域r2在一对源/漏电极20、24(源电极及漏电极)之间的方向上与第1上表面区域r1的两侧中的各自分别邻接。氧化物半导体层30的第2上表面区域r2与还原剂层44接触。还原剂层44具有含有氢的硅氮化物。关于氢,其存在根据成膜条件而被含有的情况、硅氮化物原本就含有的情况。氢通过与氧键合而引发将氧抽出的还原反应。氧化物半导体层30包含从第2上表面区域r2起被还原剂层44还原而形成的导电部64。对于导电部64而言,其因还原而使得氧被脱除,从而使得作为载流子的电子增加而成为导体。还原剂层44也载置于氧化剂层42。

[0056]

氧化物半导体层30具有夹着第1上表面区域r1及第2上表面区域r2的一对第3上表面区域r3。一对源/漏电极20、24分别与一对第3上表面区域r3接触而载置并电连接于该一对第3上表面区域r3。一对源/漏电极20、24由金属形成。氧化物半导体层30在一对第3上表面区域r3中被金属还原而实现导电化。

[0057]

就氧化物半导体层30而言,半导体部62与导电部64相比氧浓度增高而氢浓度降低。此外,与半导体部62相比,导电部64的电导率较高。此外,第3上表面区域r3紧下的氧化物半导体层30中基本不通电,主要通过源/漏电极20、24进行导电。

[0058]

根据本实施方式,还原剂层44所接触的第2上表面区域r2与氧化剂层42所接触的第1上表面区域r1的两侧中的各自分别邻接。从第1上表面区域r1氧化而形成的半导体部62与一对源/漏电极20、24不邻接。因此,在与第1上表面区域r1邻接的部分,氧化物半导体层30的膜厚的不均匀化得以抑制。

[0059]

[显示装置的制造方法]

[0060]

显示装置的制造方法中,如图5所示,形成栅电极18。以覆盖栅电极18的方式形成绝缘膜40。在绝缘膜40之上形成氧化物半导体层30。

[0061]

经氧化物半导体层30之上的金属膜的成膜及其蚀刻,以避开第1上表面区域r1及第2上表面区域r2的方式形成一对源/漏电极20、24。一对源/漏电极20、24由金属形成,使用氯系气体进行蚀刻。若使用氯系气体,则金属的蚀刻速率与半导体(氧化物半导体)的蚀刻速率接近。另外,对于半导体而言,其在与蚀刻掩膜邻接的部分中膜厚容易变得不均匀。但是,第2上表面区域r2在一对源/漏电极20、24之间的方向上与第1上表面区域r1的两侧中的各自分别邻接。因此,成为氧化物半导体层30的蚀刻掩膜的一对源/漏电极20、24与第1上表

面区域r1分开。

[0062]

以与氧化物半导体层30的第1上表面区域r1及第2上表面区域r2接触的方式形成氧化剂层42。氧化剂层42的形成包含使用氟系气体的干式蚀刻。若使用氟系气体,则由于金属的蚀刻速率与半导体(氧化物半导体)的蚀刻速率不同,因此能够获得高蚀刻选择性。

[0063]

在第1上表面区域r1及第2上表面区域r2中,氧化物半导体层30被氧化剂层42氧化。由此,形成因氧化而使得电子减少而显示出半导体性的半导体部62。氧化剂层42以还载置于一对源/漏电极20、24的方式形成。

[0064]

以与氧化物半导体层30的第2上表面区域r2接触的方式形成还原剂层44。还原剂层44以还载置于氧化剂层42的方式形成。在第2上表面区域r2中,氧化物半导体层30被还原剂层44还原。

[0065]

根据本实施方式,对于用于由氧化剂层42氧化的第1上表面区域r1而言,其不与一对源/漏电极20、24邻接。因此,在与第1上表面区域r1邻接的部分中,由蚀刻引起的氧化物半导体层30的膜厚的不均匀化得到抑制。在半导体部62中,由于膜厚均匀化,因此作为半导体的特性稳定。即使导电部64的膜厚变得不均匀,也由于为经导体化的部位而不会对薄膜晶体管tr的特性造成较大不良影响。

[0066]

[第1实施方式的变形例]

[0067]

图7是示出第1实施方式的变形例的显示装置的薄膜晶体管tr的详细剖视图。在该例中,栅电极118不与源/漏电极120、124(源电极及漏电极)重叠。由此,能够使在栅电极118与源/漏电极120、124之间形成的电容减小或使其消失。其他内容对应第1实施方式中说明的内容。

[0068]

[第2实施方式]

[0069]

图8是示出第2实施方式的显示装置的薄膜晶体管tr的详细剖视图。图9是薄膜晶体管tr的详细俯视图。

[0070]

在本实施方式中,一对源/漏电极220、224(源电极及漏电极)位于避开与氧化物半导体层230重叠的位置。也就是说,源/漏电极220、224未载置于氧化物半导体层230。因此,源/漏电极220、224的端部不存在于氧化物半导体层230之上。作为替代,一对金属层266、268分别与一对第3上表面区域r3接触并载置于该一对第3上表面区域r3。另外,一对金属层266、268分别与一对源/漏电极220、224接触而载置于该一对源/漏电极220、224。氧化物半导体层230在一对第3上表面区域r3中被金属层266、268还原而实现导电化。

[0071]

在本实施方式的显示装置的制造方法中,一对源/漏电极220、224以避开与氧化物半导体层230重叠的方式形成。也就是说,在通过金属膜的蚀刻形成源/漏电极220、224时,将未图示的蚀刻掩膜以覆盖氧化物半导体层230的方式配置。由此,氧化物半导体层230不被蚀刻。特别是,当蚀刻掩膜的端部载置于氧化物半导体层230时,膜厚在其邻接的部分变得不均匀,但在本实施方式中能够避免这种情形。

[0072]

氧化剂层242及还原剂层244以避开一对第3上表面区域r3(其夹着第1上表面区域r1及第2上表面区域r2)的方式形成。一对金属层266、268以分别与一对第3上表面区域r3接触而载置于该一对第3上表面区域r3、并且分别与一对源/漏电极220、224接触而载置于该一对源/漏电极220、224的方式形成。其他内容对应于第1实施方式中说明的内容。需要说明的是,若一对金属层266、268与图4中示出的第2电容电极26在同层中形成,则能够避免处理

成本升高而进行形成。

[0073]

[第3实施方式]

[0074]

图10是示出第3实施方式的显示装置的薄膜晶体管tr的详细剖视图。

[0075]

在本实施方式中,在一对源/漏电极320、324之间的方向上存在相互分离的多个第1上表面区域r1。在多个第1上表面区域r1的各自上分别载置有氧化剂层342,以使氧化物半导体层330被氧化。由此,氧化物半导体层330相互隔开间隔地包含多个半导体部362。半导体部362因氧化而使得电子减少从而显示出半导体性,从而能够实现晶体管的动作。

[0076]

在多个第1上表面区域r1之间存在第2上表面区域r2的一部分。在彼此相邻的第1上表面区域r1之间,在第2上表面区域r2载置还原剂层344,从而使氧化物半导体层330被还原。由此,氧化物半导体层330包含从第2上表面区域r2被还原剂层344还原而形成的导电部364。导电部364因还原而使得氧被脱除,从而使得作为载流子的电子增加而成为导体。其他内容对应于第1实施方式中说明的内容。

[0077]

[第4实施方式]

[0078]

图11是第4实施方式的显示装置的剖视图。显示装置是液晶显示装置。

[0079]

显示装置具有玻璃基板470。在玻璃基板470之上形成有底涂层434,在该底涂层434上存在薄膜晶体管tr。在薄膜晶体管tr的一个源/漏电极420、424(源电极及漏电极中的一者)连接有像素电极428。液晶的驱动应用横向电场方式,在像素电极428的下方配置有公共电极472。在二者之间存在绝缘膜474。在像素电极428上形成有未图示的狭缝。以覆盖多个像素电极428的方式层叠第1取向膜476。

[0080]

显示装置具有对置玻璃基板478。在对置玻璃基板478上,设有黑矩阵480及滤色器层482,在下侧由外罩层(overcoat layer)484覆盖。以覆盖外罩层484的方式层叠第2取向膜486。需要说明的是,在图示的例子中,黑矩阵480配置在对置玻璃基板478与滤色器层482之间,但也可以配置在滤色器层482与外罩层484之间,或者配置在外罩层484与第2取向膜486之间。在第1取向膜476与第2取向膜486之间存在液晶层488。单元间隔(cell gap)由未图示的多个间隔件保持。

[0081]

显示装置在显示图像的显示面的相反侧具有背光源模块490。背光源模块490包含led(light emitting dioder:发光二极管)等光源、导光板、光学薄膜、扩散板、反射板及框架。点光源通过导光板而被转换为面光源。

[0082]

图12是示出显示装置的整体电路的图。显示装置具备显示图像的显示区域da和显示区域da的外侧的周边区域pa。例如,周边区域pa具有包围显示区域da的框缘状的形状。显示装置在显示区域da中具备多个像素px。多个像素px沿第1方向x及第2方向y以矩阵状配置。本实施方式中,由在第1方向x上相邻的3个像素px构成1个全彩像素。

[0083]

显示装置具备多条扫描线gl、多条信号线dl。扫描线gl沿第1方向x延伸并在第2方向y上隔开间隔地配置。信号线dl沿第2方向y延伸并在第1方向x上隔开间隔地配置。需要说明的是,扫描线gl及信号线dl并非必须直线延伸,也可以是其一部分弯曲。扫描线gl与扫描电路gd连接。信号线dl与信号驱动电路sd连接。

[0084]

图13是示出图12所示的像素px的电路构成的图。像素px具备在扫描线gl与信号线dl交叉的位置附近配置的薄膜晶体管tr。薄膜晶体管tr与扫描线gl及信号线dl电连接。扫描线gl与在图12所示的第1方向x上排列的各像素px的薄膜晶体管tr连接。信号线dl与在图

12所示的第2方向y上排列的各像素px中的薄膜晶体管tr连接。

[0085]

像素电极428配置在由扫描线gl和信号线dl包围的区域中。薄膜晶体管tr与像素电极428电连接。像素电极428与公共电极472相对,利用在像素电极428与公共电极472之间产生的电场来驱动液晶层488。公共电极472与图12所示的公共驱动电路cd连接,并遍及多个像素px地配置。保持电容cs的两端与公共电极472及像素电极428电连接。

[0086]

本发明并非限定于上述实施方式,能够进行多种变形。例如,在实施方式中说明的构成能够以实质上相同的构成、发挥相同作用效果的构成或能够达成相同目的的构成来取代。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1