MEMS器件的制作方法

mems器件

技术领域

1.本发明涉及mems(micro electro mechanical systems,微机电系统)器件。

背景技术:

2.在日本特开2008-244725号公报(专利文献1)中记载了一种称为压电薄膜器件的器件。在取出下表面电极而与上表面电极电连接的部分,形成有称为导通孔的纵孔。该纵孔形成至压电体薄膜与下表面电极的界面。在专利文献1中,为了形成导通孔,利用加热后的缓冲氢氟酸进行压电体薄膜的蚀刻。在压电体薄膜与下表面电极的界面停止该蚀刻。

3.在先技术文献

4.专利文献

5.专利文献1:日本特开2008-244725号公报

技术实现要素:

6.发明要解决的课题

7.即便要通过蚀刻形成纵孔而实现与下表面电极的电连接,也有在下表面电极的表面存在金属氧化膜的情况,由于该膜的存在,接触电阻有时变大。

8.对此,本发明的目的在于,在mems器件中降低接触电阻。

9.用于解决课题的手段

10.为了实现上述目的,基于本发明的mems器件具备:压电层,其由压电体的单晶构成;第一电极,其配置于上述压电层的第一方向的表面;以及第一层,其配置为覆盖上述压电层的上述第一方向的表面,上述第一电极被上述第一层覆盖且具有凹部,上述压电层在与上述第一电极的至少一部分对应的位置处具有贯通孔,该贯通孔贯穿为将上述压电层的与上述第一方向相反的一侧即第二方向与上述凹部连结。

11.发明效果

12.根据本发明,能够降低进行从第一电极的电取出时的接触电阻。

附图说明

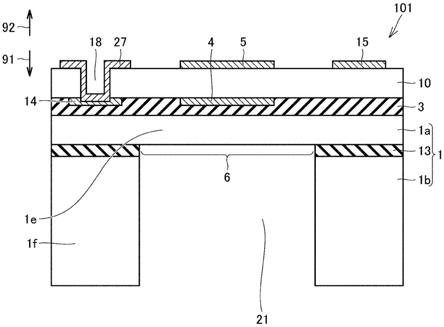

13.图1是基于本发明的实施方式1中的mems器件的剖视图。

14.图2是图1中的贯通孔的附近的放大图。

15.图3是基于本发明的实施方式1中的mems器件的制造方法的第一说明图。

16.图4是基于本发明的实施方式1中的mems器件的制造方法的第二说明图。

17.图5是基于本发明的实施方式1中的mems器件的制造方法的第三说明图。

18.图6是基于本发明的实施方式1中的mems器件的制造方法的第四说明图。

19.图7是基于本发明的实施方式1中的mems器件的制造方法的第五说明图。

20.图8是基于本发明的实施方式1中的mems器件的制造方法的第六说明图。

21.图9是基于本发明的实施方式1中的mems器件的制造方法的第七说明图。

22.图10是基于本发明的实施方式2中的mems器件的剖视图。

23.图11是基于本发明的实施方式3中的mems器件的剖视图。

24.图12是图11中的贯通孔的附近的放大图。

25.图13是第一电极为两种金属膜的层叠构造的情况下的贯通孔的附近的放大图。

具体实施方式

26.附图中所示的尺寸比不一定如实地表示实际情况,为了方便说明,有时夸大示出尺寸比。在以下的说明中,在提及上或下的概念时,不一定指绝对的上或下,有时指图示的姿势中的相对的上或下。

27.(实施方式1)

28.参照图1及图2,对基于本发明的实施方式1中的mems器件进行说明。图1示出本实施方式中的mems器件101的剖视图。图2示出将图1中的贯通孔18的附近放大后的情况。但是,为了方便说明,在图2中,去掉第二电极27而显示。

29.mems器件101是具有膜片部6的mems器件。膜片部6是在压电器件101中变薄而容易变形的部分。在图1所示的例子中,基板1具备薄壁部1e和厚壁部1f。薄壁部1e比厚壁部1f薄,容易变形。从图1中的正下方观察时,薄壁部1e被厚壁部1f包围。在图1所示的例子中,膜片部6包括薄壁部1e。通过在由厚壁部1f包围的地方形成薄壁部1e,从而基板1具有空间21。

30.mems器件101具备:由压电体的单晶构成的压电层10;配置于压电层10的第一方向91的表面的第一电极14;以及配置为覆盖压电层10的第一方向91的表面的作为第一层的中间层3。这里所说的“第一方向91”是指mems器件101的层叠方向上的任意一个朝向。在图1中,如箭头及标记所示,第一方向91是朝向图中的下方的概念。

31.这里所说的“压电体”例如可以是litao3、linbo3、zno或pmn-pt中的任意一种。中间层3是绝缘层。中间层3例如可以由sio2等形成。中间层3也可以设置为多个层。中间层3也可以包括金属层。在mems器件101中,作为基板1而使用soi基板。在图1所示的例子中,膜片部6除了包括基板1的薄壁部1e之外,还包括压电层10的一部分和中间层3的一部分。基板1包括活性层1a和基础部1b,在两者之间夹设有绝缘膜13。压电层10的至少一部分包含在膜片部6中。第一电极14被所述第一层覆盖且具有凹部19。压电层10在与第一电极14的至少一部分对应的位置具有贯通孔18,该贯通孔18贯穿为将压电层10的与第一方向91相反的一侧即第二方向92的表面与凹部19连结。

32.在这里所示的例子中,在压电层10的上表面形成有上部电极5,在压电层10的下表面形成有下部电极4。在这里所示的例子中,mems器件101具备第二电极27。第二电极27在贯通孔18的内部与压电层10及凹部19连接。

33.下部电极4与第一电极14在图1中被描绘在不同的地方,但两者可以电连接,可以直接或间接地通过导体而物理地连接。在图1所示的例子中,下部电极4与第一电极14在剖视图中未表示的地方连接。在压电层10的上表面配置有电极15。在上部电极5与电极15之间,也可以说与上述的针对下部电极4与第一电极14的连接方式同样的连接方式。上部电极5与电极15在图1中被描绘在不同的地方,但两者可以电连接。在图1所示的例子中,上部电极5与电极15在剖视图中未表示的地方连接。

34.在图1及图2中,未显示与第一电极14连接的导体,但实际上也可以通过贯通孔18

而配置与第一电极14连接的导体。

35.在本实施方式中,通过在上部电极5与下部电极2之间赋予电位差,能够使压电层10变形。压电器件101是利用弯曲振动的pmut(piezoelectric micromachined ultrasonic transducer,压电微机械超声换能器)。

36.在本实施方式中,第一电极14具有在贯通孔18的延长上与贯通孔18连通的凹部19,因此,能够降低进行从第一电极14的电取出时的接触电阻。

37.如图2所示,在第一电极14的上表面有时自然地形成有氧化膜16。在以使第一电极14的上表面露出的程度停止蚀刻的情况下,第一电极14的上表面成为保持被氧化膜16覆盖的状态,接触电阻可能因氧化膜16而增大,但在本实施方式中,如图2所示,凹部19被形成为往下挖第一电极14,因此,在与第一电极14进行电连接时,不易受到氧化膜16的影响,能够降低接触电阻。

38.在本实施方式中,例示了基板1包括薄壁部1e且膜片部6包括薄壁部1e的结构。但是,也可以为基板1不具备薄壁部1e的结构。换言之,为薄壁部1e的厚度为0的结构。在该情况下,膜片部6成为不包括基板1的薄壁部1e的结构。在该情况下,膜片部6也包括压电层10的一部分和中间层3的一部分。在膜片部6的下表面也可以露出中间层3。

39.如本实施方式所示,在贯通孔18的内部,也可以具备与凹部19连接的第二电极27。通过采用该结构,能够容易地进行从第一电极14的电取出。

40.(制造方法)

41.对本实施方式中的mems器件的制造方法进行说明。

42.首先,如图3所示,准备压电单晶基板17。压电单晶基板17例如可以是由litao3或linbo3形成的基板。接下来,在压电单晶基板17的一个面上通过成膜而形成下部电极4及第一电极14,图案化为所希望的形状。下部电极4及第一电极14可以由pt等形成。在压电单晶基板17与下部电极4及第一电极14的界面,也可以夹设ti层等作为密接层。

43.如图4所示,将中间层3形成为覆盖下部电极4。中间层3可以由sio2等形成。一旦形成了中间层3后,通过cmp(chemical mechanical polishing,化学机械抛光)将中间层3的表面平坦化。

44.如图5所示,将该构造体与基板1贴合。将中间层3与基板1相接来进行该贴合。贴合的结果是,成为图6所示的结构。也可以在中间层3与基板1接合的界面夹设金属层。基板1可以是硅基板。也可以在基板1的内部配置中间层。中间层3可以是将基板1的一部分热氧化而形成的层。

45.对压电单晶基板17进行研磨或剥离,或者经过两方的工序,使压电单晶基板17变薄至所希望的膜厚。作为用于通过研磨而将压电单晶基板17变薄的方法,可以采用磨削(grind)、cmp等。在通过剥离而变薄的情况下,预先通过离子注入法在压电单晶基板17上设置剥离层。在该情况下,通过控制离子注入的功率、深度等,能够得到所希望的极化。此外,为了恢复结晶性,或者为了控制极化,也可以进行退火。

46.如图7所示,将上部电极5成膜到压电单晶基板17的上表面,图案化为所希望的形状。上部电极5可以由pt等形成。在压电单晶基板17与上部电极5的界面也可以夹设ti层等作为密接层。

47.如图8所示,为了从第一电极14取出电连接,通过蚀刻而形成贯通孔18。贯通孔18

贯穿压电单晶基板17。在形成该贯通孔18时,也稍微往下挖第一电极14。也可以将与第一电极14电连接这样的布线形成于贯通孔18。

48.将压电单晶基板17、中间层3、基板1图案化为所希望的形状。如图9中箭头95所示,通过drie(deep reactive-ion etching,深反应离子蚀刻)而去除基板1的一部分或全部,由此形成膜片部6。进而在膜片部6的下表面去除绝缘膜13,形成第二电极27,由此,能够得到图1所示的mems器件101。

49.需要说明的是,也可以采用在膜片部6的下表面残留绝缘膜13的构造。

50.(实施方式2)

51.参照图10,对基于本发明的实施方式2中的mems器件进行说明。图10示出本实施方式中的mems器件102的剖视图。将图10中的贯通孔18的附近放大的情况与图2相同。mems器件102是使用体波的mems器件。mems器件102与实施方式1中说明的mems器件101同样地具有贯通孔18,第一电极14具有在贯通孔18的延长上与贯通孔18连通的凹部19。

52.在本实施方式中,压电层10也具有贯通孔18,第一电极14具有在贯通孔18的延长上与贯通孔18连通的凹部19,因此,在进行从第一电极14的电取出时,能够降低接触电阻。

53.(实施方式3)

54.参照图11,对基于本发明的实施方式3中的mems器件进行说明。图11示出本实施方式中的mems器件103的剖视图。图12示出将图11中的贯通孔18的附近放大后的情况。mems器件103是使用板波的mems器件。其中,这里所说的“板波”是在将被激励的板波的波长设为1λ的情况下在膜厚1λ以下的压电薄板激励的各种波的总称。在mems器件103中,在压电层10的上表面配置有梳形电极25和电极15。电极15可以与梳形电极25电连接。

55.在压电层10的下表面配置有接地导体26作为第一电极。

56.压电层10具有贯通孔18,作为第一电极的接地导体26具有在贯通孔18的延长上与贯通孔18连通的凹部19。如图12所示,凹部19也可以为设置于第一电极的端部的切口。接地导体26也可以用作浮置电极。

57.在本实施方式中,压电层10也具有贯通孔18,第一电极14也具有在贯通孔18的延长上与贯通孔18连通的凹部19,因此,在进行从第一电极14的电取出时,能够降低接触电阻。

58.可以说以下是目前为止说明的各实施方式中的共同点。所述第一电极的蚀刻率优选比所述压电体低。通过采用该结构,在第一电极中不用过度地去除,仅形成必要的凹部,容易结束蚀刻。

59.所述第一电极优选为外延生长层。如果第一电极为外延生长层,则在蚀刻时难以产生侧蚀,因此,容易形成良好的凹部。

60.第一电极也可以为两个以上的金属膜的层叠体。考虑第一电极例如为ti与ni的双层构造。考虑将ti膜形成为密接层,使ni膜在ti膜上重叠地生长。ni膜也可以通过外延生长而形成。在第一电极为ti与ni的双层构造的情况下,贯通孔18的附近例如如图13所示。形成在贯通孔18的延长上的凹部19形成为贯穿作为密接层而形成的ti膜14b,并进入ni膜14a。第一电极也可以为三层构造。第一电极也可以为作为电阻率小的金属例如包括al膜或pt膜的构造。在将第一电极设为三层构造的情况下,可以在ti膜及ni膜的基础上包括al膜或pt膜。

61.如图13所示,优选的是,所述第一电极是包括ni膜14a和配置在ni膜14a的压电层10侧的ti膜14b的层叠构造,凹部19贯穿ti膜14b,凹部19的底部处于ni层14a之中。换言之,优选的是,凹部19的表面在层叠方向上位于比ni膜14a与ti膜14b的边界面靠下方的位置。通过采用该结构,容易确保与ni层14a之间的电连接,能够降低接触电阻。

62.需要说明的是,也可以适当组合上述实施方式中的多个实施方式而采用。

63.需要说明的是,此次公开的上述实施方式在全部方面是例示,不是限制性的内容。本发明的范围由权利要求书示出,包括与权利要求书同等的含义及范围内的所有变更。

64.附图标记说明:

65.1基板,1a活性层,1b基础部,1e薄壁部,1f厚壁部,3中间层,4下部电极,5上部电极,6膜片部,10压电层,13绝缘膜,14第一电极,14a ni膜,14b ti膜,15电极,16氧化膜,17压电单晶基板,18贯通孔,19凹部,21空间,25梳形电极,26接地导体,27第二电极,91第一方向,92第二方向,95(表示drie的)箭头,101、102、103mems器件。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1